# ON-CHIP IMPEDANCE TRANSFORMATIONS FOR A STANDARD CMOS PROCESS

by

# Charles Edward Greene

Bachelor of Science in Electrical Engineering, University of Pittsburgh, 2001

Submitted to the Graduate Faculty of

the School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

University of Pittsburgh

2002

# UNIVERSITY OF PITTSBURGH SCHOOL OF ENGINEERING

This thesis was presented

by

Charles Edward Greene

It was defended on

December 10, 2002

and approved by

Ronald G. Hoelzeman, Associate Professor, Electrical Engineering

James T. Cain, Professor, Electrical Engineering

Thesis Advisor: Marlin H. Mickle, Nickolas A. DeCecco Professor, Electrical Engineering

# **ABSTRACT**

# ON-CHIP IMPEDANCE TRANSFORMATIONS FOR A STANDARD CMOS PROCESS

Charles Edward Greene, MS

University of Pittsburgh, 2002

On-chip impedance matching has become a major focus as companies and institutions move closer to a complete System on a Chip (SoC). With limited design area, it is important to obtain maximum power transfer to the required load. This research presents commonly used impedance matching techniques and extends them to include on-chip networks. These networks have inherent problems caused by the common substrate. It will be shown that the resulting parasitics can be calculated to allow analysis and manipulation of the overall design. It will also be demonstrated that the use of on-chip inductors will cause severe mismatch and loss due to their low quality factors. Finally, test networks will be fabricated in a 1.5-micron process to show the validity of the concepts presented.

# **ACKNOWLEDGEMENTS**

This research was supported in part by the Pittsburgh Digital Greenhouse through the project "A Stand Alone RF Powered SOC" and in part by the Department of Education through the GAANN fellowship.

# **TABLE OF CONTENTS**

|     |                                    | Page |

|-----|------------------------------------|------|

| 1.0 | Introduction                       | 1    |

| 1.1 | Background Problem                 | 1    |

| 1.2 | Initial Overview                   | 1    |

| 2.0 | Impedance Matching Background      | 3    |

| 2.1 | Theory of Maximum Power Transfer   | 3    |

| 2.2 | Theory of Maximum Voltage Transfer | 7    |

| 2.3 | Impedance Conversions              | 11   |

| 2.4 | Statement of the Problem           | 12   |

| 3.0 | Impedance Matching Networks        | 14   |

| 3.1 | L – Network                        | 14   |

| 3.  | 1.1 Downward Transformation        | 15   |

| 3.  | 1.2 Upward Transformation          | 21   |

| 3.2 | T – Network                        | 25   |

| 3   | 2.1 Downward Transformation        | 27   |

| 3   | 2.2 Upward Transformation          | 29   |

| 3.3 | Π – Network                        | 33   |

| 3   | 3.1 Downward Transformation        | 34   |

| 3   | 3.2 Upward Transformation          | 38   |

| 3.4 | Wideband Four-Element Networks     | 39   |

| 3.5 | Summary                            | 39   |

| 4.0 | On-Chip Layout and Considerations  | 40   |

| 4.1 | Inductors                          | 40   |

| 4.  | 1.1 ASITIC                         | 40   |

| 4.  | 1.2 Current Sheet Approximation    | 42   |

| 4.2 | Capacitors                         | 44   |

| 4.2     | 2.1 Typical                                                   | 44  |

|---------|---------------------------------------------------------------|-----|

| 4.2     | 2.2 Fingers                                                   | 46  |

| 4.3     | Parasitics and Tolerances                                     | 48  |

| 4.3     | 3.1 Equivalent Circuits                                       | 48  |

| 4.3     | 3.2 Effects on Ideal Networks                                 | 50  |

| 5.0     | Impedance Matching Software                                   | 52  |

| 5.1     | Software Functions                                            | 52  |

| 5.2     | Software Example for a Fabricated Network                     | 52  |

| 6.0     | Results                                                       | 60  |

| 6.1     | Discrete Components                                           | 60  |

| 6.2     | On-Chip                                                       | 63  |

| 7.0     | Conclusions                                                   | 75  |

| 8.0     | Future Directions                                             | 77  |

| 8.1     | Research Continuation                                         | 77  |

| 8.2     | Chip Simulator                                                | 77  |

| 8.3     | Complete System on a Chip                                     | 77  |

| Append  | lix A – Graph Code                                            | 80  |

| Matl    | ab Code used for Graphs 2.1, 2.3, & 2.4                       | 80  |

| Append  | lix B – Impedance Transformation Example                      | 82  |

| L-N     | Network Special Case: Upward and Downward Transformation      | 82  |

| Append  | lix C – Impedance Matching Software                           | 86  |

| C++     | Software Code                                                 | 86  |

| Append  | lix D – Test Setups                                           | 105 |

| D.1     | Agilent 8712ET RF Network Analyzer Setup for Discrete Network | 105 |

| D.2     | Agilent 4284A Precision LCR Meter Setup with Four-Lead Probe  | 106 |

| D.3     | Agilent 8712ET RF Network Analyzer Setup with Coaxial Probe   | 107 |

| D.4     | Substrate Bonded to Ground Plane                              | 108 |

| Append  | lix E – Mathead Calculations                                  | 110 |

| Netw    | ork Equivalent Impedances                                     | 110 |

| RIRI IC | OCB V DAA                                                     | 120 |

# LIST OF TABLES

|                                                                                                                                              | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2.1 – RMS Power Delivered to the Load Resistor for Different Loads with Vin=1V Peak                                                    | 4    |

| Table 2.2 – Output Voltage for Different Resistor Values                                                                                     | 8    |

| Table 3.1 – Network Combinations for a Given Bandwidth                                                                                       | 27   |

| Table 3.2 – Comparison of T – and Π – Network Q-values                                                                                       | 33   |

| Table 4.1 – ASITIC Variable Explanations                                                                                                     | 41   |

| Table 6.1 – Results for Discrete Component Network                                                                                           | 61   |

| Table 6.2 – On-Chip Networks and Components                                                                                                  | 63   |

| Table 6.3 – On-Chip Networks and Components at 1MHz                                                                                          | 67   |

| Table 6.4 – Comparison of Measured Values to the Values Calculated using the Predicted Values                                                | 70   |

| Table 6.5 – Comparison of Measured Values to the Values Calculated using the Predicted and Measured Values                                   | 71   |

| Table 6.6 – On-Chip Networks and Components at 10MHz                                                                                         | 72   |

| Table 6.7 – Comparison of Measured Values to the Values Calculated using the Predicted and Measured Values                                   | 72   |

| Table 6.8 – Comparison of Network Impedance for a Floating and Grounded Substrate                                                            | 73   |

| Table 6.9 – Comparison of Network Impedance Including Only the Series Resistance of the Inductor to the Network with all Parasitics Included | 74   |

| Table 6.10 – Network Impedances from all the Measured Chips                                                                                  | 74   |

# LIST OF FIGURES

|                                                                                                    | Page |

|----------------------------------------------------------------------------------------------------|------|

| Figure 2.1 – Unequal Output and Input Impedances at 10MHz                                          | 3    |

| Figure 2.2 – Circuit Diagram with Variable Load                                                    | 4    |

| Figure 2.3 – Output Power (RMS) with Reactive Conjugate in Red                                     | 5    |

| Figure 2.4 – Circuit Diagram Zout=Zload*                                                           | 6    |

| Figure 2.5 – Instantaneous Power for the Complex Conjugate Load and the Load Given in Figure 2.1   | 7    |

| Figure 2.6 – Simple Resistive Circuit                                                              | 8    |

| Figure 2.7 – Voltage Across Load Resistor for Circuit in Figure 2.2 with Reactive Conjugate in Red |      |

| Figure 2.8 – Output Voltage with Reactive Conjugate in Red                                         | 10   |

| Figure 2.9 – Series and Parallel Conversions                                                       | 11   |

| Figure 2.10 – Y and Δ Circuit Diagrams                                                             | 12   |

| Figure 3.1 – Two L – Network Transformations                                                       | 14   |

| Figure 3.2 – Example of a Complete Downward Transformation                                         | 16   |

| Figure 3.3 – Previous Example Using a Negative Q-value                                             | 18   |

| Figure 3.4 – Circuit Diagram                                                                       | 19   |

| Figure 3.5 – Completed Circuit with Matching Network                                               | 21   |

| Figure 3.6 – Example of a Complete Upward Transformation                                           | 22   |

| Figure 3.7 – Circuit Diagram                                                                       | 24   |

| Figure 3.8 – Matched Circuit for Example 2                                                         | 25   |

| Figure 3.9 – Example of a T – Network                                                              | 26   |

| Figure 3.10 – Upward then Downward Resistive Transformation with a Net Downward Transformation     | 26   |

| Figure 3.11 – Net Upward Resistive Transformation                                                  | 30   |

| Figure 3.12 – Four Possible Networks for  Q <sub>1</sub>  =10                                      | 32   |

| Figure 3.13 – Equivalent Π – Network                                                               | 32   |

| Figure 3.14 – Example of a Π – Network                                                             | 33   |

| Figure 3.15 – Downward Resistive Transformation                                                                             | 35  |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.16 – Complete Circuit Diagram for Positive Q-values                                                                | 36  |

| Figure 3.17 – Peak Power at the Load Versus Frequency Using a Worst Case Monte Carlo Sweep with the Ideal Case Shown in Red | 37  |

| Figure 3.18 – Upward Resistive Transformation.                                                                              | 38  |

| Figure 4.1 – Example ASITIC File for a 14.7nH Inductor                                                                      | 40  |

| Figure 4.2 – ASITIC Output for 14.7nH Inductor                                                                              | 41  |

| Figure 4.3 – ASITIC Graphic Output of 14.7nH Inductor                                                                       | 42  |

| Figure 4.4 – Spiral Approximated as a Solid Sheet                                                                           | 43  |

| Figure 4.5 – Typical 1pF Capacitor Layout                                                                                   | 45  |

| Figure 4.6 – Rectangular Capacitor                                                                                          | 46  |

| Figure 4.7 – Double Row of Contacts                                                                                         | 47  |

| Figure 4.8 – 1pF Capacitor Layout                                                                                           | 47  |

| Figure 4.9 – ASITIC Two-port Equivalent Circuit for an Inductor                                                             | 48  |

| Figure 4.10 – Capacitor Equivalent Circuit                                                                                  | 49  |

| Figure 4.11 – Simplified Capacitor Equivalent Circuit                                                                       | 50  |

| Figure 6.1 – Discrete Component L – Network                                                                                 | 60  |

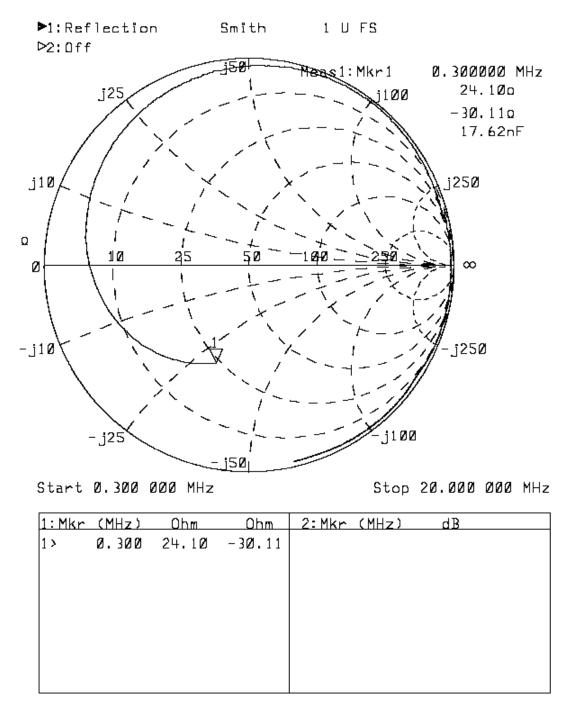

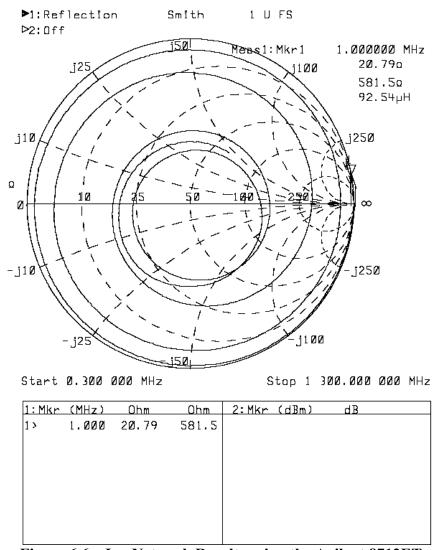

| Figure 6.2 – Smith Chart of Impedance Results                                                                               | 62  |

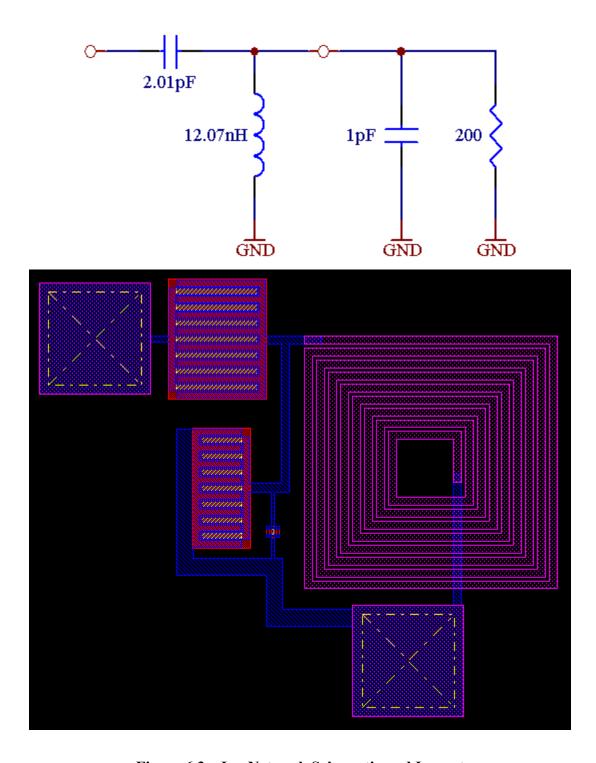

| Figure 6.3 – L – Network Schematic and Layout                                                                               | 64  |

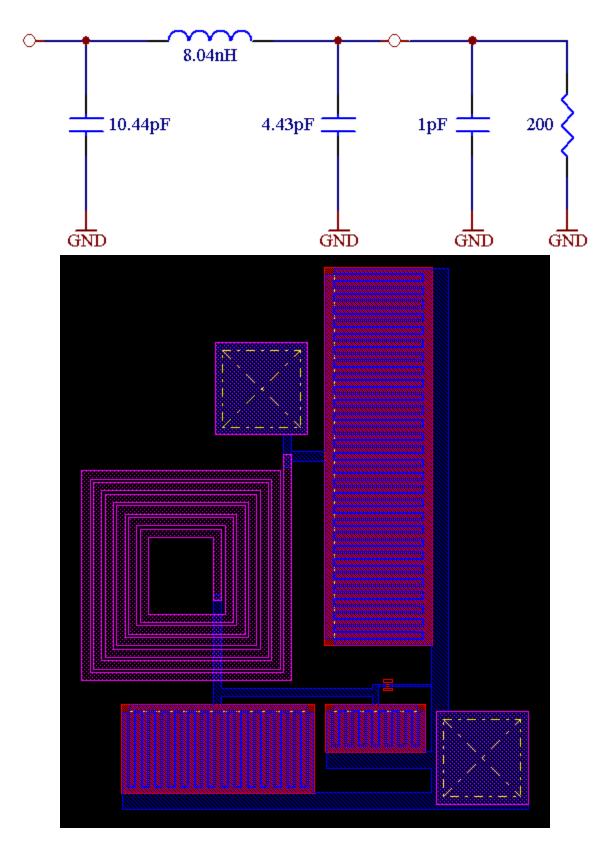

| Figure 6.4 – Π – Network (1) Schematic and Layout.                                                                          | 65  |

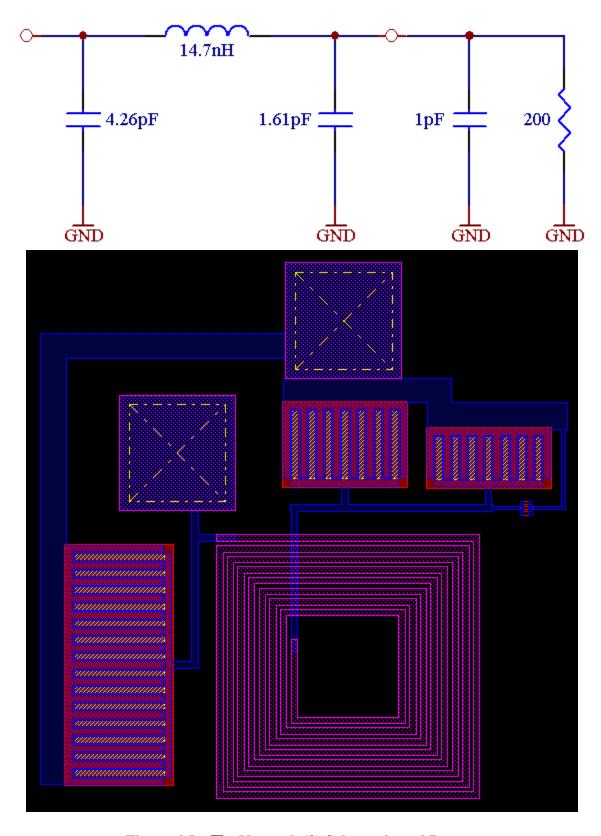

| Figure 6.5 – Π – Network (2) Schematic and Layout                                                                           | 66  |

| Figure 6.6 – L – Network Results using the Agilent 8712ET                                                                   | 69  |

| Figure B.1 – Circuit Diagram                                                                                                | 82  |

| Figure B.2 – Completed Circuit with Matching Network                                                                        | 83  |

| Figure B.3 – Completed Circuit with Matching Network                                                                        | 85  |

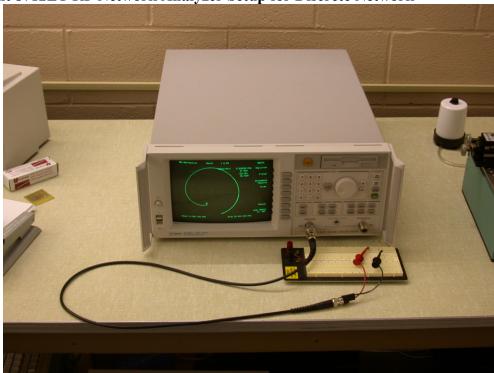

| Figure D.1 – Agilent 8712ET RF Network Analyzer Connected to the Discrete Network using Fifty-ohm Coaxial Cable             | 105 |

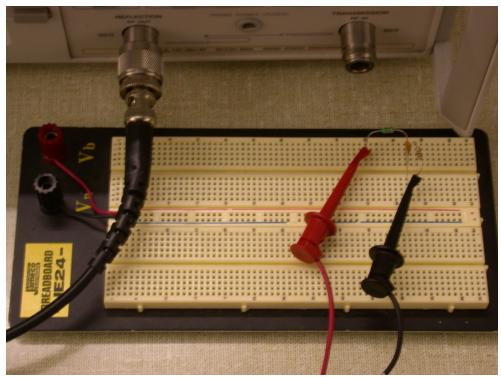

| Figure D.2 – Close-up of Discrete Network Connection                                                                        | 106 |

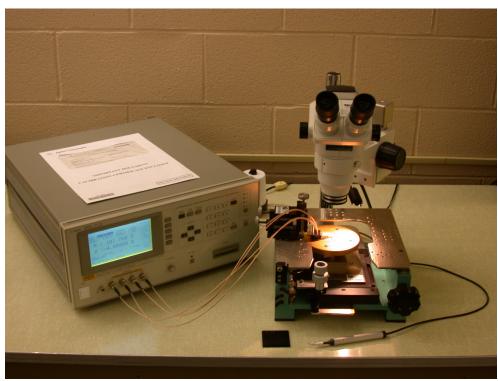

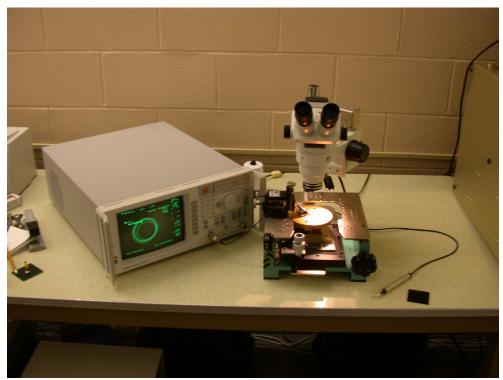

| Figure D.3 – Agilent 4284A Connected to the J micro Technology JR-2727 Probe Station through Four Fifty-ohm Coaxial Cables  | 106 |

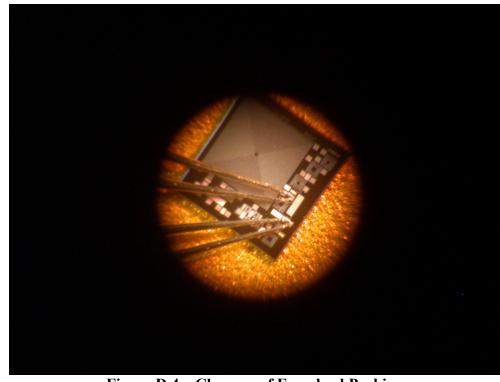

| Figure D.4 – Close-up of Four-lead Probing                                                                                  | 107 |

| Figure D.5 – Agilent 8712ET Connected to the J micro Technology JR-2727 Probe Station |       |

|---------------------------------------------------------------------------------------|-------|

| through Fifty-ohm Coaxial Cable                                                       | . 107 |

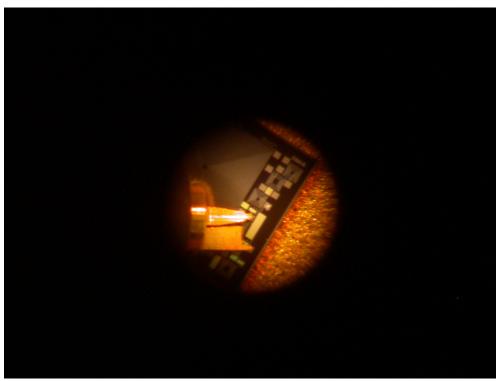

| Figure D.6 – Close-up of Coaxial Probing                                              | . 108 |

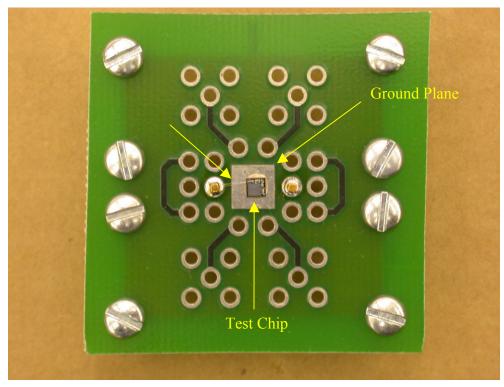

| Figure D.7 – Test Board for Grounded Substrate                                        | . 108 |

| Figure D.8 – Close-up of Bonded Chip                                                  | . 109 |

#### 1.0 INTRODUCTION

# 1.1 Background Problem

Current Radio-Frequency Identification (RFID) tags require the use of both receiving circuitry and an external antenna. The recent objective has been to create a System on a Chip (SoC) by integrating the antenna along with the required circuitry. This poses a problem when the antenna is connected to the driving amplifier. In standard systems, the output of the amplifier and the impedance of the antenna were designed to be 50 ohms. The connection of the two independent parts could then be done using standard 50-ohm coaxial cable or a microstrip transmission line. An on-chip antenna does not necessarily have an impedance of 50 ohms, and there is no need to use coaxial cable. For these reasons, the impedance does not need to be 50 ohms. The amplifier and antenna can be designed to optimize their on-chip performance without having to worry about fixed impedance values.

To obtain the maximum power transfer to the antenna for transmitting, an impedance matching network must be inserted between the two components. These networks, however, have inherent parasitic effects caused by the grounded substrate, which means they cannot simply be designed using standard methods.

# 1.2 Initial Overview

To better understand the problems with on-chip impedance matching, the available narrowband networks will be examined in detail. These topologies will be manipulated to obtain multiple networks of inductors and capacitors that can be used to match the source and load impedances. Once a network is obtained, the architecture of the components must be taken into consideration to help minimize the effects of the substrate. This must be done to insure the network performs in a desirable way.

In the following sections, the matching elements are analyzed in order to fabricate test networks with robust performance. An impedance matching program will also be presented to help characterize the matching networks. The program will be designed to include the parasitic effects of the substrate and inherent conductor losses to determine whether the network

consumes more power than it can deliver to the load. Finally, test networks will be fabricated on an analog CMOS process to see if the characterization process has been successful.

# 2.0 IMPEDANCE MATCHING BACKGROUND

# 2.1 Theory of Maximum Power Transfer

As devices become smaller, generally batteries and other energy supplying sources are also scaled in size. One way to deal with the decrease in available power is to conserve AC energy by minimizing reflections. Reflections are caused by unequal output and input impedances like the ones seen in Figure 2.1.

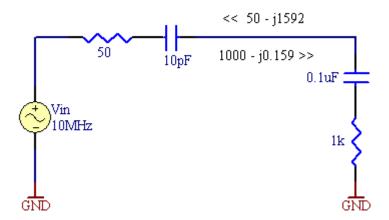

Figure 2.1 – Unequal Output and Input Impedances at 10MHz

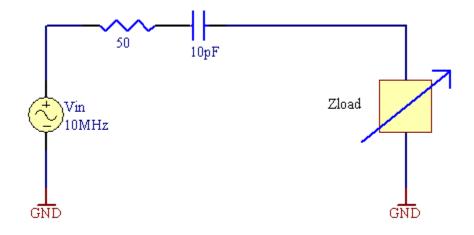

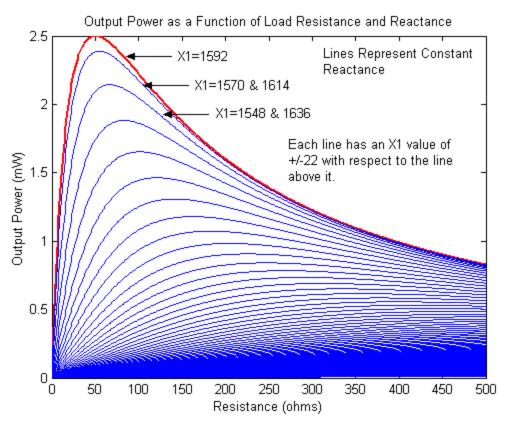

The Maximum Power Transfer Theorem states that the maximum power is received at the load when the output impedance of the driving stage is the complex conjugate of the load impedance [1]. This is best illustrated through an example. The output power for the circuit seen in Figure 2.2 was calculated for different load impedances. The results can be seen in Table 2.1. Figure 2.3 shows how changes in the load resistance and reactance affect the output power.

Figure 2.2 – Circuit Diagram with Variable Load

Table 2.1 – RMS Power Delivered to the Load Resistor for Different Loads with Vin=1V Peak

| <b>Load Impedance (Ω)</b> | Power in Load Resistor (mW), Vin = 1V |

|---------------------------|---------------------------------------|

| 1000 :0 1502              | ` ''                                  |

| 1000-j0.1592              | 0.1375                                |

| 1000+j0.1592              | 0.1375                                |

| 500-j15.92                | 0.0866                                |

| 500+j15.92                | 0.0904                                |

| 200-j159.2                | 0.0320                                |

| 200+j159.2                | 0.0473                                |

| 100-j1592                 | 0.0049                                |

| 100+j1592                 | 2.2222                                |

| 50-j1592                  | 0.0025                                |

| 50+j1592                  | 2.5                                   |

| (complex conjugate)       |                                       |

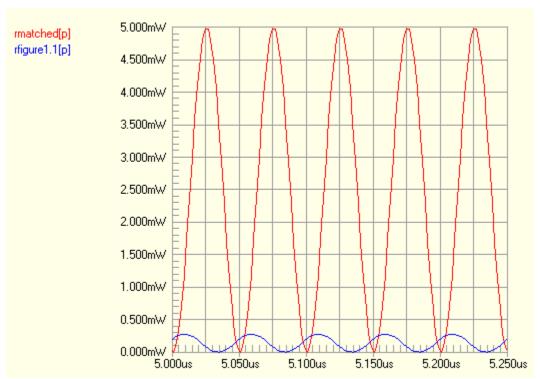

Figure 2.3 – Output Power (RMS) with Reactive Conjugate in Red

The Matlab code used to produce the preceding figure along with Figures 2.7 & 2.8 can be seen in Appendix A.

As Table 2.1 and Figure 2.3 show, the maximum load power is achieved with the complex conjugate pair. This can be seen by examining the equivalent impedance of the circuit.

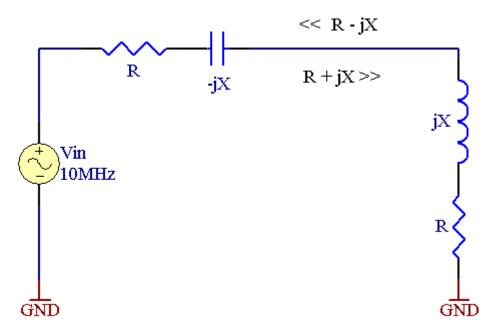

Figure 2.4 - Circuit Diagram Zout=Zload\*

$$Z_{EO} = R - jX + R + jX = 2R$$

(2.1)

$$I = \frac{V_{IN}}{Z_{EO}} = \frac{V_{IN} \angle 0^{\circ}}{2R} = \frac{V_{IN}}{2R} \angle 0^{\circ}$$

(2.2)

As seen in Equation 2.1, the equivalent impedance is totally resistive because the reactive components have canceled. The absence of a reactive element guarantees that the voltage and current will be in phase, as Equation 2.2 shows. Figure 2.5 shows the difference in instantaneous power for in-phase and out-of-phase voltages and currents.

Figure 2.5 – Instantaneous Power for the Complex Conjugate Load and the Load Given in Figure 2.1

This graph again shows that the maximum power is achieved at the load when the load impedance is the complex conjugate of the output impedance of the driving stage.

# 2.2 Theory of Maximum Voltage Transfer

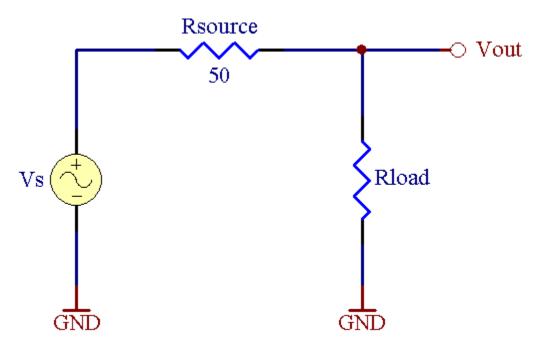

To obtain the maximum transferred voltage, the load resistance must be much greater than the output resistance of the driving stage [2]. The output voltage was calculated for the circuit seen in Figure 2.6. The results are displayed in Table 2.2.

Figure 2.6 – Simple Resistive Circuit

**Table 2.2 – Output Voltage for Different Resistor Values**

| Load Resistance (Ω) | Average Load Power | Peak Load Voltage (V) |

|---------------------|--------------------|-----------------------|

|                     | (mW)               | Vs=1V                 |

| 5                   | 0.826              | 0.091                 |

| 25                  | 2.222              | 0.333                 |

| 50                  | 2.5                | 0.500                 |

| 100                 | 2.222              | 0.667                 |

| 1K                  | 0.454              | 0.952                 |

| 5K                  | 0.098              | 0.990                 |

| 10K                 | 0.050              | 0.995                 |

| 100K                | 0.005              | 0.9995                |

| 1M                  | 0.0005             | 0.99995               |

As Table 2.2 shows, the output voltage asymptotically approaches the input voltage as the value of the output resistance is increased. This simple concept can be extended to complex output and input impedances. The following graph shows how variations in the load resistance and reactance affect the output voltage. The data were calculated using the circuit shown in Figure 2.2 with an input voltage of one-volt peak.

Resistive Load Voltage as a Function of Load Resistance and Reactance X1=1592 X1=1464 0.9 & 1720 0.8 Voltage Across Load Resistor (V) 0.7 0.6 0.5 0.4 0.3 Lines Represent Constant 0.2 Reactance Each line has an X1 value of 0.1 +/-128 with respect to the line above it. 0 400 600 800 1000 1200 1400 1600 1800 0 200 2000 Resistance (ohms)

Figure 2.7 – Voltage Across Load Resistor for Circuit in Figure 2.2 with Reactive Conjugate in Red

It can be seen from Figure 2.7 that the voltage across the load resistor increases as its value is increased. It can also be seen that the maximum voltage occurs when the reactive part of the load is the conjugate of the reactive component of the source impedance. From this, it can be concluded that maximum voltage transfer is achieved when the load impedance meets the following criteria.

$$\begin{split} R_{LOAD} \gg R_{SOURCE} \\ X_{LOAD} = -X_{SOURCE} \end{split}$$

It should be noted that this analysis was done using the voltage across the load resistor. In cases where the voltage across the entire load is desired, the maximum occurs when the resistive part is zero and the reactive element is the conjugate of the source reactance. This is illustrated by Figure 2.8, which was calculated using Figure 2.2 with an input voltage of one-volt peak. The

maximum occurs at this point since it is a resonant circuit. Resonant circuits generally have a circuit Q-value,  $Q_C$ , that is significantly larger than one [2].

$$Q_C = \frac{X}{R_T} \tag{2.3}$$

As Equation 2.3 shows, the total resistance in the circuit is inversely proportional to the circuit Q-value. By making the load resistance as small as possible, the circuit Q-value is maximized. A high valued  $Q_C$  guarantees a large and narrow peak around the resonant frequency.

Figure 2.8 – Output Voltage with Reactive Conjugate in Red

To obtain the maximum voltage transfer to the entire load, the criteria become the following.

$$\begin{split} R_{LOAD} \ll R_{SOURCE} \\ X_{LOAD} = -X_{SOURCE} \end{split}$$

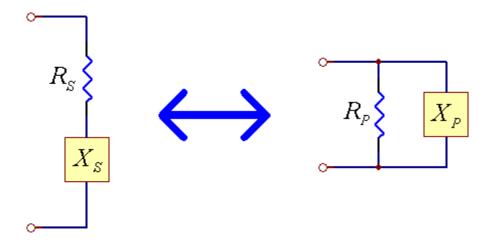

# 2.3 Impedance Conversions

The input or output impedance is not always given or desired in the series format. The figures and equations below show a simple way of converting between the series and parallel forms [2].

Figure 2.9 – Series and Parallel Conversions

$$R_{P} = \frac{R_{S}^{2} + X_{S}^{2}}{R_{S}} \tag{2.4}$$

$$X_{P} = \frac{R_{S}^{2} + X_{S}^{2}}{X_{S}} \tag{2.5}$$

$$R_S = \frac{R_P \cdot X_P^2}{R_P^2 + X_P^2} \tag{2.6}$$

$$X_{S} = \frac{R_{P}^{2} \cdot X_{P}}{R_{P}^{2} + X_{P}^{2}} \tag{2.7}$$

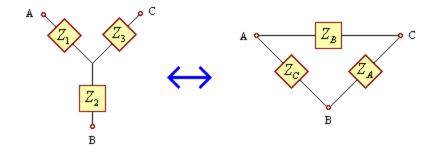

Another useful impedance transformation is between the wye and delta formats. The equations for the  $Y - \Delta$  and the  $\Delta - Y$  conversions are given below along with there circuit diagrams [2].

Figure 2.10 – Y and Δ Circuit Diagrams

$$Z_{A} = \frac{Z_{1} \cdot Z_{2} + Z_{1} \cdot Z_{3} + Z_{2} \cdot Z_{3}}{Z_{1}}$$

(2.8)

$$Z_{B} = \frac{Z_{1} \cdot Z_{2} + Z_{1} \cdot Z_{3} + Z_{2} \cdot Z_{3}}{Z_{2}}$$

(2.9)

$$Z_C = \frac{Z_1 \cdot Z_2 + Z_1 \cdot Z_3 + Z_2 \cdot Z_3}{Z_3} \tag{2.10}$$

$$Z_1 = \frac{Z_B \cdot Z_C}{Z_A + Z_R + Z_C} \tag{2.11}$$

$$Z_{2} = \frac{Z_{A} \cdot Z_{C}}{Z_{A} + Z_{R} + Z_{C}}$$

(2.12)

$$Z_{3} = \frac{Z_{A} \cdot Z_{B}}{Z_{A} + Z_{R} + Z_{C}}$$

(2.13)

# 2.4 Statement of the Problem

The problem to be addressed is the optimum matching of impedance between a circuit output and the input of a second circuit. Both of the circuits and the matching elements will be fabricated on an analog or analog/digital CMOS die.

Initially, a review of the suitable networks for impedance matching will be presented to determine the best topology with the minimal complexity. Using these candidate topologies and additional computed data, the effects of the parasitics and component tolerances will be examined. In order to simplify this design procedure, a program will be developed to determine the behavior of a specified network taking into account the parasitic effects of the common substrate along with inherent conductor losses for a given process.

The inductors and capacitors used in these networks may be laid out in a variety of fashions to obtain the desired values. These layouts, however, may not be suitable for the precise function of impedance matching. Thus, candidate layouts for both inductors and capacitors will be presented to simplify the layout process.

Specific example matching problems will be analyzed and designed to demonstrate the techniques and challenges involved in practical matching situations. These examples will be laid out and fabricated on a CMOS die to show the results. The CMOS die will then be tested, and the results will be included as a part of this research. Finally, the results will be summarized along with recommendations for future research.

#### 3.0 IMPEDANCE MATCHING NETWORKS

#### 3.1 L – Network

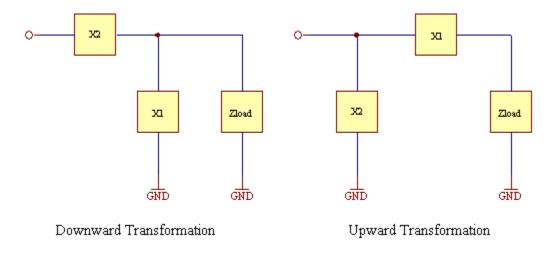

The L – Network is one of the simplest impedance matching networks. It contains two elements with the possibility of two different configurations. The figure below shows the two L – Network matching circuits.

Figure 3.1 – Two L – Network Transformations

These two networks can be used to transform any load impedance into the complex conjugate of the driving output impedance. The position of the element closest to the load determines whether the resistive transformation is upward or downward. In general, the terms upward and downward are used to describe the equivalent resistance of the network compared to the original load resistance. If the first element is in parallel with the load, the transformation is downward. If it is in series, an upward transformation is performed [3]. Given this information, it is easy to see that this element is responsible only for the resistance transformation. The element closest to the source or driver is used to cancel out or add reactance to that added by the resistive transforming element.

Now that the elements of the typical matching networks are understood, the equations used to derive their values must be presented. There will be two sets of equations presented. These sets will correspond to the downward and the upward transformations.

#### 3.1.1 Downward Transformation

A downward transformation is required if the load resistance is greater than the resistive component of the source impedance. This comparison can be done with both the source and load impedances in the series or parallel format. It can also be done with one impedance in the series format while the other is in its parallel format. For small resistive transformations, both downward and upward transformations will give the desired impedance. This special case occurs when the steps outlined in both the downward and upward transformation sections yield a noncomplex value for Q. For further explanation of this case, refer to the example in Appendix B. As explained above, the downward transformation utilizes the left hand circuit seen in Figure 3.1.

The first step in any impedance transformation is to manipulate the circuit to obtain the most desirable configuration. A desirable configuration can be defined as the circuit form that allows simple visual inspection along with uncomplicated equation derivation. For the downward transformation, it is more straightforward to have the load in its parallel format and the desired impedance (complex conjugate of the driving stage) in a series representation. This is true because the first element in the matching network is in parallel with the load while the second element is in series with the source impedance. These impedances can be quickly transformed to their parallel or series equivalent using the methods outlined in Section 2.3.

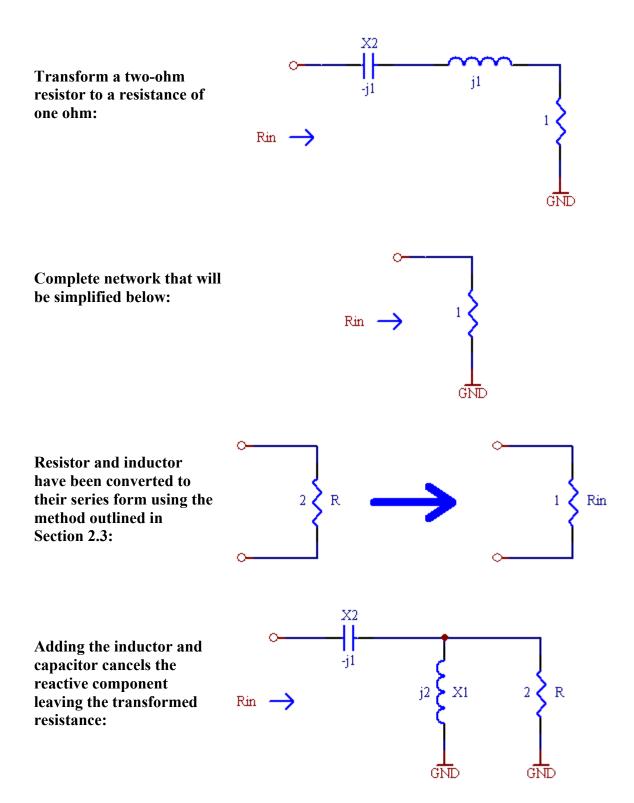

Now that the circuit is in the proper format, it can be transformed to the necessary impedance. The following figure shows the circuit representations from the beginning to the end of the transforming process.

Figure 3.2 – Example of a Complete Downward Transformation

The transformation in Figure 3.2 can be realized using the following equations [3]. The variables R and X represent the starting impedance or load while  $R_{\rm IN}$  and  $X_{\rm IN}$  correspond to the transformed impedance or complex conjugate of the driving stage. As stated before, the load is desired in the parallel format. If the load is in the series format, it must first be converted to its parallel equivalent. If R and X are taken from the series circuit, these equations will yield incorrect results.

$$Q = \pm \sqrt{\frac{R}{R_{IN}} - 1} \tag{3.1}$$

$$X_1 = \frac{X \cdot R}{O \cdot X - R} \tag{3.2}$$

$$X_2 = X_{IN} - Q \cdot R_{IN} \tag{3.3}$$

When X or  $X_{IN}$  are not present in the problem, as with the previous example, the equations defined above must be modified. Since X and R are in the parallel format for the downward transformation, the absence of X corresponds to an infinite reactance. The input elements,  $X_{IN}$  and  $R_{IN}$ , are in the series format making the absence of  $X_{IN}$  appear as a short or zero reactance. For these situations, the following equations should be substituted where needed for those described previously in this subsection.

For  $X \to \infty$ :

$$X_1 = \frac{R}{Q} \tag{3.4}$$

For  $X_{IN} = 0$ :

$$X_2 = -Q \cdot R_{IN} \tag{3.5}$$

As seen in Equation 3.1, the value of Q can be positive or negative. Its magnitude describes the bandwidth of the matching network. Larger values of Q produce smaller bandwidths while small Q-values enable wider bands. As a good approximation, the Q of the overall circuit is one half the magnitude of the Q-value for the L – Network [3]. The value of the overall Q as a function

of bandwidth is described by the following equation where  $f_o$  is the center frequency and BW is the bandwidth. This equation becomes a better approximation as the value of Q increases [2].

$$Q = \frac{f_o}{BW} \tag{3.6}$$

For a given bandwidth, there are two possible matching networks. One will have a positive Q while the other will be negative. This allows the choice between two networks with different components. The network with the most desirable characteristics can be chosen for the specified application. These characteristics include component values and element parasitics, which will be explained in Section 4.3. This can be applied to the network in Figure 3.2, which was done with a positive Q-value. The network seen in Figure 3.3 will also perform the required transform by using a negative Q-value.

Figure 3.3 – Previous Example Using a Negative Q-value

An example of this complete process can be seen in the following numerical problem.

# Example 1:

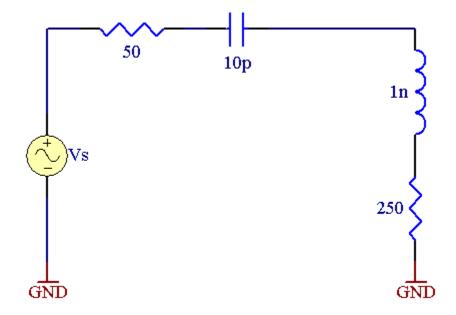

A source has an output impedance corresponding to a 50 ohm resistance in series with a 10pF capacitor. Match this output impedance to a load with a 250-ohm resistor in series with a 1nH inductor at a frequency of 1MHz. The circuit diagram can be seen below.

Figure 3.4 – Circuit Diagram

# **Solution:**

For this example, the load resistor is significantly greater than the source impedance, which means a downward transformation is required. The first step is to calculate the reactive terms in ohms.

$$10pF \rightarrow \frac{-1}{\omega C} = \frac{-1}{2 \cdot \pi \cdot f \cdot C} = \frac{-1}{2 \cdot \pi \cdot 1M \cdot 10p} = -15.915K\Omega$$

$$1nH \rightarrow \omega L = 2 \cdot \pi \cdot f \cdot L = 2 \cdot \pi \cdot 1M \cdot 1n = 6.283 m\Omega$$

Next, it is important to have the impedances in the proper format. For the downward transformation, the source impedance is required in the series format while the load should be in the parallel form. Since the source impedance is already in the series format, only the load must be transformed. Using the equations from Section 2.3:

$$R_S = 250\Omega$$

$$X_S = 6.283m\Omega$$

$$R_P = \frac{R_S^2 + X_S^2}{R_S} = 250\Omega$$

$$X_P = \frac{R_S^2 + X_S^2}{X_S} = 9.947M\Omega$$

Using the load in its parallel form, the variables for this example become the following values.

$$R = 250\Omega$$

$$X = 9.947M\Omega$$

$$R_{IN} = 50\Omega$$

$$X_{IN} = 15.915K\Omega \leftarrow Complex Conjugate$$

Using the equations in this subsection, the following matching elements were calculated.

$$Q = \pm \sqrt{\frac{R}{R_{IN}} - 1} = \pm \sqrt{\frac{250}{50} - 1} = \pm 2$$

Choosing a positive Q-value yields:

$$X_{1} = \frac{X \cdot R}{Q \cdot X - R} = 125\Omega$$

$$X_{2} = X_{IN} - Q \cdot R_{IN} = 15915 - 2 \cdot 50 = 15.815K\Omega$$

At 1MHz, these reactances are realized by the following components.

$$X_1 \rightarrow 19.894 \mu H$$

$$X_2 \rightarrow 2.517 mH$$

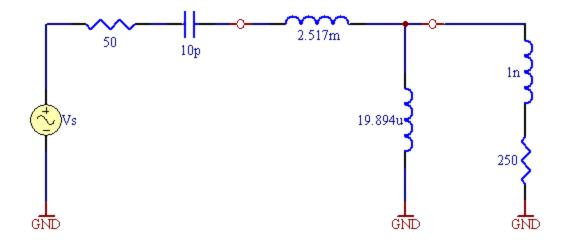

The completed circuit can be seen in the following figure.

Figure 3.5 – Completed Circuit with Matching Network

For specific applications like on-chip design, a 2.517mH inductor is not realizable. Here, it is assumed that the analog circuit designer using the results of this research will be familiar with what values of inductance, capacitance, and resistance can be fabricated. Thus, any alternative designs will be evaluated in the same manner as illustrated here.

To correct the problem of the large valued inductor, the L – Network with a negative Q-value can be calculated for comparison. In this case, however, the network with a negative Q-value has a similar component value, which is depicted in the values below.

$$X_1 = -124.998 \rightarrow 1.273nF$$

$X_2 = 16015 \rightarrow 2.549mH$

This network is still unacceptable for on-chip design. Because these two networks are the only available L – Networks, there will be a need to use a three-element matching network to produce acceptable values. These alternative topologies are covered in Sections 3.2 and 3.3.

# 3.1.2 Upward Transformation

An upward transformation is required if the load resistance is less than the output resistance of the driving stage. To accomplish the upward transformation, the right hand circuit seen in Figure 3.1 is used. Like the downward transformation, the upward transformation also has a more manageable configuration. In this case, the load is desired in the series format while the

desired impedance should be placed in the parallel form. These forms can be obtained using the methods presented in Section 2.3. The circuit diagrams for an upward transformation process can be seen in the following figure [3].

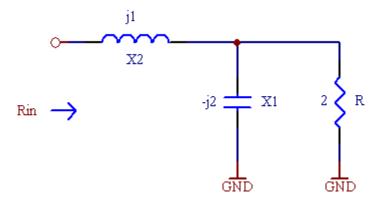

Figure 3.6 – Example of a Complete Upward Transformation

The circuit transformation in Figure 3.6 can be obtained using the following equations [3]. As previously explained, the variables R and X represent the starting impedance in its series format while  $R_{IN}$  and  $X_{IN}$  correspond to the transformed impedance in its parallel form.

$$Q = \pm \sqrt{\frac{R_{IN}}{R} - 1}$$

(3.7)

$$X_1 = Q \cdot R - X \tag{3.8}$$

$$X_{2} = \frac{X_{IN} \cdot R_{IN}}{R_{IN} - Q \cdot X_{IN}}$$

(3.9)

As with the downward transformation, the absence of X or  $X_{IN}$  means the equations above need to be modified to reflect the missing element. If this is not done, Equation 3.9 will be completely invalid and yield some form of infinity over infinity. The upward transformation requires the load in the series format, which makes an absent X appear as a short or zero reactance. The desired impedance, on the other hand, is in the parallel format, which makes the lack of  $X_{IN}$  appear as an open circuit or infinite reactance. In either case, the following equations should be substituted where needed.

For

$$X = 0$$

:

$$X_1 = Q \cdot R \tag{3.10}$$

For  $X_{IN} \rightarrow \infty$ :

$$X_2 = -\frac{R_{IN}}{Q} \tag{3.11}$$

The complete L – Network upward transformation process can be seen in the following example.

# Example 2:

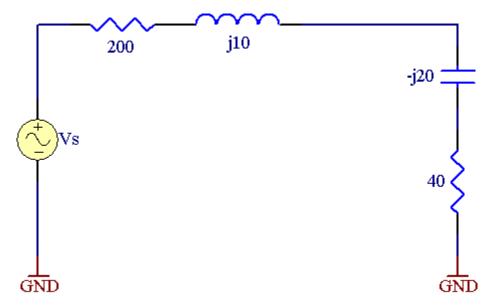

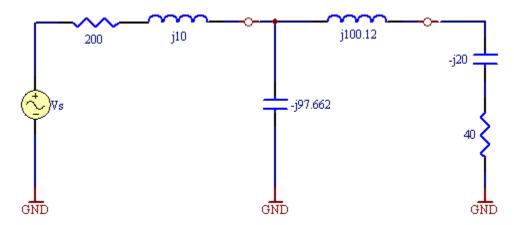

Transform a load impedance of 40-j20 to match a source impedance of 200+j10. The circuit diagram can be seen below.

Figure 3.7 – Circuit Diagram

# **Solution:**

The upward transformation requires the load impedance in the series format while the source impedance is in the parallel form. For the given example, the series source impedance becomes the following.

$$R_S = 200\Omega$$

$$X_S = 10\Omega$$

$$R_P = \frac{R_S^2 + X_S^2}{R_S} = 200.5\Omega$$

$$X_P = \frac{R_S^2 + X_S^2}{X_S} = 4.01K\Omega$$

Using the parallel source impedance, the values for this example become:

$$\begin{split} R &= 40\Omega \\ X &= -20\Omega \\ R_{IN} &= 200.5\Omega \\ X_{IN} &= -4.01K\Omega \leftarrow Complex\ Conjugate \end{split}$$

Using the equations in this subsection, the following matching elements can be calculated.

$$Q = \pm \sqrt{\frac{R_{IN}}{R} - 1} = \pm \sqrt{\frac{200.5}{40} - 1} = \pm 2.003$$

Choosing a positive Q-value yields:

$$X_1 = Q \cdot R - X = 2.003 \cdot 40 + 20 = 100.12\Omega$$

$$X_2 = \frac{X_{IN} \cdot R_{IN}}{R_{IN} - Q \cdot X_{IN}} = \frac{-4.01K \cdot 200.5}{200.5 + 2.003 \cdot 4.01K} = -97.662\Omega$$

The matched circuit can be seen in Figure A.3.2.

Figure 3.8 – Matched Circuit for Example 2

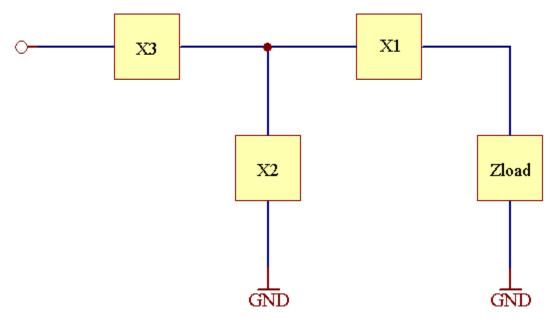

# 3.2 T – Network

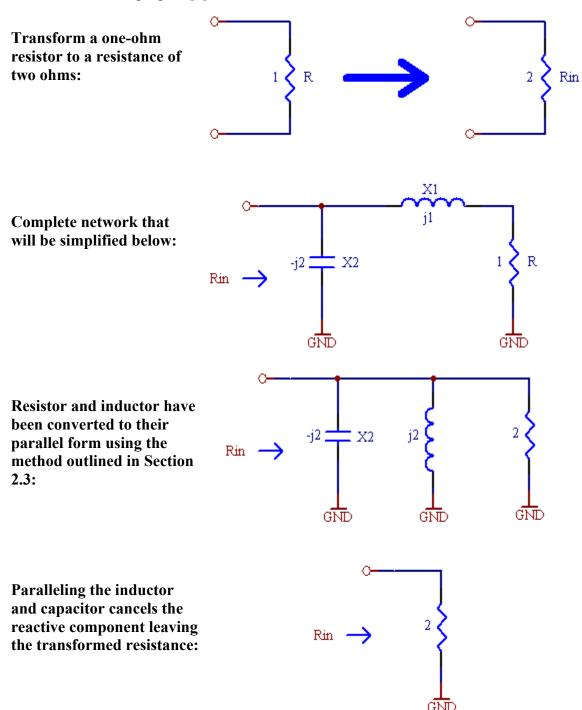

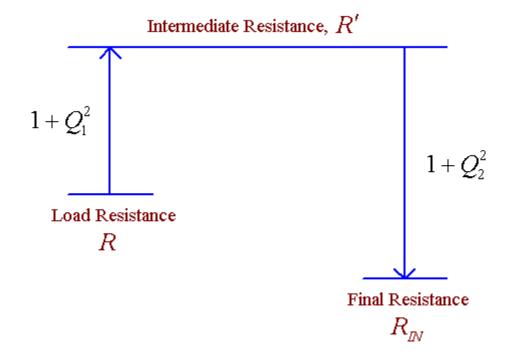

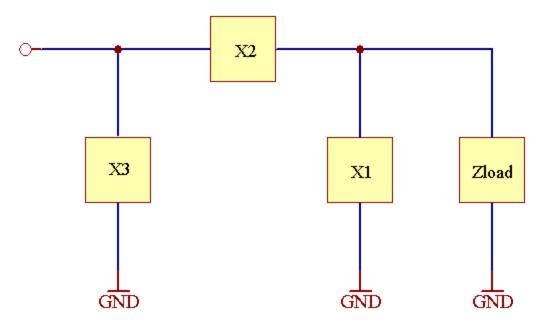

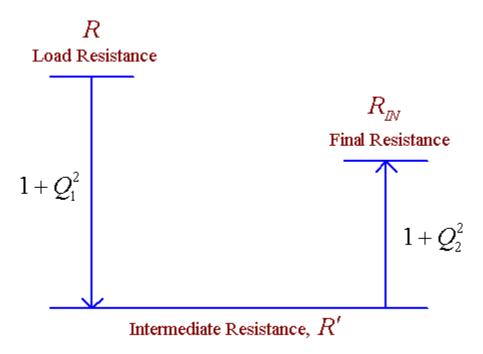

The T – Network is a three-element impedance matching network. An example can be seen in Figure 3.9. It has one main advantage over the L – Network. The third element adds another degree of freedom in the form of a second Q variable. The additional Q-value means there will be an intermediate resistance, R', in the transformation process. Figure 3.10 illustrates the intermediate resistance with a simple graph [3]. The second resistive transformation allows a value to be chosen for one of the variables. This added flexibility allows one of the Q-values to be specified or more importantly for on-chip design, one of the network's components. This minimizes design time by allowing the use of an existing component layout.

Figure 3.9 – Example of a T – Network

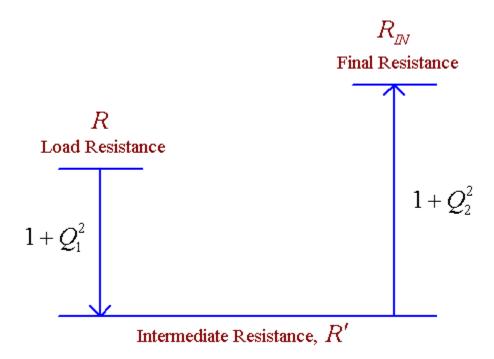

Figure 3.10 – Upward then Downward Resistive Transformation with a Net Downward Transformation

If the maximum Q-value is chosen, it must always be greater than or equal to the value of Q for the L – Network [4]. This can be explained by examining Figure 3.10. The load resistance is first transformed upward to a value dictated by  $Q_1$ . It is then transformed downward to the

required resistance using  $Q_2$ . By setting  $Q_1$  equal to zero, the intermediate resistance will be the same as the load resistance. This means that only the downward transformation will occur, and  $X_1$  will be the negative value of the load reactance. Since  $Q_1$  is generally greater than zero,  $Q_2$  must be greater than the Q of the L – Network. The same applies when setting the value of  $Q_2$  equal to zero.

As with the L – Network, a good approximation of the overall circuit Q for the T – network is one half of the maximum value of  $|Q_1|$  and  $|Q_2|$ . This approximation becomes more accurate as  $Q_1$  and  $Q_2$  become significantly different [3].

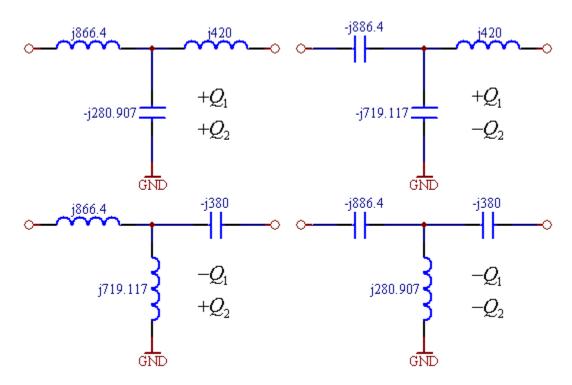

As explained for the L – Network, the Q-values can have positive and negative values. Since the T – Network has two Q-values, there will be four possible matching networks for a given bandwidth. Both of the values can be positive or negative, or one can be negative while the other is positive as shown in Table 3.1. This added flexibility allows the designer to choose the best network for the given application.

Table 3.1 – Network Combinations for a Given Bandwidth

| Combinations | $ \mathbf{Q}_1  = \mathbf{X},  \mathbf{Q}_2  = \mathbf{Y}$ |

|--------------|------------------------------------------------------------|

| Network 1    | $Q_1 = X, Q_2 = Y$                                         |

| Network 2    | $Q_1 = X, Q_2 = -Y$                                        |

| Network 3    | $Q_1 = -X, Q_2 = Y$                                        |

| Network 4    | $Q_1 = -X, Q_2 = -Y$                                       |

Although the T – Network does have its advantages, it also has a drawback. The addition of the third element introduces more parasitics and another component with potential variations that degrade the performance of the overall network. This will be discussed in more detail in Section 4.3.

## 3.2.1 Downward Transformation

The downward transformation is derived with the output and load impedances in the series format. A method for switching between parallel and series format was outlined in Section 2.3.

The equations for the downward transformation are listed below [3]. Because there is one degree of freedom, a value must be assigned to one of the variables.

$$Q_1 = \pm \sqrt{\frac{R'}{R} - 1} \tag{3.12}$$

$$Q_2 = \pm \sqrt{\frac{R'}{R_{IN}} - 1} \tag{3.13}$$

$$X_1 = Q_1 \cdot R - X \tag{3.14}$$

$$X_2 = \frac{-R'}{Q_1 + Q_2} \tag{3.15}$$

$$X_3 = Q_2 \cdot R_M + X_M \tag{3.16}$$

Where  $R,\,X,\,R_{{\scriptscriptstyle I\!N}},\,$  and  $X_{{\scriptscriptstyle I\!N}}$  are in the series form and  $\,R'>R\,\&\,\,R_{{\scriptscriptstyle I\!N}}\,.$

There is a special case when the input or output reactance is not present. Because the input and output impedances are in the series format, this corresponds to a reactance of zero or a short circuit. The previous equations are still valid since the reactance term is zeroed. For these situations, the preceding equations simplify to the following forms.

For X = 0:

$$X_1 = Q_1 \cdot R \tag{3.17}$$

For  $X_{IN} = 0$ :

$$X_3 = Q_2 \cdot R_{IN} \tag{3.18}$$

An example of the T – Network downward transformation can be seen below.

# Example 3:

It is desired to match an on-chip 200-ohm resistor in parallel with a 1pF capacitor to a 50-ohm source impedance at 915MHz. Choose a Q<sub>2</sub> value of one. Find the matching network with positive Q-values.

## **Solution:**

Using the equations presented in this subsection, the subsequent values can be calculated.

$$Q_2 = 1$$

$Q_1 = 0.401$

$R' = 100\Omega$

$X_1 = 133.597\Omega \rightarrow 23.238nH$

$X_2 = -71.362\Omega \rightarrow 2.437 pF$

$X_3 = 50\Omega \rightarrow 8.697nH$

# 3.2.2 Upward Transformation

The upward transformation is also performed with the source and load impedances in the series format. The equations for the upward transformation are the same as the downward equations (3.12-3.18).

While the downward resistive transformation is explained by Figure 3.10, the resistive transformation for the upward case is presented in the following figure [3].

Figure 3.11 – Net Upward Resistive Transformation

The upward transformation process can be seen in the following numerical example.

# Example 4:

Repeat Example 2 using a T-Network. Design the network so the magnitude of the maximum Q-value is equal to 10. Give all possible networks for this Q-value. Use the network with positive Q-values to show that the  $\Pi-$ Network (see Section 3.3) obtained from the  $Y-\Delta$  conversion will have different values for  $Q_1$  and  $Q_2$ .

#### **Solution:**

The T – Network requires the source and load impedances in the series format, which yields the following values.

$$R = 40\Omega$$

$X = -20\Omega$

$R_{IN} = 200\Omega$

$X_{IN} = -10\Omega \leftarrow Complex \ Conjugate$

Figure 3.11 shows that  $Q_1$  will have a larger value than  $Q_2$  for the upward transformation. Using this graph,

$$Q_1 = 10$$

because the problem specifies the maximum Q-value.

Using equations 3.12 - 3.16,

$$R' = R \cdot (Q_1^2 + 1) = 40 \cdot (10^2 + 1) = 4.04K\Omega$$

$$Q_2 = \pm \sqrt{\frac{R'}{R_{IN}}} - 1 = \pm \sqrt{\frac{4.04K}{200}} - 1 = \pm 4.382$$

$$X_1 = Q_1 \cdot R - X = 10 \cdot 40 + 20 = 420\Omega$$

$$X_2 = \frac{-R'}{Q_1 + Q_2} = \frac{-4.04K}{10 + 4.382} = -280.907\Omega$$

$$X_3 = Q_2 \cdot R_{IN} + X_{IN} = 4.382 \cdot 200 - 10 = 866.4\Omega$$

This network and the other three possible networks for the given  $Q_1$  value, can be seen in Figure 3.12.

Figure 3.12 – Four Possible Networks for  $|Q_1|$ =10

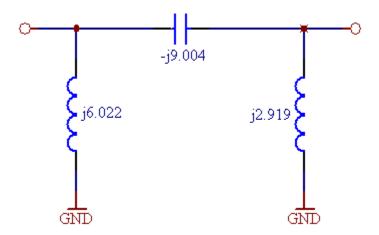

The equivalent  $\Pi$  – Network for the one calculated previously was obtained using a Y –  $\Delta$  transformation and can be seen in Figure 3.13.

Figure 3.13 – Equivalent  $\Pi$  – Network

Using the equations outlined in Subsection 3.3.2, the values of  $Q_1$  and  $Q_2$  were calculated. The following table illustrates the results.

Table 3.2 – Comparison of T – and  $\Pi$  – Network Q-values

| Network                | Value of Q <sub>1</sub> | Value of Q <sub>2</sub> |

|------------------------|-------------------------|-------------------------|

| Calculated T – Network | 10                      | 4.382                   |

| Converted ∏ − Network  | -16.637                 | -33.360                 |

The preceding table shows that the values of Q for a converted network do not match the original network. It should be advised that in applications where bandwidth must be specified specifically, the two networks, T and  $\Pi$ , need to be calculated independently to avoid potential problems.

#### 3.3 $\Pi$ – Network

The  $\Pi$  – Network is very similar to the T – Network. Figure 2.8 shows an example of a  $\Pi$  – Network. There are two ways to obtain this network. The T – Network can be calculated and then converted to the  $\Pi$  – Network using the Y –  $\Delta$  transformation outlined in Section 2.3. The  $\Delta$  – Y transformation works for calculating the T – Network from the  $\Pi$  – Network as well. In either case, the Q-values will not remain constant. For more details, refer to Example 4 in the preceding subsection. Also, the equations presented in the following subsections can be used to directly obtain the values for the  $\Pi$  – Network.

Figure 3.14 – Example of a  $\Pi$  – Network

As with the T – Network, the  $\Pi$  – Network must always have a maximum Q-value greater than or equal to that of the L – Network [3]. Also like the T – Network, the  $\Pi$  – Network has four possible network configurations for a given bandwidth. For more information, refer to Section 3.2.

The  $\Pi$  – Network has an advantage over the T – Network. It only contains one floating element while the T – Network has two. This means that the parasitic effects will be less for the  $\Pi$  – Network. This will be discussed in more detail in Section 4.3.

#### 3.3.1 Downward Transformation

The downward transformation is performed with both the load and the output impedance of the driving stage in the parallel format. Again, the series to parallel conversion was explained in Section 2.3. As with the T – Network, the added degree of freedom requires one variable to be chosen. The downward transformation equations are given below [3].

$$Q_1 = \pm \sqrt{\frac{R}{R'} - 1} \tag{3.19}$$

$$Q_2 = \pm \sqrt{\frac{R_{IN}}{R'} - 1} \tag{3.20}$$

$$X_1 = \frac{-X \cdot R}{Q_1 \cdot X + R} \tag{3.21}$$

$$X_2 = R' \cdot (Q_1 + Q_2) \tag{3.22}$$

$$X_{3} = \frac{X_{IN} \cdot R_{IN}}{R_{IN} - Q_{2} \cdot X_{IN}}$$

(3.23)

Here, R, X,  $R_{\mathit{IN}}$ , and  $X_{\mathit{IN}}$  are in the parallel form and  $R' < R \& R_{\mathit{IN}}$ .

There is a special case when the input or output reactance is not present. Because the input and output impedances are in the parallel format, this corresponds to an infinite reactance. The

equations for  $X_1$  and  $X_3$  given previously are no longer valid since the equations yield some form of infinity in both the numerator and denominator. For these situations, the following equations should be substituted for those given above.

For  $X \to \infty$ :

$$X_1 = -\frac{R}{Q_1} \tag{3.24}$$

For  $X_{IN} \rightarrow \infty$ :

$$X_3 = -\frac{R_{IN}}{Q_2} \tag{3.25}$$

Unlike the resistive transformation for the T – Network, the  $\Pi$  – Network first transforms the resistance downward and then upward to the desired value. This can be seen in the following figure [3].

Figure 3.15 – Downward Resistive Transformation

This transformation is shown in detail by the problem presented in the following example.

# Example 5:

It is desired to match an on-chip 200-ohm resistor in parallel with a 1pF capacitor to a 50-ohm source impedance at 915MHz. There is a 14.7nH inductor layout available. Let  $X_2$  equal this value to minimize the layout time. Use a Monte Carlo sweep with component tolerances at  $\pm$  15% to show how the networks performance changes as its components change value. Assume that the load and source impedances are constant at the given values.

## **Solution:**

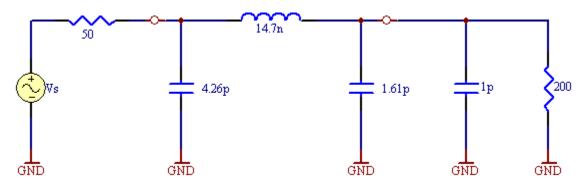

Because the value of  $X_2$  is given, the equations given in this subsection will need to be manipulated. Before this can be done, the impedances must be in the proper form. The  $\Pi$  – Network requires the source and load impedances in the parallel format. The load is specified in the parallel form, and the source impedance is in both the series and parallel form since there is no reactive term. Using Equations 3.19-3.25, the following values can be calculated.

$$X_2 = 14.7nH \rightarrow 84.5\Omega$$

$R' = 20\Omega$

$Q_1 = \pm 3$

$Q_2 = \pm 1.225$

$X_1 = -108.098\Omega \rightarrow 1.61pF$

$X_3 = -40.816\Omega \rightarrow 4.26pF$

Figure 3.16 – Complete Circuit Diagram for Positive Q-values

The completed design using positive Q-values can be seen in Figure 3.16. The peak load power versus frequency was plotted in a Monte Carlo simulation to observe the effects of the component tolerances on the performance of the network. The results can be seen in the following graph.

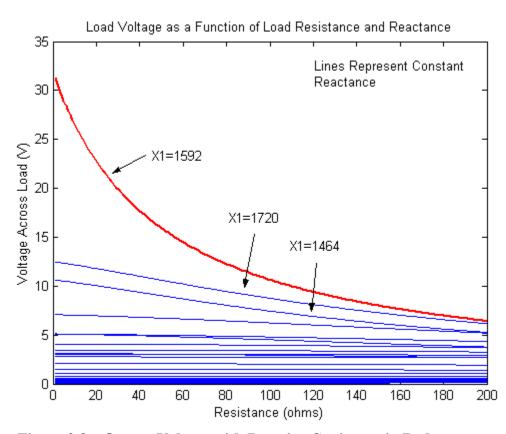

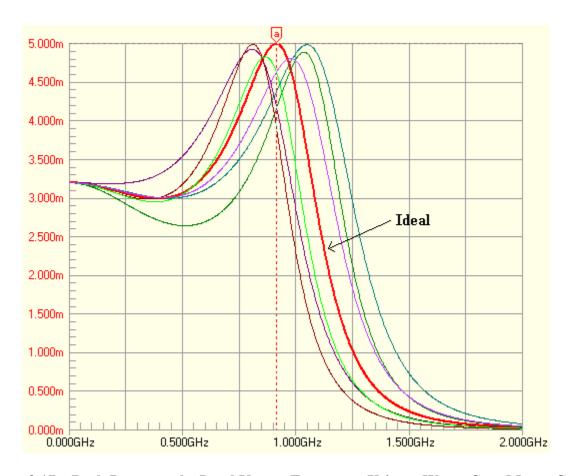

Figure 3.17 – Peak Power at the Load Versus Frequency Using a Worst Case Monte Carlo Sweep with the Ideal Case Shown in Red

As this graph shows, the ideal network provides exact matching allowing the maximum instantaneous power of 5mW to be received at the load. The graph also shows six worst-case examples of the AC power sweep. It can be seen that the maximum error is approximately 20% for this example.

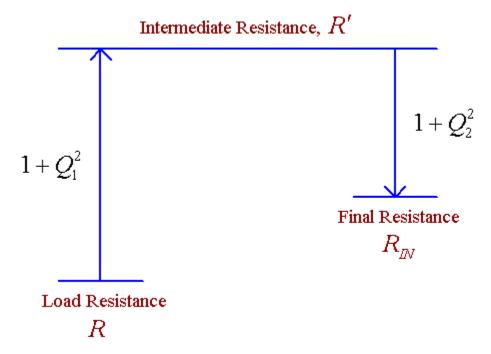

# 3.3.2 Upward Transformation

The upward transformation is also performed with the output and load impedances in the parallel format. The equations for the upward transformation are the same as the downward transformation equations (3.19-3.25).

The resistive transformation graph for the upward transformation can be seen in the following figure [3]. In this case,  $Q_2$  will be greater than the value of  $Q_1$  because the second transformation performs a larger resistive jump.

Figure 3.18 – Upward Resistive Transformation

An example of the  $\Pi$  – Network upward transformation can be seen below.

# Example 6:

Repeat Example 2 to obtain a  $\Pi$  – Network with positive Q-values. Use the minimum value for  $Q_2$ . The given impedances are in the series format.

#### **Solution:**

Using the equations described in this subsection, the following values can be verified.

$$Q_2 = 1.735$$

$Q_1 = 0$

$R' = R_{IN}$

$X_1 = 20.016\Omega$

$X_2 = 86.849\Omega$

$X_3 = -53.611\Omega$

#### 3.4 Wideband Four-Element Networks

Wider bandwidths can be obtained using a four-element impedance matching network. The four-element network is similar to two cascaded L – Networks that were described in Section 3.1. The objective of this section is only to indicate that wider bandwidths can be obtained using different networks. The addition of the fourth element contributes another component tolerance along with more parasitics, which degrade the on-chip performance to an extent that the network would cause more error than it would correct. For off-chip matching networks, more information can be obtained in [3].

#### 3.5 Summary

The preceding sections explained the multiple configurations that can be used for impedance matching. Each network has advantages and disadvantage for specific applications. It is up to the analog designer to pick the network that will have the best performance. Within each topology, there is also the choice of multiple networks because of positive and negative Q-values. Along with this, the three element networks have an infinite number of possible networks, which are obtainable by varying the network bandwidth. All of these possibilities must be evaluated to produce a high-quality matching network.

#### 4.0 ON-CHIP LAYOUT AND CONSIDERATIONS

Designing impedance matching networks requires knowledge about each individual component and how they affect the network's performance. This section describes ways to model each component (L or C) with an equivalent circuit so that the principles from the following section can be applied to designing matching networks. The following components were laid out using the AMI Semiconductor ABN Process with a 1.5-micron minimum feature size. The software package was Cadence Virtuoso.

#### 4.1 Inductors

#### **4.1.1 ASITIC**

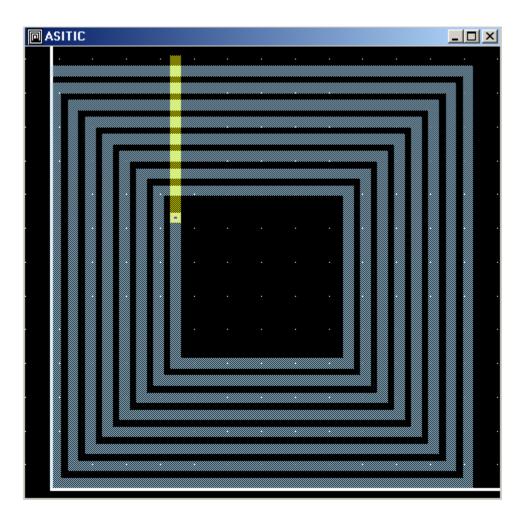

Analysis and Simulation of Spiral Inductors and Transformers for Integrated Circuits (ASITIC) is a software package developed at the University of California at Berkley that aids in the design of on-chip spiral inductors. ASITIC allows a structure to be laid out and simulated. The output will give an equivalent two-port network that will be discussed in more detail in Subsection 4.3.1. An example input file can be seen below.

```

Buffers Files Tools Edit Search Mule Help

del a

SQ NAME=A:LEN=250:WID=250:W=6.1:S=4:N=8

:METAL=M2:EXIT=M1:XORG=0:YORG=0:ORIENT=0.00:PHASE=1

ind a .915

--(DOS)-- 14p7nH.run (Fundamental)--L7--All-

```

Figure 4.1 – Example ASITIC File for a 14.7nH Inductor

The "del" command deletes the spiral with the following name. In this case, the spiral name is "a". This line is not needed but is included to be sure the spiral named "a" has been cleared. The next line lists the program variables. An explanation of these variables can be seen in the following table. The final line gives a two-port equivalent circuit along with the inductance of spiral "a" at a frequency of 0.915GHz.

**Table 4.1 – ASITIC Variable Explanations**

| Variable                                                 | Description                            |

|----------------------------------------------------------|----------------------------------------|

| SQ NAME                                                  | -name of square spiral                 |

| LEN                                                      | -outer dimension in X direction        |

| WID                                                      | -outer dimension in Y direction        |

| W                                                        | -width of trace                        |

| S                                                        | -spacing between traces                |

| N                                                        | -number of turns in 0.25 increments    |

| METAL                                                    | -inductor is wound on this layer       |

| EXIT                                                     | -center connection exits on this layer |

| XORG                                                     | -X origin on chip                      |

| YORG                                                     | -Y origin on chip                      |

| ORIENT                                                   | -angle of inductor layout              |

| PHASE                                                    | -specifies positive terminal           |

| For more in-depth details, visit the ASITIC website. [5] |                                        |

The output of this file can be seen in Figure 4.2.

```

## pitteda4.ee.pitt.edu - PuTTY

ASITIC>

ASITIC> ind a .915

Pi Model at f=0.92 GHz: Q = 2.39, 2.43, 2.70

L = 14.7 nH R = 28.1

Cs1= 268 fF Rs1= 128

Cs2= 270 fF Rs2= 92.2 f_res = 3.00GHz

A: at 0.915000 GHz L = 14.7492 (nH).

ASITIC>

```

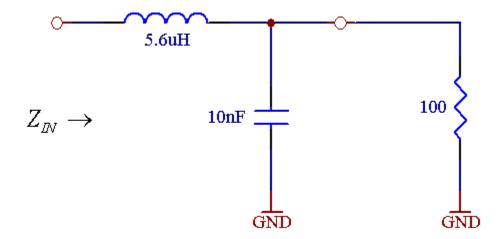

Figure 4.2 – ASITIC Output for 14.7nH Inductor

ASITIC returns the equivalent circuit and the inductance at the specified frequency, which is 0.915GHz in this case. It also plots the given inductor for visual inspection. The 14.7nH square spiral can be seen in the following figure.

Figure 4.3 – ASITIC Graphic Output of 14.7nH Inductor

# 4.1.2 Current Sheet Approximation

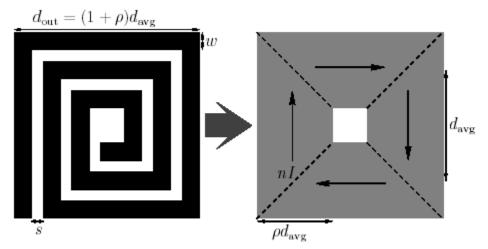

The current sheet approximation is another way to analyze inductors. The square spiral is approximated as a solid plane like the one given in the following figure. The following figure and equations were presented by S. S. Mohan from Stanford University in his Ph.D. Oral Examination [6].

Figure 4.4 - Spiral Approximated as a Solid Sheet

The inductance of a spiral is given by the following expression.

$$L_{SQ} = \frac{2 \cdot \mu \cdot n^2 \cdot d_{avg}}{\pi} \left[ \ln \left( \frac{2.067}{\rho} \right) + 0.178 \cdot \rho + 0.125 \cdot \rho^2 \right]$$

(4.1)

where

$$\rho = \frac{d_{out} - d_{in}}{d_{out} + d_{in}} \tag{4.2}$$

$d_{out}$  &  $d_{in}$  are the outside and inside diameter from side to side, respectively. For tightly wound spirals,  $d_{in} \approx 0$  which makes  $\rho \approx 1$ . "n" is the number of turns in the spiral while " $\mu$ " describes the overall permeability.

Using this method for the 14.7nH inductor designed using ASITIC yields the following values.

$$d_{out} = 250 \mu m$$

$$d_{in} = 96.4 \mu m$$

$$d_{avg} = 173.2 \mu m$$

$$\rho = 0.4434$$

Assuming  $\mu \approx \mu_o = 4 \cdot \pi \cdot 10^{-7}$  yields

$$L_{SO} = 14.569nH$$

This value is extremely close to the results of 14.7nH obtained using ASITIC. One drawback of this method is the lack of parasitic knowledge. ASITIC provides an equivalent two-port network to aid in design while this method simply gives the inductance value. For this reason, all of the impedance matching inductors were laid out using ASITIC. The current sheet approximation is very useful in other applications since it is much quicker than designing with ASITIC.

# 4.2 Capacitors

## 4.2.1 Typical

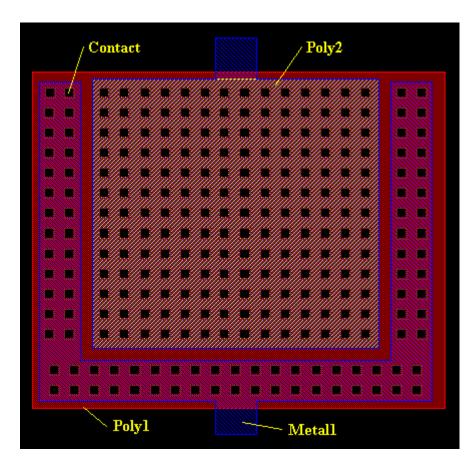

There are numerous ways to layout a capacitor on an integrated circuit. These layouts will depend on the process being used. The capacitors described in this subsection were created using a poly-to-poly layout. Poly1 is used as the bottom plate while poly2 acts as the upper plate. Metal1 is used to connect to both the top and bottom plates. This is easily seen in the following layout.

The layouts provided in the subsequent figures are by no means unique. However, they do incorporate the fundamentals of design that are needed for radio frequency matching capacitors. The main goal of the layouts is to provide a basis that can be extended to individual designs.

Figure 4.5 – Typical 1pF Capacitor Layout

The previous figure shows how metal1 can directly connect to poly2 using contacts. In order for metal1 to connect to poly1, the poly1 sheet must be stretched from underneath poly2 to allow the contacts to drop from the metal1 layer all the way to poly1. The capacitance is dictated by the overlap of poly1 and poly2. For the ABN AMI process, the capacitance is given by  $584aF/um^2$  [7].

For impedance matching networks, it is very important to minimize the loss in the matching components. This is done by keeping the series resistance as small as possible. As explained above, the plates of the capacitor are formed with polysilicon. For the ABN AMI process, the sheet resistance for poly1 and poly2 are  $23.3\Omega/\Box$  and  $21.4 \Omega/\Box$ , respectively. There is also a contact resistance between a polysilicon layer and a metal layer. For this process, the poly1-metal1 contact resistance is  $27.6\Omega$  while it is only  $14.7\Omega$  for a poly2-metal1 connection [7].

These resistances add considerable series resistance to the capacitor layout. To minimize this value, fingers are used to provide parallel resistive paths.

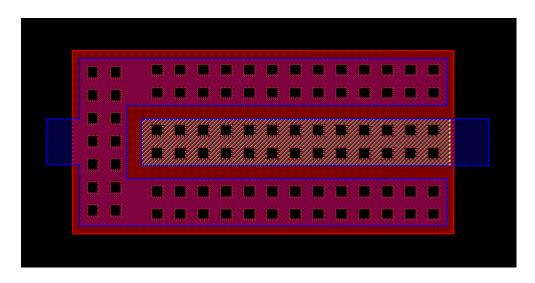

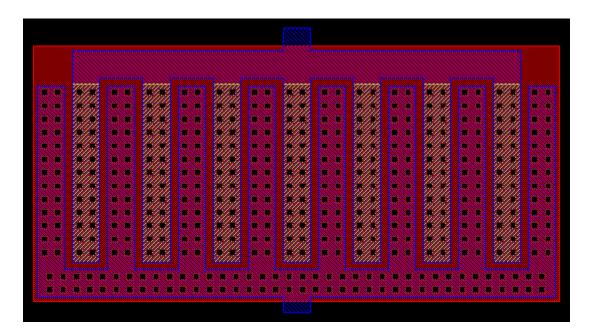

## 4.2.2 Fingers

On a typical square capacitor, the top plate will have little resistance because metal1 can contact the plate everywhere. However, the bottom plate is only connected to metal1 on the outside. Since there are no connections from poly1 to metal1 in the center of the capacitor, a large resistance is seen between the actual dielectric and metal trace. This can be seen in Figure 4.5.

To reduce this resistance, the capacitor needs to be rectangular. Figure 4.6 shows an example of a rectangular capacitor.

Figure 4.6 – Rectangular Capacitor

It can easily be seen that the resistance is minimized when the fingers are at minimum feature size. Using the minimum size gives the minimum resistance, but it also gives the minimum capacitance for a given area. Most of the area is required for the spacing between the fingers. By doubling the minimum feature size to a double row of contacts, the capacitance is doubled without a significant increase in resistance. The spacing between fingers, however, remains at minimum feature size. A layout using this technique can be seen in Figure 4.7.

**Figure 4.7 – Double Row of Contacts**

By placing multiple fingers in parallel, a coarse value can be obtained. To acquire the exact value, the length of the fingers must be adjusted. An example layout can be seen in Figure 4.8.

Figure 4.8 – 1pF Capacitor Layout

#### 4.3 Parasitics and Tolerances

# 4.3.1 Equivalent Circuits

As with all components, the inductor and capacitor layouts shown previously are not merely described by ideal components. There will be an equivalent circuit used to represent the component at a particular frequency. These parasitic effects, in general, degrade the performance of the component, which in turn degrades the entire impedance matching network. If the effects become too great, the network will cause more reflection in the case of radio frequency networks than the original unmatched circuit. For this reason, the parasitics of the components must be understood and minimized to insure the least amount of error.

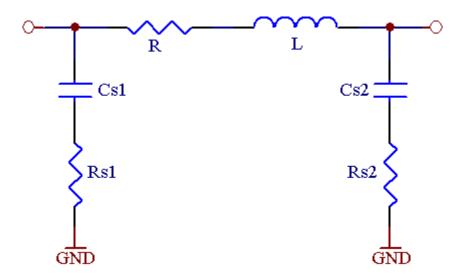

ASITIC calculates an equivalent circuit for a specified inductor layout. More information on ASITIC can be found in Subsection 4.1.1. The two-port equivalent of an on-chip inductor layout can be seen in Figure 4.9 [5].

Figure 4.9 – ASITIC Two-port Equivalent Circuit for an Inductor

The values for the variables seen in Figure 4.9 are given in an ASITIC output file. An example output file can be seen in Figure 4.2. This circuit directly replaces the fabricated inductor in the matching network. For cases where Cs1 and Rs1 or Cs2 and Rs2 are small, as is the case for the 14.7nH layout in Subsection 4.1.1, they can typically be ignored if the other components in the matching network have comparably larger impedances. This can be seen more easily by

converting Cs1 and Rs1 to their parallel form, Cp1 and Rp1. The value of Rp1 becomes  $3.42K\Omega$  while Cp1 is approximately equal to Cs1. Since Rp1 is large, it can be neglected for most networks, which are usually operating around fifty ohms. This leaves only Cp1, or Cs1 because the values are similar. Neglecting this value will depend on the network's components and configuration.

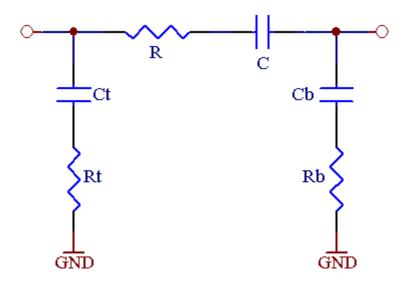

Capacitors have a very similar equivalent circuit as can be seen in Figure 4.10.

Figure 4.10 – Capacitor Equivalent Circuit

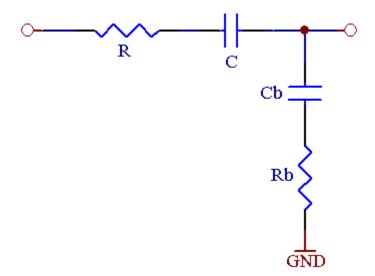

As described in Subsection 4.2.1, the capacitors used for the tested matching networks were formed using the poly1 and poly2 layers. Because the poly2 layer is above the poly1 layer and the poly1 sheet is larger to accommodate the metal1 connections, the top plate will have very little coupling to the substrate. This means the capacitor and resistor to ground associated with the top plate can be neglected as long as no traces are run over the top of the capacitor layout [8]. The simplified circuit can be seen in Figure 4.11.

Figure 4.11 – Simplified Capacitor Equivalent Circuit

The parasitic branch associated with the bottom plate will be dependant on the area of poly1. The poly1 to substrate coupling is around 37aF/um² [7]. As was explained for the inductor, the resistance value, Rb, can generally be neglected because of its large parallel value. The circuit can be simplified even more when the capacitor has a grounded terminal. The bottom plate of the capacitor can be run to ground which eliminates the other parasitic branch leaving only the series resistance, R. To minimize the value of R, the capacitor can be laid out using the finger technique described in Subsection 4.2.2. Using this method, the value of R can be minimized to a value that can be neglected leaving only the desired capacitance.

Obviously, the bottom terminal of the capacitor cannot always be grounded. In these cases, the analysis must take into account the additional elements, and the performance of the component will be degraded.

## 4.3.2 Effects on Ideal Networks

Impedance matching networks are never ideal. Even with discrete components, there are tolerances associated with each element. There is also the problem of choosing standard values. On-chip networks do not have this problem because any reasonable value can be fabricated which would again have some tolerance. The main problem, as described in this subsection, is parasitic effects caused by the substrate. In either case, the network performance will be

degraded to some extent. These effects must be considered to determine if the network will cause more mismatch in the circuit than it corrects.

#### 5.0 IMPEDANCE MATCHING SOFTWARE

#### **5.1** Software Functions

The calculation of impedance matching networks can be time consuming and monotonous. For this reason, software was created to speed the process. The purpose of the software is to combine the ideal networks presented in Section 3.0 with the parasitics caused by the common substrate. The program was written in C++. The source code is included in Appendix C. The first function of the software is to allow a choice among multiple topologies each having a variety of selections. These selections are created using positive and negative Q-values. The user is then asked to enter the parasitic values as described in Section 4.3. These values can be taken from ASITIC or can be calculated using the process parameters. The program uses these values to calculate the total power transferred and the power lost. The program also separates the lost power into categories so the dominant effect can be identified. In most cases, it will be the series resistance in the network's inductors. These resistances tend to be high due to the low quality factors of inductors formed on a silicon substrate [9]. Finally, the program will make a decision on whether the network should or should not be used by comparing the power received with and without the network. If the network is too lossy, more power is received without the matching network than when it is used.

## 5.2 Software Example for a Fabricated Network

To better illustrate the performance of the impedance matching software, a fabricated network from Section 6.2 was entered into the program. Since the program returns results for the L-, T-, and  $\Pi-$  Networks, it was possible to verify the fabricated L- Network and one of the  $\Pi-$  Networks in a single run of the program.  $\Pi-$  Network (1) was chosen for the sample given below. For a step-by-step explanation of the program, the display window has been split into various sections with a description following each.

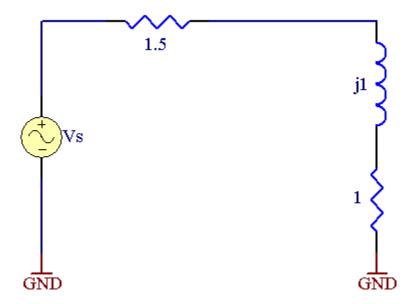

The user is first asked about the circuit's form. For the fabricated networks, the load was in the parallel form, so the choice was "n" for no.

```

If Xin or Xout is absent, enter a zero for its value. The zero is a placeholder and does not necessarily mean zero reactance.

What impedances are in parallel?

Input only — type 'i'

Output only — type 'o'

Both — type 'b'

Answer o

```

Next, the program informs the user that an absent reactance must be specified as a zero even though it may be infinite. This is required for calculation purposes since infinity cannot be entered. An "o" is entered to specify that that the output impedance is in the parallel form.

```

Rin = 50

Xin = 0

Enter output parallel resistance 200

Enter output parallel reactance -173.940

Frequency (MHz) = 915

```

The user is then prompted to enter the source and load impedances in ohms. The frequency of operation is also entered.

Because the L – Network does not have a degree of freedom, the two possible matching networks are returned. The first network, labeled A, has a positive Q while network B has a negative Q-value. A and B will be used later in the program to specify which network will be used.

```

- Network

1 X3 1

: X1 !--

1X2 1

GND

| 192 | must be >= to 0.850051

Enter |Q2| value 1

Is a \{01\} of 0.401304 acceptable? (y/n) y

-- T-Network 1 - Postive Q1, Positive Q2

j(133.597) is an inductor - 2.32379e-008 H

j(-71.3621) is an capacitor - 2.43743e-012

j(50) is an inductor - 8.697e-009 H

- T-Network 2 - Negative Q1, Positive Q2

j(64.4693) is an inductor – 1.12138e-008 H

j(-167.03) is an capacitor – 1.04137e-012 F

j(50) is an inductor – 8.697e-009 H

E--- T-Network 3 - Postive Q1, Negative Q2

j(133.597) is an inductor - 2.32379e-008 H

j(167.03) is an inductor - 2.90531e-008 H

j(-50) is an capacitor - 3.4788e-012 F

-- T-Network 4 - Negative Q1, Negative Q2

4693) is an inductor - 1.12138e-008 H

3621) is an inductor - 1.24127e-008 H

) is an capacitor - 3.4788e-012 F

(-50) is an capacitor

```

The T – Network is calculated next. Because it has one degree of freedom, a variable must be chosen. This program allows the user to choose the magnitude of  $Q_2$ . The program also displays the minimum value of  $Q_2$ . Generally the designer will pick the lowest Q-value that provides reasonable component values. A low Q-value is less sensitive to component variations because it has a wider bandwidth.

After a value is entered, the program returns the value of  $Q_1$ , which will always be less than  $Q_2$  for this case. The user is then prompted to accept the value of  $Q_1$ . If the value is not accepted, the program will ask for a new  $Q_2$ . Otherwise, the program will display the four possible matching networks for these Q-values. They are labeled C through F for easy reference later in the program.

```

PI - Network

Zin O

O Zout

IX1 I

1X3 1

GND

GND

|Q1| must be >= to 1.73205

Enter ¦Q1¦ value 6.245

Is a ¦Q2¦ of 3 acceptable? (y/n) y

-- PI-Network 1 - Postive Q1, Positive Q2

j(-39.2528) is an capacitor - 4.43128e-012 F j(46.225) is an inductor - 8.04037e-009 H j(-16.6667) is an capacitor - 1.04364e-011 F

– PI-Network 2 – Negative Q1, Positive Q2

j(27.046) is an inductor – 4.70437e–009 H j(-16.225) is an capacitor – 1.07205e–011

j(-16.225) is an capacitor - 1.07205e-011 F

j(-16.6667) is an capacitor - 1.04364e-011 F

-I---- PI-Network 3 - Postive Q1, Negative Q2

j(-39.2528) is an capacitor - 4.43128e-012 F

j(16.225) is an inductor - 2.82217e-009 H

j(16.6667) is an inductor - 2.899e-009 H

--- PI-Network 4 - Negative Q1, Negative Q2

j(27.046) is an inductor - 4.70437e-009 H j(-46.225) is an capacitor - 3.7629e-012 J j(16.6667) is an inductor - 2.899e-009 H

Would you like to rerun with different Q values (y/n)n

```

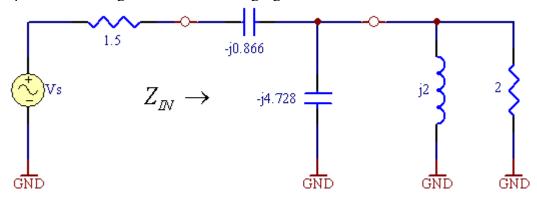

Next, the  $\Pi$  – Network is calculated in the same way as the T – Network. In this case, however,  $Q_1$  must be specified while  $Q_2$  is calculated. The designer will again try to find the lowest Q-value that yields reasonable component values. The program then uses these Q-values to return the four possible matching networks, which are labeled G through G. The user now has the option to rerun the program with different Q-values. This will only affect the G – and G – Networks because the G – Network must have the displayed G-value.

The next part of the program is used to characterize the networks performance when fabricated on a semiconductor chip. It uses the equivalent circuits described in Section 4.3 to replace the ideal components with a model that better describes their behavior. This section only calculates

the parasitic effects for one network because there are numerous variables for each element. The network described below will be "G" which is the first fabricated  $\Pi$  – network from Section 6.2.

```

-PARASITIC EFFECTS-

The following calculations will examine the effects of the

substrate's parasitics. For inductors, the parasitic elements can be obtained using the output file from ASITIC. For capacitor to ground, the bottom plate is assume to be run to ground, which minimizes the parasitics. In this case, the parasitic capacitor

In this case, the parasitic capacitor emto farads. The series resistance of

minimizes the parasitics. In this case, the parasitic capacitican be assumed in the low femto farads. The series resistance capacitors can be assumed less than 0.5 ohms if the layout was done using the method outlined in the accompanying paper. For

series resistance of

the bottom plate parasitics can be calculated

floating capacitors,

using the method outlined in the accompanying paper.

Which Network from above are you using? (A/B/C/D/E/F/G/H/I/J) G

Enter the following parameters for the capacitor X1

\langle pF \rangle = 0.1

the following parameters for the inductor X2

= 0.295

(pF) = 0.304

the following parameters for the capacitor X3

= 10.44

= 0.1

```

After specifying the chosen network, the user is asked to enter the parasitic elements for each component. As the program explanation states, these values are outlined in Section 4.3.

```

The old load including the ideal PI — matching network was

Z = 50 + j(-2.55796e-015)

The load including the parasitics of the PI — matching network is

Z = 14.5357 + j(-15.9738)

The input impedance was given or calculated to be

Z = 50 + j(0)

Amount of Maximum Power Transferred —> 65.7723%

```