## A MULTI-GIGABIT NETWORK PACKET INSPECTION AND ANALYSIS ARCHITECTURE FOR INTRUSION DETECTION AND PREVENTION UTILIZING PIPELINING AND CONTENT-ADDRESSABLE MEMORY

by

Jacob J. Repanshek

BS, University of Pittsburgh, 2003

Submitted to the Graduate Faculty of the

School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

University of Pittsburgh

2004

## UNIVERSITY OF PITTSBURGH

## SCHOOL OF ENGINEERING

This thesis was presented

by

Jacob J. Repanshek

It was defended on

September 9, 2004

James T. Cain, Professor, Electrical Engineering Department

Alex Jones, Assistant Professor, Electrical Engineering Department

Thesis Advisor: Raymond R. Hoare, Assistant Professor, Electrical Engineering Department

## A MULTI-GIGABIT NETWORK PACKET INSPECTION AND ANALYSIS ARCHITECTURE FOR INTRUSION DETECTION AND PREVENTION UTILIZING PIPELINING AND CONTENT-ADDRESSABLE MEMORY

Jacob J. Repanshek, MS

University of Pittsburgh, 2004

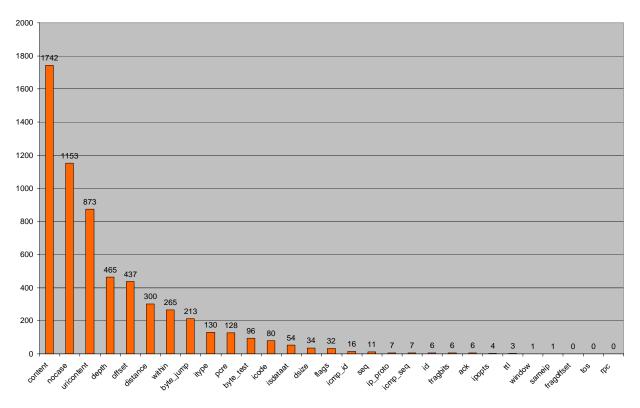

Increases in network traffic volume and transmission speeds have given rise to the need for extremely fast packet processing. Many traditional processor-based network devices are no longer sufficient to handle tasks such as packet analysis and intrusion detection at multi-Gigabit rates. This thesis proposes two novel pipelined hardware architectures to relieve the computational load of a processor within network switches and routers. First, the Embedded Protocol Analyzer Pre-Processor (ePAPP) is capable of taking an unclassified packet byte stream directly off of a network cable at line speed and separating the data into individually classified protocol fields. Second, the CAM-Assisted Signature-Matching Architecture (CASMA) uses ternary content-addressable memory to perform the task of stateless intrusion detection signature-matching. The Snort open-source software network intrusion detection system is used as a model for intrusion detection functionality. Structured ASIC synthesis results show that ePAPP supports speeds of 2.89 Gb/s using less than 1% of available logic cells. CASMA is shown to support 1.25 Gb/s using less than 6% of available logic cells. The CASMA architecture is demonstrated to be able to implement 1729 of 1993 or 86.8% of the attack signatures, or rules, packaged with Snort version 2.1.2.

## TABLE OF CONTENTS

| 1.0 | INTRO | ODUCTION                                           | 1         |

|-----|-------|----------------------------------------------------|-----------|

| 1.1 | IMP   | PORTANCE OF CYBER SECURITY                         | 2         |

| 1.2 | EFF   | FECTS OF INCREASES IN NETWORK TRAFFIC AND TRAN     | SMISSION  |

|     | SPE   | EEDS                                               |           |

| 1.3 | THE   | E NEED TO REDESIGN NETWORK SWITCHES TO FA          | ACILITATE |

|     | INT   | RUSION DETECTION                                   | 5         |

| 1.4 | PAC   | CKET ANALYSIS                                      | 7         |

| 1.5 | USI   | NG CONTENT-ADDRESSABLE MEMORY TO ASSIST IN I       | NTRUSION  |

|     | DET   | TECTION                                            |           |

| 1.6 | OVE   | ERVIEW OF ARCHITECTURE                             | 9         |

| 1.  | .6.1  | ePAPP: An Embedded Protocol Analyzer Pre-Processor |           |

| 1.  | .6.2  | A CAM-Assisted Signature-Matching Architecture     | 12        |

| 2.0 | RELA  | TED WORK                                           | 17        |

| 3.0 | ePAPP | P: AN EMBEDDED PROTOCOL ANALYZER PRE-PROCESSOR     |           |

| 3.1 | INT   | RODUCTION                                          |           |

| 3.2 | ARC   | CHITECTURE FOR PROTOCOL MAPPING                    |           |

| 3.  | .2.1  | Protocol Memory                                    | 24        |

| 3.  | .2.2  | Jump Register and Jump TLB                         |           |

| 3.  | .2.3  | Length Block                                       |           |

| 3.3   | CIRCUIT IMPLEMENTATION OF EPAPP                          |

|-------|----------------------------------------------------------|

| 3.4   | DESIGN RESULTS AND PERFORMANCE                           |

| 3.5   | CONCLUSIONS                                              |

| 4.0 C | ASMA: A CAM-ASSISTED SIGNATURE-MATCHING ARCHITECTURE FOR |

| Ι     | NTRUSION DETECTION                                       |

| 4.1   | THE SNORT INTRUSION DETECTION SYSTEM                     |

| 4.1.1 | 1 Snort Packet Header Rule Options                       |

| 4.1.2 | 2 Snort Packet Payload Rule Options                      |

| 4.1.3 | 3 Snort Post-Match Rule Options                          |

| 4.1.4 | 4 Summary of Snort Rules 50                              |

| 4.2   | TERNARY CONTENT-ADDRESSABLE MEMORY                       |

| 4.3   | PACKET HEADER SEARCHING                                  |

| 4.4   | PACKET PAYLOAD SEARCHING                                 |

| 4.5   | SNORT RULE ENCODING EXAMPLES                             |

| 4.5.2 | 1 Snort Rule Example #1 66                               |

| 4.5.2 | 2 Snort Rule Example #2 67                               |

| 4.5.3 | 3 Snort Rule Example #3 69                               |

| 4.5.4 | 4 Snort Rule Exceptions                                  |

| 4.6   | THE CASMA ARCHITECTURE                                   |

| 4.6.2 | 1 CASMA Data Flow                                        |

| 4.6.2 | 2 CASMA Timing                                           |

| 4.6.3 | 3 CASMA Testing Methodology                              |

| 4.6.4 | 4 CASMA Technology Mapping Results                       |

| 5.0 CONCLUSIONS AND FUTURE DIRECTIONS    |  |

|------------------------------------------|--|

| APPENDIX A                               |  |

| VHDL CODE FOR THE ANALYZER_TOP ENTITY    |  |

| APPENDIX B                               |  |

| VHDL CODE FOR THE ASSEMBLER ENTITY       |  |

| APPENDIX C                               |  |

| VHDL CODE FOR THE JUMP_TLB ENTITY        |  |

| APPENDIX D                               |  |

| VHDL CODE FOR THE LENGTH_BLOCK ENTITY    |  |

| APPENDIX E                               |  |

| VHDL CODE FOR THE PROTOCOL_MEMORY ENTITY |  |

| APPENDIX F                               |  |

| VHDL CODE FOR THE SNORT_CAM ENTITY       |  |

| BIBLIOGRAPHY                             |  |

## LIST OF TABLES

| Table 1. Time to Respond to a Network Packet at Various Peak Transmission Speeds | 4  |

|----------------------------------------------------------------------------------|----|

| Table 2. IP Protocol Field Description                                           | 25 |

| Table 3. UDP Protocol Field Description                                          | 25 |

| Table 4. TCP Protocol Field Description                                          | 25 |

| Table 5. The Protocol RAM Data                                                   | 28 |

| Table 6. The Jump Translation Look-Aside Buffer                                  | 29 |

| Table 7. Current Content Inside Protocol Memory                                  | 32 |

| Table 8. Performance Results After Synthesis                                     | 36 |

| Table 9. Performance Comparison With Software                                    | 37 |

| Table 10. Example Rule Header Table Format                                       | 42 |

| Table 11. Rule Header Example #1                                                 | 43 |

| Table 12. Rule Header Example #2                                                 | 43 |

| Table 13. Rule Header Example #3                                                 | 44 |

| Table 14. Rule Header Example #4                                                 | 44 |

| Table 15. Snort Rule Header and Body Example #1                                  | 45 |

| Table 16. Non-Payload Rule Options                                               | 46 |

| Table 17. Payload Rule Options                                                   | 47 |

| Table 18. Snort Rule Header and Body Example #2                                  | 49 |

| Table 19. Meta-data Rule Options                                                 | 50 |

| Table 20. Post-detection Rule Options                                             | 50 |

|-----------------------------------------------------------------------------------|----|

| Table 21. Protocol Header Fields Included in a Header Search CAM Entry            | 55 |

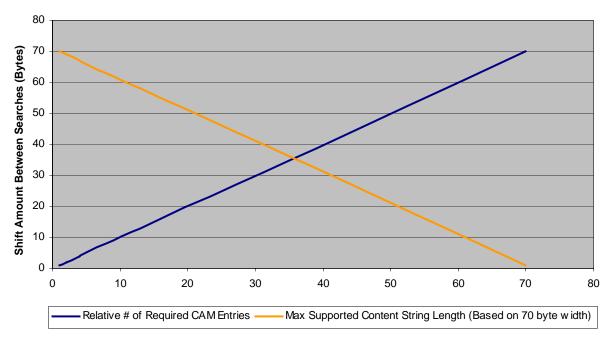

| Table 22. Effects on Time and Space Requirement for Varying Payload Shift Amounts | 59 |

| Table 23. Test Packet #1                                                          | 77 |

| Table 24. Test Packet #2                                                          | 81 |

| Table 25. Performance Results After Synthesis                                     | 85 |

# LIST OF FIGURES

| Figure 1. Typical Network Before and After Infection from a Malicious Email Attachment 1   |

|--------------------------------------------------------------------------------------------|

| Figure 2. Network Incorporating Routers and Switches with Packet Inspection Capabilities 2 |

| Figure 3. Overview of the Presented Architecture                                           |

| Figure 4. Traditional Network Switch Architecture                                          |

| Figure 5. Network Switch Augmented with the ePAPP and CASMA Architectures                  |

| Figure 6. The Protocol Analyzer Pre-Processor                                              |

| Figure 7. An Example of a Layered Protocol Description                                     |

| Figure 8. The Internal Architecture of the Protocol Analyzer Pre-Processor                 |

| Figure 9. Simulation Waveform for ePAPP                                                    |

| Figure 10. Number of Occurrences of Each Option in the Entire 1,993-Rule Snort Ruleset 51  |

| Figure 11. Example of a Search on a Populated CAM                                          |

| Figure 12. Shift Amount Between Searches vs. CAM Entries Required 59                       |

| Figure 13. Position of CASMA in the Presented Switch Architecture                          |

| Figure 14. Internal Circuit Design of the CAM-Assisted Signature-Matching Architecture 74  |

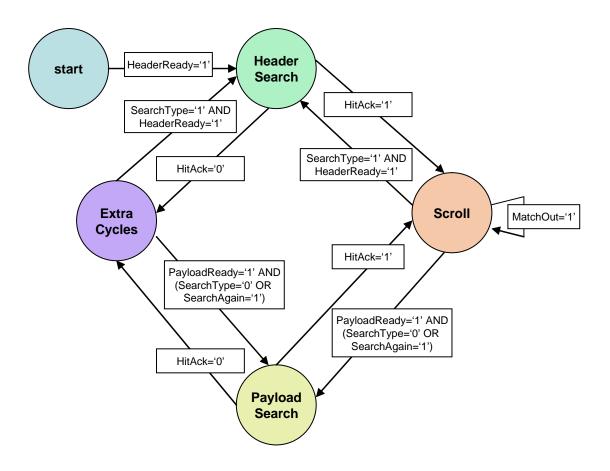

| Figure 15. Flow of the Controller State Machine                                            |

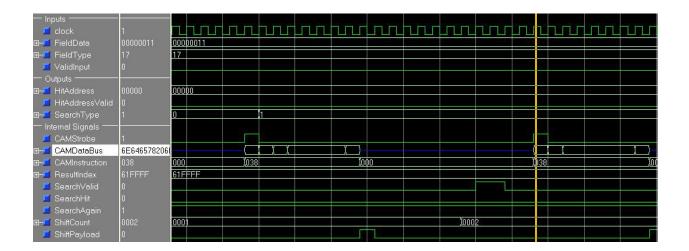

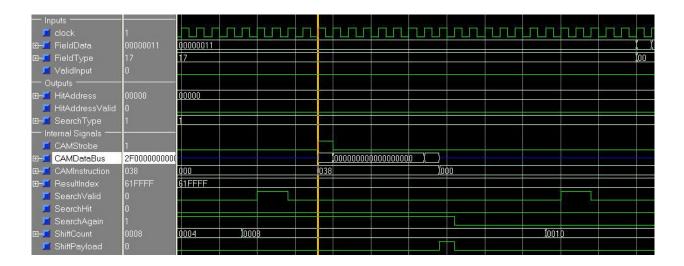

| Figure 16. Header Searching Beginning for Test Packet #1                                   |

| Figure 17. Payload Searching Beginning for Test Packet #1                                  |

| Figure 18. Payload Searching Concluding for Test Packet #1                                 |

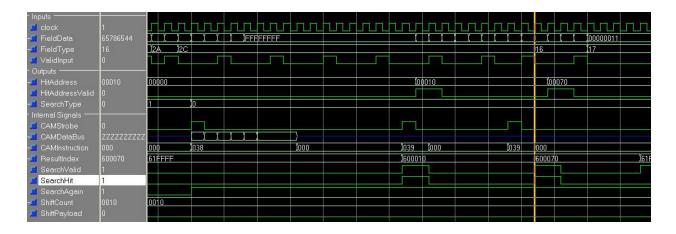

| Figure 19. Header Searching Beginning for Test Packet #2                                   |

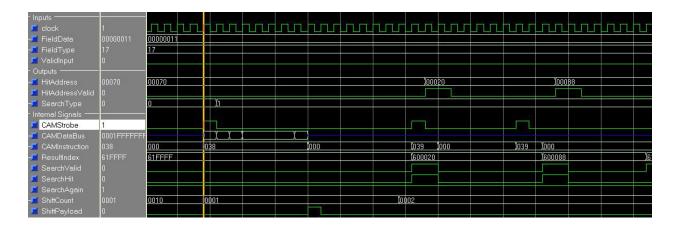

| Figure 20. Payload Searching Beginning for Test Packet #2  | . 83 |

|------------------------------------------------------------|------|

| Figure 21. Payload Searching Concluding for Test Packet #2 | . 84 |

## **1.0 INTRODUCTION**

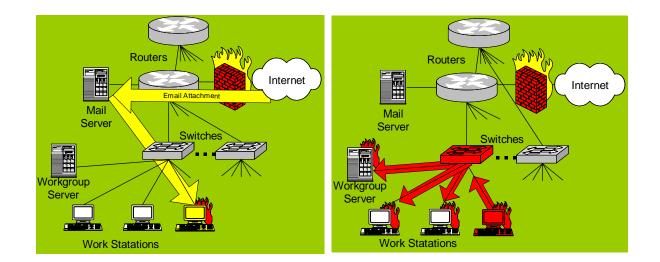

There are few areas in the contemporary computing technology industry that have received as much attention as cyber security. Rapidly increasing network transmission speeds have marked the computationally heavy task of network packet inspection as a conspicuous bottleneck in the processing and forwarding of information across the network. The need for this function, however, cannot be ignored. Consider the typical local network pictured in Figure 1. Once an infected email attachment has entered the network, there is no protection in a typical switch or router to stop the spread of malicious behavior.

Figure 1. Typical Network Before and After Infection from a Malicious Email Attachment

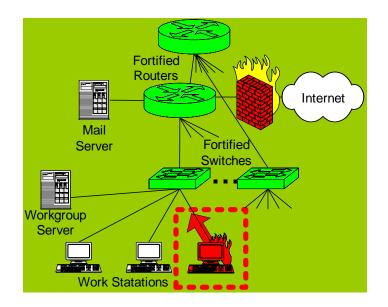

Now consider the network in Figure 2. The routers and switches in this network have been fortified, which is to say they are capable of detecting and dropping malicious traffic. Even if a single host on the network becomes infected, in this example by an email attachment, the attack will not be allowed to spread.

Figure 2. Network Incorporating Routers and Switches with Packet Inspection Capabilities

This research has developed a packet classification and intrusion detection methodology that will demonstrate performance advantages over comparable conventional solutions and allow for incorporation into high-speed network devices such as switches. This chapter clarifies the need for such a solution and introduces the challenges of cyber security, with particular respect to packet classification and intrusion detection. Snort [21], an open-source intrusion detection software solution, is introduced as a benchmark against which this original work is compared.

### **1.1 IMPORTANCE OF CYBER SECURITY**

The most evident indication of the importance of cyber security is the staggering amount of money industry must devote to it. The market research firm IDC predicts that a total of \$14

billion will be spent for companies and organizations to protect themselves from network attacks by 2005, an increase from \$5 billion in 2000 [2]. Furthermore, IDC predicts that the Intrusion Detection market (including Vulnerability Assessment) alone will have total revenue of more than \$1 billion in 2003, with a Compound Annual Growth Rate of 34% during 1999-2004 [3, 4, 5].

These numbers do not seem so unwieldy when one considers that a single malicious attack, the Code Red worm, caused \$2.62 billion in losses worldwide [6]. In one poll of primarily large corporations and government agencies, 80% acknowledged financial loss due to computer breaches [7].

Network intrusion can be defined as "any set of actions that attempt to compromise the integrity, confidentiality, or availability of a resource" [8]. As the financial figures show, cyber intrusions have created a serious problem that continues to grow. In the past ten years, the technical skills required to launch a successful network attack have decreased significantly, while the sophistication of such attacks has grown [9, 10]. Despite these facts, companies continue to migrate important information and resources to the Internet for reasons of accessibility [9].

## **1.2 EFFECTS OF INCREASES IN NETWORK**

### TRAFFIC AND TRANSMISSION SPEEDS

In order to ensure the security of a network, every packet sent or received must be considered potentially harmful until proven otherwise. But as network traffic loads become heavier and transmission speeds increase, it becomes more difficult to adequately inspect every bit of information that passes through a network. The Internet, for example, has seen a spectacular annual growth factor of 4- to 10-times in traffic volumes [1]. Such rapid rates of growth have created a great deal of interest in expanding network transmission bandwidth and increasing transmission speed. As a result, 10 Mb/s networks have been replaced by 100 Mb/s, 1 Gb/s, and even 10 Gb/s networks. With the rise of optical technology, network speeds on the order of 1 Tb/s have been developed and are expected to eventually reach a theoretical limit of about 50 Tb/s [1]. While these developments are exciting for network technology, they have created in their wake another problem for modern networks.

As the speeds of local networks increase, the amount of time available for a network device (such as a switch) to respond to a single packet decreases. As shown in Table 1, a small 64-byte packet can arrive every 51,200 ns for a 10 Mb/s network under peak traffic loads. This provides ample time to respond to each packet. At 1 Gb/s, however, there are only 512 ns to respond and at 10 Gb/s there are only 51 ns to respond.

|                                    |                                       | ]      | Гіте to Respond (Nan                     | Janoseconds)                    |  |

|------------------------------------|---------------------------------------|--------|------------------------------------------|---------------------------------|--|

| Peak Network<br>Transmission Speed | Max. # of 64 Byte<br>Packets / Second |        | Time Per Snort Rule,<br>given 1700 rules | # of 5 ns<br>Memory<br>Accesses |  |

| 10 Mb/s                            | 19,531                                | 51,200 | 30 ns                                    | 6                               |  |

| 100 Mb/s                           | 195,313                               | 5,120  | 3 ns                                     | <1                              |  |

| Gb/s                               | 1,953,125                             | 512    | .3 ns                                    | 0                               |  |

| 10 Gb/s                            | 19,531,250                            | 51     | .03 ns                                   | 0                               |  |

Table 1. Time to Respond to a Network Packet at Various Peak Transmission Speeds

Consider, now, that we wish to check each of the incoming packets to see if it matches any of an extensive set of attack signatures – patterns found within a packet that could indicate malicious traffic. Snort [8], for example, is a software-based intrusion detection system (IDS) that has over 1700 attack signatures, or rules, that must be compared against each incoming packet. Assuming a memory access takes 5 ns, the execution time per rule we wish to check our packet against drops to 30 ns per rule for 10 Mb/s and to 0.03 ns per rule for 10 Gb/s. Given that a 1 GHz processor requires 1 ns per instruction, this is quite infeasible.

# 1.3 THE NEED TO REDESIGN NETWORK SWITCHES TO FACILITATE INTRUSION DETECTION

There are some who mistakenly believe that cyber security can be achieved strictly by controlling what leaves and enters the private network. One popular solution is a firewall [11], which serves as a gateway between the private network and the outside world. By relying entirely on a gateway, however, a single point-of-failure is created. According to a CSI/FBI security report, 90% of attacks bypass firewalls [7]. Obviously, firewall protection alone is not sufficient. Without any additional protection within the network, one compromised machine could attack other hosts within the enterprise without deterrence.

Even if firewalls and other similar measures were enough to prevent all malicious traffic from entering the network, nothing prevents an attack that is launched from within. Information security surveys consistently report that more than half of all incidents are insider attacks. Many security professionals refer to the "80/20 Rule" to describe the relative probability that a problem was caused by insiders as opposed to outsiders [13]. Some form of internal protection must therefore be provided.

One proposed solution is to let each host tackle the task of intrusion detection individually. Host-based intrusion detection software can be installed on every machine on a network in order to inspect all traffic to and from that host [14]. To be effective, this solutions requires not only that every network device (including laptops and wireless devices) have the IDS software installed, but also that every device is configured properly and safe from being turned off or disabled by an authorized user. In a large enterprise network, the sheer volume of systems to be monitored may make this solution impractical. Furthermore, since only the individual machines and not the network itself are protected, any renegade laptop or wireless device that joins the network can be a source of malicious activity.

It is clear that leaving intrusion detection and prevention to the host is unwise, and that a gateway between the internal network and the outside world is not sufficient protection. There is one network device, however, that resides within the local network and sees all of the traffic traveling to and from a host: the network switch. In fact, many cases exist where malicious traffic within a network is seen only by the attack computer, the victim computer, and the switch that connects them. This makes the switch an ideal location to perform intrusion detection and intrusion prevention tasks.

Network switches, however, tend to see a lot of traffic, often at rapid transmission rates. Some switches attempt to use a monitoring port that sees an aggregate of traffic from all of the other ports on the switch [31]. This is a good solution as long as the aggregate switch bandwidth is less than that of the monitoring port. Under heavy loads, however, the monitoring port may be unable to keep up with all of the traffic coming through the switch. Consider, for example, a 48-port 100 Mb/s switch with a single Gb/s monitoring port. If the switch is only operating at 10% of maximum load, the monitoring port would see (48 x 100) x 0.1 = 480 Mb/s of traffic. This is no problem for the monitoring port. But if the load at the switch increased to 50%, the aggregate switch traffic would reach 2.4 Gb/s, much more than the monitoring port can handle.

#### **1.4 PACKET ANALYSIS**

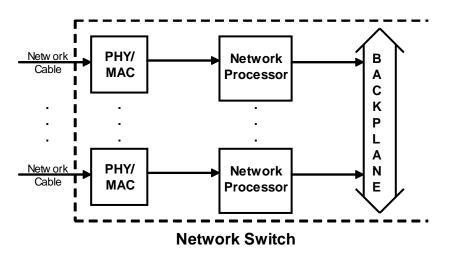

Most network devices, such as switches, rely on network processors to perform packet classification and forwarding. The network processor market has emerged as the fastest growing segment of the microprocessor industry [12]. Most network processors (NPs) utilize multiple channel processors to perform packet inspection and data extraction for each network link, typically using 32- or 64-bit RISC architectures but in some instances using VLIW processors.

One of the most fundamental tasks these network processors perform is *protocol analysis*. This is the process by which individual fields within a packet are classified and the protocols within the packet are identified. RISC processors utilize, by definition, a small subset of instructions that, when combined in a program, can execute complex tasks. The problem is that packet processing requires a large amount of bit manipulation to extract particular data fields. For example, the source and destination of an IP packet are octets 13 through 16 and octets 17 through 20, respectively. For a RISC processor, these fields must be placed in a 32- or 64-bit register before processing can take place. To achieve this protocol analysis task by software can be quite complex just to extract a few fields from a packet header. Many proposed network processors exist which use specialized, non-RISC architectures to support multi-gigabit speeds [15, 16]. These solutions are still constrained by the cycle-rich nature of processor architectures.

Application-specific integrated circuits (ASICs) are used in many network nodes to improve packet-processing speeds, however they are rarely flexible enough for rapid adaptation to protocol or standards changes [1]. However, if one were able to generalize the hardware architecture so that protocol classification information could be periodically updated in a structure such as a ROM, use of ASIC designs would become more feasible.

# 1.5 USING CONTENT-ADDRESSABLE MEMORY TO ASSIST IN INTRUSION DETECTION

Significant research has been done on intrusion detection methodologies. Perhaps the most common approach is signature-based, which is centered on the assumption that intrusion attempts can be characterized by the comparison of user activities against a database of known attacks that lead to compromised system states [17]. Signature-based intrusion detection is the basis for Snort [8], the software IDS solution previously referenced in Table 1. In order to identify potentially harmful packets, Snort must search its ruleset to find any rules that match the packet under inspection. As previously discussed, faster networks and heavy traffic loads make this approach insufficient. Attempts have been made to speedup search times using hierarchical searching and faster pattern matching algorithms [18, 19], however improvements have not been significant enough to handle gigabit network rates.

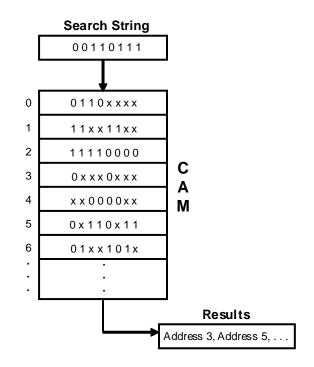

One possible solution to the delays associated with linear rule searching is the use of ternary content-addressable memory. A content-addressable memory (CAM) chip is fundamentally different than a standard RAM. Whereas a standard RAM returns data based on an address given as input, a CAM is capable of returning one or more addresses where the given input search data can be found. A *ternary* CAM is even more beneficial in that it allows for mask bits to be specified so that only a specified portion of the data stored within the CAM needs to match the input data. Most importantly, CAM searches occur in a fixed amount of time, regardless of the amount of data within the CAM itself.

Consider, for example, a 9 Mb Network Search Engine provided by Integrated Device Technologies [20]. This device contains a ternary content-addressable memory (tCAM) that supports 16,000 576-bit entries, all of which can be searched in a fixed amount of cycles. To compare, suppose that 2000 patterns need to be searched and that each pattern is only 32-bits long. Current IDS systems are processor-based and utilize GHz high-performance Pentium processors. We will conservatively assume that all data is located within L1 cache at 1ns per access. Under such assumptions, the pattern matching would require 2000 memory accesses just to read the patterns. Thus, the time-per-packet is 2,000 ns. For a CAM, all 2000 patterns are searched in parallel and the total execution time is 20ns, which is 100 times faster. Now suppose that our patterns are 320 bits wide. This would require 10 times the number of memory references on the part of the processor, making the CAM 1,000 times faster. Clearly, contentaddressable memory has a benefit to the pattern-matching nature of intrusion detection.

### **1.6 OVERVIEW OF ARCHITECTURE**

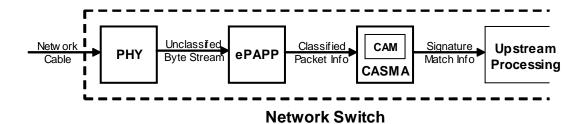

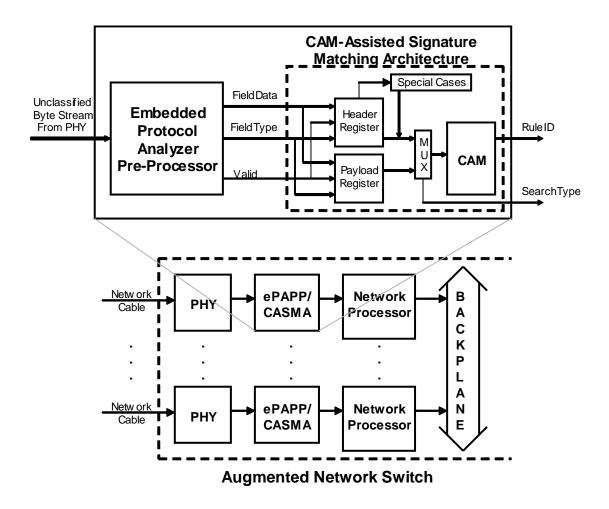

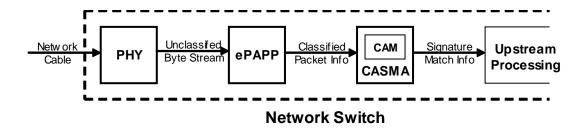

This thesis provides a novel approach to the problems of packet classification and stateless signature-matching to enable intrusion detection. Figure 3 shows an overview of the architecture presented in this thesis. The ePAPP component performs the task of pipelined protocol analysis, while the CASMA component performs stateless intrusion detection signature matching.

Figure 3. Overview of the Presented Architecture

### 1.6.1 ePAPP: An Embedded Protocol Analyzer Pre-Processor

To perform the task of packet classification through protocol analysis, the Embedded Protocol Analyzer Pre-Processor (ePAPP) is presented. ePAPP connects directly to the PHY interface, which is responsible for capturing bits off of the transmission line and outputting them in fixed-width chunks. A 100 Mb/s PHY, for example, produces a 4-bit datapath operating at 25 MHz, while a 1 Gb/s PHY produces an 8-bit datapath operating at 125 MHz. Since the goal of this work is to facilitate protocol analysis at a multi-gigabit switch, ePAPP is optimized to work with an 8-bit datapath. However, a simple 4-to-8-bit shift register can be used to convert a 4-bit stream operating at 25 MHz to an 8-bit, 12.5 Mhz stream, providing support for traditional Fast Ethernet networks.

The goal of ePAPP is to take the unclassified byte stream coming from the PHY and partition and classify the data blocks into corresponding protocol fields. These include header information fields such as source and destination addresses, header and payload sizes, and protocol flags, as well as the payload fields themselves. The partitioned data fields are output on a 32-bit bus, accompanied simultaneously by a unique 8-bit field type to identify not only the field's context (its associated protocol) but also its particular relevance (e.g., source address, payload size, header checksum). Because not all protocol fields are exactly 32 bits in length, field data output is zero-padded as necessary to ensure valid output. Fields that may be larger

than 32 bits in length, such as payloads, are divided and output over the necessary amount of 32bit increments.

While many protocol field types have a fixed length associated with them, others such as payload and optional fields can be of variable lengths. The widths of these fields must be dynamically determined based on information within the protocol header itself. ePAPP is designed to detect and use relevant information within a packet header to calculate and apply these variable widths.

ePAPP utilizes a pipelined hardware architecture to achieve the aforementioned functionality in a fixed number of cycles. Hardware architectures confined to ASIC solutions, however, are typically very static and extremely cost-prohibitive to change. Reconfigurable FPGA solutions are not as inflexible to change, but due to size and cost are ill-suited to implementation in a network device. Therefore, a time-, cost-, and space-efficient protocol analysis solution in hardware must be adaptable to changes in protocol without frequent redesign. To solve this problem, ePAPP uses a "protocol memory" to enumerate possible protocol field types as well as information about the field types themselves. By placing this information in a loadable component, such as a ROM, the functionality of ePAPP can be modified to meet protocol changes without necessitating a complete hardware redesign.

The ePAPP design proposed in this thesis currently supports the following protocols: Ethernet (IEEE 802.3), Ipv4, ARP, TCP, and UDP. While these provided a sufficient base for functional testing and synthesis results, it should be noted that the generalized nature of the ePAPP architecture is expandable to include additional protocols (e.g., ICMP, IPv6) with little more than an addition to the contents of the ROM. Since ePAPP classifies *every field in an incoming packet*, it is adaptable to virtually any application that requires protocol analysis. Its general, multi-use nature makes it quite cost-and space-efficient in a network device. One potential application for ePAPP processing is intrusion detection. Signature-based intrusion detection, in particular, relies on both a wealth of header information and on packet payloads. This thesis utilizes the ePAPP as a tool to present an associated intrusion detection architecture with the information it needs to perform content signature-matching.

### **1.6.2** A CAM-Assisted Signature-Matching Architecture

To perform the task of stateless intrusion detection, this thesis presents a CAM-Assisted Signature-Matching Architecture (CASMA). As previously discussed, the parallel-searching nature of content-addressable memory is a good fit to the search-intensive task of signature-matching. In order to establish the requirements of the CASMA architecture, we chose to use Snort as our model and performance benchmark [21]. As previously mentioned, Snort is open-source network intrusion detection software widely used and supported in industry. While newer versions of Snort are packaged with various pre-processors that provide additional services such as stateful matching, Snort's primary role is rule-based packet signature matching. Stateful inspection considers packets within a larger context that evaluates packets with respect to the current connection state. This requires the storage of connection state information, which is beyond the scope of this work. CASMA has been developed as an attempt to replicate the stateless signature matching capability of Snort in a pipelined hardware solution.

Snort rules are comprised of a number of different elements, including the type of traffic the rule pertains to (IP, TCP, UDP, ICMP), the source and destination addresses and ports for which the rule is valid, and a bevy of rule options (rules and rule options are discussed in detail in Chapter 4). Furthermore, each of these rule options can be classified as pertaining to some characteristic of either packet header information or packet payload information. This gives way to a natural delineation between "header rules" and "payload rules," which is exploited by CASMA. While Snort handles both of these types in a single rule, the proposed design will address header rules and payload rules separately.

Separating header searches from payload searches has several advantages. First, since header information will arrive from ePAPP before the payload, header searching can be initiated while the packet payload is still being buffered. Secondly, combining header and payload information into a single search string can make the size of the string impractical for use in a CAM.

Matching header information is generally a simpler process than payload content matching. If header information in an incoming packet meets all of the header requirements of a given Snort rule (for instance, the source address and port number match specific values), the packet is tagged as a possible hit (contingent upon a corresponding payload match). For most rules, it is this simple. There are, however, some exceptions that do not merely require an exact match. Some rules require that a value fall within a certain range (for instance, the source port must be less than 1024). Other rules specify that a piece of header information must *not* be a particular value (for instance, the destination port cannot be 80). Presently, ternary CAMs do not have the ability to do range or inequality checking. Therefore, each of these exceptional header search requirements are performed with hardware preprocessing and incorporated into the header search string as a 1-bit flag.

Payload searches are different from header searches in that, instead of trying to simultaneously match a number of header field values in a single combined search, the payload

13

search is attempting to match certain strings that appear at certain locations within a packet. Since the entire payload must be searched in the CAM, and since many payloads are larger than the maximum CAM width, payloads must be incrementally shifted and searched at pre-defined offsets. For reasons discussed in Chapter 4, CASMA performs a CAM search at each 8-byte offset within a payload. Therefore, a payload of *n* bytes will require ((n-1)/8) + 1 CAM searches in order to sufficiently check a payload for all possible payload signature matches. Fortunately, a payload of *n* bytes requires *n* cycles to arrive from the ePAPP unit.

Certain rules specify that a payload signature to be matched be regarded as a hit only if the signature string is found at a certain range of depths within the payload. In order to incorporate this functionality into a standard CAM search, a novel encoding scheme is proposed that specifies within a CAM entry at which depths payload string matches are valid. By inputting into the CAM as part of the search string the depth associated with the payload content being searched, payload string depth requirements can be enforced.

Results from associated header and payload searches must be correlated by a postprocessor to determine any and all rule matches, as well as determine the threat severity of the detected traffic. The specific nature of this correlation is beyond the scope of this research, however generic result outputs are provided to more easily enable rapid processing.

Figure 4 shows the general architecture of a typical switch. Packets are captured by the PHY and undergo MAC-layer processing. Packets are then passed on to a network processor that performs any processing that is required on the packet, which may include some form of packet inspection (e.g., packet filtering, intrusion detection).

Figure 5 shows a network switch that has been augmented with the ePAPP and CASMA architectures. ePAPP accepts unclassified bytes of packet data directly from the PHY and

14

classifies them through protocol analysis. The formatted packet fields are forwarded to the CASMA unit, which performs header and payload CAM searches to find potential attack signature matches. Result data is passed to the network processor to be correlated. Thus, the entire burden of packet inspection is removed from the network processor through the addition of pipelined hardware.

Figure 4. Traditional Network Switch Architecture

Chapter Two will examine research related to the goals of this thesis. Chapter Three will discuss the design and performance of the Embedded Protocol Analyzer Pre-Processor. Chapter Four will discuss the design, performance, and issues related to the CAM-Assisted Signature-Matching Architecture. Chapter Five will examine conclusions and future directions for this research.

Figure 5. Network Switch Augmented with the ePAPP and CASMA Architectures

### **2.0 RELATED WORK**

A hardware-based TCP/IP content scanning system is proposed in [22]. This work combines protocol processing engine, a per-flow state store, and content scanning engine into a single hardware architecture. Of primary interest to this research is the content scanning engine. Incoming TCP packets are streamed through the content scanner, a hardware model that is capable of scanning the payload of packets for a set of regular expressions using Deterministic Finite Automata (DFAs), as proposed in [23]. The content scanner claims speeds of up to 2.5 Gb/s. This design, however, supports only TCP flows, which is quite incomplete for intrusion detection purposes. Also, the design is targeted to an FPGA, which is cost- and size-prohibitive for use in a network device.

The work in [24] uses JHDL, a Java-based programmatic structural design tool, to create a module capable of generating circuits that match arbitrarily large regular expressions. The overall goal of this work is to prove the feasibility of using such a module on an FPGA to accelerate the task of string matching for network security applications. The work is based on the groundbreaking efforts on FPGA-based regular expression searching by Sidhu and Prasanna [25]. Search data is streamed through the match circuit one character at a time. Testing results indicate a throughput of one search character per clock cycle using the proposed method, irrespective of the length of the search string. This solution, as before, is impractical because of its dependence on a reconfigurable FPGA platform.

The method proposed in [26] attempts to implement the Snort intrusion detection engine in reconfigurable hardware on an FPGA. The research is based on an early version of Snort (v.1.8.7) that supported 1239 rules. The proposed architecture performs first a header search based on source and destination ports and addresses as well as protocol type, and then a subsequent payload search based on the results of the header search. The proposal suggests the use of CAMs to perform the necessary header and payload searches. While the work proposes many of the same fundamental concepts as this thesis, there are no design details or results available to support a proof of concept. Again, the choice of an FPGA as a target for the architecture is an impractical choice.

The architecture proposed in [28] is another attempt to map Snort rules directly into reconfigurable hardware. The design features content pattern-matching engines that match payload chunks in 4 byte increments against a given rule. Each rule, represented by its own generated structural VHDL, is searched in parallel. Initially, packet header information (source and destination ports and addresses, protocol type) is checked against the header requirements corresponding to a given rule. If there is a match, 4 byte shifts of payload information are fed into the rule's individual content pattern-matching engine. If a match is found, the corresponding packet is flagged and potentially dropped. Only 105 Snort rules are implemented in this design, and no explanation is given how these rules are mapped to VHDL. By its own admission, this contribution relies on frequent reconfiguration to account for new rules, hence its FPGA target. This suffers from the same drawbacks as much of the previously mentioned research.

The goal of [29] is to speed up multi-field packet classification using CAM-like memory. Citing the expensive nature of high-density ternary CAMs, 128 bit-wide ternary CAM-like memories (CLMs) are proposed which function like individual CAM entries but are touted as more cost-effective. The research focuses on classification of IPv6 packets based on IP source and destination addresses, source and destination ports, and protocol type. Each of the five field types is searched individually in parallel with the other field types, and results are correlated with specialized combinational logic to produce a rule match index uniquely identifying a rule hit. The proposed architecture has elements in common with this thesis, however its restriction to IPv6 packet classification does not satisfy the larger scope of the thesis effort.

The Granidt (Gigabit Rate Network Intrusion Detection Technology) architecture is proposed in [27]. This work proposes an integrated hardware/software solution that improves Snort performance by performing rule matching in custom hardware using CAMs. The software "rule compiler" is responsible for accepting a subset of Snort rule syntax and producing a hardware representation of the rule fields to be matched. The rule compiler creates several tables that are used to initialize the search CAMs, as well as an internal representation of the rules that links fields specified by the rules to the CAM tables and range tables. The "rule processor" software component initializes the hardware CAMs and initiates packet processing. Header and payload searches are performed separately, each facilitating a number of individual CAMs. A match vector that indicates the results of the CAM searches is correlated to the internal rule database to determine the appropriate action for a matched rule. Since the rule compiler is in software, new rules can be added to the design without resynthesis. This design is flawed, however, in that it requires several individual CAMs, which is cost-prohibitive. Also, the maximum supported signature size is 20 bytes, which is not sufficient for a large number of Snort rules. Details of the mapping of the rules themselves into hardware are not clearly defined.

### 3.0 ePAPP: AN EMBEDDED PROTOCOL ANALYZER PRE-PROCESSOR

This chapter presents a hardware Embedded Protocol Analyzer Pre-Processor (ePAPP) that performs the protocol analysis of network packets at line speeds of at least 1 Gb/s using only a small amount of area on a structured ASIC technology. The device fits between the physical network interface and an upstream processor or additional hardware pipeline (CASMA) and replaces the software protocol analysis program typically run on a processor, achieving a significant performance increase. The presented solution is additionally advantageous in that every protocol field of a network packet is classified. The particular protocols being analyzed can be configured in an internal memory within the pre-processor, allowing easy protocol upgrades and product versatility in different applications. A single configuration in the protocol memory can handle hundreds of protocols without reprogramming. A prototype of ePAPP that supports various protocols including Ethernet, IPv4, ARP, TCP, and UDP has been designed in VHDL and synthesized for a 130 nm a structured ASIC technology. Results show that 2.89 Gb/s can be achieved when implemented on a structured ASIC, using less than 1% of available logic cells. The prototype is also demonstrated to have a decoding latency 75 times faster than the conventional software.

### **3.1 INTRODUCTION**

As the speeds of local networks increase, the amount of time available for a network device (such as a switch) to respond to a single packet decreases. To improve upon traditional software solutions, network processors have been developed which are capable of performing packet classification and forwarding at higher speeds. Most network processors (NPs) utilize multiple channel processors to perform packet inspection and data extraction for each network link, typically using 32- or 64-bit RISC architectures but in some instances using VLIW processors.

One of the most fundamental tasks these network processors perform is *protocol analysis*. This is the process by which individual fields within a packet are classified and the protocols within the packet are identified. RISC processors are by definition a small subset of instructions that, when combined in a program, can execute complex tasks. The problem is that packet processing requires a large amount of bit manipulation to extract particular data fields. For example, the source and destination of an IP packet are octets 13 through 16 and octets 17 through 20, respectively. For a RISC processor, these fields must be placed in a 32- or 64-bit register before processing can take place. To achieve this protocol analysis task by software can be quite complex just to extract a few fields from a packet header.

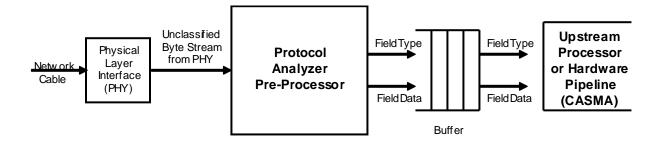

The physical layer interface (PHY) to a network cable translates analog signal levels into a stream of fixed width digital data. For example, the interface to a 100 Mb/s PHY is a 4-bit wide data path that operates at 25 MHz and a 1 Gb/s PHY is an 8-bit wide data path that operates at 125 MHz. This thesis presents a hardware Embedded Protocol Analyzer Pre-Processor (ePAPP) that resides between the PHY and the channel processor to replace the protocol analysis work that is usually done by software in the processor, with a great performance improvement over software solutions. The objective is to assemble and output the individual protocol fields of a packet at line speeds, augmenting the field data output with a field type that is unique to the particular protocol and field description. Moving the protocol analysis work from software to the hardware ePAPP drastically reduces the execution time for protocol analysis, as well as removes software overhead in the Channel Processor.

Many proposed network processors exist which use specialized, non-RISC architectures to support multi-gigabit speeds [15,16]. These solutions are still constrained by the cycle-rich nature of processor architectures. We propose a design that will be able to separate and classify *every field of a network packet* in a minimal number of cycles.

Application-specific integrated circuits (ASICs) are used in many network nodes to improve packet processing speeds, however they are rarely flexible enough for rapid adaptation to protocol or standards changes [1]. By utilizing a ROM to store protocol classification information, our proposed design allows for incorporation of new standards and designs without complete ASIC redesign.

In this chapter, Section 3.2 presents the reconfigurable architecture for mapping the protocols into hardware. Section 3.3 presents a circuit implementation of a prototype supporting protocols including Ethernet, IPv4, ARP, UDP, and TCP. Section 3.4 introduces performance of the design and performance benefits over conventional software.

### **3.2 ARCHITECTURE FOR PROTOCOL MAPPING**

ePAPP is a hardware-based Protocol Analyzer that will receive a fixed width stream of packet data from the PHY and output a stream of organized data by forwarding the Field Type and Field Data values. As shown in Figure 6, values can be forwarded to an upstream network processor or another pipelined hardware unit, such as CASMA. The Field Type is a unique number that specifies a particular field of a particular protocol. It is used to classify the data that is simultaneously presented on the Field Data bus.

Figure 6. The Protocol Analyzer Pre-Processor

The width of the Field Data bus is the same as the register widths inside the upstream processor. Field Data is gathered directly from the incoming stream of packet data and is zero-padded depending on the width of the associated protocol field. Thus, rather than seeing a stream of 4- or 8-bit values, an upstream processor would see a stream of packet field information. This would drastically reduce the amount of pre-processing an upstream processor would have to perform before it could determine the proper packet handling.

Field widths in data packets vary a great deal, and many fields will not consume the entire register width. This will not reduce the efficiency of the upstream processor as long as the average field width is larger than the fixed width stream coming off of the PHY. In most cases, the field width will be significantly larger and, in some cases, may need to be broken into two or more separate fields, as with packet payloads. This is beneficial to the upstream processor as it better fits its architecture.

Due to the continuing development of Internet protocols, we store the definition of protocol types in a Protocol Memory, which makes it easy for protocol updates, reconfiguration, or expansion.

Apart from the Protocol Memory, there are two other parts assisting with the protocol field classification: a "Jump Translation Look-aside Buffer (TLB)" with a "Jump Register" to handle branches between different layers of protocols according to the information found in packet headers; and a "Length Block" to get length information for variable length protocol fields (for example, a payload field) according to packet headers. The following sections describe in detail of how to map protocols into these three blocks.

### **3.2.1 Protocol Memory**

The Protocol Memory, which stores the protocol field information used for classification, provides protocol information to the Protocol Analyzer. A unique number is assigned to each field type of each supported protocol. The current Internet protocols are very complex, involving multiple headers of dynamic lengths (one for each layer of abstraction) and demanding branches between encapsulated protocol layers.

An example using the IPv4, UDP, and TCP protocols is shown here. The associated protocol field descriptions are given in Tables 2 through 4, respectively. The Protocol Field (octet 10) of the Internet Protocol defines which protocol is used above the Network layer. Specifically, the Protocol Field of IPv4 defines the format of the Data fields within the IP packet, octets 21 and greater, which can either be the UDP format as shown in Table 3, or the TCP format showed in Table 4. Furthermore, octet 3 and 4 define the Total Length of the IP packet, from which can we derive the length of IP payload. The Internet Header Length can be gathered from the second nibble of octet 1, which will dictate the existence of optional octets 21 through 24. Thus, the data within a packet header determines how the packet is to be interpreted. This traditional layering scheme requires that the Protocol Analyzer have a decision tree to determine how it should interpret the stream of data.

## Table 2. IP Protocol Field Description

| OCTET POSITION      | IP FIELD DESCRIPTION                   | ABREVIATION |

|---------------------|----------------------------------------|-------------|

| OCTET 1             | Version (4 bit)+IHL (4 bit)            | (VER, IHL)  |

| OCTET 2             | Type of service                        | (TOS)       |

| OCTET 3,4           | Total Length                           | (TOL)       |

| OCTET 5,6           | Identification                         | (ID)        |

| OCTET 7,8           | Flags (3 bit)+Fragment Offset (13 bit) | (FLG, FRO)  |

| OCTET 9             | Time to Live                           | (TTL)       |

| OCTET 10            | Protocol                               | (PRO)       |

| OCTET 11,12         | Header Checksum                        | (IP_SUM)    |

| OCTET 13,14,15,16   | Source Address                         | (SRC)       |

| OCTET 17,18,19,20   | Destination Address                    | (DEST)      |

| (OCTET 21,22,23,24) | (Options + Padding)                    | (OPT)       |

| OCTET 21, 22        | Data                                   |             |

## Table 3. UDP Protocol Field Description

| OCTET POSITION | UDP FIELD DESCRIPTION |

|----------------|-----------------------|

| OCTET 1,2      | Source Port           |

| OCTET 3,4      | Destination Port      |

| OCTET 5,6      | Length                |

| OCTET 7,8      | Checksum              |

| OCTET 9,10     | Data                  |

## Table 4. TCP Protocol Field Description

| OCTET POSITION      | TCP FIELD DESCRIPTION  | ABBREVIATION |

|---------------------|------------------------|--------------|

| OCTET 1,2           | Source Port            | (SRC_PORT)   |

| OCTET 3,4           | Destination Port       | (DEST_PORT)  |

| OCTET 5,6,7,8       | Sequence Number        | (SEQ)        |

| OCTET 9,10,11,12    | Acknowledgement Number | (ACK)        |

| OCTET 13,14         | Data Offset(4 bit)+    | (DTO, FLG)   |

|                     | Reserved(6 bit)+       |              |

|                     | Control Flags(6 bit)   |              |

| OCTET 15,16         | Window                 | (WIN)        |

| OCTET 17,18         | Checksum               | (TCP_SUM)    |

| OCTET 19,20         | Urgent Pointer         | (URP)        |

| (OCTET 21,22,23,24) | (Options + Padding)    | (OPT)        |

| OCTET 21,22         | Data                   |              |

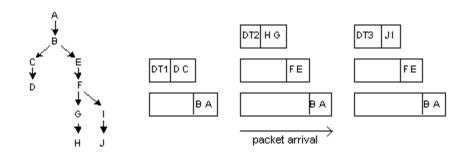

For clarity and generality, we graph a packet containing layered protocol fields A through J below (Figure 7). In this packet, fields A and B are in a lower layer protocol and the value of B determines the protocol and the meaning of the data fields that follow. Figure 7 shows the three different protocol stacks that are possible. The first protocol layer contains the fields A and B. The contents of B determine which protocol is used at the next layer up the stack. In this example, the protocol CD is used if B=20 and protocol EF is used if B=40. However, in the EF protocol, the E field is used to determine the next protocol layer but the next protocol does not start until after F. Protocol GH is used if E is 71 and IJ is used if E is 72. The field values were randomly selected for this example. DT1, DT2, DT3 are payload data fields for protocols CD, GH, and IJ, respectively.

Figure 7. An Example of a Layered Protocol Description

Most of the protocol fields have constant widths that are defined by the protocol format and are labeled as W(A), W(B),...,W(DT1) in this example. Some other fields have a variable length that is calculated from a length field appearing earlier in the same packet. For example, DT2 and DT3 have variable lengths that depend on the values of fields G and J, which define the total length of protocol GH and protocol IJ, respectively.

The following characteristics of each protocol field type are stored in the Protocol Memory:

- *Field Type*, a unique number identifying the particular protocol field. No two fields inside the Protocol Memory may have the same Field Type, even if they are from different protocols. This simplifies the processing of the packets as the Field Type number also defines the context (i.e. protocol layer) in which the field exists.

- *Field Width*, defines the width of the field if it is of constant length.

- *Protocol Indicator*, a one-bit value that indicates whether the contents of the field are indicative of the next protocol layer to be used. If *Protocol Indicator* is set to '1', the field's contents are used by the "Jump TLB" to determine the initial Field Type of the next protocol. This value is stored in the "Jump Register" until a jump to the next protocol is indicated.

- *Branch Indicator*, a one-bit value that indicates whether there should be a branch to an upper layer protocol immediately following the current field. If the value of *Branch Indicator* is '0', the next Field Type used is the current Field Type incremented by one. If the value of *Branch Indicator* is '1', the next Field Type is taken from the "Jump Register," as stored by the "Jump TLB."

- *Length Indicator*, a one-bit value that indicates whether the current field contains any length information for an upcoming variable length protocol field. If the value of *Length Indicator* is '1', the field contains length-related information and should be passed to the "Length Block" to be used in the appropriate calculations.

- *Variable Length*, a one-bit value that indicates whether the current field is of variable length. If the value of *Variable Length* is '1', the field is of a variable length that must be retrieved from the "Length Block."

• *Packet Done*, a one-bit value that indicates whether the previous field was the last of the packet. If the value of *Packet Done* is '1', the Protocol Analyzer halts until a new packet is received from the PHY.

| Protocol | Field | Field  | Branch    | Protocol  | Length    | Variable | Packet |

|----------|-------|--------|-----------|-----------|-----------|----------|--------|

| Field    | Туре  | Width  | Indicator | Indicator | Indicator | Length   | Done   |

| А        | 0     | W(A)   | 0         | 0         | 0         | 0        | 0      |

| В        | 1     | W(B)   | 1         | 1         | 0         | 0        | 0      |

| С        | 2     | W(C)   | 0         | 0         | 0         | 0        | 0      |

| D        | 3     | W(D)   | 0         | 0         | 0         | 0        | 0      |

| DT1      | 4     | W(DT1) | 0         | 0         | 0         | 0        | 0      |

| EOF1     | 5     | 0      | 0         | 0         | 0         | 0        | 1      |

| E        | 6     | W(E)   | 0         | 1         | 0         | 0        | 0      |

| F        | 7     | W(F)   | 1         | 0         | 0         | 0        | 0      |

| G        | 8     | W(G)   | 0         | 0         | 1         | 0        | 0      |

| Н        | 9     | W(H)   | 0         | 0         | 0         | 0        | 0      |

| DT2      | 10    | 0      | 0         | 0         | 0         | 1        | 0      |

| EOF2     | 11    | 0      | 0         | 0         | 0         | 0        | 1      |

| Ι        | 12    | W(I)   | 0         | 0         | 0         | 0        | 0      |

| J        | 13    | W(J)   | 0         | 0         | 1         | 0        | 0      |

| DT3      | 14    | 0      | 0         | 0         | 0         | 1        | 0      |

| EOF3     | 15    | 0      | 0         | 0         | 0         | 0        | 1      |

### Table 5. The Protocol RAM Data

Additional key fields may also be incorporated into this architecture. Table 5 shows the hypothetical Protocol RAM content for the example shown in Figure 7.

### 3.2.2 Jump Register and Jump TLB

The Jump Register and the Jump Translation Look-aside Buffer (TLB) handle the branches between different protocols. The Jump Register contains the Field Type of the next encapsulated protocol layer, as set when triggered by the "Protocol Indicator" field of the Protocol Memory. The Jump TLB is a look-up table that determines which upper layer protocol to use based on the current Field Type and Field Data when the "Protocol Indicator" signal is asserted. Table 6 shows the Jump TLB for the protocol example shown in Figure 7. When the current Field Type and Field Data match a row in the TLB and Protocol Indicator is '1', the value in the "Jump Address" column is stored in the Jump Register. This value is used for the next Field Type when "Branch Indicator" is set to '1', effectively branching to a new protocol.

In the protocol example shown in Figure 7, the "B" field's Protocol Memory entry has a value of '1' in both its "Branch Indicator" and "Protocol Indicator" fields. Thus, the Field Type for B (1) and the current Field Data (either 20 or 40) are used to determine the Jump Address. If the Field Data is 20, the Jump Address is 2, which is the start of the CD protocol. If the Field Data is 40, however, the Jump Address is 6, which is the start of the EF protocol. Since protocol field B has a '1' in its "Branch Indicator" field, the Jump Address is immediately used to indicate the next protocol after B.

For the EF protocol, the E field has a '1' in its "Protocol Indicator" entry and thus is used to determine the next encapsulated protocol in the stack. The Field Data corresponding to protocol field E (either 71 or 72) is matched with the Field Type (6), to get either 8 or 12 as the Jump Address. This value is stored in the Jump Register until the completion of field F, which indicates a branch to the next protocol.

| Field Type | <b>Field Data</b> | Jump Address |

|------------|-------------------|--------------|

| 1 (B)      | 20                | 2            |

| 1 (B)      | 40                | 6            |

| 6 (E)      | 71                | 8            |

| 6 (E)      | 72                | 12           |

Table 6. The Jump Translation Look-Aside Buffer

### 3.2.3 Length Block

The Length Block is responsible for calculating and storing the lengths of variable length protocol fields. Such fields include optional fields, alignment padding, and payloads. The lengths of these fields are determined by utilizing length information contained in previous protocol fields. For instance, the specified header length for a protocol header may be used to determine how many option and padding bytes the header contains. In another case, the header length of a protocol layer may be subtracted from the total length of that layer to determine the number of payload bytes.

In the example in Table 5, field G defines the total length of the GH protocol layer, which includes field G, field H, and payload field DT2. Since field DT2 is not fixed in length, as indicted by a '1' in its "Variable Length" entry, its length must be calculated in the Length Block. Knowing that G contains the total length of the GH layer, the width of the payload field DT2 is G - W(G) - W(H), where W(x) is the fixed width of protocol field x. This value is stored in the Length Register until the width of the payload field is requested.

### **3.3 CIRCUIT IMPLEMENTATION OF EPAPP**

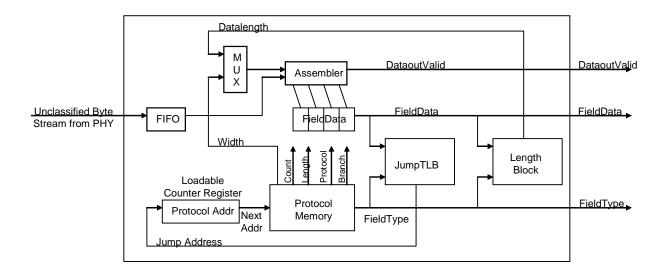

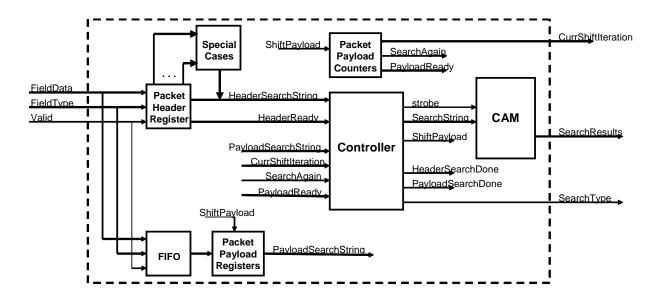

A prototype system supporting protocols Ethernet, IPv4, ARP, TCP, and UDP is implemented with the ability to process packets coming from a 1 Gb/s Ethernet PHY. Therefore, the input is a parallel stream of 8 bits from the 1 Gb/s PHY and the outputs are parallel streams of bits including an 8-bit line for the Field Type and a 32-bit line for the Field Data, as well as a single Valid bit to indicate valid output. The structure of the Protocol Analyzer Pre-Processor is shown in Figure 8, consisting of the Protocol Memory and Protocol Address Register, the Jump TLB, the Length Block, the Assembler, and a FIFO. The FIFO is at the beginning stage of ePAPP, connecting directly to the Ethernet PHY as a buffer to transfer the incoming data to the rest of ePAPP.

Figure 8. The Internal Architecture of the Protocol Analyzer Pre-Processor

The Assembler receives the parallel bit stream from the FIFO and places the bits into the correct location of the Field Data register. In essence, the Assembler is a shifter that has an internal counter loaded with the width of the current protocol field as indicated by the Protocol Memory. The contents of the Protocol Memory are shown in Table 7.

The shifter consists of four 8-bit registers to assemble the incoming blocks of 8 bits into 8-, 16-, 24-, or 32-bit chunks, as determined by the field width. A 2-to-1 multiplexer is utilized to allow the selection of a fixed field width (from the Protocol Memory) or a variable field width (from the Length Block). For fields that do not contain 32 bits worth of data, the most significant bits will be padded with zero.

| Address  | Description                               | Field<br>Width | Branch<br>Indicator | Protocol<br>Indicator | Length<br>Indicator | Variable<br>Length | Count<br>Done |

|----------|-------------------------------------------|----------------|---------------------|-----------------------|---------------------|--------------------|---------------|

| Ethernet |                                           | •              |                     |                       |                     |                    |               |

| 0        | Preamble _high                            | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 1        | Preamble_low                              | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 2        | Destination_high                          | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 3        | Destination_low                           | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 4        | Source_high                               | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 5        | Source_low                                | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 6        | Туре                                      | 1              | 1                   | 1                     | 0                   | 0                  | 0             |

| ARP      |                                           |                |                     |                       |                     |                    |               |

| 7        | Hardware                                  | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 8        | Protocol                                  | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 9        | Hardware Address Length                   | 0              | 0                   | 0                     | 0                   | 0                  | 0             |

| А        | Protocol Address Length                   | 0              | 0                   | 0                     | 0                   | 0                  | 0             |

| В        | Operation                                 | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| С        | Sender Hardware Address<br>(High bits)    | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| D        | Sender Hardware Address<br>(Low bits)     | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| Е        | Sender Internet Address                   | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| F        | Target Hardware Address<br>(High bits)    | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 10       | Target Hardware Address<br>(Low bits)     | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 11       | Target Internet Address                   | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 12       | Data Padding                              | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 13       | Data Padding                              | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 14       | Data Padding                              | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 15       | Data Padding                              | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 16       | (Ethernet)Frame Checksum                  | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 17       | End of Frame                              | 0              | 1                   | 1                     | 0                   | 0                  | 0             |

| IP       |                                           | •              |                     |                       |                     |                    |               |

| 18       | Version+Header Length                     | 0              | 0                   | 0                     | 1                   | 0                  | 0             |

| 19       | Type of service                           | 0              | 0                   | 0                     | 0                   | 0                  | 0             |

| 1A       | Total Length                              | 1              | 0                   | 0                     | 1                   | 0                  | 0             |

| 1B       | Identification                            | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 1C       | Flags (3 bit)+Fragment<br>Offset (13 bit) | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 1D       | Time to Live                              | 0              | 0                   | 0                     | 0                   | 0                  | 0             |

| 1E       | Protocol                                  | 0              | 0                   | 1                     | 0                   | 0                  | 0             |

| 1F       | Header Checksum                           | 1              | 0                   | 0                     | 0                   | 0                  | 0             |

| 20       | Source Address                            | 3              | 0                   | 0                     | 0                   | 0                  | 0             |

| 21       | Destination Address                       | 3              | 1                   | 0                     | 0                   | 0                  | 0             |

| 22       | (Options + padding)                       | X              | 1                   | 0                     | 0                   | 1                  | 0             |

# Table 7. Current Content Inside Protocol Memory

# Table 7 (continued)

| ТСР |                             |   |   |   |   |   |   |

|-----|-----------------------------|---|---|---|---|---|---|

| 23  | Source Port Number          | 1 | 0 | 0 | 0 | 0 | 0 |

| 24  | Destination Port Number     | 1 | 0 | 0 | 0 | 0 | 0 |

| 25  | Sequence Number             | 3 | 0 | 0 | 0 | 0 | 0 |

| 26  | Acknowledgement<br>Number   | 3 | 0 | 0 | 0 | 0 | 0 |

| 27  | Header Length, Reserve, URG | 1 | 0 | 0 | 1 | 0 | 0 |

| 28  | Window Size                 | 1 | 0 | 0 | 0 | 0 | 0 |

| 29  | TCP Check Sum               | 1 | 0 | 0 | 0 | 0 | 0 |

| 2A  | Urgent Pointer              | 1 | 0 | 1 | 0 | 0 | 0 |

| 2B  | (Options + paddings)        | Х | 0 | 0 | 0 | 1 | 0 |

| 2C  | Data                        | Х | 1 | 1 | 0 | 1 | 0 |

| UDP |                             |   |   |   |   |   |   |

| 2D  | Source Port                 | 1 | 0 | 0 | 0 | 0 | 0 |

| 2E  | Destination Port            | 1 | 0 | 0 | 0 | 0 | 0 |

| 2F  | UDP length                  | 1 | 0 | 0 | 1 | 0 | 0 |

| 30  | Checksum                    | 1 | 0 | 0 | 0 | 0 | 0 |

| 31  | Data                        | Х | 1 | 1 | 0 | 1 | 0 |

The shifter consists of four 8-bit registers to assemble the incoming blocks of 8 bits into 8-, 16-, 24-, or 32-bit chunks, as determined by the field width. A 2-to-1 multiplexer is utilized to allow the selection of a fixed field width (from the Protocol Memory) or a variable field width (from the Length Block). For fields that do not contain 32 bits worth of data, the most significant bits will be padded with zero.

The Protocol Address Register is a register that saves the current address of the Protocol Memory. This register is actually a loadable counter that can either be incremented by one to move to the next field within a protocol, or can be loaded with the value of the Jump Address from the Jump TLB. This loading capability allows for branches between protocols within the Protocol Memory.

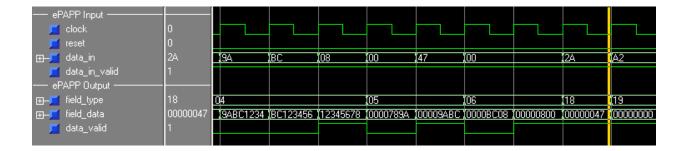

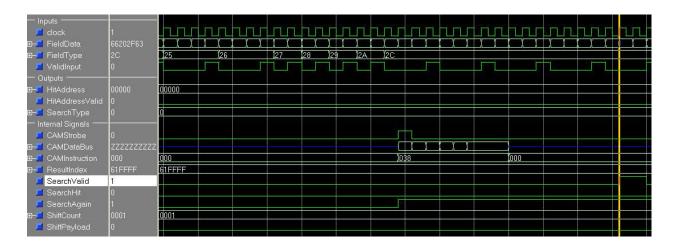

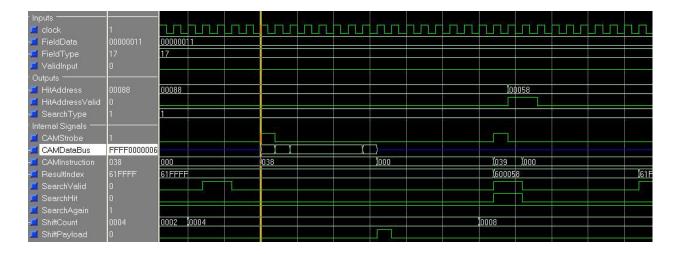

Figure 9. Simulation Waveform for ePAPP

Figure 9 shows a screenshot of a simulation waveform for ePAPP when processing a UDP packet. The inputs to and outputs from ePAPP are shown. The "data\_in" signal is representative of data arriving on an 8-bit PHY. Note that, due to FIFO and queuing delays, there is a three cycle delay between arrival of data on the PHY and its appearance in the "field\_data" output signal.

The "field\_data" and "field\_type" outputs are valid when the output "data\_valid" is high. For example, when the Field Type is 0x06 and "data\_valid" is asserted, the value of "field\_data" is 0x00000800. Field Type 0x06 corresponds to the protocol field of an Ethernet header, and the data value 0x00000800 indicates the IP protocol. Consequently, one can observe a branch to Field Type 0x18. Logically, 0x18 corresponds to the first field of an IP header.

One significant benefit of this design is the generic nature of the field classification outputs. Most probably, the outputs would be buffered and made accessible to a channel processor through memory-mapped registers. This provides a very general architecture that leaves the use of the classification information to the specific processor implementation. Consider this implementation running at 250 MHz, which would support a 2 Gb/s peak rate. Further consider a network processor running at 2 GHz. If one aggressively estimates that on average a valid field is classified every two cycles, one is left with an average of 16 processor cycles per packet field. The processor would simply need to execute a set of instructions corresponding to a particular field type, lifting a significant pre-processing burden off of the network processor itself.

## **3.4 DESIGN RESULTS AND PERFORMANCE**

The performance of the Protocol Analyzer must be sufficient to keep pace with the incoming data. For Gigabit Ethernet, the PHY transmits 8 bits every cycle at 125 MHz, thus requiring the same clock rate for the Protocol Analyzer. Fortunately, the internal architecture of the Protocol Analyzer utilizes only a small memory and TLB, both of which can reside internal to the chip, allowing a high clock rate.

It is expected that the final implementation of the Protocol Analyzer will be inside of a Network Processor using standard ASIC technology. However, to gauge this architecture's performance and size, the design has been targeted at a 130 nm structured ASIC solution. To do this, VHDL was created for the Protocol Analyzer and simulated for a Gigabit Ethernet PHY. The synthesis result is shown in Table 8.

**Table 8. Performance Results After Synthesis**

|                              | 130 nm Structured ASIC |

|------------------------------|------------------------|

| Standard-cell Instance Count | 2530 / 1.7M            |

| Size as a % of Total Cells   | < 1%                   |

| Speed in MHz                 | 360 MHz                |

| Throughput                   | 2.8 Gb/s               |

Table 9 compares the performance of the hardware ePAPP with the software-based decoder inside the "Snort" Intrusion Detection System. The software-based decoder in Snort captures packets utilizing the widely-used *libpcap* sniffing interface, a public domain library of packet capturing utilities. The decoder program in Snort version 1.9.0 needs more than 1700 lines in C code and an average of 1245 ns execution time when running on a Dell Power-Edge 4400 server which has dual 866MHz Pentium III Xeon processors, 1GB RAM, and is running the Redhat 7.2 OS. The hardware-based ePAPP uses less than 1% of a structured ASIC target and processes packets at line speeds. Protocol analysis is performed in parallel with the capturing process, and most of the processing time overlaps with the capturing process, with a maximum input to valid output latency of 6 clock cycles (less than 17 ns when circuit operates at 360 Hz). Assuming the capturing times for software and hardware are the same, we found that the pipelined protocol analysis in ePAPP brings a 75x performance improvement (1245 ns / 17 ns) in the latency for getting analysis results after capturing a packet. This presents ePAPP with

greater processing capability in high-speed networks. ePAPP and Snort support the same protocol group, with the exception of ICMP, however analysis shows that ICMP could be implemented without an appreciable effect on processing speed.

|                  | Software-Based (Part of the    | Hardware-Based ePAPP       |

|------------------|--------------------------------|----------------------------|

|                  | <b>Decoder in Snort IDS</b> )  |                            |

| Execution Type   | Sequential                     | Six-stage Pipeline         |

| Architecture     | Dual 866MHz Pentium III Xeon   | 130 nm structured ASIC     |

|                  | Processors                     |                            |

| Size             | 1700 lines in C code           | < 1% of target area        |

| Protocol Support | Fixed based on available       | Expandable by adding to or |

|                  | software instructions          | updating the Protocol RAM  |