# LOW-POWER WIRELESS DISTRIBUTED SIMD ARCHITECTURE CONCEPT: AN 8051 BASED REMOTE EXECUTION UNIT

by

### Vyasa Sai

B.Tech, Jawaharlal Nehru Technological University, 2005MS, North Dakota State University, 2008

Submitted to the Graduate Faculty of

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy in Computer Engineering

University of Pittsburgh

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Vyasa Sai

It was defended on

February 27, 2013

and approved by

James T. Cain, PhD, Professor Emeritus, Electrical and Computer Engineering Department Yiran Chen, PhD, Assistant Professor, Electrical and Computer Engineering Department Steven P. Levitan, PhD, John A. Jurenko Professor, Electrical and Computer Engineering Department

Bryan A. Norman, PhD, Associate Professor, Industrial Engineering Department

Dissertation Director: Marlin H. Mickle, PhD, Bell of Pennsylvania/Bell Atlantic

Professor, Electrical and Computer Engineering Department

Copyright © by Vyasa Sai

2013

# LOW-POWER WIRELESS DISTRIBUTED SIMD ARCHITECTURE CONCEPT: AN 8051 BASED REMOTE EXECUTION UNIT

Vyasa Sai, PhD

University of Pittsburgh, 2013

Power has become a critical aspect in the design of modern wireless systems, especially in passive device nodes such as Radio Frequency Identification (RFID) tags, sensor nodes etc. Passive RFID tags in particular use simple logic that is used to respond with a unique code or data to identify objects when queried by an interrogator, whereas wireless passive sensor devices use microcontrollers for sensor data processing. There is a need for a Minimal Instruction Set Architecture (MISA) for such passive nodes with regard to low power. In this context, passive node capabilities need to be explored, possibly to suit target applications, in order to enable more than just identification and perhaps less than those of a conventional microcontroller Instruction Set Architecture (ISA).

This dissertation research demonstrates a low-power wireless distributed processor architecture concept. The data and program instructions are stored on a powered interrogator providing wireless supervisory control for the remote passive node that has a basic processing core called the remote execution unit (REU). The interrogator and the passive node (REU) combination can be viewed as a complete processor or as multiple processing units forming the basis for a wireless distributed Single Instruction Multiple Data (SIMD) processor.

This research introduces and investigates the REU architecture using an 8051-MISA with the goal of reducing power consumption of the system. A novel low power data-driven symbol decoder-CRC along with the 8051-MISA based execution core design form the frontend and core part of the REU architecture. Clocked and asynchronous digital logic implementations of the REU core design are presented and correspondingly the power, area and speed comparisons are also provided.

Lack of strong support by commercial CAD tools is a major hurdle for synthesis of asynchronous designs. This research also presents a high-level design flow used to implement the asynchronous logic for the REU using traditional clocked CAD flows. This research work demonstrates immense potential to realize low power wireless passive sensor nodes for biomedical, automation, environmental, etc., applications especially while providing the basis for a programmable passive remote unit for distributed processing.

# TABLE OF CONTENTS

| AC  | KNO | WLEDG | SEMENTS                                              | XIII |

|-----|-----|-------|------------------------------------------------------|------|

| 1.0 |     | INTRO | DUCTION                                              | 1    |

|     | 1.1 | OV    | ERVIEW OF POWER TERMINOLOGY AND LOW POWER TECHNIQUES | 3    |

|     | 1.2 | OV    | VERVIEW OF RFID BASED SYSTEMS                        | 6    |

|     |     | 1.2.1 | RFID Tag based Systems                               | 6    |

|     |     | 1.2.2 | RFID Sensor based Networks                           | 7    |

|     |     | 1.2   | 2.2.1 Wireless Passive Sensor Networks               | 8    |

|     |     | 1.2.3 | Power Comparisons of passive RFID nodes              | 10   |

|     | 1.3 | ST    | ATEMENT OF THE PROBLEM                               | 11   |

|     | 1.4 | OU    | TLINE OF THE DISSERTATION                            | 16   |

| 2.0 |     | WIREI | LESS DISTRIBUTED PROCESSOR ARCHITECTURE CONCEPT      | 18   |

|     | 2.1 | TH    | IE ARCHITECTURAL EMBODIMENT                          | 18   |

|     | 2.2 | AN    | APPLICATION SCENARIO                                 | 19   |

| 3.0 |     | PROPO | OSED LOW POWER REU ARCHITECTURES                     | 26   |

|     | 3.1 | RE    | U FRONTEND                                           | 27   |

|     |     | 3.1.1 | Motivation                                           | 27   |

|     |     | 3.1.2 | Pulse Width Coding Scheme                            | 29   |

|     |     | 3.1.3 | PWC Decoding Mechanism                               | 30   |

|     |     | 3.1.4 | Data-Driven Decoder Design                           | 31   |

|     |     | 3.1.5 | REU Frontend Architecture                                      | 34 |

|-----|-----|-------|----------------------------------------------------------------|----|

|     | 3.2 | RE    | CU CORE DESIGN                                                 | 41 |

|     |     | 3.2.1 | 8051-MISA for REU                                              | 42 |

|     |     | 3.2.2 | CLOCKED REU CORE                                               | 46 |

|     |     | 3.2   | 2.2.1 Architecture                                             | 46 |

|     |     | 3.2   | 2.2.2 Low Power Techniques                                     | 49 |

|     |     | (a)   | MISA for REU                                                   | 49 |

|     |     | (b    | Programmable Clock Frequency based Wireless Gating             | 50 |

|     |     | 3.2.3 | ASYNCHRONOUS REU CORE                                          | 51 |

|     |     | 3.2   | 2.3.1 Motivation                                               | 51 |

|     |     | 3.2   | 2.3.2 Architecture                                             | 52 |

|     |     | 3.2   | 2.3.3 Low Power Techniques                                     | 55 |

|     |     | (a)   | MISA for REU                                                   | 55 |

|     |     | (b    | ) Asynchronous design                                          | 55 |

|     | 3.3 | PR    | OPOSED REU ARCHITECTURES                                       | 57 |

| 4.0 |     | REU D | ESIGN IMPLEMENTATIONS AND RESULTS                              | 61 |

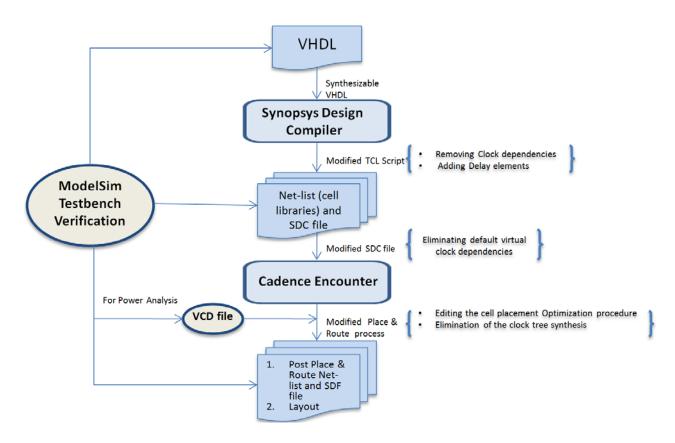

|     | 4.1 | DF    | ESIGN FLOW IMPLEMENTATION USING CLOCKED CAD TOOL FLOWS         | 62 |

|     |     | 4.1.1 | Simulate and Verify the VHDL design using ModelSim             | 65 |

|     |     | 4.1.2 | Generate a synthesizable design using Synopsys Design Compiler | 66 |

|     |     | 4.1.3 | Generate the layout using Cadence Encounter                    | 68 |

|     |     | 4.1.4 | Power estimation with Cadence Encounter                        | 69 |

|     | 4.2 | RE    | EU POST-LAYOUT SIMULATION RESULTS                              | 70 |

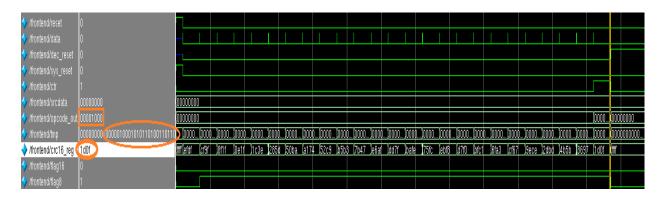

|     |     | 4.2.1 | Clocked REU Core                                               | 70 |

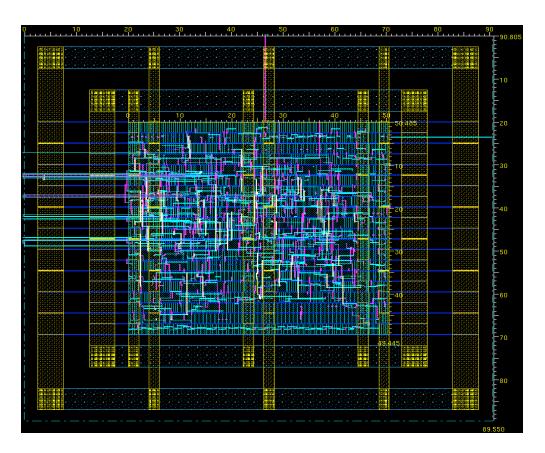

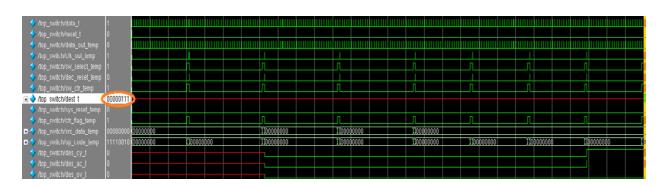

|     |     | 4.2.2 | Asynchronous REU Core                                          | 73 |

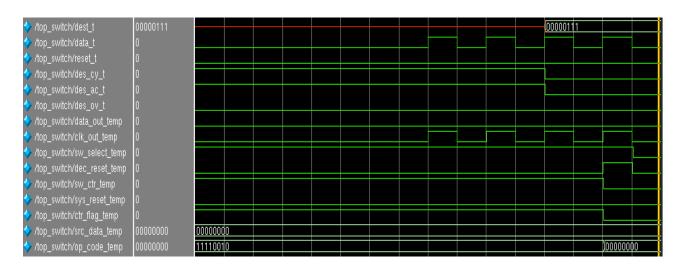

|       | 4.2.3  | REU Frontend70    | 6 |

|-------|--------|-------------------|---|

|       | 4.2.4  | Clocked REU 80    | 0 |

|       | 4.2.5  | Asynchronous REU  | 2 |

| 4.3   | RE     | EU COMPARISONS84  | 4 |

|       | 4.3.1  | Power             | 5 |

|       | 4.3.2  | Speed             | 9 |

|       | 4.3.3  | Area              | 1 |

|       | 4.3.4  | Summary92         | 2 |

| 5.0   | CONC   | LUSIONS           | 3 |

| 5.1   | CC     | ONTRIBUTIONS94    | 4 |

| 5.2   | FU     | TURE DIRECTIONS90 | 6 |

| APPEN | DIX A  | 92                | 7 |

| APPEN | DIX B  | 98                | 8 |

| APPEN | DIX C  |                   | 9 |

| APPEN | DIX D  |                   | 3 |

| APPEN | DIX E  |                   | 6 |

| REFER | RENCES | 140               | 0 |

# LIST OF TABLES

| Table 1.1: Power Comparisons of passive node based on their functionality | <i>y</i> 11 |

|---------------------------------------------------------------------------|-------------|

| Table 3.1: REU Frontend Input-Output Signal Descriptions                  | 41          |

| Table 3.2: REU-8051 Instruction Subset (MISA)                             | 43          |

| Table 3.3: REU-8051 Data Mnemonics                                        | 44          |

| Table 3.4: MISA 8051 Instructions                                         | 45          |

| Table 3.5: Clocked REU Cycles                                             | 48          |

| Table 3.6: Clocked REU Intermediate Signal Descriptions                   | 49          |

| Table 3.7: Asynchronous REU Intermediate Signal Descriptions              | 54          |

| Table A1: 8051 Instruction Descriptions                                   | 97          |

# LIST OF FIGURES

| Figure 1.1: Timing Chart for a Sensor Network           | 2                                   |

|---------------------------------------------------------|-------------------------------------|

| Figure 1.2: General Passive RFID System Architecture    | 7                                   |

| Figure 1.3: General WPSN Node Architecture              | 9                                   |

| Figure 1.4: A SIMD Processing Flow                      | 13                                  |

| Figure 1.5: Wireless SIMD Network Architecture          |                                     |

| Figure 2.1: Proposed Distributed Architecture           | 19                                  |

| Figure 2.2: State Diagram of a (RFID tag-Sensor) Transp | oonder21                            |

| Figure 2.3: Sequence diagram for an ADD operation       | 24                                  |

| Figure 3.1: Conventional Decoding Scheme                | 28                                  |

| Figure 3.2: Conventional Decoder block of a passive RF  | ID Tag29                            |

| Figure 3.3: Pulse Width Encoded Data                    | 30                                  |

| Figure 3.4: PWC Decoding Scheme                         | 31                                  |

| Figure 3.5: Data-Driven Decoding Element                | 32                                  |

| Figure 3.6: Data-Driven Decoder-CRC Unit                | 33                                  |

| Figure 3.7: REU Frontend Block Diagram                  | 35                                  |

| Figure 3.8: Design Computation Flow (a) Traditional     | al clock-driven CRC (b) Data-Driven |

| Decoder-Combinational CRC [56] (c) Data-Driven Decod    | der-CRC [57]                        |

| Figure 3.9: REU Frontend Pin Diagram                    | 40                                  |

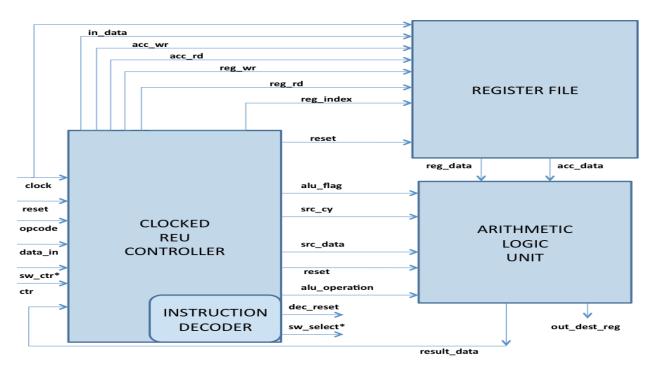

| Figure 3.10: High-level Clocked REU Core Architecture                   | 47 |

|-------------------------------------------------------------------------|----|

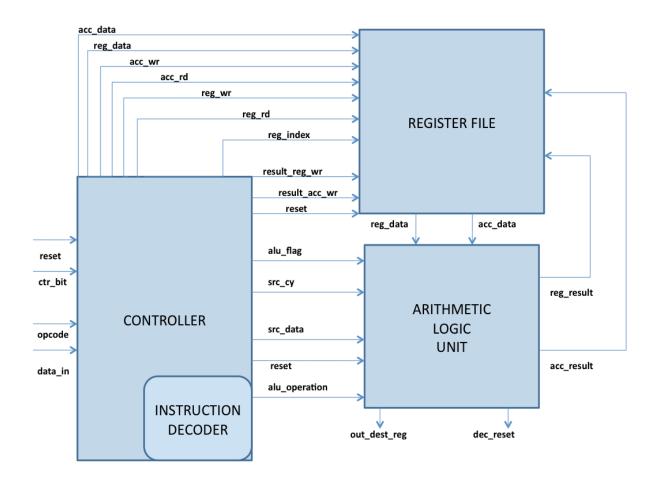

| Figure 3.11: High-level Async-REU Core Architecture                     | 53 |

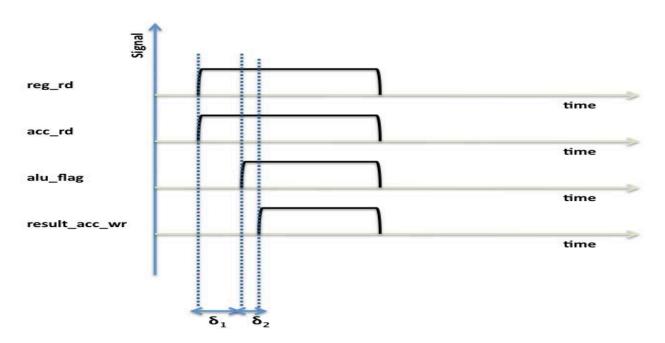

| Figure 3.12: Timing scenario for an ADD operation                       | 57 |

| Figure 3.13: Proposed Clocked REU High-level Block Diagram              | 58 |

| Figure 3.14: Proposed Asynchronous REU High-level Block Diagram         | 59 |

| Figure 4.1: Modules (a) Clocked REU (b) Asynchronous REU                | 63 |

| Figure 4.2: High Level Design Flow                                      | 64 |

| Figure 4.3: A portion of the sample VHDL code                           | 65 |

| Figure 4.4: A portion of a sample TCL script with the delay command     | 67 |

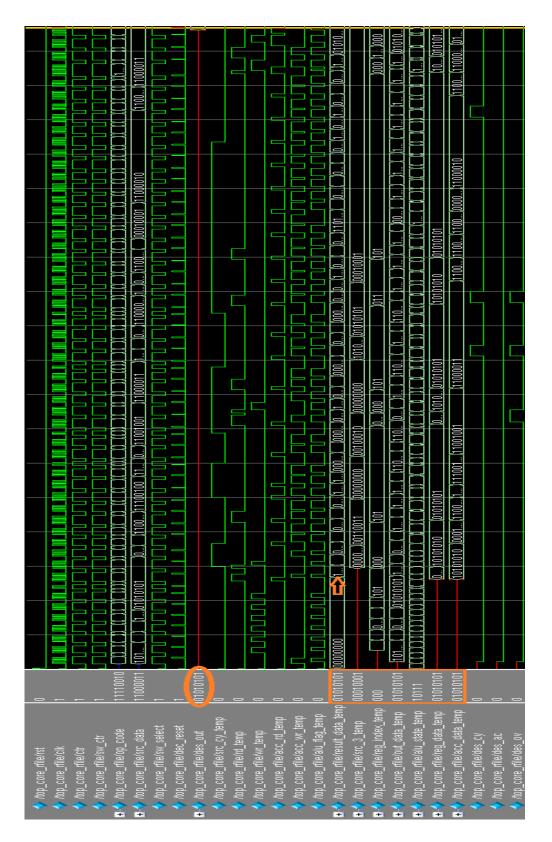

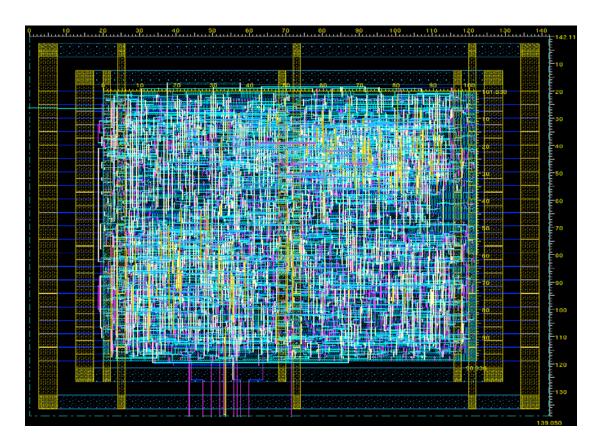

| Figure 4.5: Clocked REU Core Post-Layout Simulation.                    | 72 |

| Figure 4.6: Clocked REU Core Layout.                                    | 73 |

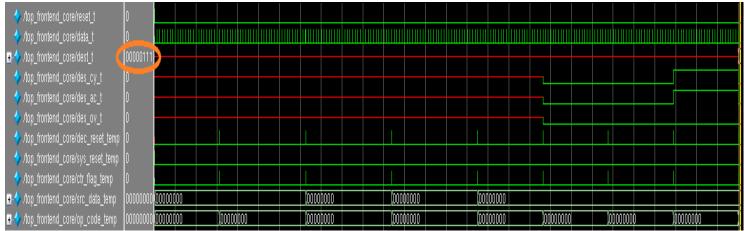

| Figure 4.7: Asynchronous REU Core Post-Layout Simulation                | 75 |

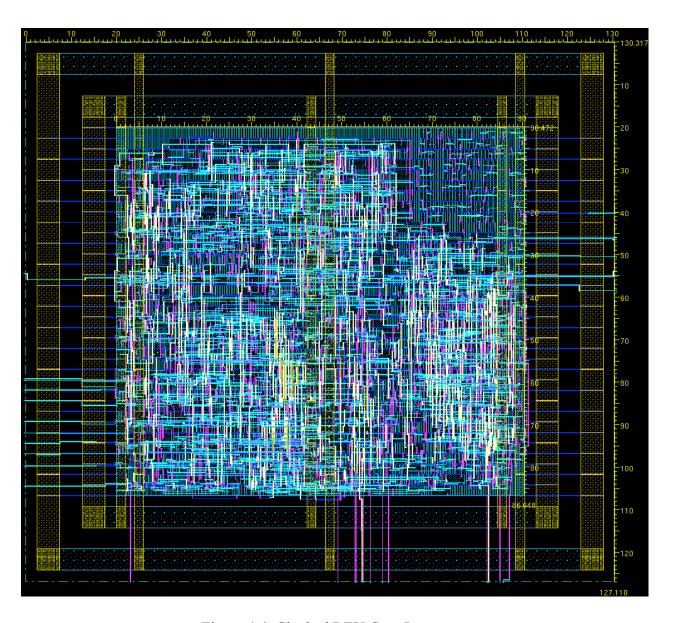

| Figure 4.8: Asynchronous REU core Layout.                               | 76 |

| Figure 4.9: Frontend Post-Layout Simulation                             | 77 |

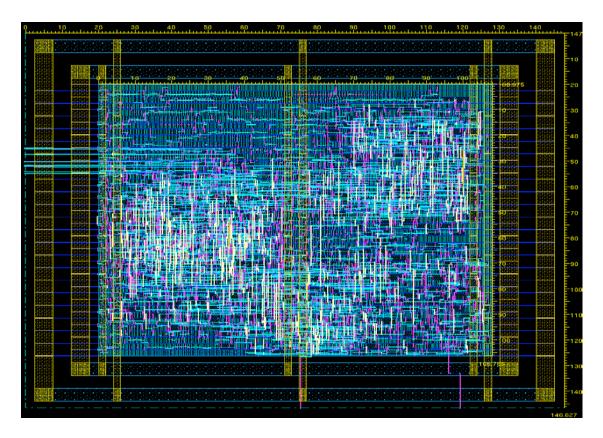

| Figure 4.10: Layout of the REU Frontend                                 | 79 |

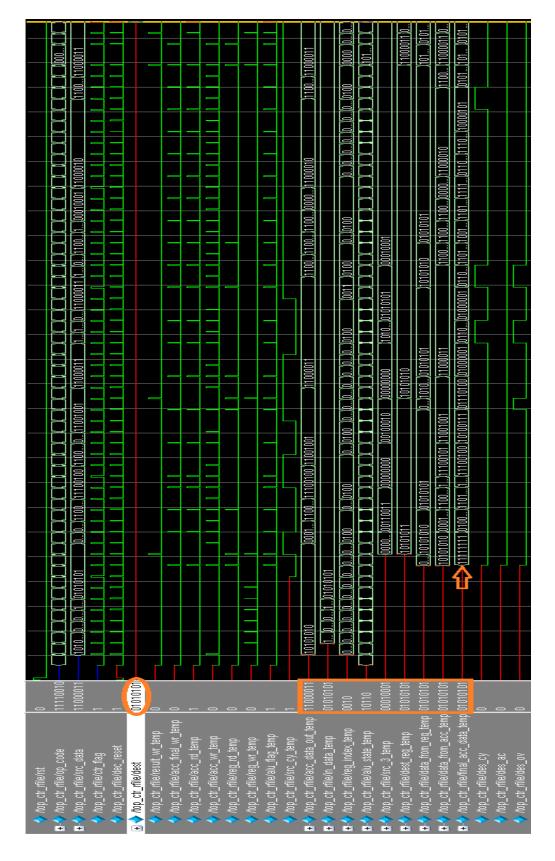

| Figure 4.11: Clocked REU Post-Layout Simulation.                        | 80 |

| Figure 4.12: Final Result Simulation (zoomed_in version of Figure 4.11) | 81 |

| Figure 4.13: Clocked REU Layout                                         | 82 |

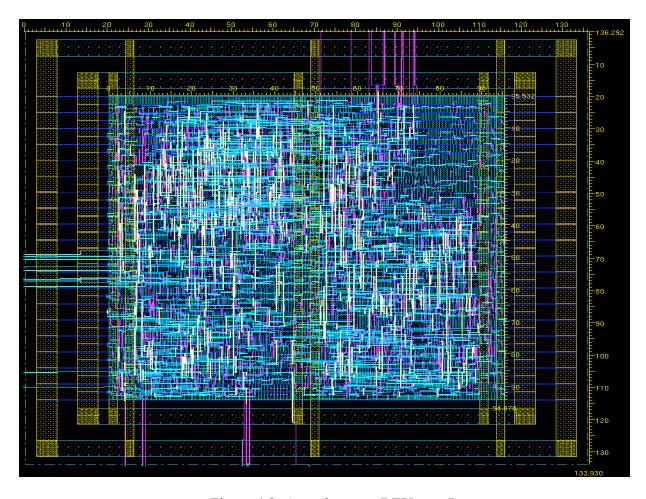

| Figure 4.14: Asynchronous REU Post-Layout Simulation                    | 83 |

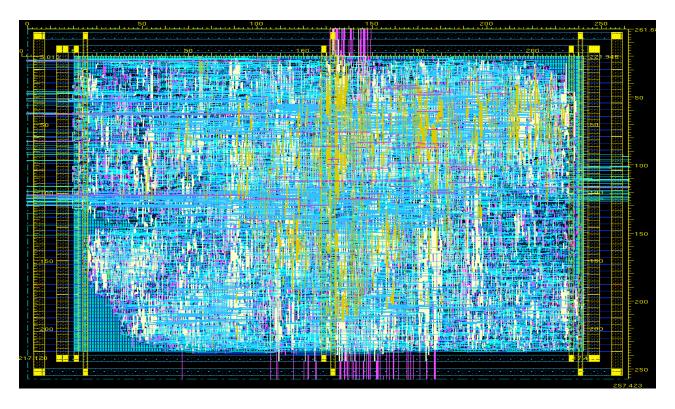

| Figure 4.15: Asynchronous REU Layout                                    | 84 |

| Figure 4.16: 8051 μC Core Layout                                        | 86 |

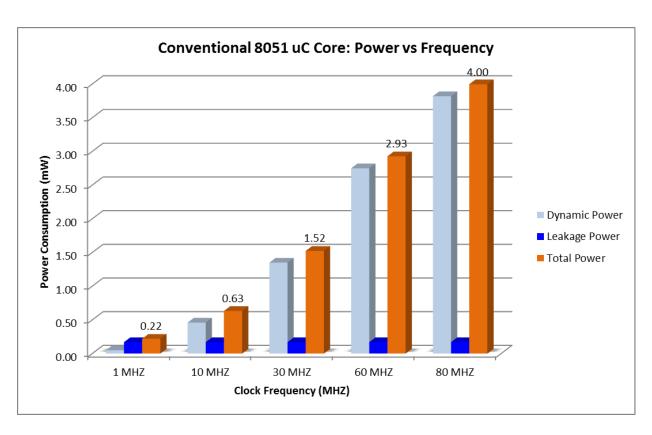

| Figure 4.17: 8051uC: Power Consumption Vs Clock Frequency               | 87 |

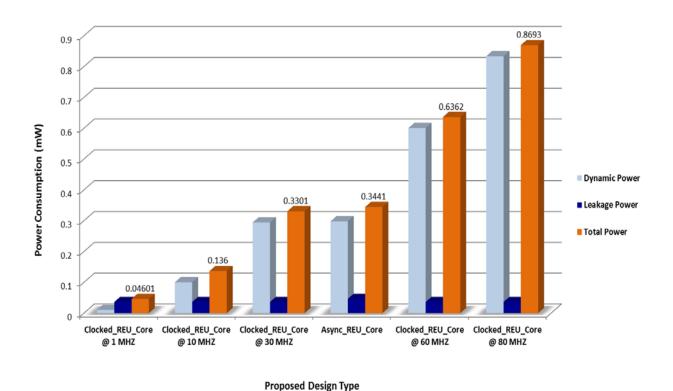

| Figure 4.18: Power Consumption Vs Proposed REU Core Design Types        | 88 |

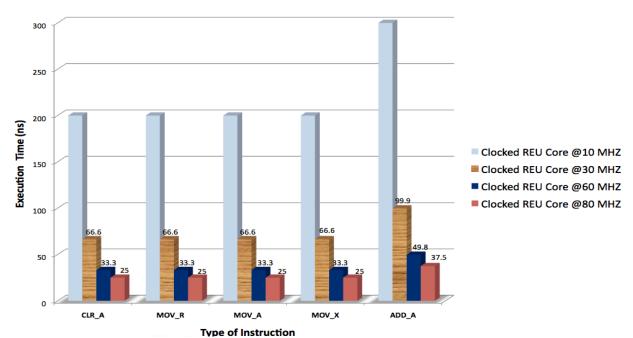

| Figure 4.19: Execution time vs Instruction Type for REU Clocked Core | . 89 |

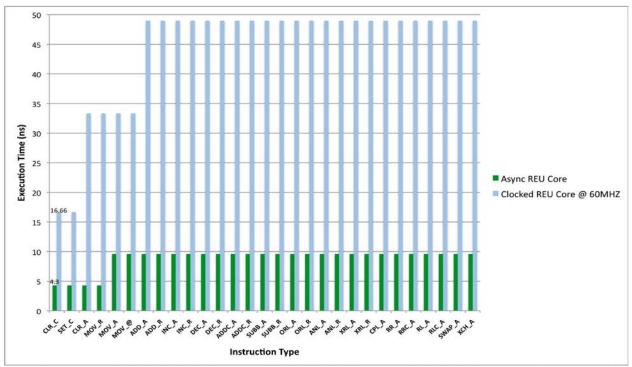

|----------------------------------------------------------------------|------|

| Figure 4.20: Execution Time vs Instruction Type                      | . 9( |

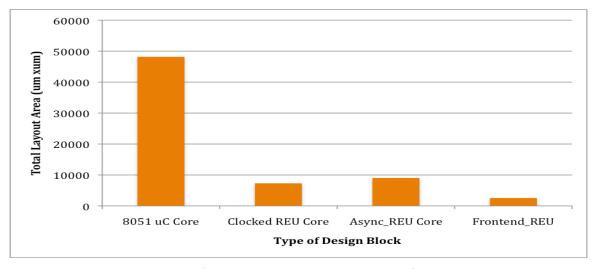

| Figure 4.21: Layout Area Comparisons                                 | . 91 |

#### **ACKNOWLEDGEMENTS**

I would like to sincerely acknowledge the valuable advice, guidance and constant support of my Advisor, Dr. M. H. Mickle throughout this research. I am deeply thankful to Dr. J. T. Cain, Dr. Y. Chen, Dr. S. P. Levitan and Dr. B. A. Norman, for their time, thoughtful inputs and valuable feedback.

This dissertation is dedicated to my mother, Dr. S. S. Kalpana. I would like to express my appreciation and thanks to my mother for her encouragement and inspiration throughout my PhD research. I wish to convey my special thanks to all my colleagues and friends for their support.

#### 1.0 INTRODUCTION

Wireless sensor networks (WSN) are generally made up of a set of autonomous multifunctional sensor nodes distributed throughout a specific environment for monitoring real world data. These sensor nodes are used to collect environmental data and transfer this data to the user through the network. Besides collecting raw data, a node may also need to perform computations on the recorded data, eliminating the need to transfer raw data to a central server for each measurement [1], [2].

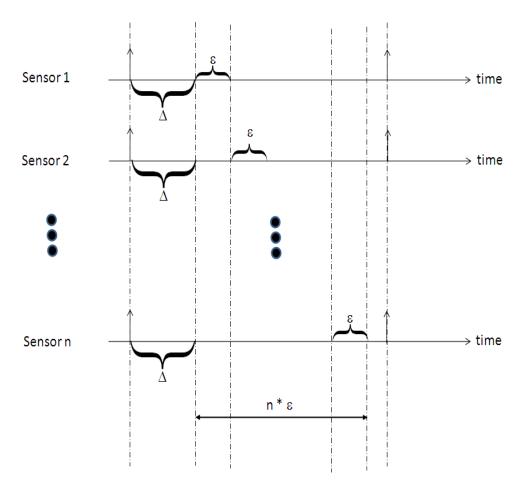

Consider a scenario with many raw sensor data readings that must be sampled simultaneously so as not to skew the measurements in time and correspondingly reducing the possible control bandwidth. The number of sensors required may be very large for some applications, e.g. environmental monitoring. By first principles, this situation is illustrated in Figure 1.1 for a set of n sensor nodes. In Figure 1.1,  $\varepsilon$  and  $\Delta$  represent the data transmit time from each sensor to the central server and the preprocessing or conditioning time for the data at the individual sensors done in parallel respectively. In many cases, the raw sensor data must be preprocessed or conditioned before being used in system calculations in order to reduce the transmitted data. The raw data readings are compared to a threshold value in order to determine whether this data needs to be transmitted or not. If the raw sensor data reading is above the threshold value, it is transmitted to the central server instantaneously; else an aggregate value is

transmitted that includes the current reading along with the other data readings below the threshold[1]. The transmission time (nɛ) especially in such a scenario is significantly reduced as opposed to preprocessing done at the central control where each and every sensor reading needs to be transmitted.

Figure 1.1: Timing Chart for a Sensor Network

This decrease in the amount of transmitted data in turn reducing the frequent radio transmissions is critical in increasing the power efficiency of the node [1]. There are many scenarios, in which the sensor data at each node is preprocessed or conditioned before the central server can further use it e.g. biomedical, physiological monitoring, environmental

monitoring, etc, [1], [2]. The main design constraint in such applications is the finite power budget for each wireless sensor node, as they require continuous and detailed monitoring over a long period of time.

### 1.1 OVERVIEW OF POWER TERMINOLOGY AND LOW POWER TECHNIQUES

Power has become a critical aspect in the design of modern processors and especially in wireless sensor devices such as embedded controllers, etc. The evolution of wireless devices with respect to size, weight, and battery life has enhanced their use in wider and more critical application spaces. For most portable devices, the integrated circuit (IC) components that form the digital processor are known to consume significant portions of the total system power [3]. High performance processors used in devices lead to the use of high clock frequency based designs that in turn lead to high power consumption. The IC typically dissipates power in the form of heat causing circuit degradation and operating failures. With the emergence of applications for battery-operated and battery-free portable wireless devices, thermal considerations and reliability issues increase and thus, there is a corresponding increased need for low power designs.

Power consumed by digital CMOS circuits can be broadly classified into two types: Static Power Consumption and Dynamic Power Consumption as shown in equation (1).

The power consumption equation is given as follows [3]:

$$P_{total} = P_{static} + P_{dynamic} \quad (1)$$

Static power ( $P_{static}$ ) also known as leakage power is consumed when the circuit is said to be inactive or static or in a non-switching state. The main source of static power is due to the leakage of current from supply rail to the ground via various paths in the circuit. The leakage current can arise from substrate injection, sub-threshold effects, tunneling effects, etc. Leakage power is also influenced by nanometer CMOS technologies.

Switching power and internal power together add up for the dynamic power consumption ( $P_{dynamic}$ ) of the circuit. Typically the dynamic power is dissipated when the circuit is active or in a switching state. Switching power dissipated is due to the charging and discharging of the load capacitance of the circuit. Internal power dissipated is due to the charging and discharging of the internal nodes of a cell. Also when both the PMOS and NMOS transistors are ON, short circuit current dissipates (short circuit) power that also contributes to the internal power consumption. Short circuit power is influenced by input transition times and the size of the transistors. For high performance systems, dynamic power is known to be the major portion of the total power consumption. The dynamic power can be described as follows [4]:

$$P_{dynamic} = C_L V_{dd}^2 f_{clk} \alpha + t_{sc} V_{dd} I_{peak} f_{clk}$$

(2)

Where switching activity is represented by  $\alpha$ ,  $C_L$  is the load capacitance;  $V_{dd}$ ,  $f_{clk}$ ,  $I_{peak}$ , and  $t_{sc}$  shown in equation (2) represent the supply voltage, frequency of the system clock, total internal switching current, and time duration of the short circuit current, respectively.

A short overview of low power design techniques is presented in the following paragraphs. The following circuit techniques are most commonly used to minimize the power consumption in wireless sensor nodes [5], [6].

A significant amount of a high performance processor's total power is being consumed due to the global clock that contributes to the dynamic power consumption. Asynchronous designs are increasingly becoming an integral part of numerous wireless sensor networks [7], [8], [9], [10] due to their low power advantages. These designs are characterized by the absence of any global periodic signal that acts as a clock. In other words, these designs do not use any explicit clock circuit, and, therefore, wait for specific signals that indicate completion of an operation before they go on to execute the next operation. Low power consumption, no clock distribution, fewer global timing issues, the absence of clock skew problems are the primary advantages of asynchronous designs over synchronous designs.

Power Supply Gating is also a low power circuit technique widely used to reduce the subthreshold leakage current of the system [11]. This process allows unused blocks in the system to be powered down in order to reduce the leakage current. This technique has been implemented in the Harvard sensor network system [12].

A subthreshold operation technique allows supply voltages ( $V_{dd}$ ) lower than threshold voltages ( $V_{th}$ ) to be used for lowering the active power consumption. This technique was first used in the complete processor design for wireless sensor networks at the University of Michigan [13], [14], [15].

#### 1.2 OVERVIEW OF RFID BASED SYSTEMS

#### 1.2.1 RFID Tag based Systems

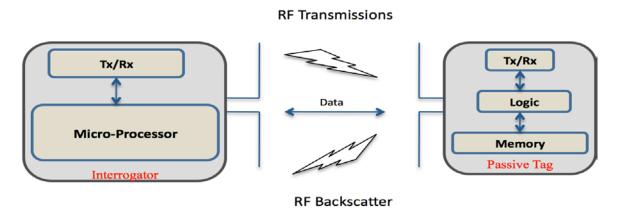

RFID has become a key technology for automatic identification systems as it ensures automatic, accurate and real-time information tracking and management. RFID systems consist of tag(s) and interrogator(s) equipped with antennas as shown in Figure 1.2 [16]. The basic function of an RFID system is to automatically identify a person or an object that is "tagged." In general, an RFID tag is mainly composed of a microchip, and an antenna, which is used for wireless data transmission. These tags, upon being queried by an RFID interrogator transmit data over the air to reply. The data exchange between an interrogator and a tag is through RF signals. RFID tags can be broadly classified based on their power source as Passive or Active tags. Active tags are battery powered for carrying out all their on-board processing and data transmissions. The read range of active tags is about 100m or greater, and these tags are priced at about \$20 or more. Passive tags are low cost and battery-free. Passive tags are powered by the impinging RF wave, which is also used for communication from an interrogator. The size of a passive RFID microchip is very small, about 0.4mm<sup>2</sup> [17], [18]. Low cost passive RFID tags are used in tracking, supply chain automation, contactless credit cards, human implants, mobile robotics, unmanned medical nursing, container safety, etc

One of the well-known small and inexpensive passive RFID tag varieties is the Electronic Product Code (EPC). EPC tags are low cost and are designed to identify objects using a unique code [19]. These tags have a small amount of on-board memory. They store an

index to point to a database that stores information related to the tagged object, such as what is on a barcode.

Figure 1.2: General Passive RFID System Architecture

The power consumption of a passive RFID microchip is one of the major limiting factors for read ranges of the tags. The basic design blocks of a microchip of an RFID tag consist of frontend, digital logic unit, and memory. The digital logic unit accounts for more than 35% of the power consumed by the entire tag [20], [21]. The input data decoding procedure, generally part of the tag frontend, is also a significant source of tag power consumption [22]. These tags use a high frequency clocked symbol decoder block to implement the decoding process.

#### 1.2.2 RFID Sensor based Networks

In general, deployment of conventional sensor networks for environmental monitoring is limited due to the active life span of the on-board non-rechargeable power source. The number of sensors required may be very large for such an application. The sensors are battery powered,

and there is overhead involved for the periodic maintenance of the battery-assisted sensors. There has been much research into prolonging the limited lifetime of WSNs through efficient circuit, architecture and communication techniques [5], [6]. In summary, the use of a WSN system is strictly limited by the battery life of the sensor nodes. RFID-based sensory systems, however are extremely useful for maintenance and deployment of many sensor units, but have the advantage of being battery-free. In addition to this advantage, the wireless characteristics and unique ID aspects of the RFID system are proving to be a great asset to WSN [23], [24], [25] for the development of WPSNs.

1.2.2.1 Wireless Passive Sensor Networks A WPSN is a non-disposable and cost efficient system that operates based on the incoming received power [23], [24], [26], [27], [28]. The concept to remotely feed a sensor node on the power from an external RF source has led to the emergence of WPSNs. This concept was first introduced to power a passive RFID tag. It is well known that passive RFID design blocks form the basis for passive sensor node architectures [29]. Passive sensor node operating frequencies fall under the same industrial, scientific and medical (ISM) frequency bands as most RFID applications. The latest trend in environmental monitoring applications is to have sensor nodes operating at power levels low enough to enable the use of energy harvesting techniques [30], [31]. This facilitates a deployed system, in theory, for continuous sensing of a considerable extended period of time thereby reducing recurring costs.

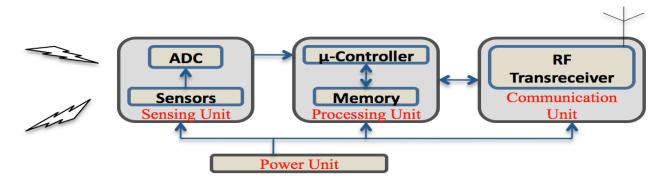

Building blocks of a typical RF based wireless sensor node architecture consist of a sensing unit, a communication unit, a processing unit and a power source as shown in Figure 1.3 [23], [27]. The components of a sensing unit, in most cases, include a sensor(s) and an

analog-to-digital converter (ADC). A sensor is a device generally used to measure some physical quantity such as temperature, light, etc. The ADC is used to convert the typical received analog data signal into a digital signal so as to be processed by the microcontroller. The processing unit consists of a low power microcontroller and a storage block. The choice of the processing unit depends on the type of the power source available to the node. The microcontroller processes data, controls, and coordinates other component functionalities. The communication unit consists of an RF transceiver module that transmits and receives data to/from other devices connected to the wireless network. In the case of a WPSN, the power unit mainly delivers the RF-DC converted power to the rest of node units and also stores additional power based on availability.

Figure 1.3: General WPSN Node Architecture

The major differences in the architectures of a conventional WSN node and a WPSN node are in the hardware of the power unit and the transceiver [23]. The power unit of the conventional WSN generally consists of a battery along with a support block called the power generator. The power unit for a WPSN node is basically an RF-to-DC converter-capacitor network. The converted DC power is used to wake up and operate the node or is kept in a

charge capacitor for future usage. A short range RF transceiver, typically a major power consuming unit on the node, is used in a conventional WSN as compared to a much simpler transceiver for modulated backscattering in the WPSN node [23], [32].

#### 1.2.3 Power Comparisons of passive RFID nodes

Table 1.1 presents a current overview of the power consumption of various types of RFID based passive nodes. The RFID tag based digital processor design reported in [33], [34] is a conventional fixed function IC that is implemented as a non-programmable state machine that responds with a hard-coded ID when queried by the interrogator. In [35], [36] the sensor integrated passive RFID tag has a fixed ID assigned to each sensor in order to support maintenance and field deployment of many sensors. The associated digital processor does not support any arbitrary computation and typically reports sensed data in addition to the RFID tag functionality.

WISP (Wireless Identification and Sensing Platform) is a battery-free sensing and computation platform that uses a low power full programmable microcontroller for enhanced functionality of the RFID tag based sensing [37], [38]. In [37], [38] the wireless passive RFID sensing design is compliant with the UHF RFID interrogator. Table 1.1 clearly illustrates the significant increase in power consumption from a typical RFID passive tag to the computationally enhanced passive RFID nodes. In [24], a general-purpose low power 16-bit programmable microcontroller (MSP430F2132) is used for managing the entire passive node. But the use of full microcontrollers is known to consume significant amounts of power especially in the context of passive sensing.

Table 1.1: Power Comparisons of passive node based on their functionality

| Reference           | Full-Design<br>Type                         | Power (µW) | Comments                                                                     |

|---------------------|---------------------------------------------|------------|------------------------------------------------------------------------------|

| Man (2007) [33]     | Passive RFID Tag                            | 3.436*     | Process: 0.18µm<br>Voltage: 1.8 V                                            |

| Yang (2010) [34]    | Passive RFID Tag                            | 0.963*     | (*Baseband processor)  Process: 0.18µm  Voltage: 1.1V  (*Baseband processor) |

| Cho (2005) [35]     | Passive RFID Tag-Temperature & Photo Sensor | 5.1        | Process: 0.25μm<br>Voltage: 1.5 V                                            |

| Jun (2010) [36]     | Passive RFID Tag-Temperature<br>Sensor      | 6*         | Process: 0.18μm<br>Voltage:0.8 V<br>(*Baseband processor)                    |

| Joshua (2006) [37]  | Passive RFID based Sensing platform-μC      | 5400**     | 6MHz, 3V<br>(**Microcontroller)                                              |

| Alanson (2007) [38] | Passive RFID based Sensing platform-μC      | 846**      | 3MHz, 1.8V<br>(**Microcontroller)                                            |

#### 1.3 STATEMENT OF THE PROBLEM

Passive RFID technology is becoming increasingly common in different environments such as home, office, industry, hospitals, library, etc enabling quick and anytime access to real-time data on uniquely identifiable passive nodes throughout their entire lifetime. Passive RFID based sensor nodes such as passive RFID tags and WPSNs mainly deal with the collection or storage of data, and transmission of that data back to the interrogator. The interrogator primarily collects and processes the data sent by the nodes. Such nodes are typically not programmable, as they have conventional fixed function IC's as their digital processors. This restricts the computational flexibility available to the node.

WPSN being an emerging research area; there is little documentation on all the power efficient scenarios applicable to passive sensor devices. In [23], [24], [26], [27] efficient antenna designs, low-power transceivers were introduced for WPSNs. But it is not only important to have energy efficient front-end and power unit designs, there is also a need to have low-power novel processor designs that allow greater ranges for WPSN nodes. In the context of having preprocessing done at the sensor side, existing computationally enhanced nodes are known to consume considerable power as mentioned in Table 1.1. This limits the performance of an RFID system especially with respect to operating ranges. Thus, to create low power passive RFID based nodes either to fit the need of any particular class of applications or as a standalone, it is desirable to remove or reduce as many of the power consuming characteristics as possible.

Low power IC design optimizations can be achieved at various levels, such as the algorithm-level, the architecture-level and the circuit-level. The research vision of this dissertation is to build a new generation of architectures for low power applications most of which are derived from new notions of distributed computing. Generally, distributed computing is mostly interpreted as multiple cores and processors. Serial, single thread processing is not viewed as distributed other than in data flow chains with proximate hardware elements.

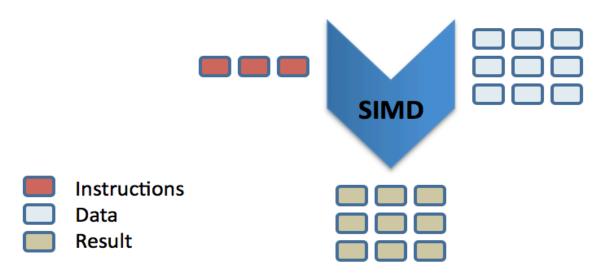

Single Instruction Multiple Data (SIMD) is a well know class of parallel computers in Flynn's taxonomy [39]. SIMDs have the ability to perform the same operation on multiple data simultaneously for processors with multiple processing units. Synchronisation between processors is not required. SIMD processing is also a form of vector processing. An add operation in a traditional scalar processor would produce a single result by adding up one pair of

operands. In a SIMD processor, a single add operation produces multiple sums of independent operand pairs on different processing units. Figure 1.4 represents the inherent parallelism in a SIMD processing flow.

Figure 1.4: A SIMD Processing Flow

Applications where a single sample produces multiple values, which are operated on at a large number of data points can take advantage of the SIMD architecture. Due to the higher level of parallelism available in SIMD architectures, instructions can be simultaneously applied to all of the data in the processing units within a single operation. Such a conventional SIMD class of processor architecture typically has wired implementation of multiple processing units that execute the same instruction sequence on different data items. The reconfigurability and scalability of processing units in such wired SIMD implementations are not convenient.

This research, however, will distribute single thread processing to a wirelessly connected digital processing core of a passive node executing sequential instructions as a single

thread paradigm. A conceptual distributed architecture with a reduced instruction set, combined with low power circuit techniques, will be introduced and investigated with the goal of reducing the power consumption of the system. These low-power considerations for the processing core will also be based on factors such as target application and trade-offs that can be made as long as the functionality required of an application is met within a given time constraint. There is a need for novel architectures that take into account such factors, especially for passive device applications.

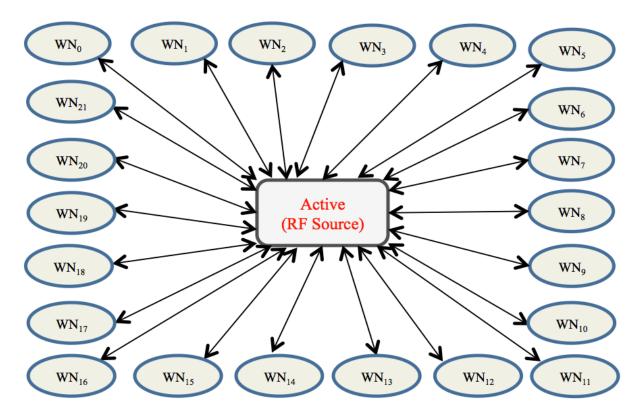

The low-power distributed architecture will consist of splitting the processor architecture of a node into two basic design blocks to support multiple remote passive processors with wireless reconfigurability. Each of the multiple passive processors is represented as a wireless node (WN), in Figure 1.5. The digital processing core of the WN will be the remote execution unit (REU), which will consist of instructions that provide basic flexibility in manipulating data. The other block forms the interrogator (active block), which will act as the control unit for the REU that supports the types of instructions such as decision, branching, etc. The WN will wirelessly execute instructions issued by the interrogator. In this scenario, the program to be executed by the WN will be stored in the interrogator and the commands will be transmitted to the REU one at a time. The interrogator remotely sends instructions to the WN, which are accordingly executed and corresponding results are communicated back to the interrogator. Thus, the interrogator and the REU based node combination can be viewed as a complete processor or as multiple processing units (nodes) forming a wireless SIMD distributed architecture class of processor systems.

Figure 1.5: Wireless SIMD Network Architecture

The wireless SIMD distributed processor architecture allows for a flexible wireless reconfigurability and scalability of the number of processing units as opposed to a conventional wired SIMD system. In other words, the REU based node lends itself a distributed architecture based remote node processor(s), which can be replicated to produce a wireless SIMD distributed processor system.

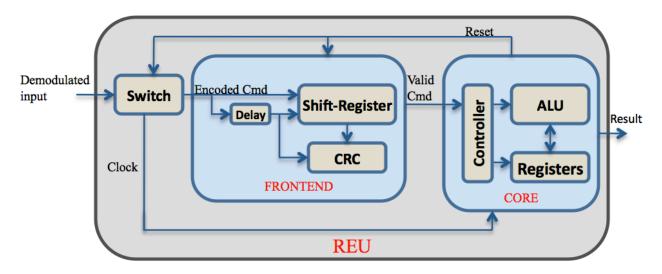

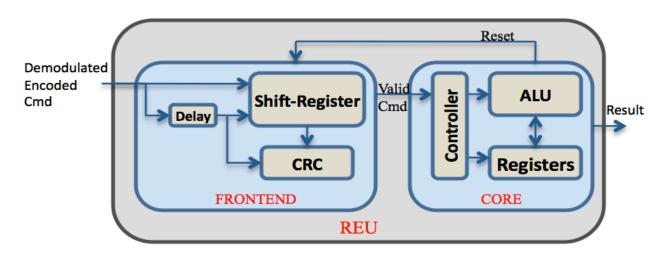

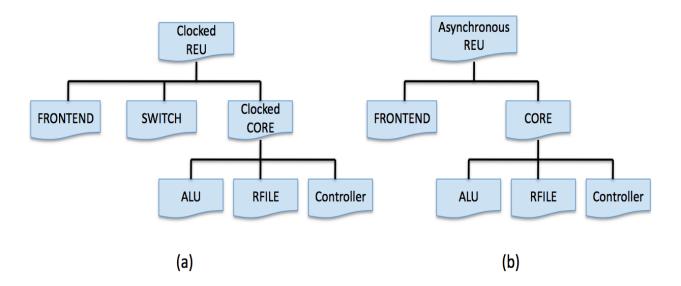

As part of the dissertation research, the REU will be implemented in two ways to allow comparison especially with respect to power consumption, speed and area. Both the implementations will consist of a frontend block for RF communication and a core block as an execution unit. The frontend block will be used to decode the input command and check for

validity of the received command. Both the REU versions will have the same frontend implementation; the major implementation with the difference being the core design. The first REU core implementation will be a clocked design that executes instructions based on clock pulses provided wirelessly by the interrogator at essentially any frequency from DC to the limit of the wireless medium or the technology implementation of the REU. The other REU core implementation will be an asynchronous design that uses no explicit clocking mechanism. Both the asynchronous and the clocked REU designs will be implemented using clocked CAD tools.

In summary, the main objectives of this dissertation are (1) to develop a low power programmable REU core design of the node processor as a wireless distributed architecture that operates remotely from the interrogator, and (2) to implement both the asynchronous and the clocked REU core designs and correspondingly investigate for comparison of their respective power consumptions.

#### 1.4 OUTLINE OF THE DISSERTATION

- ➤ Chapter 2 introduces the distributed processor architecture concept. A sample instruction sequence flow between the interrogator and wireless node (REU) is presented for illustrative purposes using 8051 instructions.

- ➤ Chapter 3 describes the proposed high-level architectures for the clocked and the asynchronous REU designs that include the individual REU front-end and the REU core.

This chapter also presents the 8051 subset of instructions chosen for REU design and associated concepts needed for the implementation of the REU architecture.

- Chapter 4 presents the high-level design flow using clocked CAD flows that were used to design, synthesize, and implement the clocked and the asynchronous REU logic. It elucidates the modifications to the traditional clocked CAD flows in order to implement the clock-less modules of the REU design. This chapter also presents the post-layout simulation and verification results of the frontend, core and the entire REU. It also provides a comparison of power, area and speed for both the clocked and asynchronous REU core implementations.

- ➤ Chapter 5 presents the conclusions and future directions of the dissertation research.

#### 2.0 WIRELESS DISTRIBUTED PROCESSOR ARCHITECTURE CONCEPT

#### 2.1 THE ARCHITECTURAL EMBODIMENT

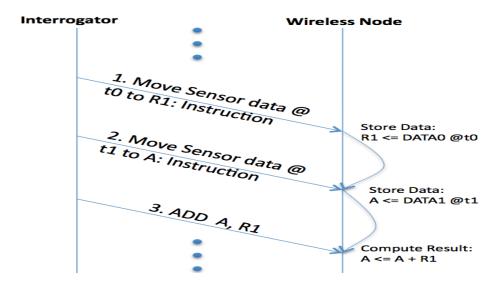

Conventional processors have basic blocks such as Control, Memory and ALU connected and hard wired as a single processing unit. A conventional processor is basically distributed into blocks to support multiple remote passive processors with wireless reconfigurability. A wireless SIMD distributed architecture concept for low power applications is introduced in this section. The distributed architecture of a conventional processor consists of two blocks namely an active block and a WN block as shown in Figure 2.1. Active implies a battery or wired power source. The active block (also known as the C&M (control and memory) unit) is always connected to the power supply. This block contains major components such as the control and storage units that are larger in size and/or consume a considerable amount of power (for example: Controller, RAM, ROM, etc). The design of the C&M block can be very flexible as it can be designed as a synchronous design block due to constant power being supplied to it. The core of the passive block consists of a digital processing core is the REU. This block is not connected to any power supply instead uses power extracted from the incoming RF signal from the active block. Both the blocks communicate thru RF signals as they can be efficiently transmitted through free space. The RF modulated signal from the active block is demodulated for incoming commands, and the output is the simple modulation of the backscatter from the antenna.

Figure 2.1: Proposed Distributed Architecture

#### 2.2 AN APPLICATION SCENARIO

In an RFID based system, the active block acts as the interrogator and the WN acts as the passive tag. A typical RFID interrogator wirelessly transmits commands to the remote passive RFID tag, which then executes these commands and responds back to the interrogator [40]. Passive RFID tags typically use Application Specific Integrated Circuit (ASIC) design to provide logic to respond to commands from an interrogator. The commands from the interrogator can be viewed as instructions issued to a digital computer [41]. Thus, the interrogator and the tag combination can be viewed as a complete processor or as multiple processing units. This will form the basis of the proposed distributed concept.

The Control and Memory (C&M) is an RF equipped control and storage block and the WN block is an REU with minimal storage capacity. The first block is allowed the flexibility to

overall be a classical von Neumann or Harvard type architecture. Commands stored on this block are transmitted wirelessly to the REU. The intent is to keep the REU block as simple as possible so as to maintain low power requirements and/or an effective read range from the C&M. Any unnecessary complexity on the passive REU will be moved onto the C&M powered block. One of the main power reduction techniques employed in the proposed REU design is to eliminate the need for a clock. The execution rate of the remote processor is to be controlled by the C&M block (interrogator).

The focus of the current research is the elements and concepts of the design of a passive execution unit that operates remotely and wirelessly from the C&M. The low-power distributed architecture will provide the basis for a passive reconfigurable processor with multiple execution REU's [42], [43]. This is a classical single instruction multiple data processor architecture as with the ILLIAC [44]. This distributed architecture has the potential for developing low power applications in sensor networks, radar, digital signal processing, instrumentation, measurement, medical electronics, embedded systems, etc.

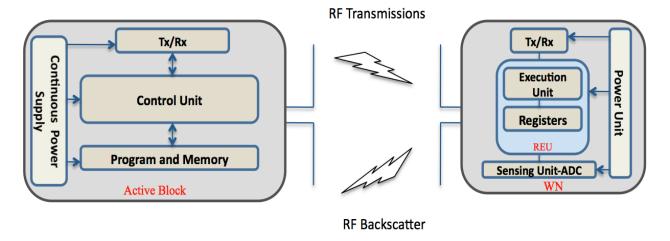

A basic state diagram for an RFID tag-Sensor node is shown in Figure 2.2 [35]. Such nodes are generally used in environment monitoring, traffic control, battlefield surveillance, etc. This RFID tag-Sensor node basically uses an RFID type unique code assigned to each sensor to enhance the wireless environment monitoring support and deployment procedures. The basic states of this type of transponder are On, Interrogating and Active. Upon receiving the energizing RF field, the transponder enters the On state. On request from the base station, the transponder enters the Interrogating state, and the demodulator and the decoder are activated to

enable the respective blocks. The basic blocks of the transponder include the ROM and the sensor block. The sensor and the ROM blocks are enabled exclusively by the command from the central server (interrogator) for power management [35]. There can be multiple sensor blocks based on the different types of sensors needed for an application. Finally, in the active state, the selected functional block is enabled and the requested information is sent back to the interrogator. The number of RFID tag-Sensor nodes may be very large in applications such as environmental monitoring and, hence, it is important for the nodes to be able to successfully send all the measured data to the interrogator avoiding collisions. The RFID (tag/interrogator) interface acts as a serial bus that travels through the air. In a wired serial bus application, bus contention is prevented by arbitration. The RFID interface also needs arbitration so that only one node transmits data over the "bus" at one time. Current RFID protocols use many existing collision prevention methods that make sure that only one tag communicates at one time [54].

Figure 2.2: State Diagram of a (RFID tag-Sensor) Transponder

Wireless nodes basically sense specific aspects of a region in which they are deployed and occasionally send sensed data to the requested, interrogator. The sensed data generally contain errors due to many factors such as resource constraints and environmental factors. Therefore, the interrogators cannot rely on single-sensor data sensed at a point of time. Data redundancy is another issue with the data sensed by various sensors. Hence in many applications the aggregated form of sensed data from single or multiple sensors over time is preferred [2]. Finding average temperature, velocity, location, pressure, etc., are well-known examples in many applications. When interrogators require an aggregated form of sensed data, performing computation of the sensed data and sending its aggregate reduces the communication overhead [45]. Existing RFID Tag-sensor nodes typically do not have any programmable arithmetic processing capabilities [35]. Adding lightweight computational elements based on the target application can enhance the wireless node.

Sensor networks employ preprocessing at the node so that every sensor sample need not be transmitted on the radio therefore not consuming all the wireless bandwidth available to the network. Transmission of only necessary sensor data readings over the radio saves the available stored energy on the node. The focus of this dissertation is on low power solutions to wireless passive sensor node processor architectures based on 8051 instructions. The choice of the 8051 is justified by the fact that it is still one of the most popular embedded processors [46], [47], [48], [49]. Furthermore, due to its small size and low cost, it has numerous applications where power efficiency is necessary. The 8051 microcontroller most commonly used in wireless nodes is considered as an example for exploring its ISA and its application to the proposed distributed

processor design concept. Using the 8051-ISA based customization of the REU architecture as part of the distributed architecture is illustrated in the following paragraphs.

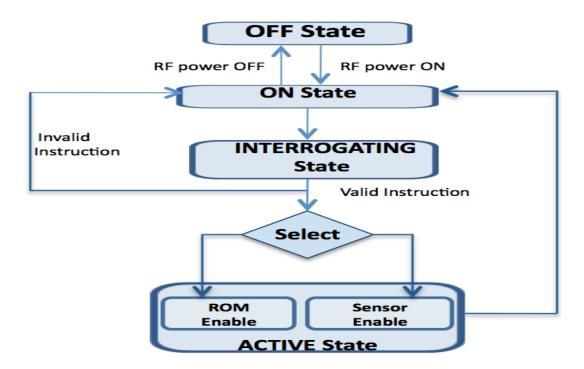

Consider a simple communication scenario between the interrogator and the node for the aggregation of sensor values at the node using an 8051 instruction [50]. The amount of temporary storage and the ALU capabilities of the WPSN node processor will be chosen to maintain low power requirements. Assume a 8051 default register bank (R0-R7) as the temporary memory space available for the execution unit. The major function is an ADD operation and, hence, the choices of the arithmetic instructions that would be part of the REU on the passive node are ADD A, Rn and/or ADDC A, Rn. The minimal data transfer instruction necessary would be the MOV A, Rn; MOV Rn, A and MOV Rn, #DATA (8-bit). The passive node processor will support only those features required to interface and communicate with the interrogator. Therefore, the branch, comparison, load and store instructions compatible with the i8051 ISA will be implemented on the interrogator side rather than on the passive side.

Consider an ADD operation: ADD A, R1 (A = A+R1), where R1 denotes one of the eight (R0-R7) 8-bit 8051 working registers for a selected register bank and A denotes the 8-bit accumulator register. Figure 2.3 represents a high-level sequence diagram for an ADD operation. Let the sensed data be stored in any of the sensor registers that could be any one of the (R0-R7) directly mapped to the sensor. The interrogator sends out instructions to transfer the sensed data stored in the sensor register to the R1 (assuming not a sensor register) and A registers respectively. These 8051 working registers along with the accumulator form the temporary storage on the REU processor. On receiving the ADD instruction, the passive node

processor (REU) performs the addition operation on the already existing value in the accumulator and the new R1 value. The computed result is stored in the accumulator register. Alternatively, the tag could then be instructed to send the result back to the interrogator in a register to memory transfer where the register is mapped as a transmitting buffer. The interrogator serves the role of main memory for storage of large data items. Loads (reads) and stores (writes) are performed by the interrogator and tag communicating data values using the over-the-air protocol. The C&M node will contain main memory that acts as the major storage area for the majority of data items.

Figure 2.3: Sequence diagram for an ADD operation

Sensor applications require special purpose hardware suitable to cater to a different set of requirements. It is necessary to explore the instruction architecture space in order to enhance the capability of the execution unit depending on the application. Characteristics of the target applications and the utility of the sensors make it important to choose applicable hardware for sensor networks on a case-by-case basis. Some of the well-known basic core algorithms form a

class of simple applications such as the sum-array (aggregation of all values in a list), Top10 (finds top 10 values in a list), majority consensus (finds the majority values in a list), min-max finder (finds minimum and maximum values in a list), Binary search (typical search algorithm for a sorted list), Matrix Multiplication (matrix multiplication for small size matrices), etc. [50]. To arrive at an energy efficient processing solution on a sensor node, there are always communication/computation tradeoffs. Hence, the choice of a design for sensor node architecture not only depends on the various power management techniques, but also on the application space.

The procedures to choose the components and the associated instructions based on the 8051 architecture illustrated in this chapter can be used to generalize and extend these concepts to any microprocessor ISA such as the Motorola 6800, Intel 8085, etc. In summary, the distributed architecture components, especially the ones in the passive cell, need to be based on the target application requirements. Once the application requirements are determined, the ISA of the target architecture can be selected for the implementation of the distributed architecture. A minimal set of instructions based on the corresponding minimal register (ROM/RAM) storage can be chosen to form the target ISA. Because these instructions are dependent on registers of the target architecture, it is necessary to choose only the required registers, which can be part of the passive cell, providing maximum flexibility. Therefore, determination of the right combination of different factors blending into a distributed design will decide the power requirement of the passive cell based on the application. The next chapter introduces the proposed low power REU designs based on the 8051 ISA that form the passive cell architecture.

#### 3.0 PROPOSED LOW POWER REU ARCHITECTURES

This chapter presents the major contributions of this research: a novel data-driven symbol decoder and minimal 8051-instruction set based computation unit. The proposed decoder and computation unit form the basis for the REU frontend and the REU core architectures respectively. The input instruction is an encoded bit sequence that will have command bits (Opcode) as well as data bits. The command bits instruct the processor to perform a specific operation on the input data bits. A data-driven CRC block is used as part of the frontend to check the validity of the received instruction. The frontend consists of registers and delay elements that are used to decode and store the received encoded instructions. The basic necessary set of instructions supported by the REU based on the target application is defined as the minimal ISA (MISA). The core unit is based on a MISA compatible with the 8051 ISA. The REU core consists of an 8051-compatible ALU unit and controller and requires a minimum number of temporary storage registers to support the selected 8051 instructions.

Both the data-driven symbol decoder design and the computation unit designs can be independently used for various wireless applications such as RFID, WPSN, etc. A potential architecture for combining the data-driven decoder design and the execution unit to form the low power REU will be established in this chapter. The motivation for low power design choices and details of individual REU components will be also described in the following

sections. The major focus of this chapter will be to introduce the design philosophies, and elements of the REU architectures that have been implemented as custom asynchronous and clocked digital designs to reduce power requirements.

# 3.1 REU FRONTEND

#### 3.1.1 Motivation

Wireless serial data transfer environments are always prone to noise and transmitter-receiver synchronization issues especially over long distances [51]. The synchronization issues in general concern the need for the receiver to use the same clock frequency as the transmitter in order to accurately detect the transmitted data. In modern data transmissions, all traditional receivers extract the original data from the encoded bit stream using an explicit clock. This clock is extracted from the transmitted data, or is separately generated using additional circuitry [35], [52].

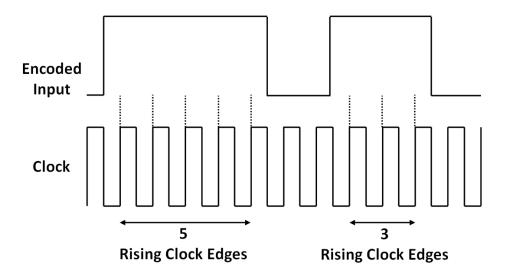

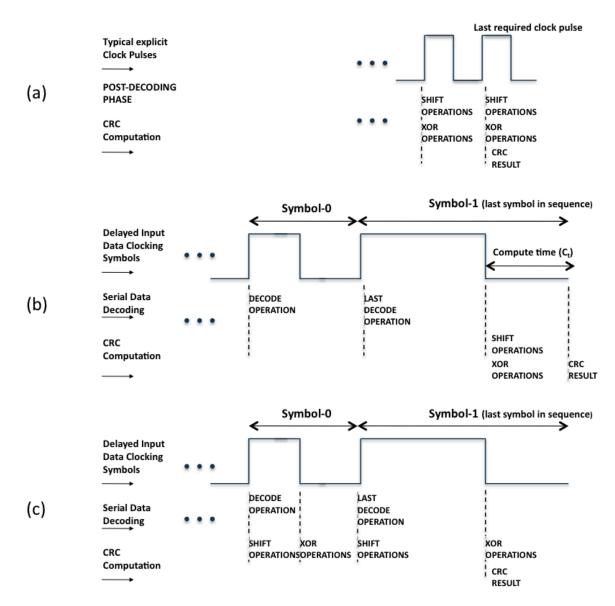

Manchester encoding and variable pulse width encoding techniques are very widely used in wireless digital transmissions [53], [25]. For example, a variable pulse width encoding technique is currently used in passive RFID tags [54]. Oversampling with a clock is a classical decoding process for pulse width modulated signals [35], [52]. The demodulated input to the decoder is the pulse interval encoded data that are converted to the regular binary symbols at the decoder output. The conventional decoding scheme is shown in Figure 3.1.

Figure 3.1: Conventional Decoding Scheme

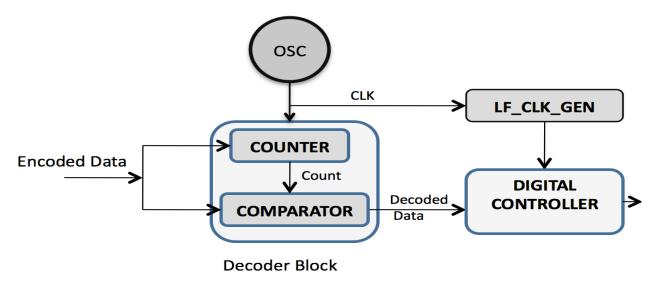

The conventional decoder block represented in Figure 3.2 is a part of the conventional RFID tag frontend architecture [35], [52]. The decoder mainly consists of counters, registers, comparators, and a high frequency oscillator. This decoder is explicitly driven by a high frequency clock of several MHz. The demodulated input is converted to a series of binary symbols '1' 's and '0' 's by comparing the number of clock pulses occurring in each symbol period. In Figure 3.1, when the symbol period is high, '1' is identified based on the occurrence of five (5) clock pulses whereas '0' is identified based on the occurrence of only three (3) clock pulses. A typical data rate of 40kHz, corresponding to a symbol period length of 6.25µs, is considered as an example [54]. The decoded data are fed back to a digital block which actually runs at a much lower frequency range of about 40kHz - 640kHz [52]. Hence, a low frequency clock generator is required to convert the high frequency clock of several MHz to a low frequency clock to drive the digital backend of the tag. Such high frequency operations consume considerable amounts of power [33], [55].

Figure 3.2: Conventional Decoder block of a passive RFID Tag

The next section introduces a novel pulse width-coding (PWC) scheme for low power applications. The symbol width properties of the PWC scheme allow the traditional decoder at the receiver side to be replaced with a low-power data-driven decoding circuit. The major advantages of the proposed PWC scheme include minimal decoder hardware, synchronization among the transmitter, receiver, and low-power decoder. The low-power PWC scheme can be applied to various wireless passive device designs such as passive tags, passive sensor nodes, etc.

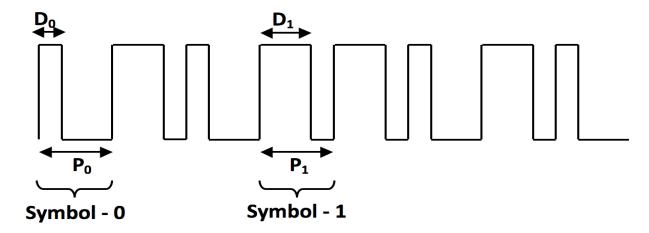

# 3.1.2 Pulse Width Coding Scheme

The PWC scheme represents symbol-0 with a square wave (with time period  $P_0$ ), which has a pulse width  $D_0$ , and symbol-1 with a square wave (with time period  $P_1$ ), which has a pulse width  $D_1$ , where  $D_0 \ll D_1$  and  $P_0 = P_1$ . Figure 3.3 represents an example 8-bit input symbol data stream "01011010" in the proposed PWC encoded format. From Figure 3.3,  $P_0$  and  $P_1$

represent time periods of symbol-0 and symbol-1, respectively. Each of symbol-1 and symbol-0 occupies an active time span (i.e., pulse width interval) equal to that of  $D_0$  and  $D_1$ , respectively. The PWC decoding mechanism is described in the next section.

Figure 3.3: Pulse Width Encoded Data

# 3.1.3 PWC Decoding Mechanism

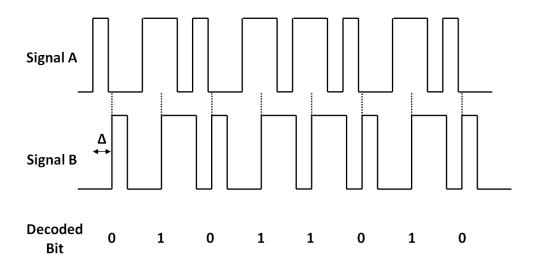

The received waveform after demodulation results in an encoded digital data stream as shown in Figure 3.3. The proposed PWC decoding scheme is shown in Figure 3.4 using the encoded symbol data "01011010" as an example. The encoded data can be decoded by sampling (Signal A in Figure 3.4), with the same encoded data stream delayed by time  $\Delta$  (Signal B in Figure 3.4). In other words, Signal A (PWC encoded data) represents the input demodulated serial data representing the symbol data stream "01011010". The Signal B is the delayed version of the incoming PWC Signal A. The rising edge of Signal B is used to sample the incoming Signal A. It can be clearly seen from Figure 3.3 that the first decoded output binary bit is "0", second decoded binary bit is "1" and so on. At the rising edge of Signal B, the decoded bit is "1",

whenever both the signals occur (i.e., especially symbol-1). Hence for the above-mentioned Signal A example, the output binary decoded bit sequence is "01011010". For successful PWC decoding, it is necessary to have  $D_0 < \Delta < D_1$ . One possible way of reduced power consumption is by minimizing the value of  $D_0$ , which minimizes the delay circuitry in particular.

Figure 3.4: PWC Decoding Scheme

# 3.1.4 Data-Driven Decoder Design

This section introduces a data-driven decoder design to perform the PWC decoding. The term 'data-driven' is used to indicate that the decoder is solely driven by the input data and, hence, eliminates the need for any typical external clock driven mechanisms.

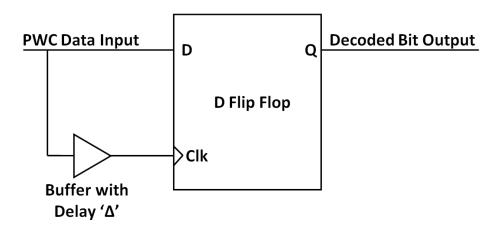

To implement the data-driven decoder as a digital circuit, the required components are a D flip-flop and a delay buffer. The demodulated encoded data stream (Signal A in Figure 3.4) is connected to the input terminal of a traditional D Flip-Flop, and the same encoded data

stream delayed by time  $\Delta$  (Signal B in Figure 3.4) is connected to the clock input. This is shown in Figure 3.5. It is clear that the input encoded data is sampled at every rising edge of the delayed version of the same encoded data in order to distinguish '1' and '0'. The incoming encoded data is decoded by data driven element shown in Figure 3.5 and corresponding decoded data is stored in a shift register following the decoding. This is a data driven mechanism that eliminates use of high frequency clock signals to decode the incoming data stream largely reduces the dynamic power consumption [56], [57].

Figure 3.5: Data-Driven Decoding Element

A potential application for the data driven decoding scheme is in Gen-2 RFID systems [54]. These RFID systems currently use a variable pulse interval encoding to represent symbol-0 and symbol-1 [54]. The proposed decoding circuit will reduce the power consumed at the receiver while the encoder design remains unchanged at the transmitter.

The proposed decoding scheme illustrated in Figure 3.4 uses a self-clocking mechanism eliminating the use of an external clock [56]. This scheme basically uses delayed input data to

drive the decoder components such as a shift register, etc. In other words, the delayed input data acts as a clock to trigger components of the decoder.

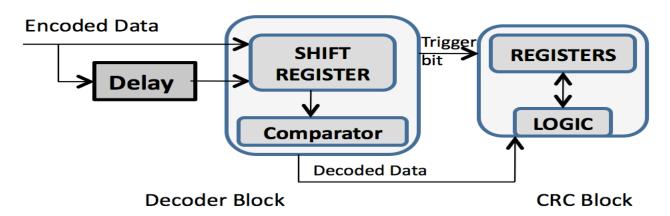

The block diagram for the proposed data-driven symbol decoder is shown in Figure 3.6. The decoder architecture consists of a shift register, comparator and a delay block. The delay in hardware generally translates to a buffer element. A buffer element is typically built using an even number of inverters. The proposed data-driven architecture eliminates the use of high frequency driven counters and a high frequency oscillator, which are typically used in the conventional decoder as shown in Figure 3.2.

Figure 3.6: Data-Driven Decoder-CRC Unit

The simulation results have shown that the data-driven decoder consumes considerably less power when compared to the conventional decoder design [56]. These dynamic power consumption simulation results of the data-driven decoder and the conventional decoder were 58nW and 9195nW respectively. The data-driven decoder forms the major part of the REU

frontend. The detailed implementation and the design methodology of the decoder as part of the REU frontend are presented in Chapter 4.

#### 3.1.5 REU Frontend Architecture

Main Features of the Frontend Design are as follows:

- Data-Driven Decoder-CRC-16 block forms the REU frontend design. This block uses

the low power self-clocking mechanism to decode the incoming instruction and check

for validity of the received instruction.

- 2) The REU design supports two types of instructions based on 8051 MISA:

- a. 25-bit Input Frame: LENGTH (1-bit)-OPCODE (8-bit)-CRC (16-bit) and

- b. 33-bit Input Frame: LENGTH (1-bit)-OPCODE (8-bit)-DATA (8-bit)-CRC (16-bit)

- 3) Supports a counter-less Variable-Length Instruction Identification algorithm implementation.

The data-driven decoder-CRC implementation as shown in Figure 3.7 consists of a shift register of bit width 'n' that is used for decoding and storing the decoded input data stream. Here, 'n' is a function of the data width and the CRC length used for the input data stream. The encoded data are sampled at the rising edge of the delayed data in order to generate decoded bits, which are stored in the shift register and correspondingly used in the CRC check.

Figure 3.7: REU Frontend Block Diagram

Counters typically are used to keep track of the number of shifts especially in designs using shift registers. Counters in RFID symbol decoders are also used to count the number of clock pulses, which provides the basis for accurately decoding the incoming encoded data. Elimination of the counter hardware for low power needs alternate mechanisms to identify whenever the shift register is full. In the proposed architecture, an additional single-bit is added to the register and is the only additional hardware required to indicate that all the decode data have been successfully loaded into the register and is ready to be used for the next operation. Traditionally, all the flip-flops (registers) in a shift register are reset to '0'. In the proposed n-bit shift register design; the 0<sup>th</sup> register bit is reset to bit '1', and all the remaining bits are set to '0'(assuming left shift). When the content of the extra register is bit '1', then the n-bit shift register is considered full. The only modifications needed to keep track of decoded data are: an extra 1-bit flip-flop (register) and the reset sequence to initialize the n-bit shift register. This forms the n-bit register in the decoder design.

A pseudo-code is used as an example to differentiate the (25-bit and 33-bit) widths of the incoming instructions at the Frontend an algorithm along with an illustration of the abovementioned decoding process. Once the shift register indicates it is full, the decoded data are checked for correct message transmission to the intended receiver. For variable instruction length inputs, the following algorithm is introduced.

# Counter-less Variable-Length Instruction Identification Pseudo-code

Reset values:

On the rising edge of delayed data (data\_clk), each decoded bit is stored in register "reg". The 'reg' width is 34 (reg(33 downto 0)) at it included the storage space for the 33-bit instruction and extra bit. After decoding of every bit, the following pseudo-code is executed:

```

if (rising\_edge \ of \ data\_clk) \ then \qquad // check \ trigger \ edge if (len\_detect8 = '0' \ and \ len\_detect16 = '0') \ then \qquad // \ check \ flag \ status if (reg \ (1 \ downto \ 0) = "11") \ then \qquad // \ check \ register \ start \ bits len\_detect16 <= '1'; \qquad // \ set \ flag \ to \ identify \ 16-bit elsif (reg(1 \ downto \ 0) = "10") \ then \qquad // \ check \ register \ start \ bits len\_detect8 <= '1'; \qquad // \ set \ flag \ to \ identify \ 8-bit end \ if; end \ if; end \ if;

```

The "len\_detect8" and "len\_detect16" are flags which are set on the first occurrence of "10" and "11" in the decoder register that stores the decoded input bit stream respectively. These flags are used to differentiate the two instruction lengths. The first bit in "10" represents the reset value of decoder register, reg(0), and the second bit '0' indicates the opcode instruction length (25-bit). Similarly, the first bit in "11" represents the reset value of the decoder register reg(0) and the second bit '1' indicates the opcode-data instruction length (33-bit). Once the length of the instruction is known, the different fields in the input instruction can be easily identified and processed accordingly. Only one of the two flags (either len\_detect8 or len detect16) is always high during every instruction execution process.

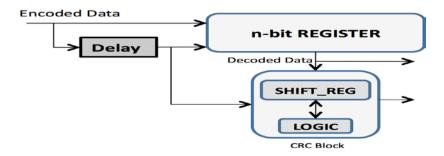

In a traditional CRC hardware implementation, a simple shift register in combination with XOR logic performs serial CRC computations on an input serial data stream. The typical CRC design computation flow is shown in Figure 3.8 (a). This clocked decoder-CRC block is considered part of the frontend of an RFID passive tag and is known to consume a significant amount of power [55], [56].

Typically, a combinational design logic implementation of a CRC consists of simple registers (Flip-Flops) and XOR gates. The final CRC result is computed based on the initial value (seed), decoded data and the intermediate CRC values. The decoded data and the appended CRC are stored in the n-bit register; the initial CRC value is stored in a seed register that is also used to store intermediate CRC values. In the context of a CRC design block implemented as a combinational logic in the proposed architecture, the CRC block is triggered

after the completion of the decoding process. The combinational CRC design computation flow for the data-driven decoder is shown in Figure 3.8 (a).

Figure 3.8: Design Computation Flow (a) Traditional clock-driven CRC (b) Data-Driven Decoder-Combinational CRC [56] (c) Data-Driven Decoder-CRC [57]

For the RFID clocked tag decoder and the data-driven decoder, the CRC computation for error detection check is performed only after the demodulated data are decoded and

available for use. The clock-driven process requires extra clock cycles to drive the CRC circuit in addition to the cycles used for decoding each bit. Implementing the CRC design as a combinational block increases the complexity of the design as 'n' increases. Computing CRC after data decoding further slows down the processing speed of the frontend block of the target wireless device such as an RFID passive tag.

The novelty of the proposed data-driven CRC implementation is the ability to take advantage of specific encoding properties of the input sequence in order to realize a self-clocking CRC at the passive receiver side for low power applications. The proposed frontend design consists of an n-bit register for decoding and storing the incoming data and a typical 16-bit register for performing CRC computation on the decoded bits. A data-driven implementation uses the delayed input encoded data as a clocking signal in order to sample the input data [56].

At every rising edge (signal going high) of the delayed encoded signal (also termed as delayed input data clocking symbols as in Figure 3.8 (b) and (c)), the encoded symbol is sampled, decoded and stored in a 1-bit flip-flop (register) as shown in Figure 3.7. At the same rising edge, typical CRC-CCITT fixed shift operations are performed on the 16-bit seed CRC register. On the falling edge (signal going low) of the same delayed encoded signal, the basic set of typical XOR operations are performed on the stored decoded bit obtained at the rising edge of the same symbol and/or intermediate CRC operations. This final computed CRC value is updated to the CRC output register. The proposed data-driven CRC computation flow has been illustrated in Figure 3.8 (c) [57].

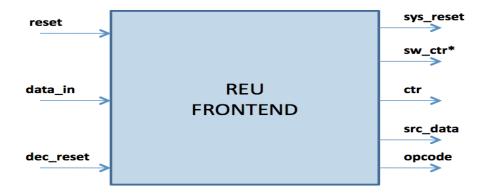

A high-level input-output pin diagram of the REU frontend is shown in Figure 3.9. The decoded input instruction frame that is generated by the frontend acts as an input block to the REU core unit. A potential acceptable decoded "data in" input frame to the frontend consists of two sizes: len(1-bit)-opcode(8-bit)-CRC(16-bit) and len(1-bit)-opcode(8-bit)-src data(8-bit)-CRC(16-bit) supported by the REU design. The len (bit) field is used to differentiate the two 25bit and the 33-bit frames. The *opcode* field represents the 8-bit 8051-instruction opcode format and the CRC represents the 16-bit code used to detect transmission errors in the received 8-bit opcode and/or src data. The src data field represents the 8-bit 8051-source data format. A typical CRC-16 polynomial of the form is  $g(x) = x^{16} + x^{12} + x^5 + 1$  is part of the frontend architecture. The 'ctr' is set by the frontend block on receiving a valid input frame and is used as trigger for the sequence of events that must take place in order to execute a specific instruction on the REU. The detailed description of the input-output signals used in Figure 3.9 is presented in Table 3.1. The opcode is an 8-bit 8051-instruction opcode that includes a source register and the destination register [71]. The "src data" is an 8-bit data that is generally part of the 16-bit 8051-instructions. The 8051 MISA based REU core supports a set of the 8-bit and 16bit 8051-instructions that will be explained in detail in the following section.

Figure 3.9: REU Frontend Pin Diagram

**Table 3.1: REU Frontend Input-Output Signal Descriptions**

| Signal    | Bit-Width | Descriptions                                                                                            | Signal    | Bit-Width | Descriptions                                                                                                            |

|-----------|-----------|---------------------------------------------------------------------------------------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| Reset     | 1         | Used to reset the system for the start of a new program                                                 | Dec_reset | 1         | Used to reset necessary signals of the Front end block.                                                                 |

| Opcode    | 8         | Instruction opcode (part of the received frame sequence)                                                | ctr       | 1         | Write signal that enables<br>writing data to the 8-<br>register bank (temporary<br>storage (set/reset by<br>controller) |

| data_in   | 8         | Encoded data that is either a Part of the 16-bit Instruction data (part of the received frame sequence) | Sw_ctr*   | 1         | Used as the set/reset the frontend switch (*if switch used)                                                             |

| sys_reset | 1         | Used to reset the system for the start of a new program.                                                | Src_data  | 8         | Input data (data_in) to ALU                                                                                             |

The simulation, verification and implementation details of the REU frontend will be presented in Chapter 4.

# 3.2 REU CORE DESIGN

The passive REU is based on a reduced 8051 Instruction Set Architecture (ISA). The choice was based on providing a maximum 8051 flexibility using the default 8051 register bank. This reduced 8051 ISA forms the 8051 MISA that will be described in the following sections.

### **3.2.1 8051-MISA for REU**

The active block or in other words the interrogator will transmit program instructions to the REU that executes these instructions and returns the results back to the interrogator. The REU, for example, will have the capability to perform simple functions like OR, XOR, AND, ADD, etc. that will be compatible with the 8051. This interrogator and the REU together form a complete processor.

8051 is an 8-bit microcontroller that includes an instruction set of 255 operation codes as shown in Table 3.2 [71]. The branch, comparison, load, and store instructions will be implemented on the interrogator side rather than on the REU side. The amount of temporary storage and the ALU capabilities of the REU will be chosen to maintain low power requirements. The REU will be programmed to execute a basic set of 8051-instructions that largely includes arithmetic (ADD, ADDC, SUBB, INC, DEC), Logical (ANL, ORL, XRL, CLR, CPL, RL, RLC, RR, RRC, SWAP), data transfer (MOV, XCH) and Boolean manipulation (CLR, SETB, CPL) instructions. The most demanding instructions like the divide (DIV), multiply (MUL) and decimal adjust (DA) will not been included in the MISA keeping the REU as minimal as possible, but form a part of the interrogator's instructions set. The MISA can be further enhanced based on a case-by-case requirement for any chosen target application during the REU design process.

Table 3.2 represents the 8051 instruction set by opcode. The instructions highlighted in **bold** represent all 116 instructions that form the MISA instruction set of the REU core design.

Only the instructions highlighted in *bold-italic* represent the instructions that are part of the 8051 instruction ISA.

Table 3.2: REU-8051 Instruction Subset (MISA)

|      | 0x00 | 0x01  | 0x02  | 0x03 | 0x04 | 0x05  | 0x06 | 0x07 | 0x08 | 0x09 | 0x0a | 0x0b | 0x0c | 0x0d | 0x0e | 0x0f |

|------|------|-------|-------|------|------|-------|------|------|------|------|------|------|------|------|------|------|

| 0x00 | NOP  | AJMP  | LJMP  | RR   | INC  | INC   | INC  | INC  | INC  | INC  | INC  | INC  | INC  | INC  | INC  | INC  |

| 0x10 | JBC  | ACALL | LCALL | RRC  | DEC  | DEC   | DEC  | DEC  | DEC  | DEC  | DEC  | DEC  | DEC  | DEC  | DEC  | DEC  |

| 0x20 | JB   | AJMP  | RET   | RL   | ADD  | ADD   | ADD  | ADD  | ADD  | ADD  | ADD  | ADD  | ADD  | ADD  | ADD  | ADD  |

| 0x30 | JNB  | ACALL | RETI  | RLC  | ADDC | ADDC  | ADDC | ADDC | ADDC | ADDC | ADDC | ADDC | ADDC | ADDC | ADDC | ADDC |

| 0x40 | JC   | AJMP  | ORL   | ORL  | ORL  | ORL   | ORL  | ORL  | ORL  | ORL  | ORL  | ORL  | ORL  | ORL  | ORL  | ORL  |

| 0x50 | JNC  | ACALL | ANL   | ANL  | ANL  | ANL   | ANL  | ANL  | ANL  | ANL  | ANL  | ANL  | ANL  | ANL  | ANL  | ANL  |

| 0x60 | JZ   | AJMP  | XRL   | XRL  | XRL  | XRL   | XRL  | XRL  | XRL  | XRL  | XRL  | XRL  | XRL  | XRL  | XRL  | XRL  |

| 0x70 | JNZ  | ACALL | ORL   | JMP  | MOV  | MOV   | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  |

| 0x80 | SJMP | AJMP  | ANL   | MOVC | DIV  | MOV   | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  |

| 0x90 | MOV  | ACALL | MOV   | MOVC | SUBB | SUBB  | SUBB | SUBB | SUBB | SUBB | SUBB | SUBB | SUBB | SUBB | SUBB | SUBB |

| 0xa0 | ORL  | AJMP  | MOV   | INC  | MUL  | UNDEF | MOV  |

| 0xb0 | ANL  | ACALL | CPL   | CPL  | CJNE | CJNE  | CJNE | CJNE | CJNE | CJNE | CJNE | CJNE | CJNE | CJNE | CJNE | CJNE |

| 0xc0 | PUSH | AJMP  | CLR   | CLR  | SWAP | ХСН   | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  | ХСН  |

| 0xd0 | POP  | ACALL | SETB  | SETB | DA   | DJNZ  | XCHD | XCHD | DJNZ |

| 0xe0 | MOVX | AJMP  | MOVX  | MOVX | CLR  | MOV   | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  |

| 0xf0 | MOVX | ACALL | MOVX  | MOVX | CPL  | MOV   | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  | MOV  |

The remaining two instructions highlighted only in **bold** form the set of instructions that have been modified to suit the REU requirements. A modified instruction with respect to its common 8051 functionality is the MOVX instruction (MOVX @R<sub>i</sub>, A). The 8-bit instruction opcode used for this MOVX instruction is "11110010". The functionality of the instruction was modified to suit the target REU core design. Upon the execution of this instruction, data

available in the accumulator register will be transferred to a destination register. The destination register is used to hold data that is transmitted out of the REU based on the request from the interrogator. The other modified instruction is the NOP that can be used as an external reset sent by the interrogator to the REU in order to clear up all the data from the previous operations from the registers and signals.

For instance, an ADD operation R3 =#R1+R2, where Ri denotes a register, i#=#0,1,2,... The interrogator sends out the R1 and R2 values to load and store it in the temporary storage on the REU. Then, the ADD operation is performed by the REU and the computed result is sent back to the interrogator on request. The interrogator will contain main memory that acts as the major storage area for large volumes of data items. This is the same technique used to power passive RFID tags. Thus such tags do not need periodic battery replacements [35]. This makes such tags suitable for embedded tag applications, especially where long-term monitoring is not economical.

Table 3.3 contains the notes for data addressing mnemonics for the instruction sets described in 3.4.

Table 3.3: REU-8051 Data Mnemonics

| R <sub>n</sub> | Working registers (R <sub>0</sub> -R <sub>7</sub> ) |

|----------------|-----------------------------------------------------|

| #data          | 8-bit constant embedded in instruction              |