# IMPROVING PHASE CHANGE MEMORY (PCM) AND SPIN-TORQUE-TRANSFER MAGNETIC-RAM (STT-MRAM) AS NEXT-GENERATION MEMORIES: A CIRCUIT PERSPECTIVE

by

#### Bo Zhao

B.S., Electrical Engineering, Beihang University, 2007M.S., Electrical Engineering, University of Pittsburgh, 2009

Submitted to the Graduate Faculty of

the Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy in Computer Engineering

University of Pittsburgh

2013

### UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Bo Zhao

It was defended on November 8th 2013

and approved by

Jun Yang, Ph.D., Associate Professor

Department of Electrical and Computer Engineering

Steven P. Levitan, Ph.D., John A. Jurenko Professor

Department of Electrical and Computer Engineering

Hai (Helen) Li, Ph.D., Assistant Professor

Department of Electrical and Computer Engineering

Youtao Zhang, Ph.D., Associate Professor

Department of Computer Science

Paul W. Leu, Ph.D., Assistant Professor

Department of Industrial Engineering

Dissertation Director: Jun Yang, Ph.D., Associate Professor

Department of Electrical and Computer Engineering

Copyright © by Bo Zhao 2013

## IMPROVING PHASE CHANGE MEMORY (PCM) AND SPIN-TORQUE-TRANSFER MAGNETIC-RAM (STT-MRAM) AS NEXT-GENERATION MEMORIES: A CIRCUIT PERSPECTIVE

Bo Zhao, PhD

University of Pittsburgh, 2013

In the memory hierarchy of computer systems, the traditional semiconductor memories Static RAM (SRAM) and Dynamic RAM (DRAM) have already served for several decades as cache and main memory. With technology scaling, they face increasingly intractable challenges like power, density, reliability and scalability. As a result, they become less appealing in the multi/many-core era with ever increasing size and memory-intensity of working sets.

Recently, there is an increasing interest in using emerging non-volatile memory technologies in replacement of SRAM and DRAM, due to their advantages like non-volatility, high device density, near-zero cell leakage and resilience to soft errors. Among several new memory technologies, Phase Change Memory (PCM) and Spin-Torque-Transfer Magnetic-RAM (STT-MRAM) are most promising candidates in building main memory and cache, respectively. However, both of them possess unique limitations that preventing them from being effectively adopted.

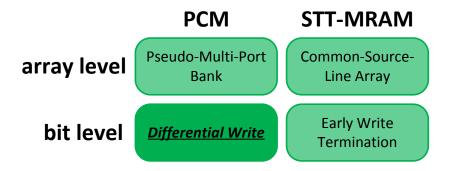

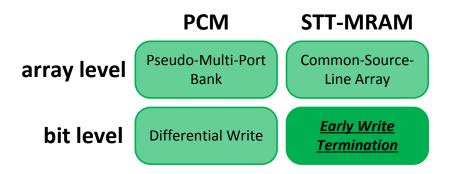

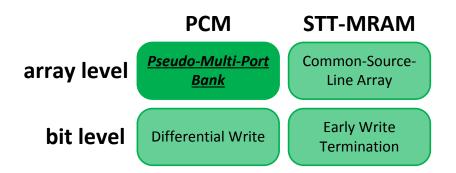

In this dissertation, I present my circuit design work on tackling the limitations of PCM and STT-MRAM. At bit level, both PCM and STT-MRAM suffer from excessive write energy, and PCM has very limited write endurance. For PCM, I implement Differential Write to remove large number of unnecessary bit-writes that do not alter the stored data. It is then extended to STT-MRAM as Early Write Termination, with specific optimizations to eliminate the overhead of pre-write read. At array level, PCM enjoys high density

but could not provide competitive throughput due to its long write latency and limited number of read/write circuits. I propose a Pseudo-Multi-Port Bank design to exploit intrabank parallelism by recycling and reusing shared peripheral circuits between accesses in a time-multiplexed manner. On the other hand, although STT-MRAM features satisfactory throughput, its conventional array architecture is constrained on density and scalability by the pitch of the per-column bitline pair. I propose a Common-Source-Line Array architecture which uses a shared source-line along the row, essentially leaving only one bitline per column.

For these techniques, I provide circuit level analyses as well as architecture/system level and/or process/device level discussions. In addition, relevant background and work are thoroughly surveyed and potential future research topics are discussed, offering insights and prospects of these next-generation memories.

#### TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                     | 1  |

|-----|--------------------------------------------------|----|

|     | 1.1 Research Overview                            | 6  |

|     | 1.2 Dissertation Organization                    | 11 |

| 2.0 | BACKGROUND                                       | 12 |

|     | 2.1 SRAM                                         | 12 |

|     | 2.2 DRAM & eDRAM                                 | 16 |

|     | 2.3 PCM                                          | 20 |

|     | 2.4 STT-MRAM                                     | 25 |

| 3.0 | BIT LEVEL ENERGY REDUCTION AND LIFETIME IMPROVE- |    |

|     | MENT FOR PCM                                     | 29 |

|     | 3.1 Energy and Lifetime Problems of PCM          | 30 |

|     | 3.2 The Opportunity: Redundant Bit-Writes        | 31 |

|     | 3.3 Differential Write                           | 32 |

|     | 3.3.1 Circuit Design                             | 33 |

|     | 3.3.2 Overhead                                   | 35 |

|     | 3.4 Evaluation Results                           | 35 |

|     | 3.4.1 Modeling                                   | 35 |

|     | 3.4.2 Energy and Lifetime Results                | 37 |

|     | 3.5 Beyond Energy and Lifetime                   | 38 |

| 4.0 | BIT LEVEL ENERGY REDUCTION FOR STT-MRAM          | 39 |

|     | 4.1 Energy Problem of STT-MRAM                   | 40 |

|     | 4.2 The Opportunity: Redundant Bit-Writes        | 40 |

|            | 4.3           | Early Write Termination                                             | 41 |

|------------|---------------|---------------------------------------------------------------------|----|

|            |               | 4.3.1 Rationale                                                     | 41 |

|            |               | 4.3.2 Circuit Design                                                | 43 |

|            |               | 4.3.3 Overhead                                                      | 46 |

|            | 4.4           | Evaluation Results                                                  | 47 |

|            |               | 4.4.1 Modeling                                                      | 47 |

|            |               | 4.4.2 Energy and Performance Results                                | 49 |

| <b>5.0</b> | $\mathbf{AR}$ | RAY LEVEL THROUGHPUT IMPROVEMENT FOR PCM                            | 51 |

|            | 5.1           | Throughput Problem of PCM                                           | 52 |

|            | 5.2           | Pseudo-Multi-Port Bank Design                                       | 54 |

|            |               | 5.2.1 Overview                                                      | 55 |

|            |               | 5.2.2 Circuit Design                                                | 58 |

|            |               | 5.2.3 Circuit Component Details                                     | 63 |

|            |               | 5.2.4 Overhead                                                      | 69 |

|            |               | 5.2.5 More Discussions on Circuit Design                            | 70 |

|            | 5.3           | Memory Scheduling Opportunities                                     | 72 |

|            | 5.4           | Evaluation Results                                                  | 74 |

| 6.0        | AR            | RAY LEVEL DENSITY AND SCALABILITY IMPROVEMENTS                      |    |

|            | FO            | R STT-MRAM                                                          | 75 |

|            | 6.1           | Density and Scalability Problems of Dual-Bitline Array Architecture | 76 |

|            | 6.2           | Common-Source-Line Array Design                                     | 77 |

|            |               | 6.2.1 Common-SL Layout                                              | 77 |

|            |               | 6.2.2 Read and Write                                                | 78 |

|            |               | 6.2.3 Concerns of Gate Oxide Breakdown                              | 80 |

|            | 6.3           | Design for Reliability                                              | 81 |

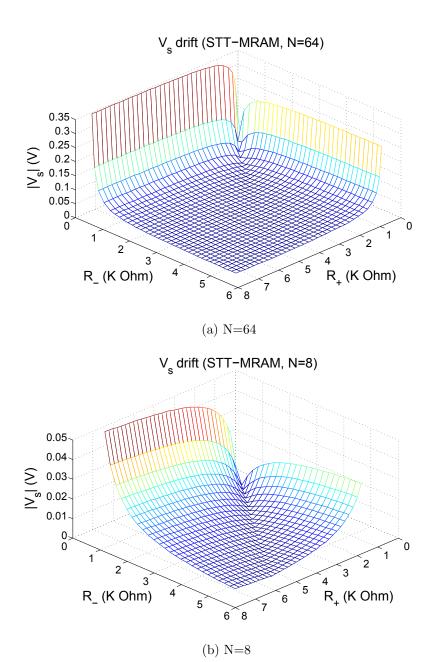

|            |               | 6.3.1 Mitigating $V_s$ Drift                                        | 83 |

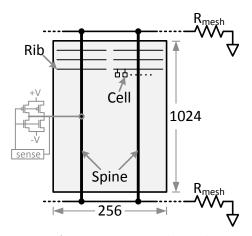

|            |               | 6.3.2 Array Design                                                  | 85 |

|            |               | 6.3.3 Compensation Circuit                                          | 88 |

|            | 6.4           | Evaluation Results                                                  | 89 |

|            | 6.5           | Design Styles with Common-Source-Line Architecture                  | 92 |

| 7.0 | RELATED WORK                            | 94  |

|-----|-----------------------------------------|-----|

|     | 7.1 PCM                                 | 94  |

|     | 7.1.1 Prototype Chips & Circuit Designs | 94  |

|     | 7.1.2 Architectural Innovations         | 97  |

|     | 7.2 STT-MRAM                            | 101 |

|     | 7.2.1 Prototype Chips & Circuit Designs | 101 |

|     | 7.2.2 Architectural Innovations         | LO4 |

| 8.0 | CONCLUSION & FUTURE WORK                | 107 |

|     | 8.1 Future Work                         | 107 |

|     | 8.1.1 PCM                               | 107 |

|     | 8.1.2 STT-MRAM                          | 108 |

|     | 8.2 Conclusion                          | 112 |

| BIF | BLIOGRAPHY                              | 112 |

#### LIST OF TABLES

| 1 | Comparison of solid-state memory technologies                   | 5  |

|---|-----------------------------------------------------------------|----|

| 2 | Latency and energy parameters used in architectural simulations | 36 |

| 3 | Signal conditions and induced actions in different write cases  | 45 |

| 4 | Per-access read/write energy                                    | 47 |

| 5 | Per-access read/write latency                                   | 48 |

| 6 | Delay, energy and area overheads                                | 69 |

| 7 | STT MTJ parameters                                              | 83 |

| 8 | Layout rules used in area estimation                            | 89 |

| 9 | Data patterns used in evaluations                               | 90 |

#### LIST OF FIGURES

| 1  | Memory hierarchy and application range of memory technologies               | 2  |

|----|-----------------------------------------------------------------------------|----|

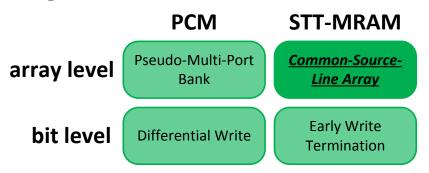

| 2  | Challenges of PCM and STT-MRAM to be addressed                              | 8  |

| 3  | Circuit level solutions to the challenges of PCM and STT-MRAM               | 10 |

| 4  | Schematic of an SRAM cell                                                   | 12 |

| 5  | SRAM cell read operation                                                    | 13 |

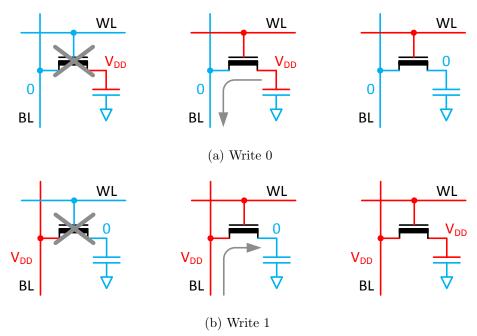

| 6  | SRAM cell write operation                                                   | 14 |

| 7  | Leakage currents in an SRAM cell                                            | 15 |

| 8  | An 8T dual-port SRAM cell with one read port and one write port             | 15 |

| 9  | Schematic of a DRAM cell                                                    | 16 |

| 10 | DRAM cell read operation                                                    | 17 |

| 11 | DRAM cell write operation                                                   | 18 |

| 12 | DRAM cell leakage                                                           | 18 |

| 13 | Cross-section comparison of DRAM cells with trench and stacked capacitors . | 19 |

| 14 | Conceptual view of a PCM cell showing phase change device structure         | 21 |

| 15 | Read and write voltage/current/temperature pulses                           | 21 |

| 16 | PCM cell read operation                                                     | 22 |

| 17 | Three types of PCM cell using different access devices                      | 23 |

| 18 | Conceptual view of an STT-MRAM cell showing MTJ structure                   | 26 |

| 19 | Schematic of an STT-MRAM cell                                               | 26 |

| 20 | STT-MRAM cell read operation                                                | 27 |

| 21 | Bit level solution for PCM: Differential Write                              | 29 |

| 22 | Lifetime of PCM memory without any improvement technique                    | 31 |

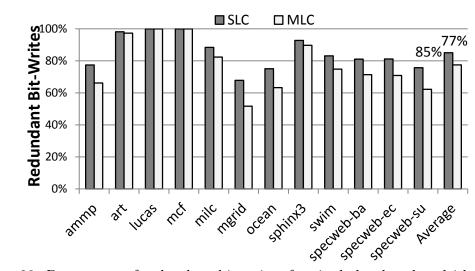

| 23 | Percentage of redundant bit-writes for single-level and multi-level cells       | 32 |

|----|---------------------------------------------------------------------------------|----|

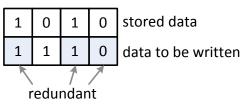

| 24 | Identify redundant bit-writes based on comparison                               | 33 |

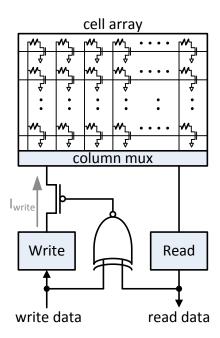

| 25 | A micro-architectural view of Differential Write                                | 33 |

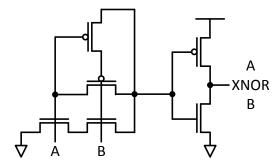

| 26 | XNOR circuit implementation                                                     | 34 |

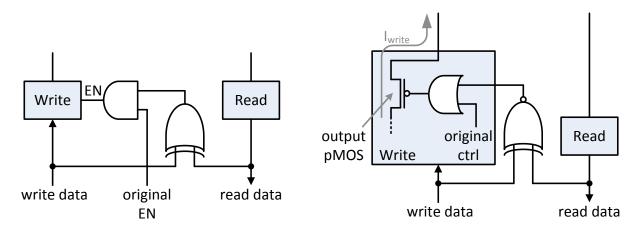

| 27 | Two alternative design styles of Differential Write                             | 34 |

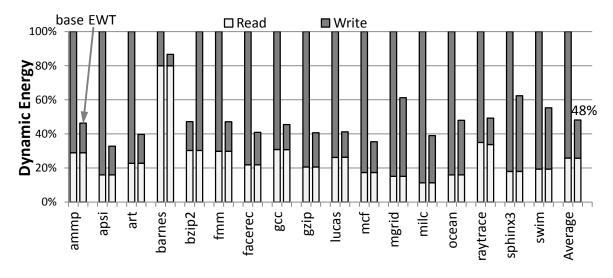

| 28 | Dynamic energy breakdown showing energy savings of Differential Write (SLC)     | 37 |

| 29 | Lifetime (days) after applying Differential Write                               | 38 |

| 30 | Bit level solution for STT-MRAM: Early Write Termination                        | 39 |

| 31 | Redundant bit-writes in 16MB STT-MRAM L2 cache                                  | 40 |

| 32 | Overview of EWT circuit design                                                  | 43 |

| 33 | The voltage divider behavior of the write current path                          | 44 |

| 34 | Comparator circuit                                                              | 46 |

| 35 | Dynamic energy breakdown showing energy savings of EWT                          | 49 |

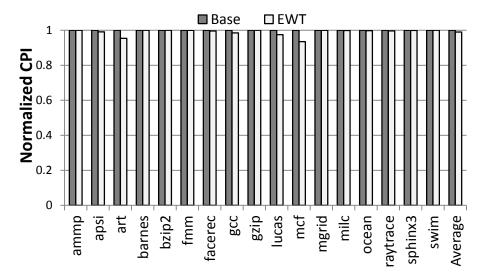

| 36 | Performance improvements                                                        | 50 |

| 37 | Array level solution for PCM: Pseudo-Multi-Port Bank                            | 51 |

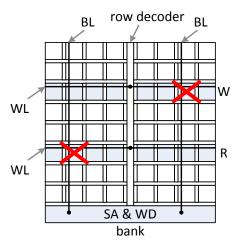

| 38 | Overview of memory organization showing 4 concurrent accesses in a bank         | 55 |

| 39 | Interference among wordlines and bitlines for write and read                    | 56 |

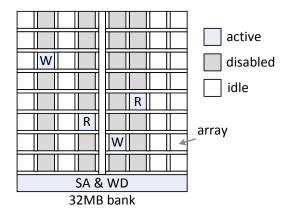

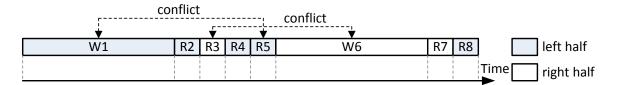

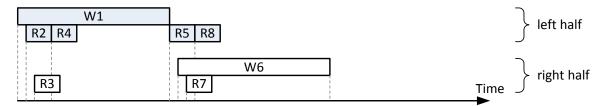

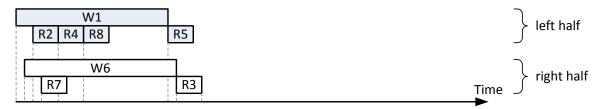

| 40 | Three array states in a bank                                                    | 57 |

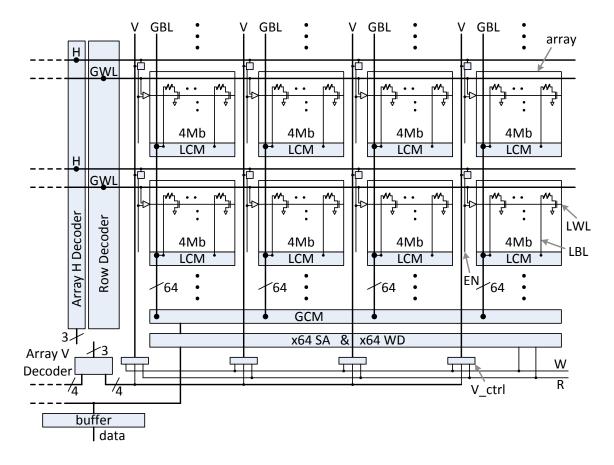

| 41 | Architecture of Pseudo-Multi-Port Bank design showing the right-half bank .     | 59 |

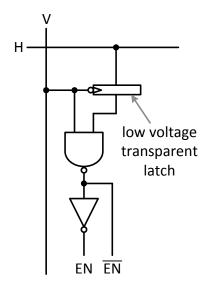

| 42 | Array enable circuit                                                            | 60 |

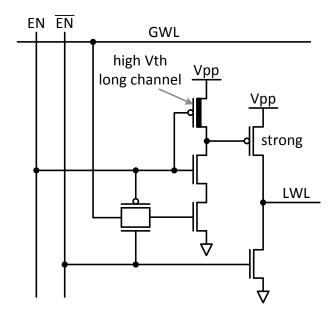

| 43 | LWL driver                                                                      | 60 |

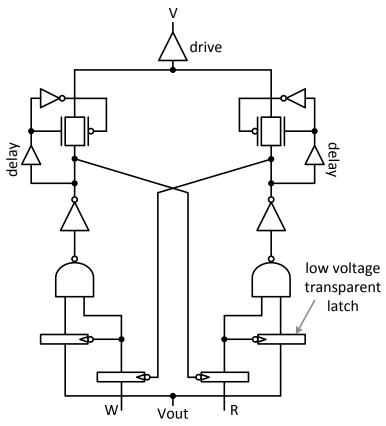

| 44 | $V_{\rm ctrl}$ circuit to hold the V signal while releasing the array V decoder | 61 |

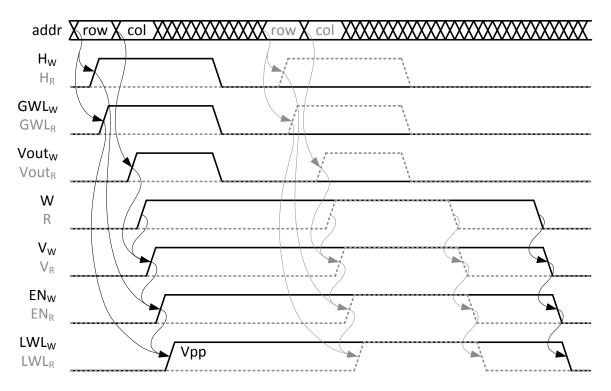

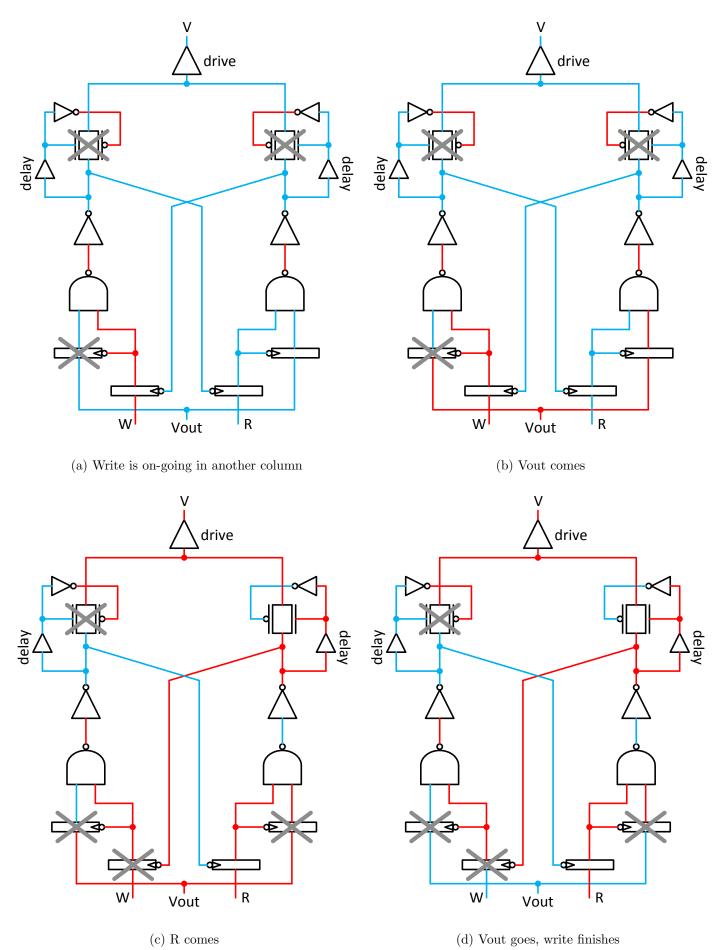

| 45 | Timing graph of a read carried in parallel with a write (not to scale)          | 62 |

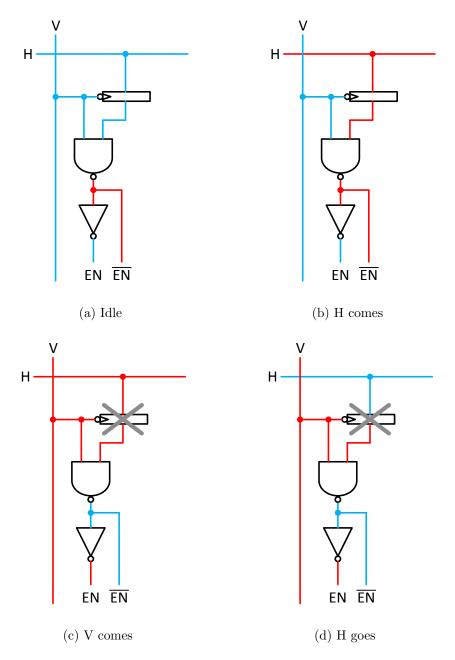

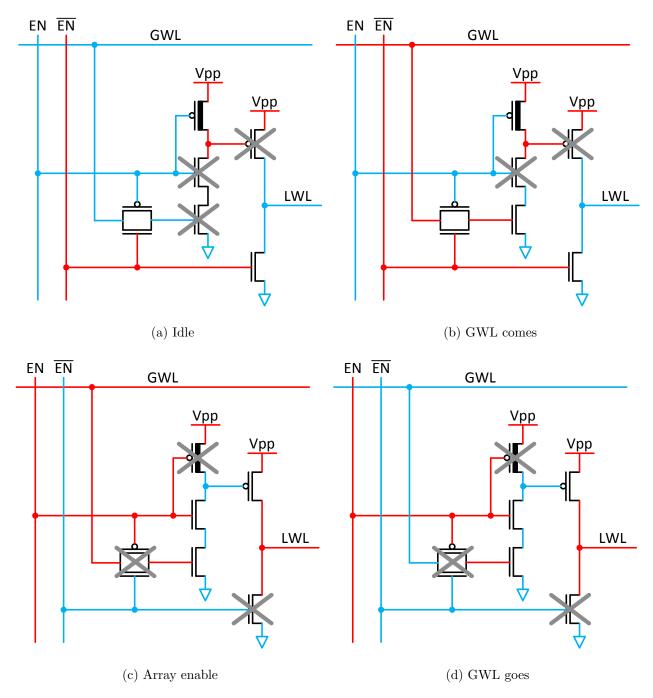

| 46 | Steps to select/enable an array                                                 | 63 |

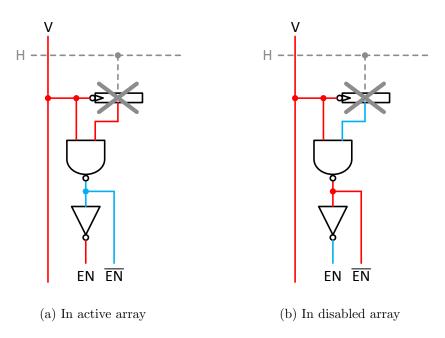

| 47 | States of array enable circuits in different arrays                             | 64 |

| 48 | Steps to activate a LWL                                                         | 65 |

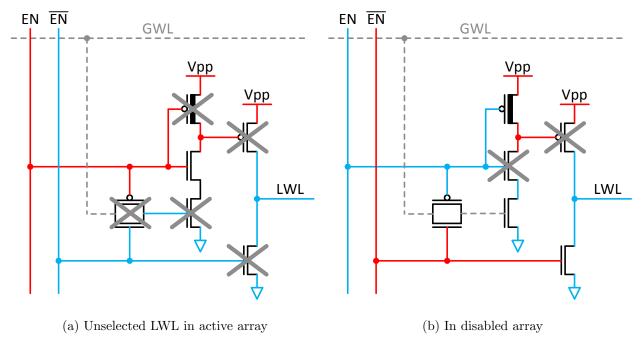

| 49 | States of LWL drivers in different arrays                                       | 66 |

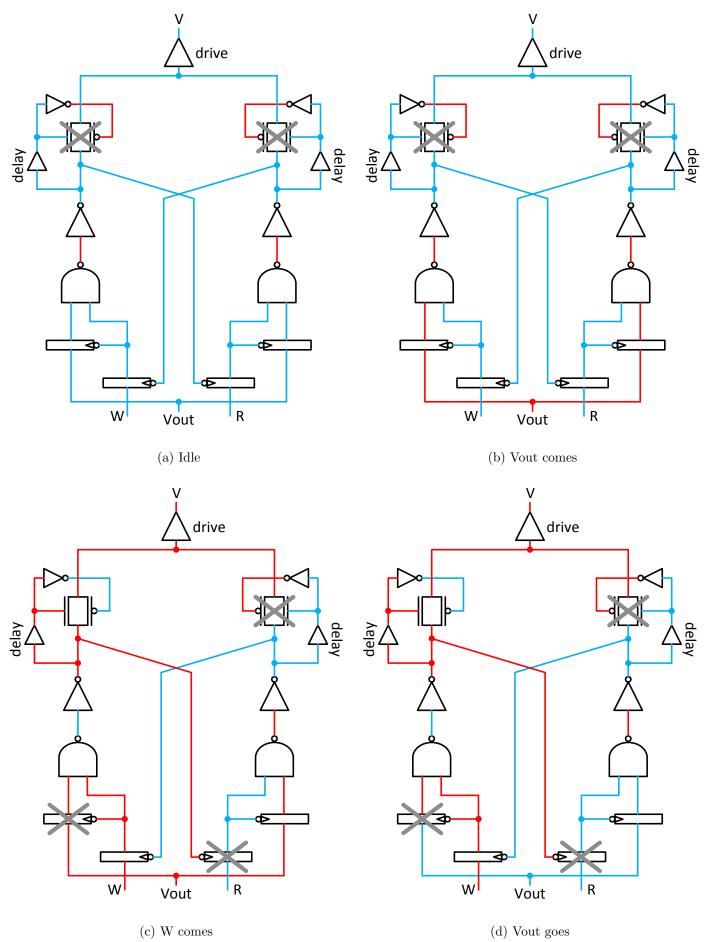

| 50 | Selecting a V signal for the 1st access                                         | 67 |

| 51 | Selecting a V signal for the 2nd access in parallel with the 1st access         | 68 |

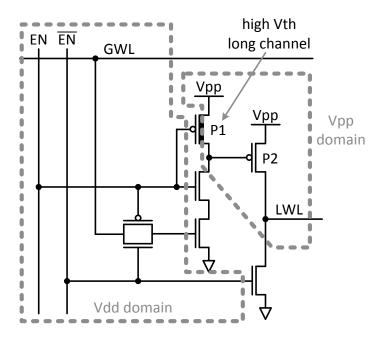

| 52 | Two voltage domains in a LWL driver                                             | 70 |

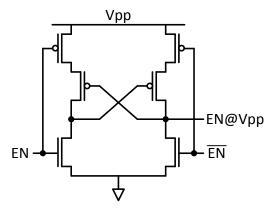

| 53 | Level converter circuit to adapt EN signal to $V_{PP}$ domain        | 71  |

|----|----------------------------------------------------------------------|-----|

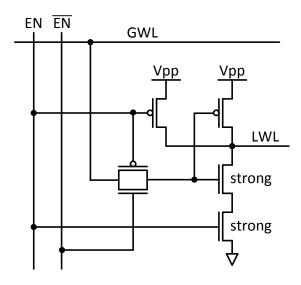

| 54 | LWL driver design for diode-selected PCM cell                        | 72  |

| 55 | Impact of scheduling on requests finish time                         | 73  |

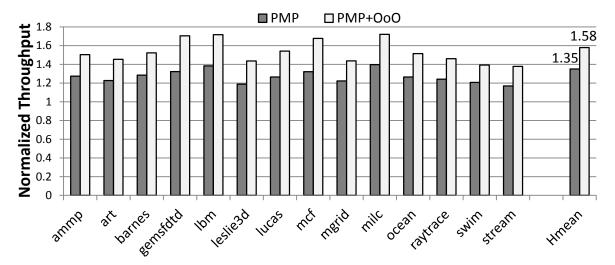

| 56 | Throughput improvements                                              | 74  |

| 57 | Array level solution for STT-MRAM: Common-Source-Line Array          | 75  |

| 58 | Illustration of a dual-BL array                                      | 76  |

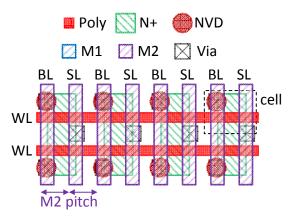

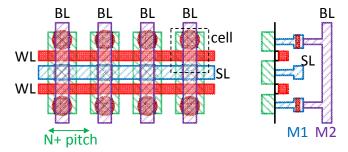

| 59 | Layout of dual-BL array                                              | 77  |

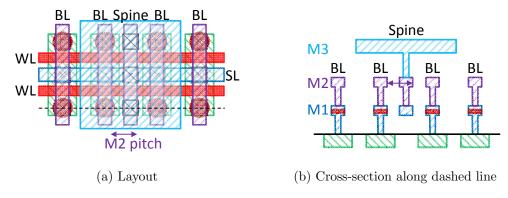

| 60 | Layout of common-SL array with cross-section view along bitline (BL) | 78  |

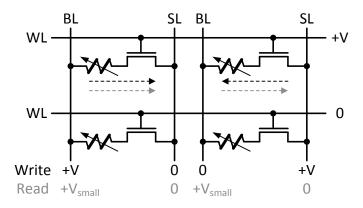

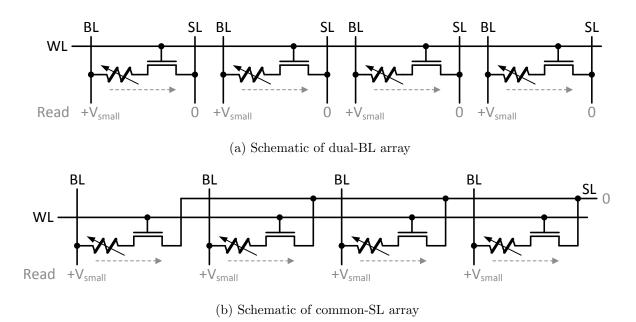

| 61 | Schematic comparison between dual-BL and common-SL arrays            | 78  |

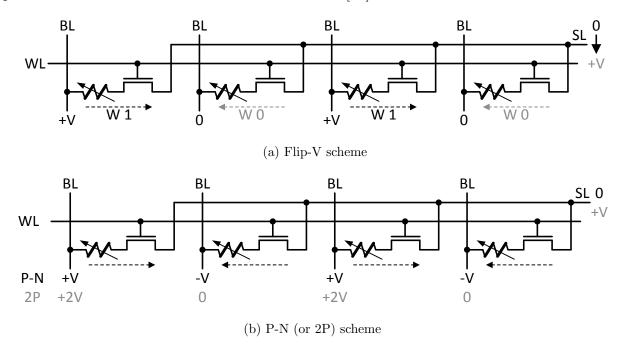

| 62 | Two write schemes in common-SL array                                 | 79  |

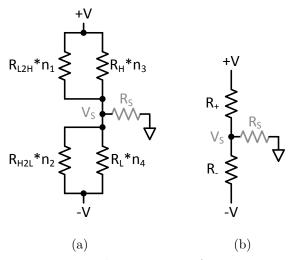

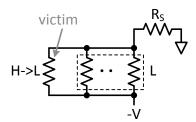

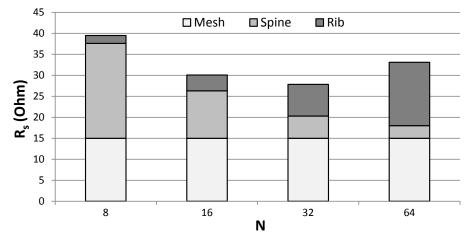

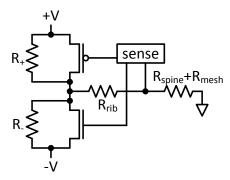

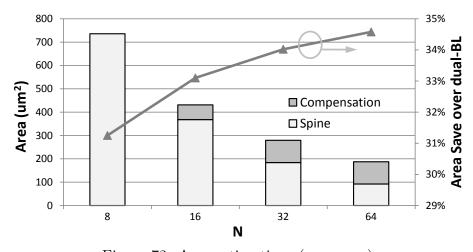

| 63 | Equivalent circuits of write operation                               | 82  |

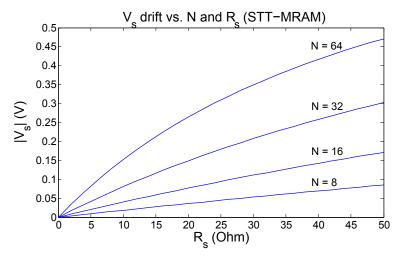

| 64 | $V_s$ vs. $R_+$ and $R$ for $N$ =64 and 8, $R_s$ =30 $\Omega$        | 84  |

| 65 | Equivalent circuit of the worst-case data pattern                    | 84  |

| 66 | $V_s$ drift as a function of $N$ and $R_s$                           | 85  |

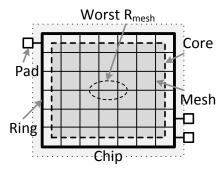

| 67 | Simple illustration of ground/power supply system                    | 86  |

| 68 | An array example with $N=128$                                        | 86  |

| 69 | $R_s$ tradeoffs                                                      | 87  |

| 70 | Physical design of spines                                            | 87  |

| 71 | Equivalent circuit of write operation with compensation              | 88  |

| 72 | Area estimations (per array)                                         | 88  |

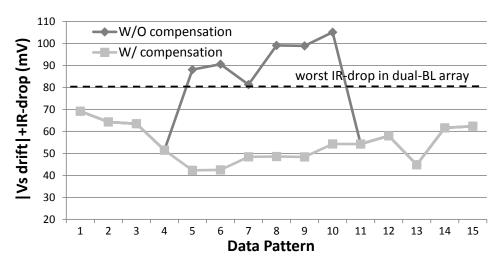

| 73 | $V_s$ drift + IR-drop $vs.$ data pattern in STT-MRAM $(N=16)$        | 91  |

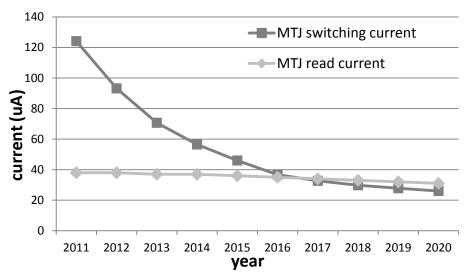

| 74 | STT-MRAM current scaling trends                                      | 110 |

#### ACKNOWLEDGMENTS

Completing a Ph.D. degree is an individual achievement, yet it is obviously not possible without the personal and practical supports of numerous people. One of the joys of completion is to look over the journey past and remember all these individuals who have helped and encouraged me in one way or the other during this rewarding and amazing journey.

First and foremost, it is difficult to overstate my gratitude to my advisor, Professor Jun Yang, and my "secondary" advisor, Professor Youtao Zhang. I could not have asked for better role model of researchers, each enthusiastic, diligent, and insightful. The joy and perseverance they have for academic pursuits were contagious and motivational for me. They have taught me, both consciously and unconsciously, how conscientious research is conducted. In addition, Professor Jun Yang and Professor Youtao Zhang are inspirational, supportive, patient, and the true embodiment of a mentor. I am deeply grateful to them for giving me the confidence to explore my research interests and the guidance to avoid getting lost in my exploration. Beyond knowledge, their special attention to details trained me to schedule, to organize, to illustrate, to present, all are invaluable skills for whatever I am and will be working on. It has always been my honor and pleasure working with Professor Jun Yang and Professor Youtao Zhang.

In combination with the mentorship of my advisor, I am blessed to work with my active committee members and taught by many intelligent faculties. Professor Steven Levitan is not only a fabulous guide but a dear friend: sharp, cheery, perceptive, and thankfully, readily available for me. He was very generous with his time and knowledge, and we had numerous useful discussions and brainstormings throughout my graduate study. He also led me into the door of integrated circuit design, and I have never expected my three-year Teaching Assistant service for his introductory and advanced VLSI courses to be so fun and rewarding. My sincere gratitude is reserved for Professor Hai (Helen) Li and Professor Yiran Chen for their constructive insights and advices, which were substantially helpful to my research and study. I would like to thank Professor Paul Leu from Industrial Engineering for his time, interest, helpful comments, and a welcome diversity of perspectives. I also

appreciate Professor Ken Mai, Professor Larry Pileggi, and Professor Rick Carley at ECE department of Carnegie Mellon University, for their informative course works that provided me with thorough and in-depth knowledge.

Also, I have been very fortunate with my brilliant research group comrades: Ping Zhou, Yu Du, Lei Jiang, Yi Xu, Lin Li. They have contributed immensely to my personal and professional time at Pittsburgh. The group has been a constant source of friendships as well as inspiration, feedback, suggestion, assistance, and collaboration. I am indebted to them for helping me whole-heartedly on many of my research projects, and for providing a stimulating and fun environment in which to learn and grow. Moreover, heartfelt thanks goes to my roommates and all my friends and classmates in University of Pittsburgh and Carnegie Mellon University, for their friendship and company, for each and every day and night and meal and game we spent, enjoyed, and suffered together.

Despite the geographical distance, my family was always nearby. Words cannot express the feelings I have for my mother Zheng Liu, my father Zhongxiang Zhao, and all my grandparents who raised me with unconditional love and supported me in all my pursuits. I would not be here if not for you. My dear daughter, Ziyue Zhao, who joined my life sixteen months ago, thank you for re-energizing me with laughters every evening after a long day. I wish to thank my entire extended family as my constant harbor, spiritually, emotionally, and physically, during the hard and easy times. And also to my in-laws for their faithful love, help and encouragement over the past ten years. Lastly, to my beloved, Di Wang, for always being there. Wherever I am, all of you are always in my heart.

To My Family

#### 1.0 INTRODUCTION

The two most essential functions of computer systems are computation and storage. While computations are mostly centralized in the Central Processing Unit (CPU), storages take place ubiquitously, from temporary buffering of intermediate computation results, to permanent massive file backups that can be carried in our pockets.

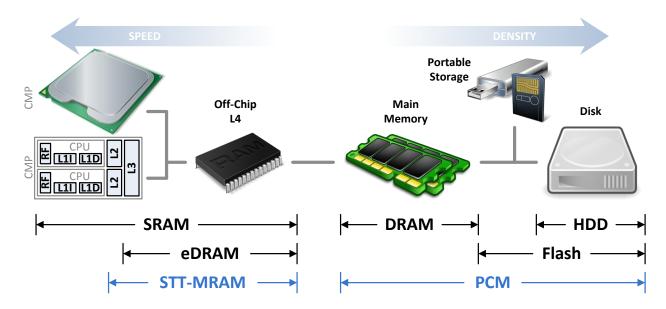

In computer systems, the vast existence of storage is organized in a hierarchical manner known as the *memory hierarchy* illustrated in Figure 1. A memory hierarchy can be seen as a hardware optimization that takes the benefits of spatial and temporal localities to speed up data accesses. It distinguishes each level in the hierarchy by speed and density. The higher level memories (closer to CPU) are faster to serve the high frequence CPU, but smaller to hold only the most active data. The lower level memories (further from CPU) tend to be slower, but larger to store the large working set. Thus, a program will achieve greater performance if it uses data while it is cached in the higher levels of the memory hierarchy and avoids bringing other data into the higher levels of the hierarchy that will displace data that will be used shortly in the future.

The unique speed and density requirements in turn determine the choices of memory technologies in each level. In classic implementations that still dominate nowadays, Static RAM (SRAM), Dynamic RAM (DRAM), and mechanical Hard Disk Driver (HDD) are employed in the hierarchy from top to bottom, as shown in Figure 1. SRAM is the fastest memory that can match the GHz operation of CPU pipeline. It can also take advantage of its multi- to many-port capability to achieve extremely high bandwidth which is crucial to Register Files (RF) and L1 caches. Moreover, it is built out of standard logic transistors that can be seamlessly integrated with CPU components on-chip. Therefore, SRAM is the natural choice of all kinds of on-chip storage, as well as the large off-chip L4 cache due to

its faster speed than DRAM. Although DRAM is also a solid-state memory, it is generally not process-compatible with CPU due to its specially optimized fabrication processes for the dedicated capacitor and high density. DRAM is used as large main memory with adequate speed and much lower power than SRAM. It features much higher density and thus capacity to hold the entire working sets of multiple programs. HDD provides even higher density and capacity than DRAM with non-volatile storage for the whole file system. However, data accesses are carried out by mechanical mechanisms of rotating the disks and moving the magnetic heads for address searching, resulting in very high latency.

Figure 1: Memory hierarchy and application range of memory technologies.

As more and more processor cores are integrated in a Chip Multi-Processor (CMP) to exploit computational parallelism, the capacity demand for on-chip storage, especially lower level caches, increases rapidly. As a result, large caches usually occupy >50% die area in modern processors, giving rise to the leakage concern of SRAM in deep sub-micron technologies. SRAM cell is particularly leaky due to its multi-transistor nature. This is less a problem in small and very active higher-level caches, but becomes prohibitive given the large size and low activity of L3 caches. Besides, the low density of SRAM, also a result of its multi-transistor cell, leads to too large cache area and thus large die size that ultimately increases cost and decreases yield. In the other end of the hierarchy, although the density of HDD kept growing constantly, its speed was not improved fast enough that lagged behind all

upper-level memories further and further. Also, its mechanical movements based operations are not suitable for the fast-growing portable applications.

Consequently, in the past decade, we have seen the rise of eDRAM and Flash. eDRAM is essentially DRAM "embedded" with processors. It is fabricated with logic-compatible processes, yielding higher speed than commodity DRAM, at the expense of shorter retention time and lower density. Nevertheless, eDRAM still offers ~3× density over SRAM, with much lower leakage. Therefore, successful adoptions of eDRAM as up to 80MB on-chip L3 cache [59] and 192MB off-chip L4 cache [65] have been demonstrated. Because its latency is still relatively large compared to SRAM, eDRAM is not yet utilized in the more delay-sensitive L2 caches. In the other end of the hierarchy, Flash memory based Solid State Disks (SDD) easily outperform HDD by orders of magnitudes, with lower power and heat dissipation. While in the middle, commodity DRAM kept scaling and doubling its capacity. Up to this point, we have got a pure solid-state memory hierarchy.

However, as the integrated circuit technology heading into the deep sub-micron territory and approaching the  $\sim 10nm$  era, this entire pool of memories face crisis again. The refresh problem of DRAM/eDRAM worsens rapidly with technology advancement and capacity increase, as well as temperature and process variations. This is because the cell transistor becomes leakier and more vulnerable to variations with shrinked footprint, and there are more rows of cells to be refreshed within the same time interval in a larger memory with larger number of rows. Such refresh problem will place more negative effects on system performance in future generations of DRAM/eDRAM. To maintain reasonable retention time and sensing margin, adequate cell-to-bitline capacitance ratio must be maintained in DRAM/eDRAM, this in turn limits the size shrinking of cell capacitor and ultimately hurts the DRAM scaling in general. Furthermore, DRAM main memories consume >40% power of modern computer systems, and such percentage will keep growing with faster and larger DRAMs. On the other hand, Flash also faces scaling problem because of its limited footprint of the floating gate and thus limited number of stored electrons that is very vulnerable to process variation. As a result, although people are pushing Flash's multi-level capability to an extreme, very sophisticated read and write schemes must be developed to make it viable. Flash also has very limited lifetime of only  ${\sim}10^5$  writes. So SSDs are usually equipped with up to 50% user-invisible redundancy (known as over-provisioning) to maintain the nominal capacity in its lifecycle (e.g. 10 years). Its block-level erase and program is not only slow but also too inefficient from an energy point of view. Moreover, generating the very high voltage (~20V) for erase/program out of the decreasing supply voltage is becoming harder. Finally, both DRAM/eDRAM and Flash suffer from worsening reliability. They become less immune to soft error mechanisms like alpha particle strike due to the decreasing number of electrons held in their storage nodes.

Recently, there is an increasing interest in introducing new non-volatile memory technologies such as Phase Change Memory (PCM), Spin-Torque-Transfer Magnetic-RAM (STT-MRAM), Memristor, Ferroelectric RAM (FeRAM), Conductive-Bridging RAM (CB-RAM), etc., to the memory hierarchy in replacement of existing memories. Among these emerging memory technologies, Phase Change Memory (PCM) and Spin-Torque-Transfer Magnetic-RAM (STT-MRAM) are two of the most promising candidates as the next-generation memories. Table 1 compares PCM and STT-MRAM with existing solid-state memory technologies SRAM, eDRAM, DRAM and Flash. PCM and STT-MRAM share many common characteristics like resistance-based storage, non-volatility, high density, good scalability, low leakage, immunity to soft errors, etc. Nevertheless, they possess unique features that distinguish themselves in the memory hierarchy.

PCM features similar cell density to DRAM and Flash and multi-level storage capability, which naturally place it at the lower levels of the memory hierarchy, as shown in Figure 1. Due to its clear advantages like byte-addressability, lower latency, better endurance, better scalability and better reliability, PCM is an inherent replacement of Flash and HDD on disk storages and portable storages. When compared to DRAM, PCM still exhibits many benefits on density, leakage, non-volatility, scalability and reliability. However, disadvantages also exist as long latencies, high write energy, low throughput and limited endurance. Therefore, special efforts must be paid to mitigating these drawbacks for successful application of PCM as DRAM replacement in main memory.

STT-MRAM usually have similar or better density than eDRAM with advantages like lower leakage, non-volatility, better scalability and better reliability. Although its 10<sup>15</sup> write endurance is worse than eDRAM, this is generally good enough to be considered unlimited.

Table 1: Comparison of solid-state memory technologies. <sup>a</sup>

|                                    | SRAM          | eDRAM              | DRAM      | Flash           | PCM              | STT-MRAM      |

|------------------------------------|---------------|--------------------|-----------|-----------------|------------------|---------------|

| State-of-the-art cell size $(F^2)$ | 135           | 35                 | 6         | 4               | 4                | 14            |

| Storage type                       | latch         | charge             | charge    | trapped charge  | resistance       | resistance    |

| Cell read speed                    | 100ps         | 1ns                | 10ns      | $10\mu s$       | 30ns             | 1ns           |

| Cell write speed                   | 100ps         | 1ns                | 10ns      | $100\mu s$      | 150ns            | $3\sim 10ns$  |

| Read energy                        | Low           | Low                | Medium    | Medium          | Low              | Low           |

| Write energy                       | Low           | Low                | Medium    | High            | High             | Medium        |

| Leakage                            | High          | Medium             | Medium    | Medium          | Low              | Low           |

| Throughput                         | Very High     | High               | Medium    | Very Low        | Low              | High          |

| Retention time                     | $\infty$ with | $50\mu s \sim 1ms$ | >64ms     | non-volatile    | non-volatile     | compromisable |

| (volatility)                       | power         | . 16               | 16        |                 |                  | non-volatile  |

| Write endurance                    | $10^{16}$     | $10^{16}$          | $10^{16}$ | $10^{5}$        | $10^8 \sim 10^9$ | $10^{15}$     |

| Multi-level storage                | No            | No                 | No        | $4\sim$ 6b/cell | 2b/cell          | Possible      |

| Multi-port access                  | Many-port     | 2-port             | No        | No              | No               | No            |

| Scalability                        | Good          | Poor               | Poor      | Poor            | Good             | Good          |

| Byte addressability                | Yes           | Yes                | Yes       | No              | Yes              | Yes           |

| Sofe error                         | Low           | High               | High      | High            | No               | No            |

| Logic-process compatibility        | Yes           | Yes                | No        | No              | Possible         | Possible      |

<sup>&</sup>lt;sup>a</sup>Based on state-of-the-art and most-aggressive data from published prototypes.

Hence, STT-MRAM covers the entire application range of eDRAM, as shown in Figure 1. Furthermore, STT-MRAM can go higher than eDRAM in the hierarchy to L2 cache thanks to its short read latency and shorten-able write latency with non-volatility compromise technique of volatile write. Notice that although STT-MRAM cell read latency is much larger than SRAM, the read access latency at memory module level can be comparable or smaller with same capacity, resulting from the much higher density and thus reduced footprint and interconnect delay. Above L2 cache, SRAM is irreplaceable due to its unparalleled speed and throughput, and the multi/many-port capability as the necessity of Register Files and L1 caches. However, the much large write energy of STT-MRAM, even with volatile write, is a major hurdle of using it in higher level caches which have relatively high write activity [5]. Furthermore, although the density and scalability of STT-MRAM device/cell are excellent, such advantages are suppressed by the domination of wiring in its cell array. Therefore, improvements are also necessary for STT-MRAM as a replacement of eDRAM and SRAM in large caches.

#### 1.1 RESEARCH OVERVIEW

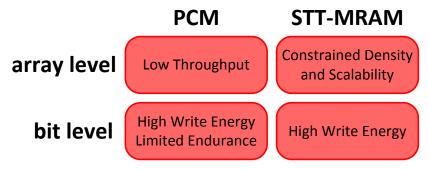

As discussed above, although considered promising, both PCM and STT-MRAM face unique limitations that prevent them from being effectively adopted as main memory and large cache, respectively. Here I further identify these challenges at bit and array levels.

Bit Level Challenge: PCM. PCM write is a thermal-driven process that involves heating (melting) and cooling (crystallizing) the phase change material to change its crystal structure and thus resistance (details in Chapter 2.3). These procedures incur high current injection in the range of  $0.1 \sim 1 mA$  [9, 29]. Such high currents are supplied from high voltage sources of  $2\sim5V$  [7, 29]. Moreover, the currents keep flowing through the phase change material for  $50\sim400ns$  [7, 29] to fully finish melting or crystallizing. Therefore, the per-bit write energy of PCM is quite high. For instance, assuming the conservative write current, voltage, and pulse width to be  $100\mu A$  [9], 2V [7], and 50ns [29] respectively, this leads to  $100\mu A \times 2V \times 50 ns = 10 pJ$  per bit, which is much higher than DRAM's  $\sim 1.5 pJ$  per bit [63]. What makes things worse is the fact that the high write voltages are generated by charge pump circuits from regular power supplies with limited power efficiency. So the actual energy/power consumption is even higher at chip level. On the other hand, due to the repeated heat stress in melting and crystallizing processes, a PCM cell can be written for a limited number of times, typically  $10^8 \sim 10^9$  [81]. While this is better than the  $10^5$  write endurance of Flash, it is much worse than that of a DRAM cell (10<sup>16</sup>) and is a big concern when PCM is used in main memory.

Bit Level Challenge: STT-MRAM. STT-MRAM write uses spin-polarized current flowing through the magnetic device to disturb its magnetic torque in one stable direction, turn the torque, and let it settle in the other stable direction with different resistance (details in Chapter 2.4). Similar to PCM, such procedure also requires high current in the range of  $50\sim500\mu A$  [28, 19], as while as long period of  $10\sim100ns$  [19, 16, 36]. Therefore, STT-MRAM also suffers from high write energy of conservatively  $50\mu A \times 1.2V \times 10ns = 0.6pJ$  per bit, much higher than that of SRAM and eDRAM. Several recent studies proposed to relax the non-volatility requirement from the typical ten year storage-class retention time, to reduce the write pulse width and thus write energy [52]. However, even with such volatile writes,

the write energy still dominates total energy of an STT-MRAM based cache, offsetting the energy savings from low leakage [5].

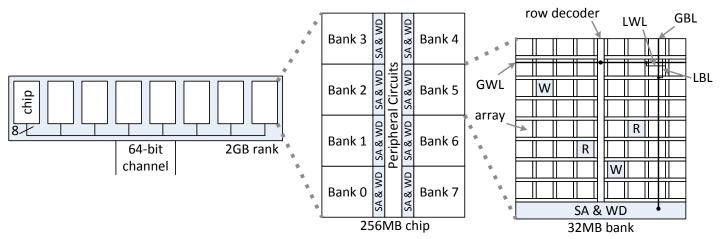

Array Level Challenge: PCM. Besides write energy and endurance, one major challenge for PCM to replace DRAM is its low throughput. For example, a state-of-the-art PCM chip can achieve 40MB/s program throughput [9], while the throughput of even an old DDR2-800 DRAM is 100MB/s per chip. PCM's throughput is constrained by three factors. First, given the large write power per bit, large number of concurrent bit-writes can raise concerns of voltage droop and power supply noise [14]. Hence the number of cells written in parallel has to be restricted [26], which is already constrained by the chip power budget. However, as will be shown in later chapters, our bit level solution can effectively remove large portion of bit-writes and thus provide power headroom for throughput improvement. Also, good scalability of phase change materials implies that aggressive write current scaling can be expected. Therefore, the write power/energy factor is less a concern here [9]. Second, PCM's write operation is not only slow but much slower than its read operation, which is determined by the device characteristics. A typical set (crystallizing) procedure takes at least 120ns [7], and the write latency of multi-level PCM is much worse due to the multi-iteration program-and-verify procedure [4]. Moreover, because of the limited number of concurrent bit-writes, writing a line (e.g. 512 bits) is usually completed in several iterations, with each iteration writing part of the line, incuring  $\sim 1000ns$  page write latency [85]. Obviously, such long writes increase memory bank occupation time and thus block the subsequent accesses. Third, read and write circuits of PCM are usually quite large as a result of high-current, high-voltage operations and complex control. This is even more pronounced considering the extremely small and dense PCM cells of down to  $4F^2$ . To keep the overhead of peripheral circuits low for high area efficiency and high effective density, PCM chips usually utilize limited number of read and write circuits that are globally shared among all arrays in a PCM bank [7, 26, 29, 47, 14, 9], ultimately limiting achievable throughput.

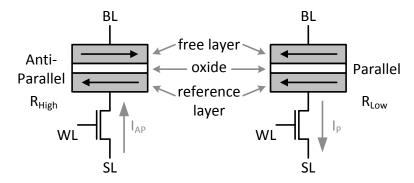

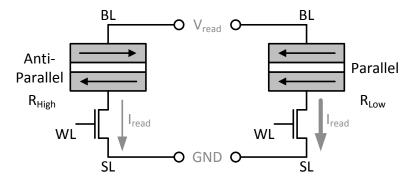

Array Level Challenge: STT-MRAM. Unlike the uni-polar PCM which utilizes the same current direction for read, write-1 and write-0, the magnetic device of STT-MRAM is a bipolar device that changing its state from '0' to '1' requires a different current direction than from '1' to '0'. To provide bi-directional currents to an STT-MRAM cell, a classic array

structure utilizes bitline pairs to control voltages on two ends of a cell [19, 27, 13, 61, 57, 70]. However, with aggressive scaling of the magnetic device and the access transistor [51, 1], the wire width and spacing of bitline pair determine the actual cell size in an array [27, 13, 57] and become the bottleneck to further shrinking memory area, suppressing the benefits of device scaling. In other words, the device/cell level advantages cannot be translated into array level benefits. This problem is usually overlooked due to the illusion of excellent density and scalability of STT-MRAM device/cell.

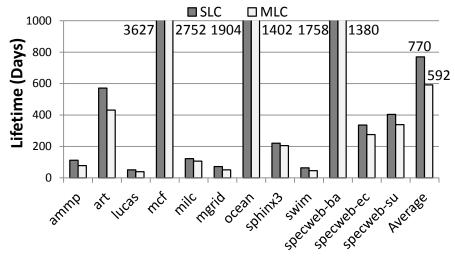

In summary, the challenges of PCM and STT-MRAM are at bit and array levels, as shown in Figure 2. At bit level, both PCM and STT-MRAM suffer from excessive write energy, and PCM has very limited write endurance. At array level, PCM enjoys high density but could not provide competitive throughput due to its long write latency and limited number of read/write circuits. Although STT-MRAM owns satisfactory throughput, its conventional array architecture is constrained on density and scalability by the pitch of per-column bitline pair.

Figure 2: Challenges of PCM and STT-MRAM to be addressed.

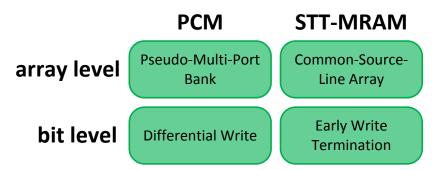

As responses to these challenges, in my research work I develop multiple circuit solutions at corresponding bit or array levels, as listed below.

Bit Level Solution: PCM. In memory write operations, a great portion of bit-writes are redundant. That is, a write into a cell did not change its value. Based on this observation, I implement a circuit-level technique Differential Write [75, 31] to remove these unnecessary bit-write operations in PCM. Before each write, Differential Write performs a read first, and compares the stored data with to-be-written data. Then, only the cells that are actually changed are written, all redundant bit-writes are suppressed. As a result, the write energy and thermal stress on these redundant cells are removed, leading to significant

energy reduction and lifetime improvement. In addition, Differential Write helps reduce write power and opens new opportunities to throughput enhancement and power-budget based memory scheduling [78].

Bit Level Solution: STT-MRAM. Similar to main memory, redundant bit-writes also widely exist in caches. For the same purpose of removing redundant bit-writes, I extend Differential Write to STT-MRAM with specific optimizations to remove the overhead of pre-write read. This is possible because the state change of the magnetic device is not a gradual procedure. Instead, resistance changes abruptly near the end of a write cycle. This means that at the early stage of a write operation, STT-MRAM cell still holds its valid old value. On the other hand, a read operation is performed through applying a voltage on the cell and then sensing the resulting current. A write operation follows exactly the same scenario of flowing current through the cell, except its higher voltage and longer pulse. Therefore, by sensing the write current at early stage of a write, the original cell data can be known, followed by throttling the write current if it is redundant. Such an *Early Write Termination* [76] technique achieves significant energy reduction with no performance penalty.

Array Level Solution: PCM. The slow write operation of PCM can hold a bank for a long time and blocks subsequent read operations. This is quite harmful to system performance as reads are on the critical path of CPU execution while writes are not. In fact, there is possibility to parallel a read with the on-going write because only the write circuits are in use and the read circuits are idle. However, the write operation occupies peripheral circuits like row decoder that are necessary for a read to start. Also, a second access to the same bank may interfere with the existing one and destroys both accesses. I propose a Pseudo-Multi-Port Bank design [78] that allows write and read to happen concurrently in different arrays of the bank, and thus the limited number of read and write circuits are fully utilized to provide parallelism. By leveraging the hierarchical wordline and bitline structures, the decoder result is latched on local wordlines so that the row decoder and global wordlines are released for other accesses to use in a time-multiplexed manner. Besides intra-bank parallelism, the Pseudo-Multi-Port Bank design provides potential for novel memory scheduling enhancements to fully take advantage of intra-bank parallelism and further improve throughput.

Array Level Solution: STT-MRAM. In a conventional dual-bitline array structure, every column of cells has a bitline pair consists of one bitline and one source-line which are identical metal wires. To eliminate the dominance of the bitline pair on cell area, I propose a Common-Souce-Line Array structure [72, 73] in which the per-column source-lines are removed and replaced by per-row source-lines that are shared by cells in the same row. A common-source-line array retains the original read scheme of a dual-bitline array but requires new method to write because writing different cells in a row are no longer independent. I develop novel write schemes and refine the array design to cope with the cell interference problem during a write. Compared to a dual-bitline array, the common-source-line array achieves significant area saving and liberates the scaling potential of future STT-MRAMs.

In summary, my circuit level solutions to the challenges of PCM and STT-MRAM are shown in Figure 3. At bit level, for PCM I implement Differential Write to remove large number of unnecessary bit-writes that do not alter the stored data. It is then extended to STT-MRAM as Early Write Termination, with specific optimizations to remove the overhead of pre-write read. At array level, I propose a Pseudo-Multi-Port PCM bank design to exploit intra-bank parallelism by recycling and reusing shared peripheral circuits between accesses in a time-multiplexed manner. For STT-MRAM I propose a Common-Source-Line Array architecture which uses a shared source-line along the row, essentially leaving only one bitline per column.

Figure 3: Circuit level solutions to the challenges of PCM and STT-MRAM.

Although the proposed solutions are circuit level designs, they also bring forth new potentials and opportunities to other design levels. Therefore in addition to circuit level analyses, for each technique I provide adequate architecture/system level and/or process/device level discussions for more comprehensive insights of my research work.

#### 1.2 DISSERTATION ORGANIZATION

The remainder of this dissertation is organized as follows. Chapter 2 introduces the background knowledge within the scope of this work. The proposed techniques are then detailed in Chapter 3, 4, 5, 6. Chapter 7 thoroughly surveys related work. Finally Chapter 8 discusses potential future research topics and concludes this dissertation.

#### 2.0 BACKGROUND

This chapter first briefly reviews the popular SRAM and DRAM/eDRAM, and then describes the essential characteristics of the emerging PCM and STT-MRAM.

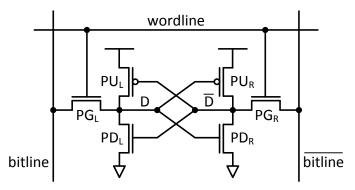

#### 2.1 SRAM

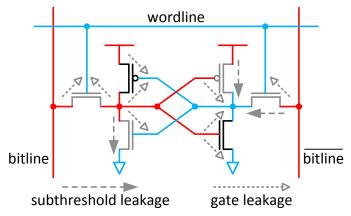

As the name suggests, the storage nodes of Static RAM (SRAM) are "statically" held to power or ground to retain their values as long as power is applied. To achieve this, a standard SRAM cell uses internal feedback based on a symmetric, bi-stable structure as shown in Figure 4. It contains a latch formed by a pair of cross-coupled inverters  $PU_L/PD_L$  and  $PU_R/PD_R$  holding the state, and a pair of access transistors  $PG_L$  and  $PG_R$  controlled by the wordline to read or write the state through the complementary bitlines. The positive feedback ensures the complementary logic values on the two storage nodes D and  $\overline{D}$ , and corrects disturbances caused by leakage or noise.

Figure 4: Schematic of an SRAM cell. PU – Pull Up; PD – Pull Down; PG – Pass Gate.

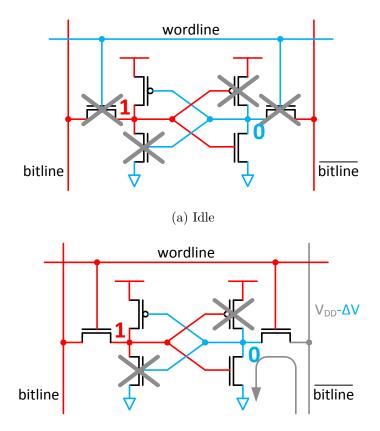

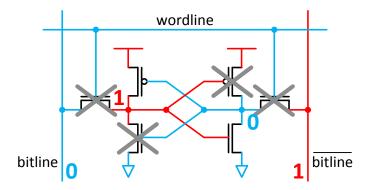

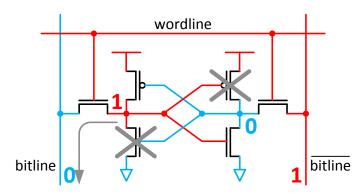

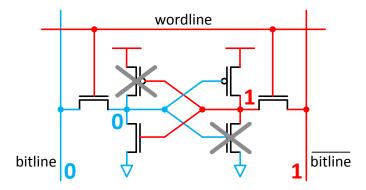

SRAM cell read operation is illustrated in Figure 5. The two bitlines are precharged high at  $V_{DD}$  and then left floating. When the wordline is raised and PGs are turned on, the 0-side bitline is discharged to  $V_{DD} - \Delta V$  through the PD and PG, while the other bitline remains high. In case of small signal sensing, such  $\Delta V$  is in the range of  $100\sim200mV$  which can be captured by the sense amplifier circuit connected to bitlines to determine the logic value. In case of large signal sensing,  $\Delta V = V_{DD}$  so bitlines swing full-rail and can drive skewed inverters directly. In both cases, the cell read latency is only in the order of 100ps.

(b) Turn on access transistors and pull down the 0-side bitline Figure 5: SRAM cell read operation.

The write operation is shown in Figure 6. According to the write data, one bitline is held low by the write driver circuit while the other floats high. When the wordline is turned on, the 1-node is discharged by the write driver through PG, and the inverter on the 0-node will be eventually triggered once the 1-node is low enough, which ultimately flip the cell state using positive feedback. Thanks to such feedback mechanism, SRAM cell write is also very fast.

(a) Set bitline voltages

(b) Turn on access transistors and discharge the 1-node

(c) 0-node inverter triggered by the discharged 1-node and cell flips to the new state

Figure 6: SRAM cell write operation.

Although such multi-transistor cell structure provides stable storage and fast read/write, it also leads to large cell area  $(>130F^2)$  and thus low density. The other resulting drawback is high leakage. Figure 7 illustrates the subthreshold and gate leakage paths in an SRAM cell (junction leakages are not shown). As shown in the figure, each cell possesses multiple

leakage paths. When many SRAM cells are organized into memory arrays and blocks, the total leakage becomes significant. This is especially problematic in large caches with millions of SRAM cells even with advanced leakage control schemes. Therefore, leakage powers of SRAM memories are usually dominated by cell leakage.

Figure 7: Leakage currents in an SRAM cell.

Figure 8: An 8T dual-port SRAM cell with one read port and one write port.

On the other hand, SRAM cell features unparalleled flexibility for function extensions. For example, the 8-transistor dual-port cell shown in Figure 8 provides a separate read port by adding a duplicated read path (PD and PG) and the corresponding wordline and bitline to the standard 6-transistor cell. Thanks to its decoupled structure, both read and write portions of the cell can be independently optimized, leading to better margins and therefore lower  $V_{DD-min}$ , which is crucial for L1 caches to sustain aggressive DVFS of the processor. To achieve higher throughput as required by register files, more read ports (PD and PG) and write ports (a pair of PGs) can be added at the expense of larger area and higher

leakage. Furthermore, other structural extensions are also available for two bi-directional ports, Content-Addressable Memory (CAM), subthreshold memory, etc.

In summary, thanks to its fast operations, multi-port capability, and process compatibility, SRAM is widely used in all kinds of on-chip storage. On the other hand, due to its low density and high leakage, SRAM is becoming less appealing in large on-chip caches.

#### 2.2 DRAM & EDRAM

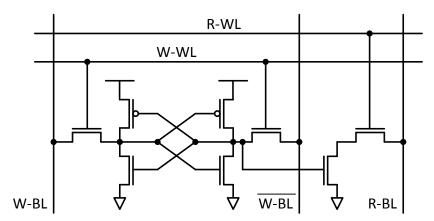

As opposed to SRAM, Dynamic RAM (DRAM) stores data as charge on a capacitor that is "dynamically" floating. Thus, the basic cell is substantially simpler and smaller than SRAM, as shown in Figure 9. It only consists of a capacitor to store charges, and a pass gate transistor controlled by the wordline (WL) to read or write the cell through the single bitline (BL).

Figure 9: Schematic of a DRAM cell.

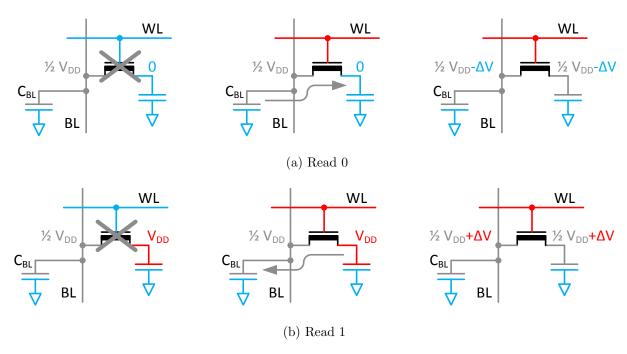

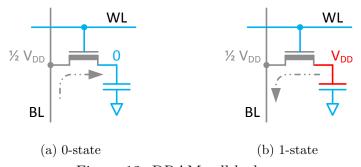

DRAM cell read operation is illustrated in Figure 10. The BL is precharged to the mid-point voltage  $\frac{1}{2}V_{DD}$  and then left floating. When the WL is raised and the access transistor is turned on, charge sharing happens automatically between cell capacitor and BL capacitance. At the end of charge sharing, the BL and the cell reach a common voltage which is  $\Delta V$  higher or lower than  $\frac{1}{2}V_{DD}$ , and such  $\Delta V$  can be used by sense amplifier (SA) circuit to determine the logic value. However, at the same time the voltage stored on the cell capacitor is destroyed. This requires to equipe every BL with a SA which can amplify the  $\Delta V$  to a logic level on BL and cell, so the full-rail voltage is restored into every cell. Therefore, the number of SAs in a DRAM memory equals to the number of cells on one row. This entire row of SAs also acts as the row buffer: WL and SAs remain active after data

sensing, and SAs hold the sensed data as full-rail voltages on BLs which can be accessed by I/O using column address. Because DRAM cell and thus BL pitch is small, a 1:1 ratio of BL:SA is challenging. Fortunately, a DRAM SA is quite simple to consist of only 2 cross-coupled inverters, and layout tricks can loose the SA pitch to be  $2 \sim 4 \times$  the BL pitch. DRAM read operation is much slower than SRAM due to the RC delay of charge sharing and the weak SA driving long BL. Also, such destructive read is extremely energy inefficient because the mandatory restore must happen on all BLs and cells even if only a very small portion of the row is accessed by I/O.

Figure 10: DRAM cell read operation.

The write operation is shown in Figure 11. According to the write data, the write driver (WD) circuit overpowers the SA which then pulls the BL to  $V_{DD}$  or ground. The BL voltage is then gradually forced onto the cell capacitor by charging or discharging through the access transistor. Therefore in case of open-page access (row buffer is active), a DRAM write is always "write-through": the write data overdrives SA row buffer as well as the cell. Such write operation, and similarly the restore operation after a read, is quite slow as a result of the RC behavior on BL and cell.

Because the dynamic storage node in DRAM cell is not held to power or ground, charges leak into or out of the cell over time which gradually weakens the voltage margin between

Figure 11: DRAM cell write operation.

cell and BL, as shown in Figure 12. The stored value is lost when the margin becomes too low to be distinguished by the read circuit. Therefore, DRAM cells must be periodically read and refreshed to restore the voltage on the cell capacitor. The time between the value is fully restored/written to the cell to the value expires is defined as the *retention time*. Obviously, longer retention time is favorable to mitigate the energy consumption and latency/throughput impacts of refresh operations.

Figure 12: DRAM cell leakage.

Suppressing cell leakage is one of the most effective ways to prolong retention time. In current commodity DRAM technologies, the cell access transistor has very high  $V_{th}$  to reduce subthreshold leakage that a  $V_{DD}$  at its gate can barely turn it on. So DRAM wordlines are

at a boosted voltage domain  $V_{PP}$  [81, 83] to 1) fully turn on access transistor for read and write, and 2) offset the  $V_{th}$  drop when passing a high voltage (logic 1) throught the nMOS access transistor. Also, inactive wordlines are pulled to a negative voltage below ground so the gate of the access transistor is more inversely biased to further suppress leakage [81, 2]. Furthermore, the structure, material, and fabrication of the access transistor are actually specially engineered for leakage control, and more efforts are needed in deeper scaled technologies.

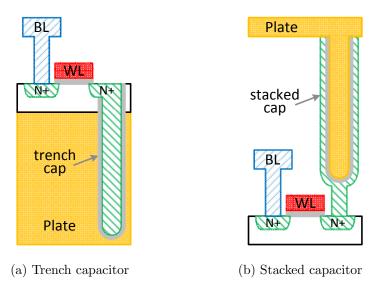

Building large cell capacitor is also critical for retention time. This is usually implemented as trench or stacked capacitor [81]. A trench capacitor is essentially a deep hole etched into the silicon substrate, as illustrated in Figure 13(a). In contrast, the stacked implementation resides above the cell transistor, as shown in Figure 13(b). By exploiting vertical dimension spaces, both kinds of capacitor can achieve very high capacitance in small footprint. Because capacitance is directly proportional to physical dimensions of a capacitor device [37, 60], modern implementations of both device types tend to have very high and growing aspect ratio with technology scaling [81], i.e. they become deeper/taller to maintain capacitance with thrinking footprint. This creates fundamental challenges in the fabrication process and circuit integration, which ultimately limit the DRAM scaling.

Figure 13: Cross-section comparison of DRAM cells with trench and stacked capacitors.

Commercial stand-alone DRAMs are built in specialized processes optimized for dense capacitor structures to offer a cell size down to  $6F^2$ , but they also have much higher latency

and are not compatible with micro-processor/SoC/ASIC fabrication processes. Embedded DRAMs (eDRAM) share the same fundamentals with stand-alone DRAMs but trade density and retention time for logic process compatibility and lower latency, so that it can be integrated on-chip as an SRAM alternative in large caches to provide higher density and lower power [2]. Some types of eDRAM use capacitor-less multi-transistor cell to totally eliminate the extra complexity and cost of capacitor integration [11].

In summary, DRAM's high density and low power earned it the position in high capacity main memory. Its embedded variants are also preferable to SRAM in large caches. However, the worsening refresh problem, energy inefficiency, and scaling difficulty are unique challenges in future DRAM generations.

#### 2.3 PCM

Analogous to DRAM that uses a capacitor device to store a bit data, Phase Change Memory (PCM) utilizes a special device made of phase change material to remember information. The phase change material is one type of chalcogenide alloy, such as  $Ge_2Sb_2Te_5$  (or GST in short), which can exist in two stable physical states: amorphous and crystalline. In the amorphous state, the material structure is highly disordered and thus highly resistive. In the crystalline state, the material has a regular crystalline structure and exhibits low resistivity. PCM exploits the significant difference in resistivity (>10<sup>2</sup>) between these two states to store data, dissimilar from SRAM and DRAM that stores data as voltage levels. Typically, a cell in the amorphous state (high resistance) is regarded as a RESET state (or logic '0'), and a cell in crystalline state (low resistance) is regarded as a SET state (or logic '1'). The state of a GST device is preserved even after the cell is powered off, meaning that PCM is non-volatile. PCM also has good data retention time around ten years in general [81, 26, 4].

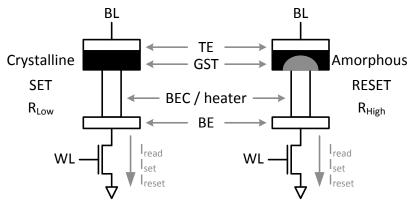

Figure 14 illustrates a PCM cell showing the structure of a typical storage node. The device usually consists of a thin layer of GST and a joule heater (or Bottom Electrode Contact (BEC)), sandwiched between top and bottom electrodes (TE and BE) that provide electronic contacts with the bitline (BL) and the access device (an nMOS in this example).

Figure 14: Conceptual view of a PCM cell showing phase change device structure.

Once the access transistor is enabled by the wordline (WL), read ( $I_{read}$ ) or write ( $I_{SET}$ ,  $I_{RESET}$ ) currents from the BL can flow through the cell. These are essentially different from the voltage-mode/charge-based read/write operations of SRAM and DRAM.

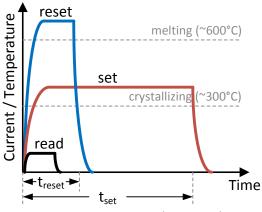

Writing a PCM cell requires changing the physical state of its GST material. This is performed by injecting write currents for the heater to heat the GST at their junction. There are two write operations controlled by the applied voltage/current and duration, as shown in Figure 15. The SET operation heats GST above crystallization temperature ( $\sim 300^{\circ}$ C) but below melting temperature ( $\sim 600^{\circ}$ C) over a period of time with gradual quenching process. This places the entire GST in the low-resistance ( $1K\sim 2K\Omega$  [40, 7]) crystalline state (black in Figure 14). The RESET operation heats GST above melting temperature with fast quenching. This turns part of the GST near the junction into high resistance ( $100K\sim 700K\Omega$  [40, 29]) amorphous state (the gray "mushroom cap" in Figure 14).

Figure 15: Read and write voltage/current/temperature pulses.

Such write operations contribute to the main limitations of PCM. Due to the heating and cooling processes, both SET and RESET take relatively long time to complete, and SET ( $150\sim400ns$  [9, 29]) is slower than RESET ( $50\sim100ns$  [7, 9]). These procedures incur high current injection in the range of  $0.1\sim1mA$  [9, 29] which are supplied from high voltage sources of  $2\sim5V$  [7, 29]. Therefore, the write power and energy per PCM cell are quite high. Given limited power budget, the number of cells written concurrently has to be restricted [26] to prevent excessive voltage droop and power supply noise [14], leading to multi-iteration operation with extremely long total latency in writing a wide line/page [26, 29, 85]. Such long writes increase memory bank occupation time and thus block subsequent accesses, ultimately hurt memory throughput and system performance, as will be discussed in Chapter 5. Also as a result of the repeated heat stress in melting and crystallizing, a PCM cell can be written for a limited number of times, typically  $10^8\sim10^9$  [81], which is orders of magnitude lower than SRAM and DRAM ( $10^{16}$ ). As will be demonstrated in Chapter 3, a PCM main memory without any lifetime improvement technique may last only  $\sim200$  days running a typical SPEC CPU program.

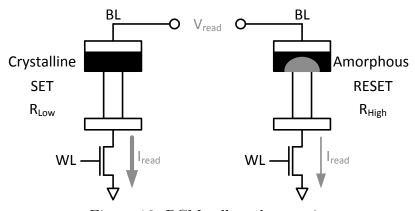

Figure 16: PCM cell read operation.

Reading data from a PCM cell involves sensing the resistance of the GST, as shown in Figure 16. When a regulated low voltage  $V_{read}$  is applied on BL, the amount of current  $I_{read}$  that flows from BL to the cell is determined by the cell resistance, i.e. larger with a SET cell and smaller with a RESET cell. The sense amplifer (SA) then compares  $I_{read}$  with a reference current  $I_{ref}$ , which is  $I_{read-RESET} < I_{ref} < I_{read-SET}$ , to determine the logic value. Notice that from a cell's perspective, the only differences between read and write are the

amount and duration of applied current. Because  $V_{read}$  and  $I_{read}$  are intentionally upper limited, PCM read operation is non-destructive and has negligible heat stress compared to write operations. And read is much faster than write with  $\sim 60ns$  random access latency at chip level [7, 26].

One distinguished benefit of such current-mode read/write operations is the efficient column multiplexing. In DRAM, charge sharing between cell and BL happens automatically once WL turns on, which destroys the entire row of data. This requires to restore every cell and drive/precharge every BL on the row, even if only a very small portion of the row is selected by column multiplexer for read/write. Similarly in SRAM, one BL per cell is discharged automatically once WL turns on, no matter the created voltage margin is used or not by SA, bringing forth stability concerns. And obviously all the BLs has to be precharged after the access. In other words, in both SRAM and DRAM the read process takes place unconditionally on every cell of an active row, regardless of the column multiplexer configuration. Therefore, with voltage-mode operations, a significant portion of energy is wasted on these "half-selected" (row-selected but not column-selected) cells and their BLs. With current-mode operations, cells are always in a passive position, and currents from read or write circuits are only directed to column-selected BLs and cells. Therefore on half-selected cells and BLs, neither the storage is violated nor any energy is wasted.

Figure 17: Three types of PCM cell using different access devices. The storage node is depicted as the alterable resistor.

There are three main options for the access device in a PCM cell: MOS, BTJ, and diode. The MOS-selected [7, 3, 40, 26, 17, 47] and BJT-selected [15, 4, 62] cells in Figure 17(a) and 17(b) are quite similar: WL controls the conductivity of the access device, and read and

write currents flow through the cell to ground. The cell sizes are dominated by the access devices that are larger than the storage node. The diode-selected cell [29, 14, 9] in Figure 17(c) is fundamentally different that the active WL is grounded to drain read and write currents. Thanks to its simplest structure and the tiny diode device that can be stacked with the GST device, a diode-selected cell can achieve the smallest cell size of  $4F^2$  [14, 9], which is just a cross-point of WL and BL. However, because turning on the diode requires an applied voltage which consumes the operation voltage headroom, the read and write operation voltages should be higher than the MOS-selected cell by the built-in potential (or threshold voltage) of a diode [29].

In PCM chips, boosted voltages are widely used mainly for two reasons. First of all, because GST resistance is quite large, high voltage is required to generate the high write currents. Secondly, because of the current-driven read and write operations, it is important to mitigate signal IR drop by minimizing the serial parasitic resistance in the read/write current path. So high voltages are also applied to the switch devices in the path, e.g. cell access transistors and column multiplexers, to make them more conductive [26, 9]. The huge current load, the coexistence of multiple boosted voltage levels, and the fine-grain controls for on/off scheduling, position compensation [40], pulse shaping [29], etc. lead to complex and large voltage regulation systems, mainly consist of charge pumps, that usually occupy considerable silicon area in high density PCM chips [14, 9]. Also as a result of the high current/voltage operations, read and write circuits of PCM are usually quite large in size. Hence, when pairing them with the extremely dense cells, their numbers are limited, and they are highly shared through hierarchical connections, for the purposes of pitch matching and density conservation.

The non-volatility of PCM is a new opportunity to exploit. Because the non-volatile, zero-leakage cells can preserve data without power, it is possible to power down an entire memory bank or chip during idle phases to eliminate leakage power on peripheral circuits [75, 31], which is crucial to meet the low-power requirements of future memory systems. Moreover, the physical state based storage is immune to soft errors caused by alpha particle or cosmic radiation usually seen in voltage/charge based storages [85]. PCM also offers much better scalability that the write currents reduce with the shrinking of GST device [81, 7],

which is also a substantial solution to the power-bounded throughput problem [9]. Hence PCM provides a truly scalable solution compared to conventional DRAM.

Also, given the large resistance contrast between crystalline and amorphous states, it is possible to exploit partial crystallization states to store two or more bits per cell, forming a multi-level cell (MLC) PCM [4]. The MLC write typically uses an iterative Program-and-Verify (P&V) scheme. Here, a RESET operation is always done first to put the cell in an initial state. A series of SET and verify (read) operations then follow until the target resistance level is reached. This achieves precise control of the smaller resistance ranges, but also incurs extremely long latency [4]. When combining MLC storage with the  $4F^2$  cell size, PCM can offer much better storage density than DRAM.

#### 2.4 STT-MRAM

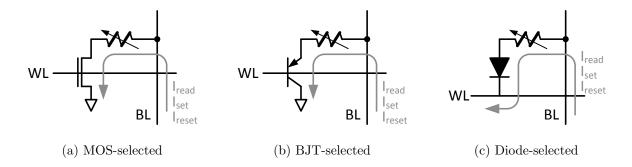

Despite the many common characteristics with PCM, such as resistance-based storage, current-mode read/write operations, non-volatility, good scalability, soft error immunity, etc., Spin-Torque-Transfer Magnetic-RAM (STT-MRAM) is based on a unique storage mechanism using the Magnetic Tunnel Junction (MTJ) device as the storage element. Figure 18 illustrates an STT-MRAM cell showing the structure of a typical MTJ device. It includes two ferromagnetic layers separated by one oxide barrier layer. The reference layer has a fixed magnetization direction and the free layer has an alterable one. The magnetization direction of free layer is changed by passing a driving current spin-polarized by reference layer [19]: a current from reference layer to free layer rotates the direction of free layer to the opposite of reference layer, resulting an anti-parallel (AP) and high-resistance state of MTJ (logic '1'); a current in the other direction parallelizes directions of the two layers, resulting an parallel (P) and low-resistance state (logic '0'). The state of an MTJ device is preserved even after the cell is powered off, meaning that STT-MRAM is non-volatile. STT-MRAM also has good data retention time around ten years in general [81].

Besides the current direction requirement, in either AP- or P-writing, the write current must be larger than the threshold or switching current of the MTJ device, and it must be

Figure 18: Conceptual view of an STT-MRAM cell showing MTJ structure.

applied for a certain amount of time (switching latency), to successfully alter the MTJ state [19]. Actually, during write operations, MTJ state and resistance change abruptly near the end of a write cycle [58, 6], different from the gradual, cumulative procedure in PCM writes. In other words, at the early stage of a write operation, an STT-MRAM cell still holds its valid old value. Also, there exist dependencies between switching current and switching latency: the larger the applied write current, the shorter the required time to flip the MTJ state [19, 12].

The underlying principle of MTJ switching is that the spin-polarized current disturbs the magnetic torque of free layer in one stable direction, turn the torque, and let it settle in the other stable direction. Similar to PCM write, such procedure also requires high current in the range of  $50\sim500\mu A$  [28, 19], as while as long period of  $10\sim100ns$  [19, 16, 36]. Therefore, STT-MRAM also suffers from high write power and energy per bit. Fortunately, unlike PCM, the MTJ device generally has unlimited write endurance ( $10^{15}$ ) [81].

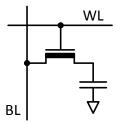

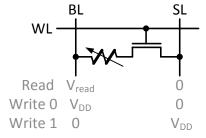

Figure 19: Schematic of an STT-MRAM cell. (MTJ = alterable resistor)

Because of such bipolar nature of MTJ switching, a MOS transistor is the undoubted choice of access device to provide bi-directional conductivity. Also, a pair of wires, one bitline

(BL) and one source-line (SL), is utilized to manipulate voltages on two ends of a cell, as shown in Figure 19. Due to the simple 1 MOS + 1 MTJ structure, the width and spacing of this wire pair usually determine the actual cell size in an array [27, 13, 57].

Similar to PCM, reading data from an STT-MRAM cell is performed by sensing the resistance of the MTJ, as shown in Figure 20. When a regulated low voltage  $V_{read}$  is applied on BL and SL is grounded, the read current  $I_{read}$  that is inversely proportional to the cell resistance is compared by the sense amplifer (SA) with a reference current  $I_{ref}$ , which is  $I_{read-AP} < I_{ref} < I_{read-P}$ , to determine the logic value. Notice that the direction of read current can be determined at design time to be same as either AP- or P-writing. Such a choice is usually made by considering the combined effective resistance of MTJ and nMOS, for the purpose of maximizing sensing margin [36]. And read is usually faster than write with <10ns latency [16, 12].

Figure 20: STT-MRAM cell read operation.

For read operation, one of the most important MTJ characteristics is the difference between high and low resistances, formally defined as Tunneling Magnetoresistance Ratio (TMR):

$$TMR = \frac{R_{AP} - R_P}{R_P}$$

Another crucial factor is the absolute MTJ resistance. Larger TMR and resistance are favorable to yield better sensing margin and delay [12, 1], because the resistance difference can be more distinguishable when parasitic resistances are present. Current STT-MRAM prototypes usually have TMR of 100%~130% [19, 36, 12] and resistance in the range of

$2K\sim9.5K\Omega$  [19, 27]. These two parameters will be gradually improved over process generations via device level advancements [81, 12, 1].

STT-MRAM shares many benefits with PCM, e.g. efficient column multiplexing, zero cell leakage, non-volatility, soft error immunity, etc. As one advantage over PCM, STT-MRAM generally does not require high voltages to operate, making it more favorable as embedded memories for on-chip applications (also thanks to its unlimited write endurance). STT-MRAM also features very good scalability that the MTJ switching current can reduce with the shrinking of MTJ size [81, 12, 1]. This is a substantial improvement over previous generations of toggle MRAM technology which writes MTJ using magnetic field produced by the current on an adjacent wire [39]. With the toggle MRAM cell scaling down, such write current actually scales up to maintain the same energy density [1, 34]. Therefore, STT-MRAM is the absolute choice of future MRAM generations.

MTJ was also considered as a candidate in building cross-point memory arrays [34, 46]. Cross-point arrays achieve high cell density as there are no selection devices (typically much larger than the memory device itself) in cells. However, it is also difficult to select a cell without disturbing the adjacent ones, as a result of sneaky paths that lead to huge leakage current [34]. With MTJ, such sneaky path effect could be prohibitive as a result of its low TMR and low absolute resistance. For example, in a 64×64 array of a cross-point MRAM prototype [46], 97% of current is leaked away, and only 3% is effective in writing. This in turn limits the achievable sub-array size and area efficiency, and requires complex peripheral circuits to bias unselected cells, offsetting the benefit of high cell density. Therefore, MTJ is inferior to other bipolar memory devices with large resistance ratios, such as Memristor [10, 54], in building cross-point memory arrays.

# 3.0 BIT LEVEL ENERGY REDUCTION AND LIFETIME IMPROVEMENT FOR PCM

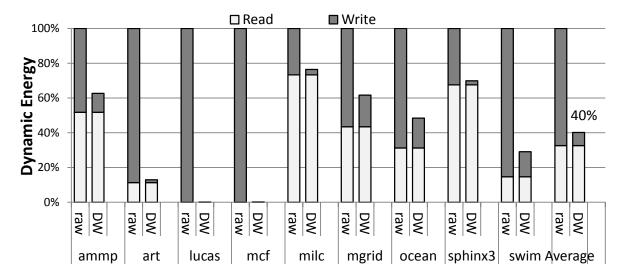

Despite the advantages like density, leakage, non-volatility, scalability and reliability, two major shortcomings of PCM as the main memory are high write energy and limited write endurance. Based on the observation of redundant bit-writes, in this chapter I develop circuits to implement the Differential Write (DW) technique that removes these unnecessary bit-write operations in PCM [75, 31]. Because only the cells that are actually changed are written, it is capable of both reducing write energy and extending cell lifetime. Evaluations show that DW offers 60% dynamic energy saving and 4.5× lifetime improvement on average. When combining DW with simple wear-leveling techniques, it is demonstrated that PCM-based main memory is practical in terms of lifetime [75, 31]. In addition, Differential Write helps reduce write power and opens new opportunities to throughput enhancement and power-budget based memory scheduling [78]. Thanks to its fundamentality and simplicity, DW can be seemlessly integrated into upper level techniques. Notably, it was used as the basis of some later studies [8, 18, 78], and also incorporated in a Samsung prototype [14].

Figure 21: Bit level solution for PCM: Differential Write.

## 3.1 ENERGY AND LIFETIME PROBLEMS OF PCM

Both write energy and write endurance challenges are results of the phase change material characteristics. PCM's thermal-driven write processes incur high current injection in the range of  $0.1 \sim 1mA$  [9, 29]. Such high currents are supplied from high voltage sources of  $2 \sim 5V$  [7, 29]. Moreover, the currents keep flowing through the phase change material for  $50 \sim 400ns$  [7, 29] to fully finish melting or crystallizing. Therefore, the per-bit write energy of PCM is quite high. For instance, assuming the conservative write current, voltage, and pulse width to be  $100\mu A$  [9], 2V [7], and 50ns [29] respectively, this leads to  $100\mu A \times 2V \times 50ns = 10pJ$  per bit, which is much higher than DRAM's  $\sim 1.5pJ$  per bit [63]. What makes things worse is the fact that the high write voltages are generated by charge pump circuits from regular power supplies with limited power efficiency. So the actual energy/power consumption is even higher at chip level. Furthermore, the low leakage of PCM can lead to significant leakage saving over DRAM, given that leakage contributes to large portion of main memory energy due to the low activity. However such benefit may be overwhelmed by the excessive write energy.

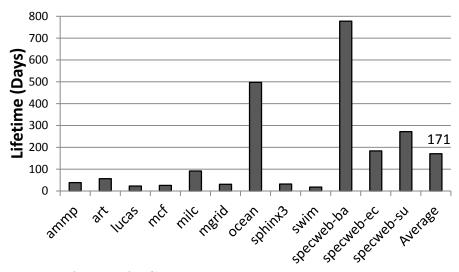

On the other hand, due to the repeated heat stress in melting and crystallizing processes, a PCM cell can be written for a limited number of times, typically  $10^8 \sim 10^9$  [81]. While this is better than the  $10^5$  write endurance of Flash, it is much worse than that of a DRAM cell  $(10^{16})$  and is a big concern when PCM is used in main memory. To illustrate the problem, the "unprotected" lifetimes of a PCM main memory are tested using a variety of benchmarks including SPEC2K, SPEC2006, and SPECWeb <sup>1</sup>. Here I refer the lifetime of a PCM to the duration before the first cell starts to fail, and the number of rewrite cycles for a PCM cell is assumed to be  $10^8$ . Figure 22 shows the projected lifetime of PCM memory without any enhancement technique. As shown in the figure, the results range from 25 days for mcf to 777 days for specweb-banking, and the average is only 171 days. Hence in order to make PCM main memory practical, lifetime improvement techniques are needed to extend PCM lifetime to an acceptable level.

<sup>&</sup>lt;sup>1</sup>Architectural simulations in this chapter were performed by Ping Zhou at Department of Electrical & Computer Engineering, University of Pittsburgh.

Figure 22: Lifetime of PCM memory without any improvement technique.

## 3.2 THE OPPORTUNITY: REDUNDANT BIT-WRITES

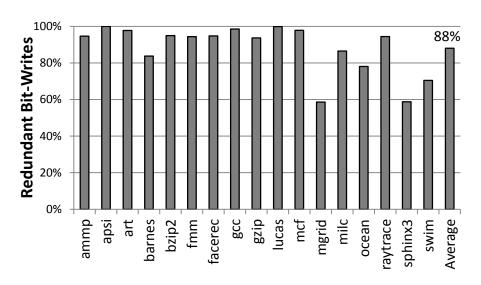

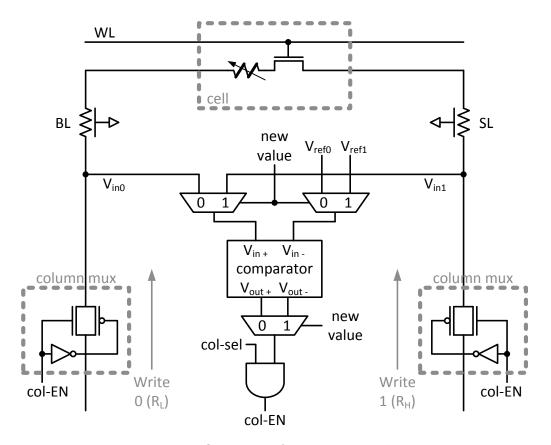

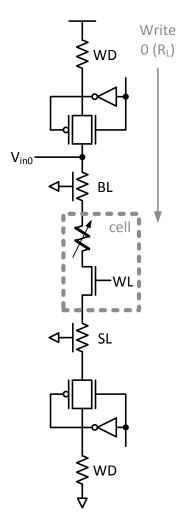

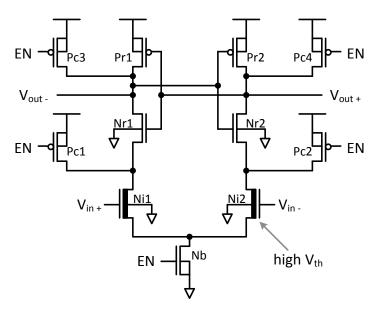

To improve the write energy and endurance of PCM memory, one intuitive step is to reduce the total number of bit-writes. Several existing studies have shown that there is a high probability that a write into a cache or memory location does not change its content, and therefore can be removed. Such an observation has been used at the word level for L1 cache [32], multiprocessors [33], and off-chip memories [30]. Intuitively, this phenomenon is more significant at bit level [75, 31].