# MODULAR MULTILEVEL CONVERTER BASED HIGH VOLTAGE DC PROTECTION

by

#### **Patrick Thomas Lewis**

B.S. in Electrical Engineering, University of Pittsburgh 2012

Submitted to the Graduate Faculty of

the Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

Patrick T. Lewis

It was defended on

November 24, 2014

and approved by

Gregory F. Reed Ph.D., Professor,

Department of Electrical and Computer Engineering

Tom McDermott Ph.D., Assistant Professor,

Department of Electrical and Computer Engineering

Zhi-Hong Mao Ph.D., Associate Professor,

Department of Electrical and Computer Engineering

Thesis Advisor: Gregory F. Reed Ph.D., Professor,

Department of Electrical and Computer Engineering

Copyright © by Patrick T. Lewis

2014

# MODULAR MULTILEVEL CONVERTER BASED HIGH VOLTAGE DC PROTECTION

Patrick T. Lewis, M.S.

University of Pittsburgh, 2014

This thesis addresses the protection of a high voltage DC (HVDC) system that utilizes the modular multilevel converter (MMC) topology, a voltage sourced converter (VSC), and incorporates two transmission line sections, a cable and an overhead line. Protection for high voltage AC systems is mature in installation experience. On the other hand there are many avenues of research needs for the protection of the more modern technology, HVDC.

The avenue of system protection focused upon in this work is the system restart sequence post DC side faults. This restart sequence is simply the sequence of events that occur necessarily in order to restart the HVDC system after a specified fault is already isolated and diminished. This avenue of system protection is focused upon but not exclusively. Fault isolation and suppression are also protection topics noted and discussed. Ultimately a fault section identification protection method is required for restart of the HVDC system when there are two transmission line sections. Specific to the HVDC system design presented there is desire for no communication channel between the converter stations of the system. Additionally, recovery of the system to normal operation is preferably as fast as possible in order to maintain power delivery with minimal disturbance. Solutions to these challenges are investigated and proposed.

The first part of this thesis work involves the detailed modeling of the MMC-HVDC system in the PSCAD simulation environment. After providing the validation of the model, both a parameter sensitivity analysis and an in-depth fault case analysis are performed for the overall

examination of protection needs of the HVDC design. The fault analysis evaluation brings to light the means for a unique protection coordination method for the system design during post-fault system restart. The protection method ensures that cable faults, assumed to be permanent faults, are not reclosed upon while for any non-permanent faults attempt of reclose is made. The protection coordination method proposed in this work is unique in that it utilizes a signal characteristic to the HVDC system design to implement protection coordination without the use of a communications channel between converter stations.

## TABLE OF CONTENTS

| AC  | KNO | WLEDGMENTSXII                                            | Ι |

|-----|-----|----------------------------------------------------------|---|

| 1.0 |     | INTRODUCTION                                             | 1 |

|     | 1.1 | BACKGROUND                                               | 1 |

|     | 1.2 | MMC-HVDC PROTECTION DESIGN CONDITIONS                    | 7 |

|     | 1.3 | MOTIVATION AND CONTRIBUTIONS                             | 8 |

|     | 1.4 | CONTENT ROAD MAP                                         | 9 |

| 2.0 |     | MMC-HVDC SYSTEM MODELING 1                               | 1 |

|     | 2.1 | MODULAR MULTILEVEL CONVERTER MODELING 1                  | 2 |

|     |     | 2.1.1 System Parameters                                  | 3 |

|     |     | 2.1.2 MMC Circuit Synthesis and Capacitor Initialization | 8 |

|     |     | 2.1.3 Capacitor Balancing Algorithm                      | 7 |

|     |     | 2.1.4 Controller Design and Tuning                       | 1 |

|     | 2.2 | HVDC SYSTEM MODEL VALIDATION4                            | 1 |

|     | 2.3 | CONCLUSION 5.                                            | 3 |

| 3.0 |     | PARAMETER TRENDS RESULTING FROM SENSITIVITY ANALYSIS 5   | 4 |

|     | 3.1 | TREND OF DC LINE REACTANCE5                              | 6 |

|     | 3.2 | TREND OF TRANSFORMER REACTANCE 6                         | 0 |

|     | 3.3 | TREND OF ASYMMETRICAL ARM REACTANCE 6                    | 2 |

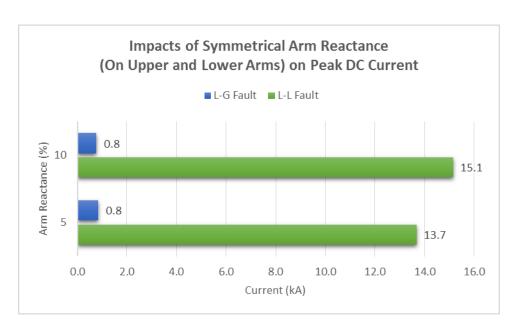

|     | 3.4  | TRENDS OF SYMMETRICAL ARM REACTANCE66                      |

|-----|------|------------------------------------------------------------|

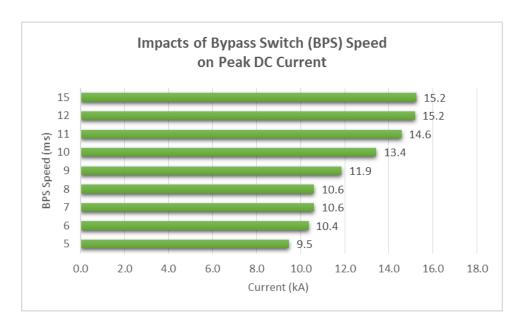

|     | 3.5  | TREND OF BYPASS SWITCH (BPS) SEED68                        |

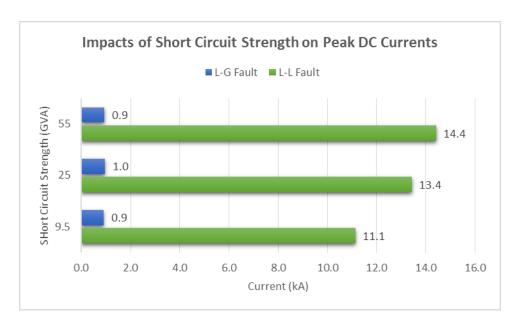

|     | 3.6  | TRENDS OF SHORT CIRCUIT STRENGTH70                         |

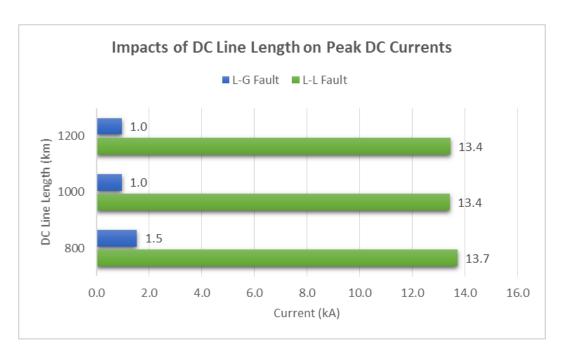

|     | 3.7  | TREND OF DC LINE LENGTH73                                  |

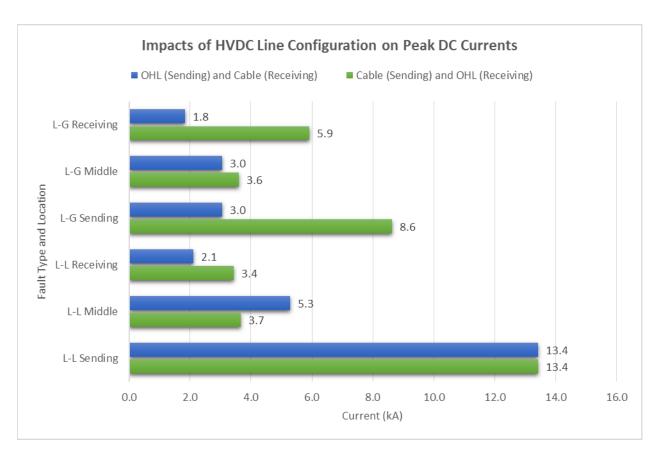

|     | 3.8  | TREND OF HVDC LINE CONFIGURATION74                         |

|     | 3.9  | CONCLUSION                                                 |

| 4.0 |      | FAULT ANALYSIS AND EVALUATION OF CHARACTERISTIC SIGNAL. 78 |

|     | 4.1  | SYSTEM PROTECTION BACKGROUND78                             |

|     | 4.2  | FAULT PROTECTION ANALYSIS 81                               |

|     | 4.3  | CHARACTERISTIC SIGNAL FOR SECTION IDENTIFICATION 84        |

| 5.0 |      | FAULT SECTION IDENTIFICATION PROTECTION METHOD96           |

|     | 5.1  | BASIS FOR PROPOSED NOVEL PROTECTION METHOD96               |

|     |      | 5.1.1 Conditions Met and Oscillation Applied               |

|     |      | 5.1.2 Resolving Problematic L-L Faults within Method 102   |

|     | 5.2  | PROTECTIVE RELAY CONSIDERATIONS 115                        |

|     | 5.3  | CONCLUSION 117                                             |

| 6.0 |      | CONCLUSION118                                              |

|     | 6.1  | FUTURE WORK                                                |

| API | PENI | DIX A                                                      |

| DID | TIO  | CD A DILIV                                                 |

## LIST OF TABLES

| Table 1: HVDC System Parameters for Validation Model Development                                                              |

|-------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Parameters Simulated with Associated Sensitivity Ranges for Trends Analysis 55                                       |

| Table 3: Validation Model Parameters, Used as the Base Cases of Trends Analysis                                               |

| Table 4: Case List Showing Variance of DC Line Reactance                                                                      |

| Table 5: Case List Showing Variance of Transformer Reactance                                                                  |

| Table 6: Case List Showing Variance of Asymmetrical Arm Reactance                                                             |

| Table 7: Case List Showing Variance of Symmetrical Arm Reactance                                                              |

| Table 8: Case List Showing Variance of Bypass Switch (BPS) Speed                                                              |

| Table 9: Case List Showing Variance of Short Circuit Strength                                                                 |

| Table 10: Case List Showing Variance of DC Line Length                                                                        |

| Table 11: Case List Showing Variance of HVDC Line Configuration                                                               |

| Table 12: Parameters Selected from Trends Analysis for Protection Analysis                                                    |

| Table 13: Protection Sequence                                                                                                 |

| Table 14: Sets of Cases for the Fault Protection Analysis                                                                     |

| Table 15: Frequency Sweep of Cable Capacitance and Inductance per Meter for the Frequency Dependent Cable Model in Simulation |

| Table 16: Relay Coordination Table for the DC System relating to Section Identification 114                                   |

## LIST OF FIGURES

| Figure 1: Schematic of the Modular Multilevel Converter Topology                                                              | 3 |

|-------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2: HVDC System Design with Cable and Overhead Line Sections Making up the HVDC Line                                    |   |

| Figure 3: One-Line Diagram of HVDC System                                                                                     | 2 |

| Figure 4: PSCAD Cable Model between Converters Rated for +/- 500 kV DC 10                                                     | 6 |

| Figure 5: PSCAD Overhead Line Model Rated for +/- 500 kV DC                                                                   | 7 |

| Figure 6: Modular Multilevel Converter Schematic                                                                              | 9 |

| Figure 7: Submodule Operation                                                                                                 | 0 |

| Figure 8: Demonstration of the Controllable Voltage Levels of the Multilevel Converter Based upon a Six Cell System $(n = 6)$ |   |

| Figure 9: Line-To-Neutral AC Voltage Output of MMC Converter                                                                  | 4 |

| Figure 10: Demonstration of Voltage Initialization within the PSCAD Environment (not fina PSCAD model)                        |   |

| Figure 11: Reference and Carrier Waveforms for Switching Algorithm                                                            | 8 |

| Figure 12: Calculation of the Number of ON Cells in the Upper and Lower Arms of Phase A 29                                    | 9 |

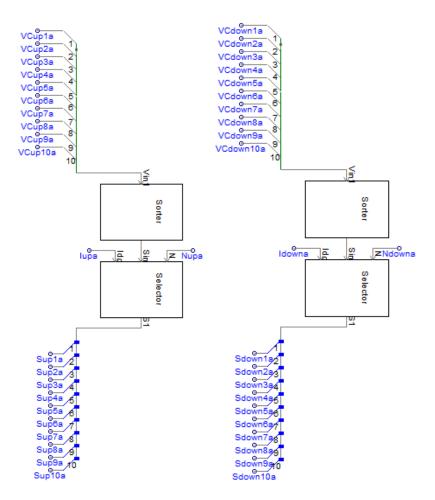

| Figure 13: Sorting and Selection Modules for the Upper and Lower Arms of Phase A 30                                           | 0 |

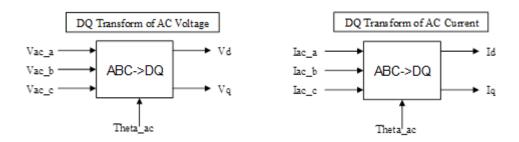

| Figure 14: Generic Park Transformation Blocks for Voltage and Current                                                         | 2 |

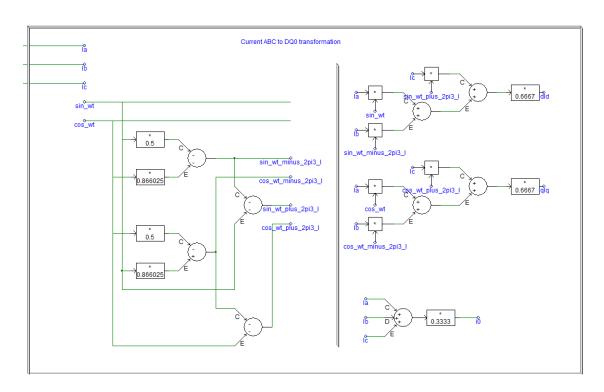

| Figure 15: Current ABC to dq0 Transformation Implementation in PSCAD                                                          | 3 |

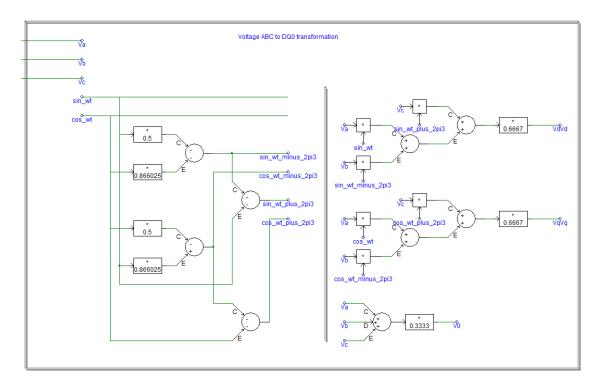

| Figure 16: Voltage ABC to dq0 Transformation Implementation in PSCAD                                                          | 3 |

| Figure 17: AC Current Regulator Block Diagram                                     | 35 |

|-----------------------------------------------------------------------------------|----|

| Figure 18: Illustration of Modulated Case with Third Harmonic Injection [22]      | 36 |

| Figure 19: Current Controller Implementation in PSCAD                             | 36 |

| Figure 20: Third Harmonic Injection and Generated Reference Signals in PSCAD      | 37 |

| Figure 21: Simplified Equivalent Circuit on AC Side                               | 37 |

| Figure 22: AC Voltage Regulator and PSCAD Implementation                          | 39 |

| Figure 23: DC Voltage Regulator Diagram and PSCAD Implementation                  | 40 |

| Figure 24: Real Power Regulator                                                   | 41 |

| Figure 25: Top Level View of PSCAD HVDC System Model                              | 42 |

| Figure 26: Demanded and Actual DC Voltage on MMC A                                | 43 |

| Figure 27: d-Axis Current Controller Response                                     | 44 |

| Figure 28: <i>q</i> -Axis Current Controller Response                             | 45 |

| Figure 29: d and q-Axis Voltages Establishing Reference Voltage for PWM Modulator | 45 |

| Figure 30: Modulation Index                                                       | 46 |

| Figure 31: Third Harmonic Injected AC Control Signal Waveform                     | 47 |

| Figure 32: Capacitor Voltage for Full Duration                                    | 48 |

| Figure 33: Steady State Capacitor Voltage                                         | 48 |

| Figure 34: Line-to-Neutral AC Voltage Created by the Converter                    | 49 |

| Figure 35: Line-to-Line AC Voltage Created by the Converter                       | 50 |

| Figure 36: Grid Side Voltage, Converter Side Voltage, and Reference Waveform      | 51 |

| Figure 37: Grid Side of Transformer Line-to-Neutral AC Voltage                    | 51 |

| Figure 38: DC Power Transfer                                                      | 52 |

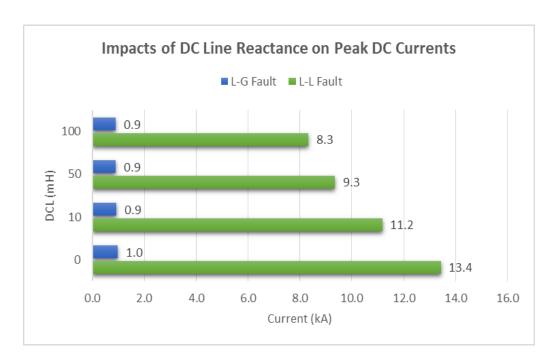

| Figure 39: Impacts of DC Line Reactance on Peak DC Currents                       | 58 |

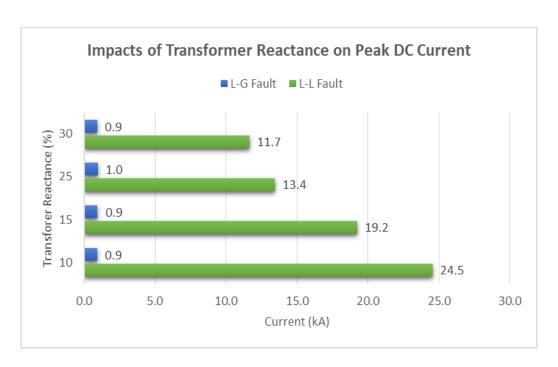

| Figure 40: I | Impacts of Transformer Reactance on Peak DC Currents                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------------------|

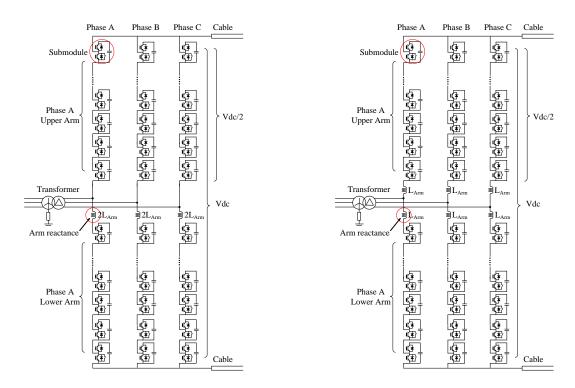

| Figure 41: ( | Comparison of Asymmetric (Left) and Symmetric (Right) Arm Reactance                                                    |

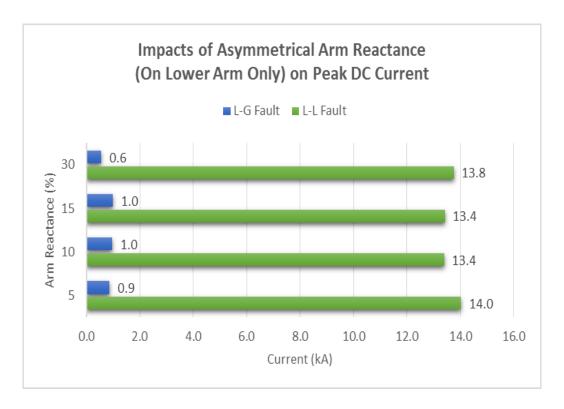

| Figure 42: I | Impacts of Asymmetrical Arm Reactance on Peak DC Current                                                               |

| Figure 43: I | Impacts of Symmetrical Arm Reactance on Peak DC Currents                                                               |

| Figure 44: I | Impacts of Bypass Switch Speed on Peak DC Current                                                                      |

| Figure 45: I | Impacts of Short Circuit Strength on Peak DC Currents                                                                  |

| Figure 46: I | Impacts of DC Line Length on Peak DC Currents                                                                          |

| Figure 47: I | Impacts of HVDC Line Configuration on Peak DC Currents                                                                 |

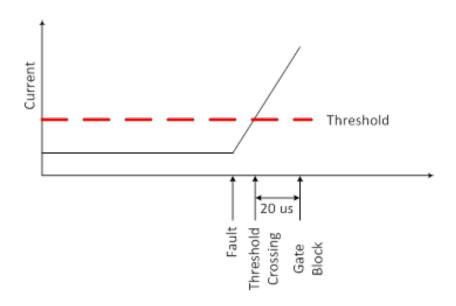

| Figure 48: 0 | Overcurrent Protection as the Initiation of the System Protection Sequence                                             |

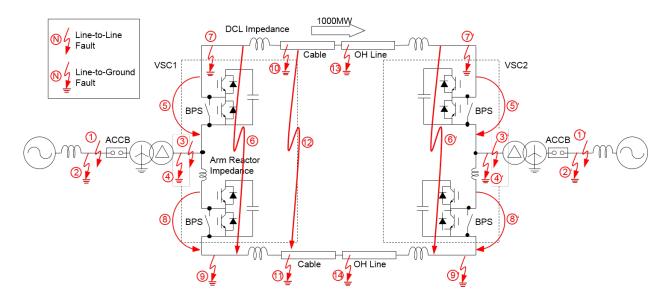

| Figure 49: I | Fault Locations and Types for All Case Scenarios for the Fault Protection Analysis 83                                  |

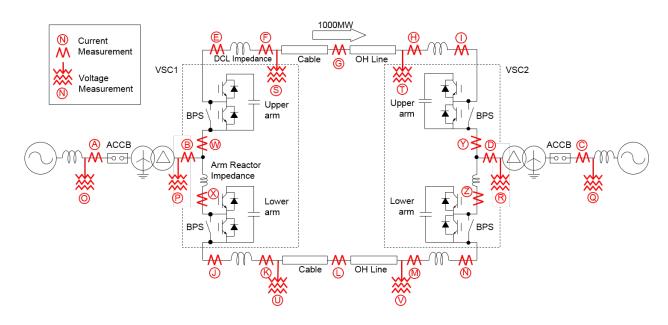

| _            | HVDC System Voltage and Current Measurements Monitored for Fault Protection<br>Analysis                                |

| Figure 51: I | HVDC System Voltage and Current Measurements                                                                           |

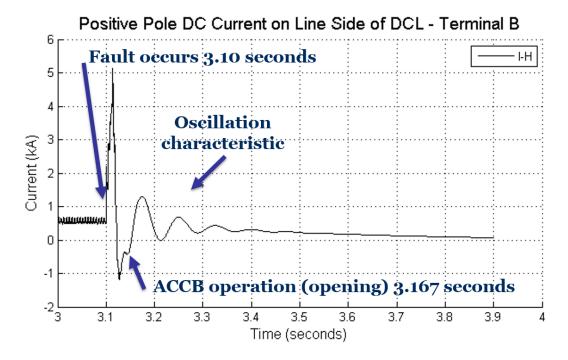

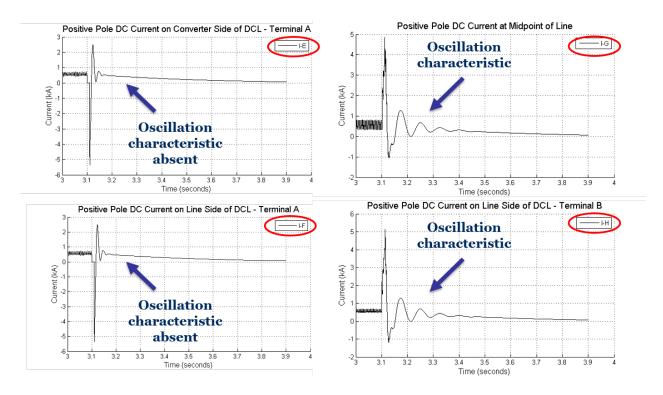

| Figure 52: I | Example of Current Oscillation in Case 3-1-407                                                                         |

| Figure 53: I | Example of Voltage Oscillation in Case 3-1-407                                                                         |

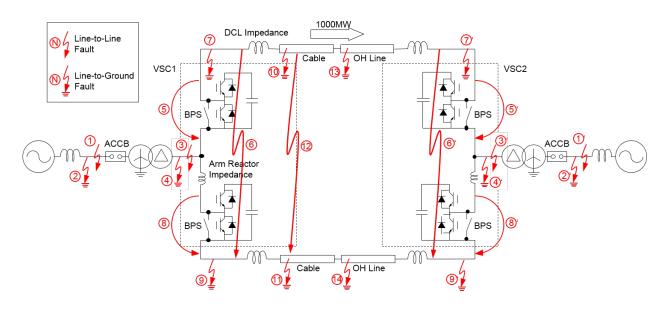

| Figure 54: I | Fault Locations for all Case Scenarios                                                                                 |

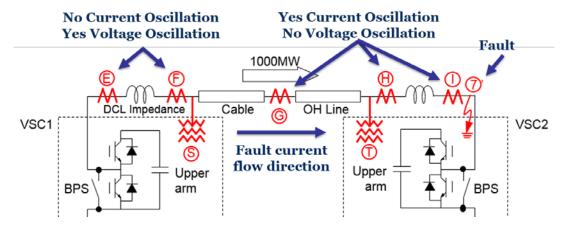

| _            | Positive Terminal of Example Case 3-1-407 showing Signal Oscillation Caused by Capacitive Nature of Cable              |

| _            | Case 3-1-407 Positive Terminal Currents showing that Signal Oscillation Appears in Current after Passing through Cable |

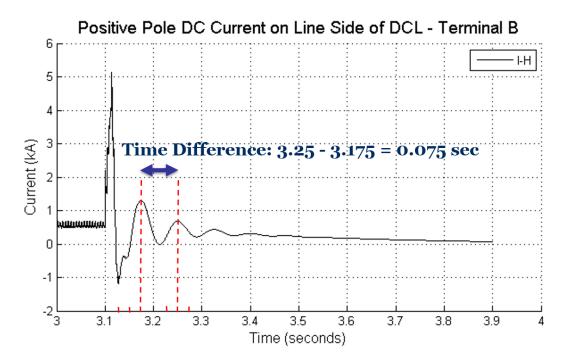

| Figure 57: I | Example of Current Oscillation in Case 3-1-407 with the Period of                                                      |

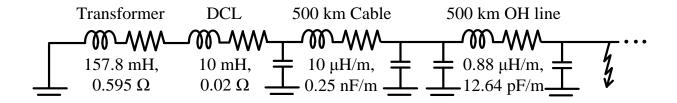

| Figure 58:   | HVDC System Equivalent RLC Circuit for Case 3-1-407 Post ACCB and BPS Operation                                        |

| Figure 59:   | Simplified Equivalent LC Circuit for Case 3-1-407 for Determining Oscillation Frequency                                |

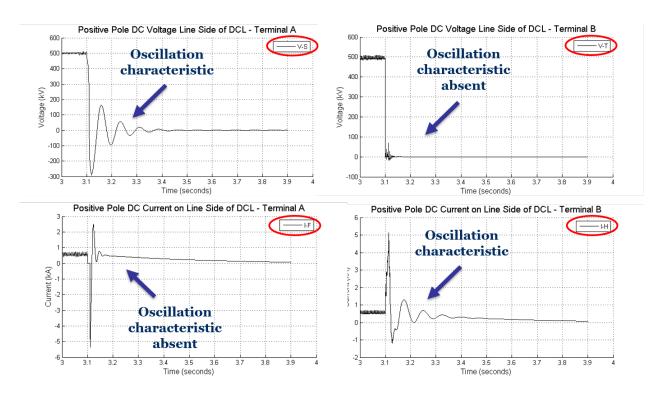

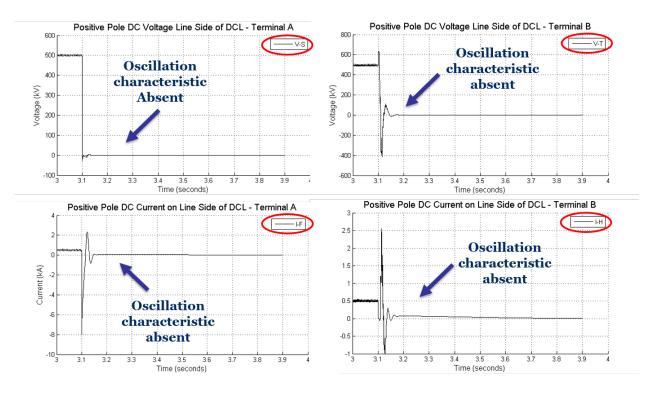

| Figure 60: | Case 3-1-407 Positive Terminal Voltage and Current Measurements are Consistent with Complementary Distinctive                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 61: | Case 3-1-404 Positive Terminal Voltages and Currents for Line-to-Ground Cable Fault with an absence of any Oscillation                        |

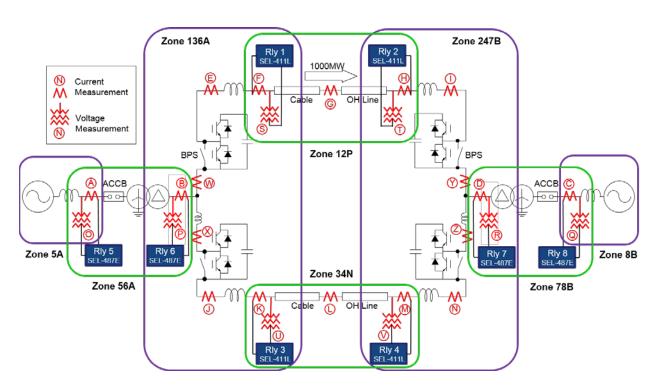

| Figure 62: | Placement of Protective Relays and Zones of Protection                                                                                        |

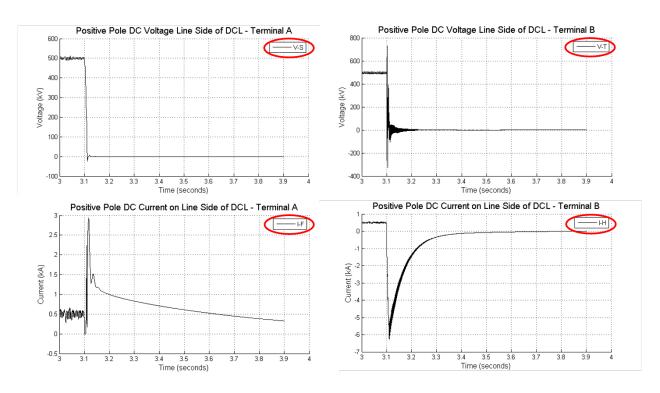

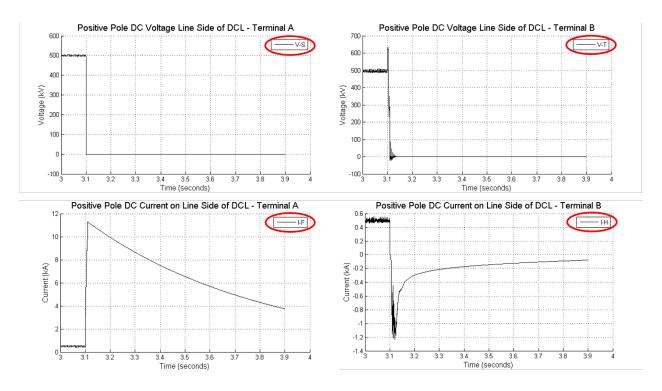

| Figure 63: | L-L DC Fault at the Midpoint of the OH Line – Positive Terminal Voltages and Currents Shown                                                   |

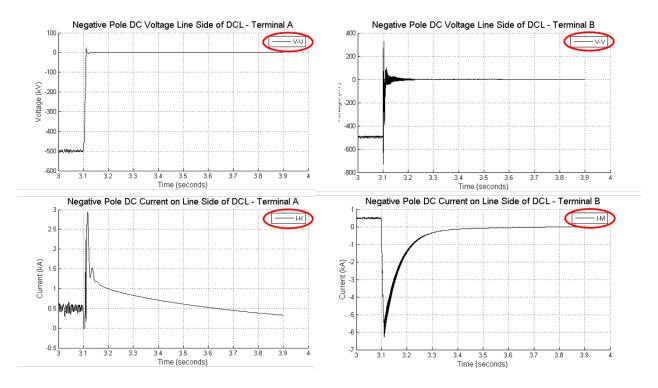

| Figure 64: | L-L DC Fault at the Midpoint of the OH Line – Negative Terminal Voltages and Currents Shown                                                   |

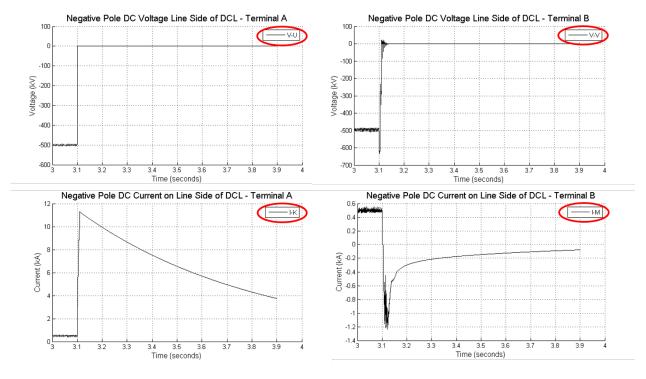

| Figure 65: | Case 3-2-104 L-L DC fault at the Sending End of the Cable – Positive Terminal Voltages and Currents Shown                                     |

| Figure 66: | Case 3-2-104 L-L DC fault at the Sending End of the Cable – Negative Terminal Voltages and Currents Shown                                     |

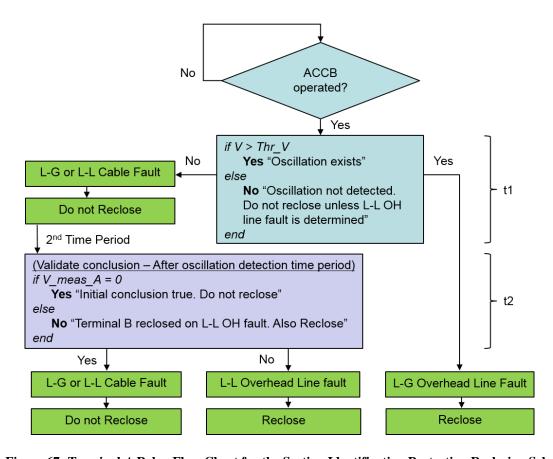

| Figure 67: | Terminal A Relay Flow Chart for the Section Identification Protection Reclosing Scheme                                                        |

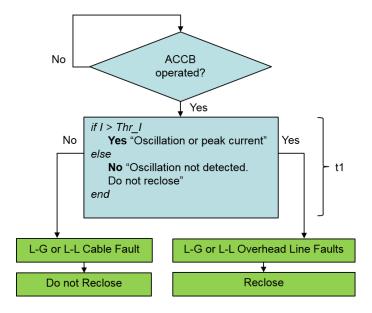

| Figure 68: | Terminal <i>B</i> Relay Flow Chart for the Section Identification Protection Reclosing Scheme                                                 |

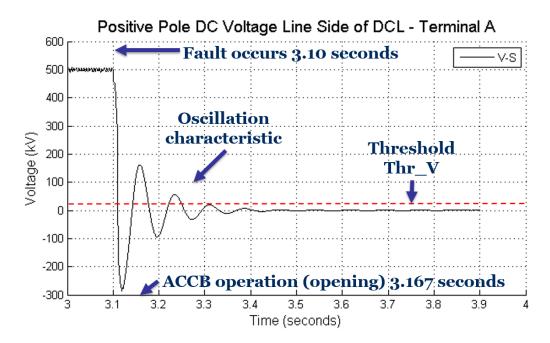

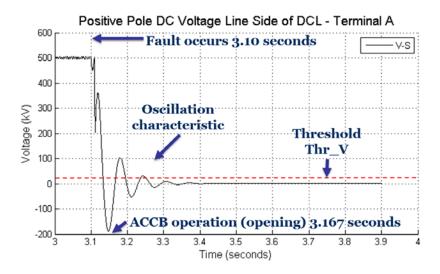

| Figure 69: | Protective Relay Voltage Threshold applied to a Terminal <i>A</i> Relay during a L-G Fault on the Receiving End of the OH Line (Case 3-1-407) |

| Figure 70: | Protective Relay Voltage Threshold applied to a Terminal A Relay during a L-G Fault in the Middle of the OH Line                              |

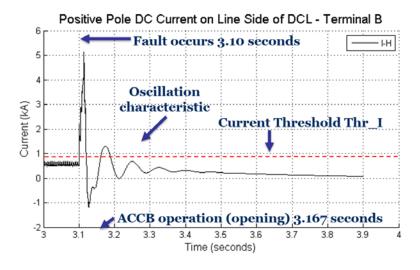

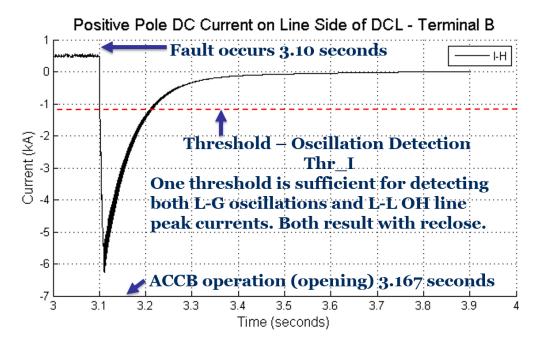

| Figure 71: | Protective Relay Current Threshold applied to a Terminal <i>B</i> Relay during a L-G Fault on the Receiving End of the OH Line (Case 3-1-407) |

| Figure 72: | Protective Relay Current Threshold applied to a Terminal <i>B</i> Relay during a L-L Fault in the Middle of the OH Line                       |

| Figure 73: | Protective Relay (SEL 411L) Advanced Line Differential Protection, Automation, and Control System [31]                                        |

| Figure 74: | Circulating Current Path Depicted in the Modular Multilevel Converter Topology, Caused by the DC Line-to-Line Fault                           |

#### **ACKNOWLEDGMENTS**

First of all, I want to acknowledge and thank my family for their support and love. I especially thank my beautiful wife, Heidi, for taking care of me, being extremely supportive of my educational efforts and for encouraging me to do the very best that I can to the glory of God. I also thank my parents and siblings for being the best family that anyone could ask for. The childhood that I had with you has prepared me in so many ways for where I am today.

I thank my academic advisor, Dr. Greg Reed, who has made this exceptional educational opportunity a reality. I am also greatly appreciative of the guidance of a few other professors at the University of Pittsburgh, namely Dr. Zhi-Hong Mao, Dr. Bill Stanchina, and Dr. Tom McDermott. At this point I take a moment to mention a great big thank you to Brandon Grainger my colleague, now Dr. Brandon Grainger my professor. You have been a mentor, a brother in Christ, and a friend throughout my graduate career. I also acknowledge all of my fellow graduate colleagues that I have had over these past two years and some. I look forward with anticipation to continuing the collaboration and the good times that I have had with you all. I also thank the industry sponsors of this research for their collaborative effort and guidance.

Lastly I acknowledge and thank both my church family and most importantly my heavenly Father. The faith and grace that God has given me has guided me through each step of my life. He has given me the gift of pursuing an education, an opportunity to be a difference maker, and I seek to be a good steward of the life that He gives.

#### 1.0 INTRODUCTION

As an introduction to the thesis work presented, a background of HVDC transmission technology is given. The reason for researching specifically MMC-HVDC is described. Necessary background of protective relay technology is also covered. For clarification the conditions of the desired MMC-HVDC protection design is defined. Additionally the motivation and the contributions of the work are presented. Lastly, the content of each chapter is briefly explained before delving into the body of the thesis.

#### 1.1 BACKGROUND

High Voltage Direct Current (HVDC) is rapidly becoming a predominant choice over high voltage alternating current (HVAC) for many applications of modern transmission projects due to its desirable benefits [1],[2]. HVDC is defined as a DC transmission system incorporating power electronic based controls and other static controllers to enhance system controllability, control power flows, and improve power transfer capability. HVDC transmission is especially desirable for applications that require long distance power delivery due to significantly higher operational efficiency as compared to HVAC. Another application for which it is specifically desirable to utilize HVDC is subsea cable transmission, also for the reason of more efficiently delivering the power. An example of a subsea application is offshore wind generation,

transmitted to shore by subsea cables [2],[3]. Another example of subsea cabling would be transmission of power from one land mass to another with a channel of water between [4]. Future needs of bulk power transmission and subsea cable applications will be met with HVDC technology. With the increased penetration of wind power on the U.S. both offshore and in the Midwest, there will be increased need for subsea cabling and long distance bulk transmission applications. This thesis work supports these applications by analyzing long distance HVDC transmission specifically including two sections to the HVDC line, a cable section (subsea) and overhead (OH) line section (above ground).

HVDC technology is based off of two different converter designs, the line-commutated converter (LCC) and voltage sourced converter (VSC). The classical LCC-based HVDC technology, also known as classic HVDC, is based upon thyristor-based technology. LCC-HVDC is a mature technology with robust reliability, low losses, and a successful history. Advances in semiconductor technology has made VSC-based HVDC possible, utilizing primarily the IGBT (insulated gate bipolar transistor). The IGBT is capable of switching frequencies significantly faster than thyristors. Low switching frequencies is a disadvantage of LCC. VSC is now becoming the choice converter design over LCC in HVDC applications [2]. There are a number of VSC-based converters; the topology of study in this work is the modular multilevel converter (MMC) due to its numerous advantages.

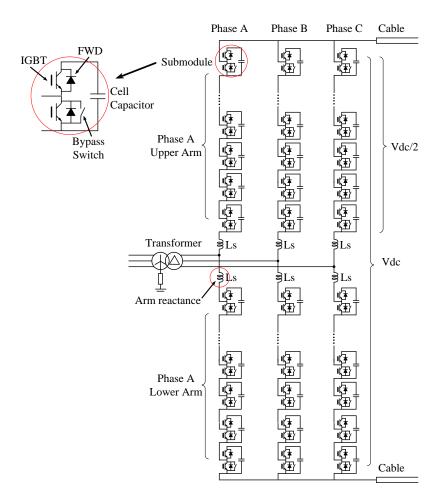

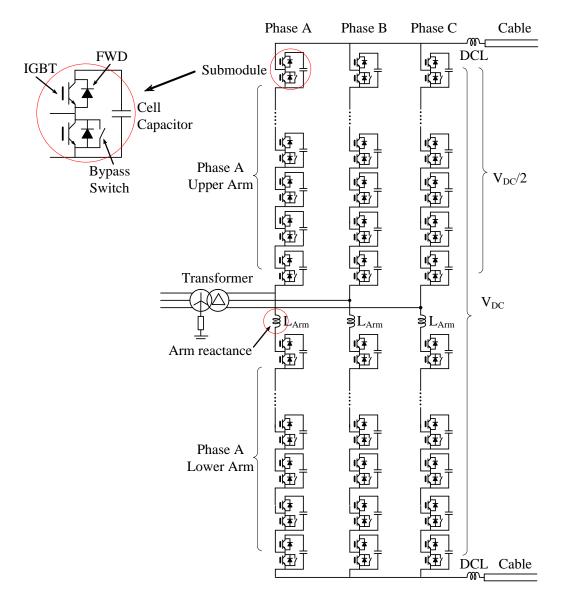

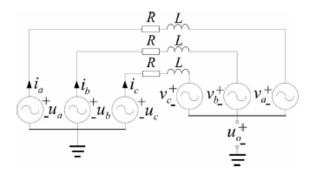

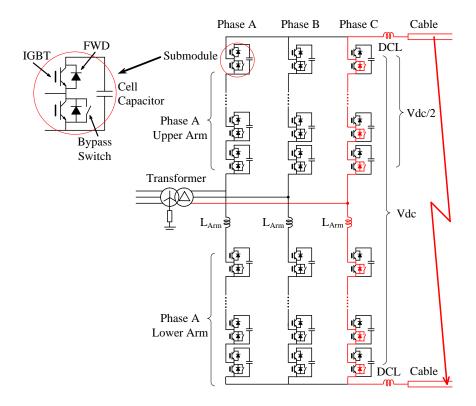

The VSC-based modular multilevel converter (MMC) topology is desirable for HVDC applications due to the number of advantages it can offer in comparison to other topologies [2], [5]. The MMC topology, depicted in Figure 1, boasts a number of advantages over traditional VSC multilevel designs including its high modularity in hardware and software, low generation

of harmonics, lower switching frequency of semiconductor devices, easily scalable, and, most importantly, a stronger approximation of a sinusoidal output with increasing submodules [5], [6].

Figure 1: Schematic of the Modular Multilevel Converter Topology

Due to HVDC being choice for future bulk transmission and subsea installations, combined with the advantages of MMC-HVDC in particular, it is desired to minimize or eliminate entirely any hindrances or weaknesses of the technology. There is need of minimizing the weaknesses of MMC-HVDC so that the numerous benefits can be utilized, so that MMC-HVDC can become a viable competitor with the mature technologies.

Extensive literature reviews are provided for the MMC topology, modulation, and control in [1] and [5], controller design in [1] and [7], and protection needs in [6] and [8]. In a HVDC transmission system there is a need to address the protection needs of the MMC-HVDC technology design. Protection for AC systems is a mature technology, but on the other hand DC systems have many opportunities to investigate protection needs. There is a need to research DC side fault scenario events and to propose how to handle these events in terms of protection [8]. Especially with the introduction of VSC-HVDC and an increase of VSC systems being installed, the protection of these systems needs to be spoken to.

In protecting MMC-HVDC from DC side faults, there are two exclusive options of a device to implement: 1) DC circuit breaker technology [9], [10], or 2) traditional AC circuit breaker technology combined with custom relay protection coordination on the DC side [8],[11]. The first method has drawbacks. Primarily, DC circuit breaker technology on a high voltage scale is immature and expensive at the present time [1]. Therefore the second method will be investigated. The MMC-HVDC system analyzed in this work will include AC circuit breaker technology.

There are two primary protection challenges facing the MMC-HVDC system design: 1) fault current must be extinguished quickly so that the converter fault withstand rating is not surpassed as well as so that a system restart sequence can commence as soon as possible, and 2) the fault location must be quickly identified so that the system can restart to normal operation as soon as possible maintaining power transmission. The first challenge is a future work item, outside the scope of this thesis work. The second challenge is the primary problem addressed in this work, and a solution to this problem is proposed in chapters 4 and 5.

To expound upon the second challenge, the need is to attempt reclosing the circuit breakers upon non-permanent faults scenarios on the HVDC line and to not reclose the circuit breakers upon permanent fault scenarios. The HVDC line for the design in this work is made up of two sections, a cable and an OH line section. Fault scenarios that occur in the OH line section are potentially non-permanent faults. AC circuit breaker attempt of reclose is then desired. Fault scenarios that occur in the cable section can be assumed to be permanent. AC circuit breaker reclose is not desired. It is therefore desired to identify the fault section in order to know whether or not to attempt ACCB reclose. In order to maintain transmission operation as often as possible, it is crucial for an HVDC system to feature a system restart sequence that restarts the system as quickly as possible post a fault case scenario. This work will propose a system restart sequence that will incorporate protective relay coordination with ACCBs to implement a fault section identification protection method.

When considering protective relay technology there are a few items to describe before continuing further. Fault section identification has been attempted in multiple ways on various types of systems by use of the following methods: wavelet transform, Kalman filtering, neural network, and vector support machine [12], [13], [14]. These solutions can be marginally effective in achieving section identification, but they are calculation heavy, consuming precious time, in determining the section. Fault location identification, identifying the exact location along the transmission distance, could be applied for the purpose of section identification by use of distance (or impedance) protective relaying or traveling-wave based protective relaying, but again these methods are time consuming even if they are marginally effective. Additionally, location identification performs more work than necessary when simply section identification is desired. The exact location of the fault in terms of distance from a converter station is

unnecessary when the desired information is to know whether the fault is located in the cable or OH line region of the HVDC line. All that is necessary to resolve the specific section identification challenge is to identify which section the fault is located in, the cable or OH line section. This work proposes a solution, novel to the HVDC design specified, that identifies the section without performing time consuming location identification.

Protective relay coordination for transmission systems most often requires a communications channel between the converter stations [15]. This is primarily due to the fact that most transmission relay protection is in the form of line current differential protection which requires a communications channel inherent to the relay function [15]. Communications in protection inherently slows down the process of restarting the transmission system after a fault event. Communications are also expensive especially for transmission and can often be unreliable [16]. For the purpose of faster fault isolation and faster system restart, it is desired to design a protection coordination scheme that does not utilize a communications channel. Examples of noncommunication relay coordination protection design are found in [16]–[19]. These examples all fall into the category of relay protection where detection of local circuit breaker operation is depended upon by the relay protection operations. This desire for noncommunication relay coordination protection is set as one of the conditions on the MMC-HVDC protection design proposed through this thesis work.

More protective relay functionality will be presented in chapter 5, but there is one more detail to be considered in defining the conditions set on the MMC-HVDC protection design, the number of signal samples stored in relay memory. A relay stores a certain number of samples of the fault current or voltage signals at a specific sampling frequency. For example, the relay protection in [14] samples at 1kHz and keeps 10 samples in memory. These specifications

change depending upon the relay being used. For the sake of protection method speed, it is desirable for a relay to make a protective action decision in as few memory samples as needed. Speed is everything when protecting against faults. This condition of minimum relay memory samples is set upon the proposed protective solution applied to the MMC-HVDC design.

The protection needs for an MMC-HVDC system is the premise of this thesis. The specific protection need addressed in this work is fault section identification in order to enable fast protection coordination during system restart. Included as future work, is the quick suppression of MMC circulating fault current, expounded upon in the conclusion of this work. The end result of this thesis is the proposal of a fault section identification protection method.

#### 1.2 MMC-HVDC PROTECTION DESIGN CONDITIONS

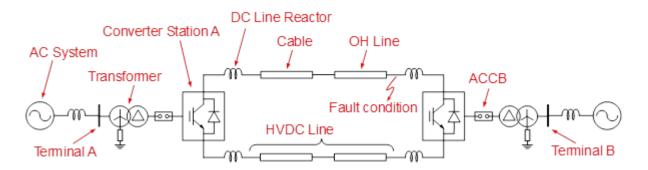

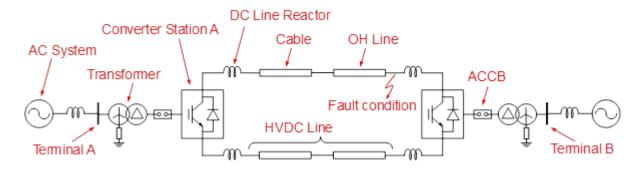

Throughout the discussed background, certain conditions were set on the HVDC design being considered. In summary of these conditions, the desired HVDC transmission design includes the MMC topology, a two section transmission line, and AC protection devices (ACCBs) in protecting against DC side fault scenarios. Two desired conditions are to implement the proposed fault section identification protection method without the use of a communications channel and to minimize the number of stored fault signal samples upon which the relay protection coordination design depends. Remember, the motivation is to restart power transmission as quickly as possible for the reliability of power delivery. The full list of the desired MMC-HVDC design conditions to be met are listed here:

- Both cable and overhead line sections making up the HVDC line

- HVDC technology implementing the MMC topology

- Only AC protection devices utilized in protecting against DC side fault scenarios

- Communication-less protection coordination between converter stations for faster fault isolation and system restart

- Minimize required fault signal memory samples upon which the protection coordination design depends

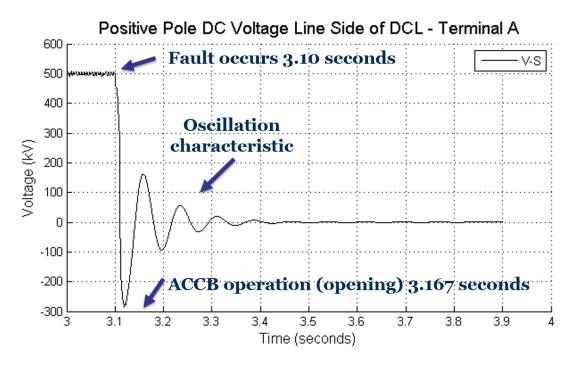

Figure 2 is a diagram of this HVDC system design. Terminal *A* and terminal *B* are depicted in this figure, essentially giving terminology to the AC grid connections located on the left and right of the DC system. Terminal *A* is also termed as the sending end of the system while terminal *B* as the receiving end, since power flow as a reference is defined from terminal *A* to terminal *B*. The various other system components are also labeled in this figure.

Figure 2: HVDC System Design with Cable and Overhead Line Sections Making up the HVDC Line

#### 1.3 MOTIVATION AND CONTRIBUTIONS

This work is the development of a protection scheme to account for all faults on the DC side of an MMC-HVDC system specifically for a design including both overhead (OH) line and cable sections making up the overall HVDC line. The overall motivation of this work is to equip MMC-HVDC technology to overcome its draw backs and implementation challenges so that its

benefits might be utilized. The primary problem tackled in this work is the challenge of fault section identification in attempt of system restart. The motivation specifically for a fault section identification method is reliability of power delivery. As an end result, a reclose will be attempted for any DC side fault that is potentially non-permanent, and consequently a restart to normal operation is achieved as frequently as possible and as quickly as possible.

Ultimately the contribution of this work is to equip future installations and product lines of MMC-HVDC technology. This work is one more step in supporting the implementation of the beneficial technology. Specific contributions from this work include the trends of MMC-HVDC component sensitivity analysis, awareness of how an MMC-HVDC system responds to a comprehensive list of faults, and a protection coordination scheme uniquely applicable to this promising HVDC system design. There is also considerable significance in the contribution of a fault section identification method incorporated into relay coordination without using a communication channel and without the use of DC circuit breakers. This contribution is ultimately the speed in which the system is restarted after a fault scenario.

#### 1.4 CONTENT ROAD MAP

Now that an MMC-HVDC background has been portrayed along with the protection problem that motivates this work, the process in achieving a solution can be presented. This process is simply organized by chapter. The second chapter describes the detailed modeling of the MMC-HVDC system in the PSCAD environment. Both MMC circuit theory implementation and validation of the model are presented. This is the foundation of the entire work. Validation of the MMC-HVDC model shows that the fault protection analysis will result with expected fault

response dynamics. The third chapter presents a trends analysis of the various system elements and components. A sensitivity analysis is performed upon each primary system parameter to determine its impact on DC fault current. This parametric trends analysis is constructive for fine tuning the selection of system parameters for a fault protection analysis. This analysis is also useful for observing which parameters are critical in the design of MMC and of HVDC systems. The fourth chapter presents the fault protection analysis performed and presents the primary results that were found to be useful in support of the protection method design to be achieved. A signal, characteristic to the HVDC design, was identified through analysis of the results and proved useful for the implementation of a fault section identification protection method. This signal is proven to be an expected system dynamic through circuit analysis. The fifth chapter presents the proposal of the fault section identification method. This chapter presents the overall protection coordination design to be applied to the desired HVDC design with all design conditions met. A summary of conclusions are then given along with a description of future work to be performed.

#### 2.0 MMC-HVDC SYSTEM MODELING

Through this second chapter, the theory and modeling of the monopolar HVDC system within the PSCAD/EMTDC simulation environment is presented and validated. The converter station topology is based upon the Modular Multilevel Converter (MMC) arrangement. All system parameters utilized within this chapter's validation model are provided. Various details of the modeling are documented in this section including a circuit synthesis of the MMC converter, MMC capacitor initialization and balancing procedures, controller implementation (DC and AC voltage, current, and power regulators). The method for tuning the controllers, as well as all references used to aid in the model development are presented. With the theoretical platform established, PSCAD simulation results are provided showing model behavior. Graphical results include a validation of the capacitor balancing algorithm, controller dynamic behavior, and standard system checks that illustrate that the model is performing as expected.

In this work, there are 60 submodules modeled per converter station (10 cells per arm) resulting in 120 total including both converters. This number of cells (submodules) was selected according to modeling experience acquired in the modeling process. The selection was based upon adequately capturing fault current magnitudes and maintaining an IEEE 519 specified level of total harmonic distortion (THD). Various numbers of cells were simulated and 10 cells were chosen in conclusion. The challenge of

For clarity Figure 2 provides a diagram of the HVDC system in its entirety, labeling the portions of the model in order to lay a foundation of understanding of the system model from a high-level view.

Figure 3: One-Line Diagram of HVDC System

#### 2.1 MODULAR MULTILEVEL CONVERTER MODELING

A detailed model of the MMC-HVDC system was created in the PSCAD/EMTDC simulation environment tool. A detailed model was created, as opposed to the option of an approximate or average model, for the purpose of observing the dynamics generated by the switching states of the submodules inherent to the modular multilevel converter design. When faults occur on an MMC-HVDC system, the energy dissipation from the submodule capacitors needs to be modeled as closely as possible. It is desired to observe the circulating currents typical for an MMC topology upon a fault scenario. This requires that we model the converter in detail including an algorithm for capacitor energy balancing to replicate an actual system as close as possible. With these items being necessary for the accurate simulation of faults on the HVDC system, a detailed

model was created. The level of detail was limited by the fact that device physics were not modeled. This was deemed unnecessary for the purposes of this work. In the end, the peak fault current magnitudes observed on the system are a primary concern to be modeled accurately. Energy dissipation of the submodule capacitance is modeled as closely as possible to measure peak current magnitudes accurately, but device physics does not significantly weigh into these measurements.

#### 2.1.1 System Parameters

It is important to begin by defining the parameters that were used in the model and describing the reasoning behind these parameters. The parameters defined for this initial test system were gathered by a combination of student research and discussions with industry contacts. With all sources considered Table 1 lists the parameters decided upon for the initial validation model. Note that this parameter list is preliminary. Further analysis documented in the next chapter aids the exact selection of each parameter value based upon a trends analysis.

**Table 1: HVDC System Parameters for Validation Model Development**

Rated AC RMS Voltage 500 kV Rated DC Voltage  $\pm 500 \text{ kV}$ Short Circuit Capacity 25000 MVA Rated Power of Converter 1000 MW Nominal Frequency 60 Hz Submodule Capacitance 300 uF (10 cell/arm system) Transformer Reactance 0.25 p.u. 0.0 HDC Line Transformer MVA Rating 1050 MVA Transformer Turns Ratio 1:1 Arm Reactance 10% at bottom of lower arms Line Length 1000 km

These system parameters have had a history of revisions. Only the final set of validation model parameters are provided here. Calculations, values and explanations are provided here for the model development parameters.

#### AC System

The rated 500 kV voltage was selected due to typical high voltage transmission rating in the U.S. market. The frequency of 60 Hz is selected also because it is standard for a U.S. market. A short circuit current range was selected according to typical U.S. market ratings based off of discussions with industry personnel.

$$I_{SC} = 11kA - 63kA$$

The short circuit capacity of the system was calculated with the following calculations. Observe and note that the short circuit current of 63 kA dictates the worst case scenario corresponding to a short circuit capacity of 55,000 MVA.

$$S_{SC} = I_{SC}V_{rated}^{new} \sqrt{3} = (11kA)(500kV)\sqrt{3} = 9,500MVA$$

$$S_{SC} = I_{SC}V_{rated}^{new}\sqrt{3} = (63kA)(500kV)\sqrt{3} = 55,000MVA$$

#### Transformer

The transformer connection type  $(Y-\Delta)$  was selected based off of typical transmission line installations. The rated capacity (1050 MVA) was selected based off of a typical 500 kV transformer. The reactance value for the transformer was selected based off of a typical 500 kV transformer installation.

Advised from industry contacts, an X/R ratio of 100 was applied to the transformer impedance and resistance. While holding to an X/R ratio of 100 and keeping the transformer reactance selected, we obtain a corresponding transformer resistance value. This resistance value is calculated as shown here.

$$\frac{X_{p.u.}}{R_{p.u.}} = 100$$

$$R_{p.u.}^{new*} = \frac{0.25 \, p.u.}{100} = 0.0025 \, p.u.$$

This per unit transformer resistance was inserted into our model.

#### Converter

The rated AC voltage is 500 kV according to the system rating selected. The rated DC voltage is  $\pm 500 \text{ kV}$ , equivalent to 1000 kV. The measured voltage difference from the positive to the negative terminals on the DC side of the converter is 1000 kV.

$$V_{DC} = 500kV - (-500kV) = 1000kV$$

The power rating of 1000 MW was selected, and the rated converter current was calculated accordingly.

$$I_{converter}^{new} = \frac{P}{V} = \frac{1000MW}{500kV} = 1000A$$

#### DC Line Reactor

There is a potential need for a DC line reactance in the system, but for the purpose of the initial validation model no DC line reactance was used. The DC line reactor is not implemented in the initial model being described in this chapter. This parameter was being neglected until the model functioned appropriately. DC line reactance and resistance was applied for the various fault analysis cases presented in the next chapters of this work.

#### DC Line

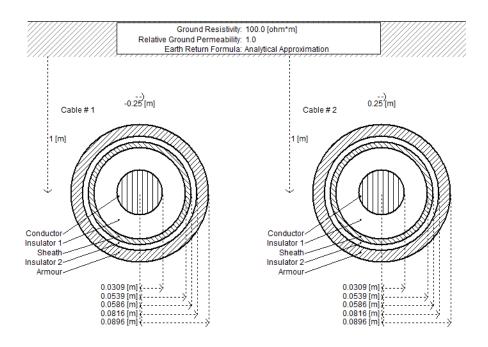

In the end there is need for both a cable and an overhead (OH) line model to simulate the multi-section DC line totaling at a 1000 km line. A 1000 km DC cable was employed for initial testing of the model. This cable implementation was based on the availability of reliable

references for DC cables. With industry advisement, a  $\pm$  320 kV rated cable model (electrogeometric model) was imported into PSCAD for the purposes of validating the simulation model. Because the desired design is rated for  $\pm$  500 kV, another electro-geometric based cable model that meets that specification was found, based on [20]. A PSCAD graphic of the cable model with material radii is provided in Figure 4 based off of this reference.

Figure 4: PSCAD Cable Model between Converters Rated for +/- 500 kV DC

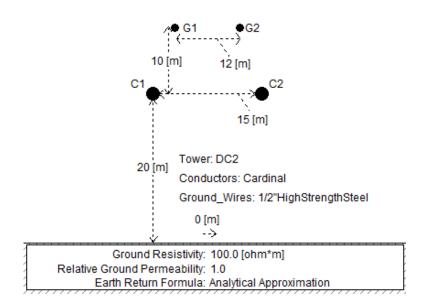

The overhead line PSCAD model was based off of data gathered from literature as well as textbook references [20], [21]. The OH line model is based off of an actual ± 500 kV DC OH line located in Gochang County in South Korea [20]. Conductor data was collected from the second edition of Power System Analysis and Design by Glover and Sarma [21]. Cardinal conductor data was implemented. The details GMR (geometric-mean radius) of 0.0122834 meters and the DC resistance of 0.06083 ohms/mi at 25 degrees Celsius were selected according

to these sources. A PSCAD graphic of this OH line model with specific structure dimensions and associated details displayed [20] is provided in Figure 5.

Figure 5: PSCAD Overhead Line Model Rated for +/- 500 kV DC

The end result of the model incorporates 500 km of this OH line model and 500 km of the cable model described. This combination of models was ultimately used in any PSCAD simulation associated with the proposal of the section identification method or with the parametric trends analysis. But for the initial validation model presented in this chapter, 1000 km of the cable model is implemented.

#### MMC Configuration

The IGBT and diode drop voltages are not applicable for system validation purposes or for the purposes of this work. These intrinsic details do not need to be captured in a "system" model of the converter stations. For an actual system, hundreds of submodules would exist and consequently the cell capacitance would be quite small. However, rather than modelling

hundreds of cells per arm as would be fitting for a 500 kV, 1000 MW system, only ten were used for modeling purposes. To properly scale the capacitance to the system, the value from the 6 cell model presented in [7] was chosen as a starting point. From here a conversion was employed to properly size the capacitors for this model.

$$C_{ref} = 2500 \mu F$$

$$C_{new} = C_{ref} \cdot \frac{N_{new}}{N_{ref}} \cdot \frac{S_{new}}{S_{ref}} \cdot \left(\frac{V_{DCref}}{V_{DCnew}}\right)^{2} = 2500 \mu F \cdot \frac{10}{6} \cdot \frac{1000 MVA}{50 MVA} \cdot \left(\frac{60 kV}{1000 kV}\right)^{2} = 300 \mu F$$

Thus a capacitance value of 300µF is used for each submodule capacitance in the model.

#### 2.1.2 MMC Circuit Synthesis and Capacitor Initialization

The modular multilevel converter (MMC) topology design for the HVDC converter station is shown in Figure 6. The topology boasts a number of advantages over traditional multilevel designs including its high modularity in hardware and software, low generation of harmonics, lower switching frequency of semiconductor devices, easily scalable, and, most importantly, a stronger approximation of a sinusoidal output with increasing submodules [3].

Figure 6: Modular Multilevel Converter Schematic

The MMC in Figure 6 can consist of n series-connected half-bridge submodules on each of the six arms, two arms per phase. Figure 6 shows an example with n series-connected submodules. For the validated model presented in this report, the number of submodules, or n, is 10. For the entire two converter configuration, there are 120 submodules, 60 submodules per converter. On each phase arm, inductances,  $L_{Arm}$ , are placed to provide current control and limit fault currents [7]. The bypass switch in parallel with each submodule is typically a press-pack

thyristor used to protect the endangered freewheeling diodes in the case of a fault. A single thyristor is usually enough if the aim is to protect the diode from overcurrent. Recently, research teams have proposed a double thyristor switch to allow the MMC to more quickly clear the fault current and restart power transmission after nonpermanent faults on overhead lines [6]. These discussions will be continued in following sections of this work.

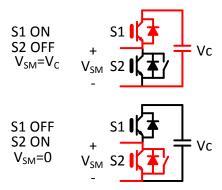

Each MMC submodule consists of a half bridge cell where its output voltage is either equal to its capacitor voltage or zero depending on the switching states (two states). The two switches per submodule are complimentary in nature. The submodule voltage  $V_{sm}$  takes on the value of 0 volts or the voltage on the capacitor depending upon which switch is ON and which is OFF. Figure 7 demonstrates this submodule operation. The operation directly depends upon the binary input to the IGBT switches (S1 and S2) specific to each submodule. When  $V_{sm} = V_C$  the submodule as a whole is considered ON. When  $V_{sm} = 0$  the submodule is considered OFF.

**Figure 7: Submodule Operation**

From the perspective provided by Figure 6 and Figure 7, equation (1) can be easily determined based on Kirchoff's voltage law for each phase, j. Note that for equation (1), S takes on the value of 0 or 1 depending on the switching state of S1 in the submodule. A subscript of

"upper" or "lower" signifies submodule position in the arm, above or below the AC midpoint of the converter. Located adjacent to this midpoint, variable  $L_S$  is the inductance of the arm reactor, [7]. This inductance  $L_S$  is clearly marked in Figure 6 on each of the six converter arms.

$$V_{dc} = V_{upper,j} + V_{lower,j}$$

$$= \sum_{i=1}^{6} \left( S_{upper,i} V_{capacitor,i} \right) + \sum_{i=1}^{6} \left( S_{lower,i} V_{capacitor,i} \right) + L_{s} \left( \frac{d}{dt} i_{upper} + \frac{d}{dt} i_{lower} \right)$$

(1)

The number of levels in the AC output of the converter is a function of the number of modules in series per arm. The modulation strategy utilized for our study to synthesize an eleven-level (n+1) waveform at the ac-side of the converter is a standard phase disposition sinusoidal pulse width modulation technique (PD-PWM). To extend the linear operating range of the PWM strategy and increase the fundamental component of the AC-side line voltage of the MMC, third harmonic injection principles are utilized, [22]. Third harmonic injection is further discussed within the control section of this chapter.

In general for one converter station designed with the MMC topology, there are a total of 2n capacitors per phase in the upper and lower arms. At any instant, only n capacitors can be turned ON in the circuit. Mathematically in terms of switching functions, equation (2) must always hold true for each phase, j.

$$\sum_{i=1}^{n} S_{upper,i} + S_{lower,i} = n \tag{2}$$

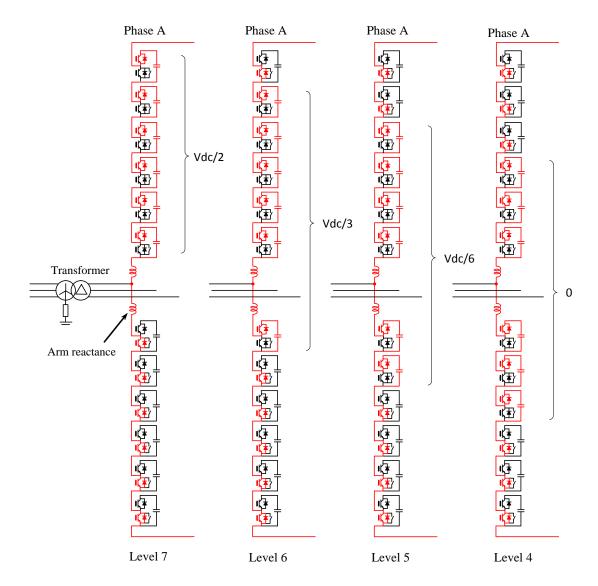

Understanding this constraint offers the opportunity to illustratively describe how the output voltage waveform is built using eleven (n+1) levels with Figure 9. Notice that this constraint is ultimately what makes it possible to convert from AC to DC. While the output AC voltage changes by levels of submodule capacitance voltage to create a sinusoidal output at the

AC terminal, the DC terminal maintains a constant voltage because of the fact that only n submodules are ON at any given instant. This concept is clearly visualized with Figure 8 (based upon a 6 submodule system [n = 6] for a theoretical example).

When considering a theoretical example system with 6 submodules (n = 6), the system is considered a 7 voltage level system (n + 1). To achieve Level 7 all upper switches of one arm must be turned ON ( $V_{sm} = V_C$ ) while all lower switches of the same arm must be turned OFF ( $V_{sm} = 0$ ). To achieve Level 6, the first 5 upper switches closest to the arm reactor must be turned ON and one lower switch closest to the arm reactor must be turned ON with all other switches OFF. Figure 8 provides a visual aid of these voltage level changes on the Phase A branch of the MMC. This pattern continues until the approximate sinusoidal waveform is established based upon 7 levels. Further detail of the switch synthesis can be found in [7].

Figure 8: Demonstration of the Controllable Voltage Levels of the Multilevel Converter Based upon a Six Cell System (n = 6)

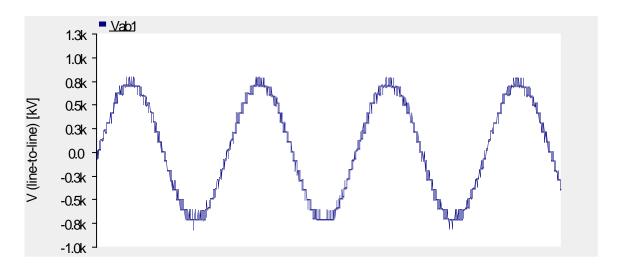

This approximate sinusoidal waveform based upon 7 levels is the AC line-to-neutral voltage. The line-to-neutral voltage specifically defines the multilevel converter capability (n + 1 levels). With 7 submodules per arm, the converter presented in this example from Figure 8 is a 7 level converters because n is equal to six. With 10 submodules per arm, the converters presented in this validation model are 11 level converters. While the line-to-neutral voltage is

defined by having n + 1 levels, the AC line-to-line voltage waveform is defined by having 2n - 1 levels. Thus for the modeled system with 10 cells:

$$n + 1 = 10 + 1 = 11$$

levels

$$2n-1=2(10)-1=19$$

levels

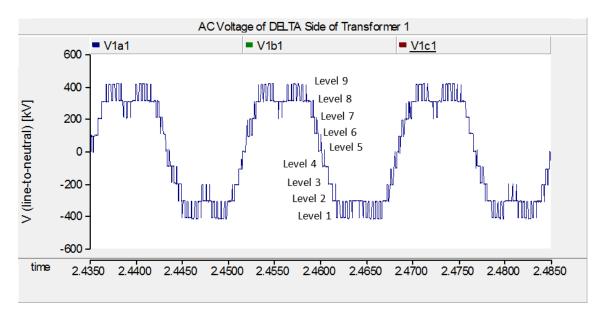

Figure 9 shows the MMC line-to-neutral AC voltage output from the PSCAD model. The line-to-neutral voltage has 9 voltage levels when we would obtain 11 according to our equations above. These 9 voltage levels are as expected though because we have lost the highest and lowest levels (as indicated in Figure 9 where levels 1 and 11 are nonexistent in the plot) corresponding to an m (modulation index) being equivalent to approximately 0.83 at the time. With an m of 1.0, all 11 voltage levels would be seen. Model validation is further developed in Section 3.

Figure 9: Line-To-Neutral AC Voltage Output of MMC Converter

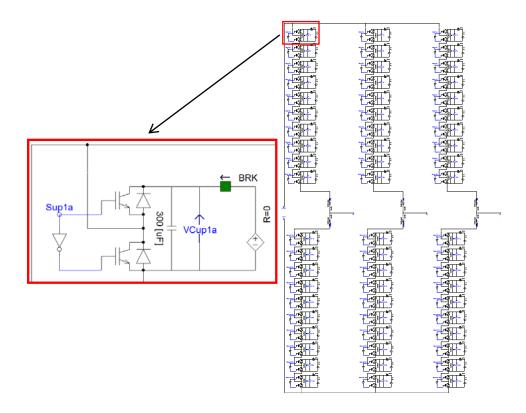

While modeling the described system, a challenge arose due to initialization of the model in the PSCAD environment. Starting from zero voltage on the system, where all cell capacitors started from an uncharged state, the system model could not establish expected steady-state behavior. The model was incapable of charging up the voltage from a cold start. Therefore a modeling strategy was needed to initialize a specified voltage on all cell capacitors. The strategy implemented was to start the system with DC sources inserted in parallel to each submodule capacitor charging the capacitor until each capacitor was charged to a specified voltage.

Figure 10 shows a PSCAD view of the entire MMC converter, as well as a close up of one submodule to provide a visual of the switched in parallel DC source per submodule. These DC sources are initially included in the circuit and disconnected by switching logic at 0.10 seconds, a time at which all submodule capacitors are ensured to be fully charged to the specified voltage.

Upon a complete charge of all capacitors, the DC sources would be switched out of the circuit then allowing the appropriately charged capacitors to take over the system operation in a stable voltage state. Without this capacitor charging initialization strategy the system was not capable of starting in a stable enough state to operate correctly. Once this initialization strategy was implemented, the process of accurately modeling the system could proceed.

Figure 10: Demonstration of Voltage Initialization within the PSCAD Environment (not final PSCAD model)

The specified initializing voltage chosen for this model validation was 100 kV per submodule capacitor. At steady-state, each submodule capacitor will be charged to 100 kV in order that 10 capacitor voltages add up in series to a total voltage of 1000 kV at all times. Remember that n capacitors out of 2n capacitors per phase will at all times be turned ON. These n capacitor voltages (n=10 for this model validation) add up to the necessary 1000 kV.

$$V_{C,ref} = \frac{V_{DC}}{N_{Cells}} = \frac{1000kV}{10} = 100kV$$

Validation of the PSCAD HVDC system model is provided at the end of this chapter. Voltage initialization and voltage control illustrations will be provided with corresponding PSCAD diagrams. It will be displayed that each submodule capacitance is charged to 100 kV by

the parallel DC sources, and then at 0.1 seconds the system will begin switching normally with DC sources switched out.

## 2.1.3 Capacitor Balancing Algorithm

A problem that arises if left unaddressed is a voltage imbalance between the various capacitors in a given arm. This is due to the different rates at which the capacitors are switched, resulting in more charge being stored in the capacitors that are switched the least frequently. To remedy this problem an algorithm was implemented based on that demonstrated in [7], which relies on selection of cells based on capacitor voltage and the direction of current flow. The capacitor balancing algorithm can be separated into three distinct steps: determination of the number of conducting cell capacitors per arm, sorting of cells based on capacitor voltage, and selection of the conducting cells based on current direction. These steps are described here:

- 1. Calculate the number of ON cells in upper and lower arms based on the value of the voltage reference compared to ten carriers.

- 2. Sort the cells in each arm based on ascending voltage magnitudes.

- 3. If the current in an arm is positive, select ON cells based on ascending capacitor voltage. If the current in an arm is negative, select ON cells based on descending capacitor voltage.

In a given phase of the converter, there must be exactly ten cell capacitors conducting at any given moment in time. As discussed previously, this can be represented by the following equation (3).

$$\sum_{i=1}^{n} S_{upper,i} + S_{lower,i} = 10 = n$$

(3)

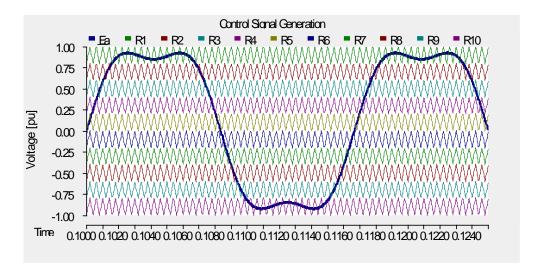

In order to determine the total number of upper and lower cells that must be on, a comparative algorithm was used. This algorithm compared a third harmonic injected sinusoidal waveform to a series of ten triangular carrier waveforms which evenly divided the magnitude of the reference.

Figure 11: Reference and Carrier Waveforms for Switching Algorithm

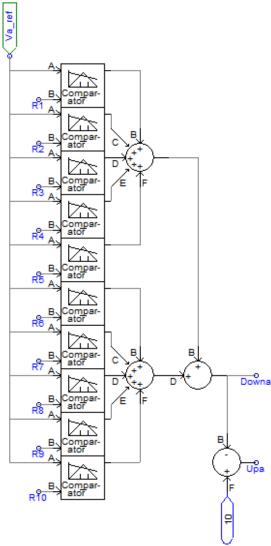

Each carrier signal was tied to a comparator. The output of each comparator was equal to 1 when the reference voltage was greater than its corresponding carrier signal and otherwise equal to 0. The outputs of all of the comparators for a given phase were summed, which was equivalent to the total number of necessary ON cells for the upper branch of that phase or  $Nup_a$ . The same was done for the inverse of the comparator outputs, yielding the total number of necessary ON cells for the lower branch of the same phase or  $Ndown_a$ . This system is shown in Figure 12.

Figure 12: Calculation of the Number of ON Cells in the Upper and Lower Arms of Phase A

The next step was to sort the cells in the upper and lower arms of a given phase in order of ascending capacitor voltage. The sorting algorithm chosen was a standard bubble sort, which was chosen for its simplicity in terms of implementation in the PSCAD environment. The bubble sort functions by comparing each capacitor voltage to the next one and pushing the higher voltage towards the top of the array. This process is repeated until the voltages are in ascending order. However, rather than outputting the array of capacitor voltages, the function block that was implemented instead outputs the indices of the corresponding switches. Thus, if cell 5 in the

upper arm had the highest capacitor voltage, the last element of the output array would be 5. This sorted array was sent as output.

The final step of the voltage balancing method was the selection algorithm. This module had 3 inputs: the number of cells ON in the given arm, the measured current flowing in the arm, and the sorted array of cell indices from the capacitor voltage sorting algorithm. If the current flowing in the arm was positive, the module selected the number of cells specified in ascending order. If the current flowing in the arm was negative, the module selected the number of cells specified in descending order. The module then output the necessary signals to switch the associated IGBT selections. Figure 13 is an image of these sorting and selection modules.

Figure 13: Sorting and Selection Modules for the Upper and Lower Arms of Phase A

## 2.1.4 Controller Design and Tuning

Next a description of the control structure implemented into PSCAD for each converter is provided. This section covers all control associated topics of the control modeling implementation. These topics include Park's transformation, the current controller, controller performance tuning, determining current controller gains, AC voltage regulation, DC voltage regulation, and power regulation.

### Park's Transformation

For each converter station, standard PI controllers were implemented into our PSCAD/EMTDC model to regulate current, the DC output voltage, and the AC regulator. First, the Park's transformation utilized is displayed in (4a) and (4b). Note that *K* is the transformation matrix and variable *f* can be either current or voltage. Figure 14 shows generic Park Transformation blocks to more simply picture what is going on. The line-to-ground voltage measurements and current measurements for the DQ transformation are taken on the primary side (AC side, Y-side) of the transformer interfacing the MMC converter.

$$f_{dq0} = K f_{abc} \tag{4a}$$

$$K = \frac{2}{3} \begin{bmatrix} \sin(\omega t) & \sin(\omega t - 2\pi/3) & \sin(\omega t + 2\pi/3) \\ \cos(\omega t) & \cos(\omega t - 2\pi/3) & \cos(\omega t + 2\pi/3) \\ 1/2 & 1/2 & 1/2 \end{bmatrix}$$

(4b)

Figure 14: Generic Park Transformation Blocks for Voltage and Current

The Park's transformation implementation into PSCAD performed on both the current and voltage measurements are found in Figure 15 and Figure 16, respectively. Prior to the software performing the Park's transformation computations, logic is used to convert the current and voltage measurements into per unit. In the top left of each figure, one will see three inputs connected by three green bars. This is where per unit values enter into the dedicated area of the file for converting to d and q quantities.

Figure 15: Current ABC to dq0 Transformation Implementation in PSCAD

Figure 16: Voltage ABC to dq0 Transformation Implementation in PSCAD

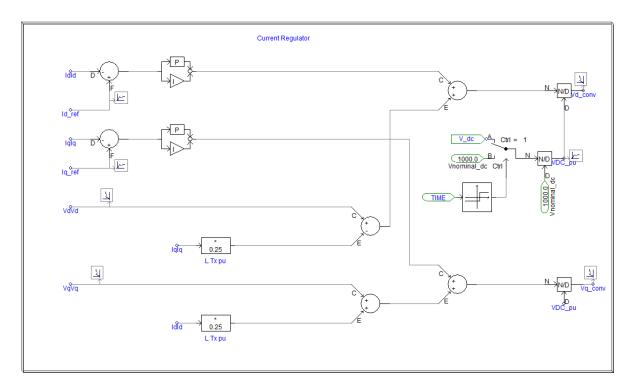

#### Current Controller

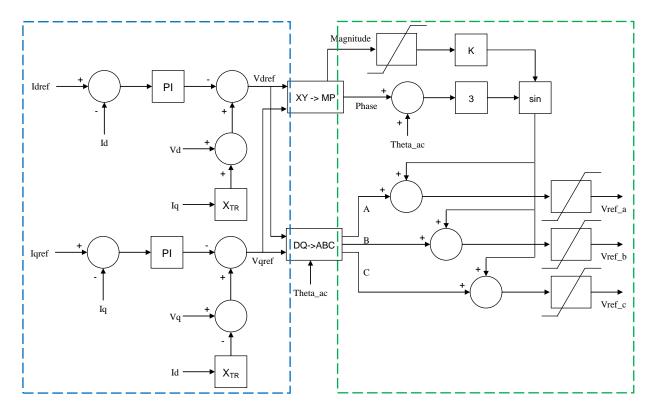

The AC current regulator for each HVDC converter station is found in Figure 17. The section surrounded with a blue outline is the current controller and the section with a green outline sets up the reference signals for the pulse width modulator. The standard relationships, based off of Kirchoff's voltage law, governing the current controller are listed as (5a) and (5b) for the d-axis and q-axis, respectively [23]. Note that  $k_P$  and  $k_I$  are the PI controller gains and  $X_{Tx}$  is the transformer reactance.  $V_{d,meas}$ ,  $V_{q,meas}$ ,  $I_{d,meas}$ ,  $I_{q,meas}$  are the variables computed from Figure 16, the results of Park's transformation. The error amplified by the PI controller that receives the difference between the measured DC voltage value and reference DC voltage value determines the direct axis current reference,  $I_{d,ref}$ . Similarly, the error amplified by the PI controller that receives the difference between the measured AC voltage value and reference AC voltage value determines the quadrature axis current reference,  $I_{q,ref}$ . These latter PI controllers corresponding to the DC voltage regulator and AC voltage regulator will be described in upcoming material.

$$V_{d,ref} = V_{d,meas} + X_{Tx}I_{q,meas} - \left[k_p \left(I_{d,ref} - I_{d,meas}\right) + k_I \int \left(I_{d,ref} - I_{d,meas}\right) dt\right]$$

(5a)

$$V_{q,ref} = V_{q,meas} - X_{Tx} I_{d,meas} - \left[ k_p \left( I_{q,ref} - I_{q,meas} \right) + k_I \int \left( I_{q,ref} - I_{q,meas} \right) dt \right]$$

(5b)

Figure 17: AC Current Regulator Block Diagram

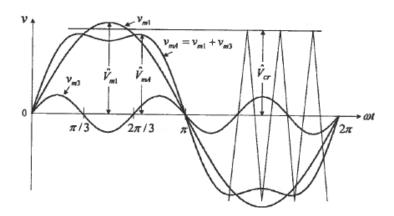

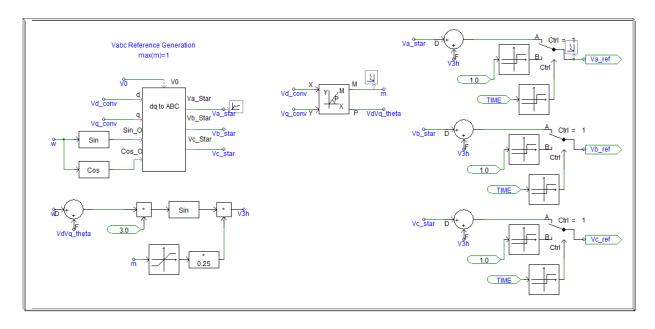

To obtain the desired DC rated voltage of the system, it may be required to increase the fundamental line-to-line voltage by adding a third harmonic component to the three-phase sinusoidal modulating wave without causing overmodulation [22]. This technique is illustrated in Figure 18. Essentially, the peak *fundamental* component can be higher than the peak triangular carrier wave, which boosts the fundamental voltage. At the same time, the *modulated* wave can be kept lower than the carrier signal avoiding problems caused by overmodulation. This technique is referred to as third harmonic injection. The reference signal generated is a combination of the three-phase sinusoidal modulated wave signal generated by the current controller based upon  $V_{d,ref}$  and  $V_{q,ref}$  and a third harmonic signal. The latter describes the purpose of the section outlined in green of Figure 17. Figure 19 and Figure 20 are the current controller and third harmonic injection implementations in PSCAD, respectively.

Figure 18: Illustration of Modulated Case with Third Harmonic Injection [22]

Figure 19: Current Controller Implementation in PSCAD

Figure 20: Third Harmonic Injection and Generated Reference Signals in PSCAD

Tuning Controller Performance [23], [24]

A simplified equivalent circuit on the AC side of the back-to-back HVDC system is found in Figure 21. The positive sequence relationships of the MMC, in terms of their synchronous *dq*-frame components can be expressed by (7a) and (7b), respectively [23].

Figure 21: Simplified Equivalent Circuit on AC Side

$$\frac{di_d}{dt} = -\frac{R}{L}i_d + \omega i_q + \frac{1}{L}u_d - \frac{1}{L}V_d \tag{7a}$$

$$\frac{di_q}{dt} = -\frac{R}{L}i_q - \omega i_d + \frac{1}{L}u_q - \frac{1}{L}V_q \tag{7b}$$

Substituting (5a) into (7a), one will arrive at (8). Equation (8) represents a first order system with open-loop transfer function described by (9).

$$L\frac{di_d}{dt} + Ri_d = \left[k_p \left(I_{d,ref} - I_{d,meas}\right) + k_I \int \left(I_{d,ref} - I_{d,meas}\right) dt\right]$$

(8)

$$l(s) = \frac{k_p + k_i / s}{Ls + R} \tag{9}$$

If the two gains are selected by (10), the open-loop and closed-loop transfer function simplify to (11) and (12), respectively.

$$k_p = \frac{L}{\tau} \quad k_I = \frac{R}{\tau} \tag{10}$$

$$l(s) = \frac{1}{\tau s} \tag{11}$$

$$G(s) = \frac{1}{\tau_S + 1} \tag{12}$$

Determining Current Controller Gains

Utilizing a value of 1 millisecond for  $\tau$  and per unit values for L and R, the following gains were determined:

$$L = \frac{X_{Tx}}{\omega} = \frac{0.25 \, p.u.}{377} = 0.000663$$

$$\frac{X_{Tx}}{R_{Tx}} = 100 \rightarrow R = \frac{0.25 \, p.u.}{100} = 0.0025 \, p.u.$$

$$k_p = \frac{L}{\tau} = \frac{0.000663 \, p.u.}{1 ms} = 0.663 \quad k_I = \frac{R}{\tau} = \frac{0.0025 \, p.u.}{1 ms} = 2.5 \xrightarrow{inverted} 0.4s$$

The per unit values utilized for L and R were the per unit values previously specified for the transformer inductance and resistance. Arm inductance and arm resistance were neglected in these gain parameter calculations since the transformer impedance is dominant.

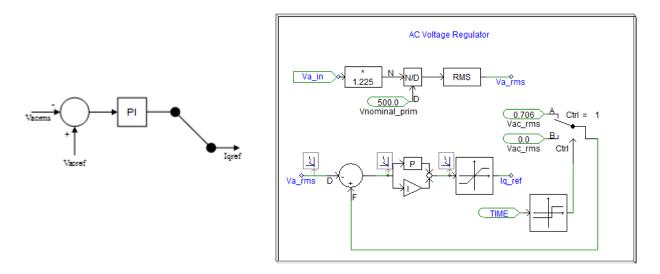

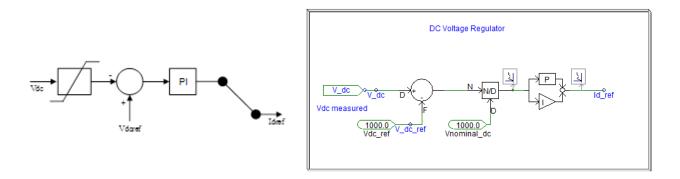

AC Voltage Regulator, DC Voltage Regulator, and Power Regulator

The last components associated with the controllers in the model include the AC voltage regulator, the DC voltage regulator, and the power regulator. The AC regulator utilized in the PSCAD implementation is provided in Figure 22. The tag labeled  $Va_i$  is a voltage measurement from the system not in per unit. Note that V(3/2) is equivalent to 1.225. There is also switch logic that sets the voltage reference at certain points in the simulation. The first reference point, B, is set until the capacitors in the MMC are initialized. As stated earlier in this report, this loop sets the quadrature axis current reference for the current controller.

Figure 22: AC Voltage Regulator and PSCAD Implementation

The DC regulator utilized and the PSCAD implementation is provided in Figure 23. As stated earlier in this report, this loop sets the direct axis current reference for the current controller. The PI controller was tuned iteratively corresponding to the response time of the system and the capacitance of each arm. This resulted in  $k_p = 10$  and  $k_I = 200$ .

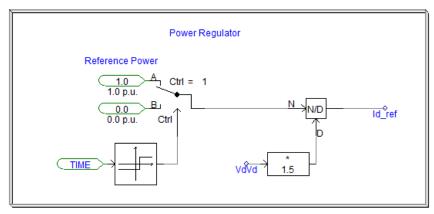

Figure 23: DC Voltage Regulator Diagram and PSCAD Implementation

In the monopolar HVDC system, one converter acts as the sending end (A) and the other as the receiving end (B) at any given time. The converter controlled by the DC voltage regulator can be seen as the sending end. The receiving end must then be controlled by a real power regulator, ensuring proper power transfer through the system. The real power regulator can be seen in Figure 24. Switch logic is used here to require full power flow only after steady state voltage is achieved in simulation, initially set to *B* and switched to *A* at 3 seconds of run time.

Figure 24: Real Power Regulator

DC voltage regulator is implemented in terminal A converter control while the power regulator is implemented in terminal B converter control. Each of these controllers function to set the direct axis current reference for the controller.

# 2.2 HVDC SYSTEM MODEL VALIDATION

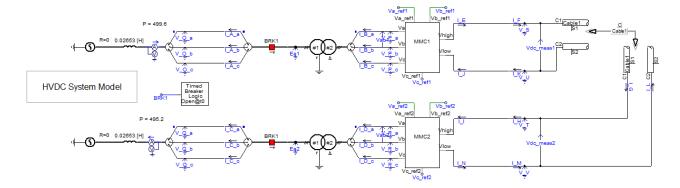

The purpose of this section is to validate the PSCAD HVDC system model by showing simulation results and assessing that they are as expected. Figure 25 shows a top level view of the entire monopolar HVDC system model in the PSCAD environment. Note that all measurement points used for plotting results are shown in this figure.

Figure 25: Top Level View of PSCAD HVDC System Model

First, the validation simulation process is here described for the purpose of having a lens through which to view and analyze the validation results. At the start of the validation simulation, the system voltage is first initialized and shown to reach steady state. This was achieved by allowing 0.1 seconds to pass before beginning converter operation. During that time, a DC voltage source of 100 kV is applied to each converter submodule capacitance to initially charge these capacitors. These DC sources are disconnected from each submodule capacitance after 0.1 seconds has passed, and the converter is simultaneously connected to the system. At this point system power flow is not yet required. In converter B control, the power reference is initially set at 0.0 p.u. to ensure achieving steady state voltage before requiring power flow. Note that at the start of converter operation (post capacitance charging), a large transient occurs in PSCAD results due to converter connection with the system. For one example of this transient, reference Figure 26, the plot of demanded and actual DC voltage at the terminal A MMC. This transient should be viewed as a computational occurrence, not as a true circuit phenomenon. This transient can be seen to reach steady state in the converter approximately at or before 1 seconds of run time. With ample time after steady state operation has been achieved, power flow is then demanded of the system at 2 seconds time. This power flow demand is achieved in simulation by changing the power regulator control reference from 0.0 p.u. to 1.0 p.u. Next, in order to demonstrate proper response from the system due to demand changes, the DC voltage is stepped from 1000 kV to 1050 kV at 3 seconds, achieved by changing the voltage regulator reference from 1000 kV to 1050 kV. Proper functionality of voltage regulation is thus demonstrated. By use of this validation simulation process, the goal of this section is achieved by demonstrating both system and control level functionality at steady state and after the step input.

The DC voltage over the course of simulation can be seen in Figure 26. It is clear that after the initial transient, the DC voltage settles near the demanded 1000 kV value. No more than 10% fluctuation in the voltage is permissible. In steady state, the overshoot can be calculated as:

$$Overshoot = \frac{V_{actual} - V_{demanded}}{V_{demanded}} \cdot 100\% = \frac{1006kV - 1000kV}{1000kV} \cdot 100\% = 0.6\%$$

Figure 26: Demanded and Actual DC Voltage on MMC A

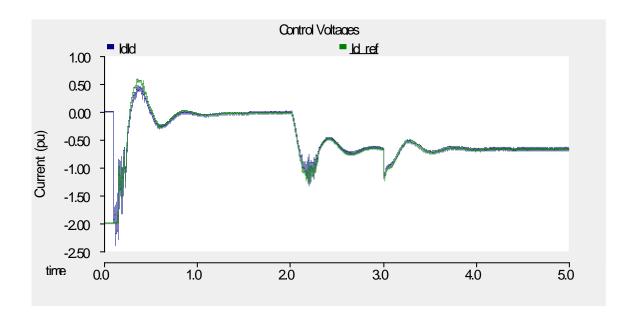

As shown in Figure 23, the step change in the DC voltage drives a corresponding change in the reference point for the direct axis current,  $I_{d\_ref}$ , via the outer PI control loop. The inner

loop control for the d-axis current then responds accordingly as demonstrated in Figure 27. Both the power demand input to the system at 2 seconds as well as the voltage step input at 3 seconds can be clearly seen, both with a rapid response from the controller. While there is noise on this signal and many others within the system, it is negligible and preferable to filtering to maintain a faster response.

Figure 27: *d*-Axis Current Controller Response

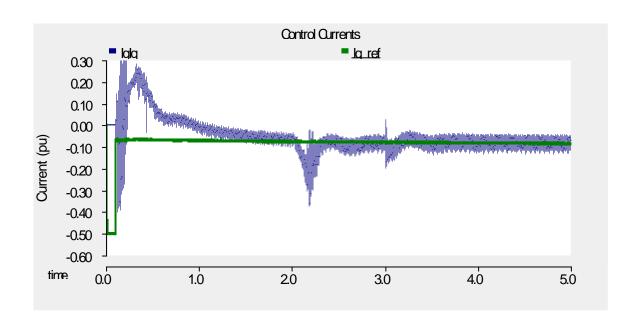

Figure 28 gives the current controller response for the q-axis controller. This control signal is also driving towards the reference established by the AC current regulator. The q-axis current is satisfactorily regulating to the reference.

Figure 28: q-Axis Current Controller Response

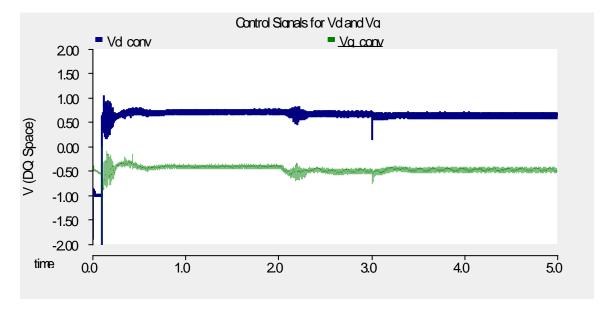

The signals that establish the reference signal for the pulse width modulator, referred to as the reference d and q-axis voltage control responses, are shown in Figure 29.

Figure 29: d and q-Axis Voltages Establishing Reference Voltage for PWM Modulator

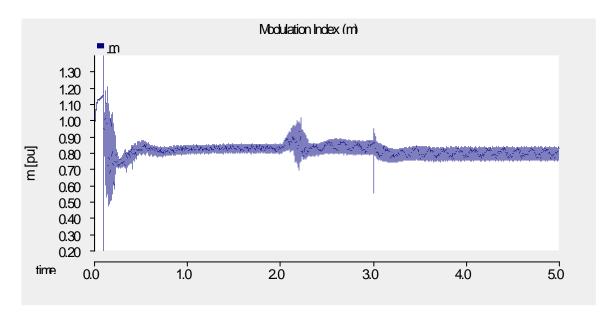

The modulation index (m) is displayed in Figure 30. Note that the modulation index operates within the linear range if its value falls between 0 and 1. Also, m is a function of the reference d and q-axis voltage signals shown in Figure 29. The correlation between these signals and the modulation index is clear upon observation. The 2 second and 3 second simulation events are clearly observed in each of these signals, responding in the same way. Once the system reaches steady state with power flow at approximately 2.5 seconds, the modulation index reaches an average value of 0.83 as expected. The modulation index is observed to decrease when the voltage is stepped from 1000 kV to 1050 kV at 3 seconds. This is as expected, because the system is rated for 1000 kV. Running the system at 1050 kV, higher than system ratings, will cause operation to fall farther from ideal rated operation (m=1.0).

Figure 30: Modulation Index

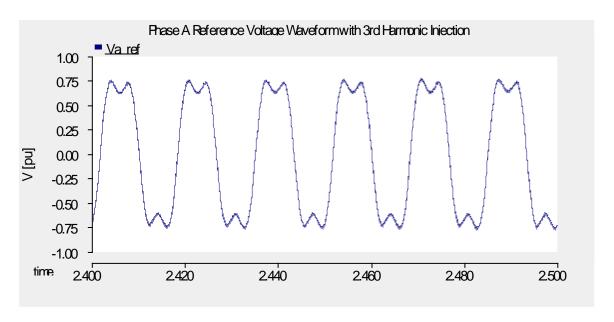

The d and q-axis control voltages, along with m, are then used to form the reference AC voltage waveform with third harmonic injection. This control signal is the output of the

controller that drives the comparators in the converter itself, and is displayed in Figure 31. This figure displays the AC control signal reference waveform during steady state with power flow. This signal is compared with the carrier waveforms to determine the number of submodules to switch, as previously shown in Figure 11.

Figure 31: Third Harmonic Injected AC Control Signal Waveform

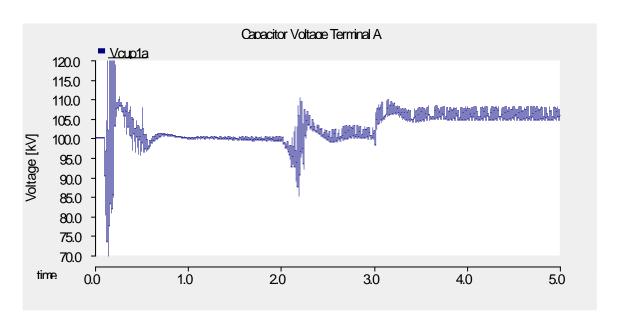

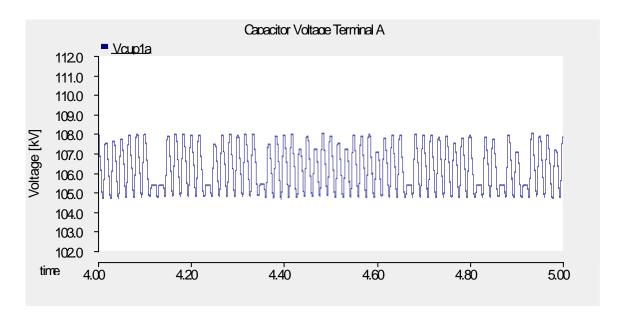

The sequenced switching of submodules according to the control reference waveform above yields fluctuating voltages on the capacitors in the converter. According to desired specifications, the  $\Delta V$  (ripple voltage) of the capacitors was limited to no more than a steady state  $\pm$  10%  $\Delta V$ . The capacitor voltage for the full duration of simulation is shown in Figure 32 and the steady state operation is shown in Figure 33.

Figure 32: Capacitor Voltage for Full Duration

Figure 33: Steady State Capacitor Voltage

The calculation of the voltage fluctuation is shown below. It is found to be 3.15%, which is well below the 10% specified limit.

$$\Delta V_{cap} = \frac{V_{\text{max}} - V_{avg}}{V_{avg}} = \frac{108kV - 104.7kV}{104.7kV} (100) = 3.15\%$$

By switching the capacitors according to the control output reference waveform of Figure 31 and the capacitor balancing algorithm previously presented, the line-to-neutral AC voltage waveform shown in Figure 34 is the AC output of the converter, with a peak of 408 kV. The line-to-line AC voltage is expected to be 500 kV (line-to-line RMS), as seen in Figure 35. The following calculation validates the simulation finding:

$$V_{LL}^{RMS} = \frac{\sqrt{3}}{\sqrt{2}} V_{LN}^{peak} \longrightarrow 500kV = \frac{\sqrt{3}}{\sqrt{2}} 408kV$$

Figure 34: Line-to-Neutral AC Voltage Created by the Converter

Figure 35: Line-to-Line AC Voltage Created by the Converter

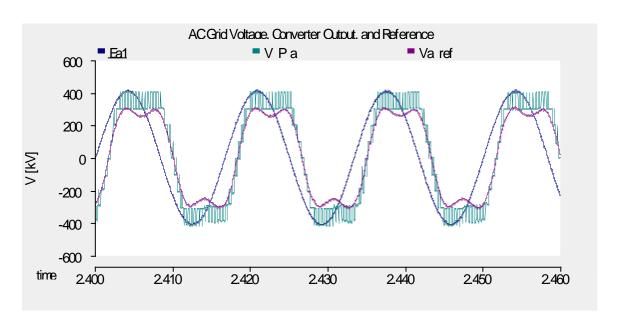

This waveform is a strong illustration that shows that the HVDC system model is functioning satisfactorily – all circuitry, capacitor balancing algorithm, and system controls. A clearer comparison of this waveform with the control signal that governs it, as well as the line-to-neutral voltage on the grid side of the transformer is presented in Figure 36. Note that the slight phase shift between the AC voltages on the converter side and the grid side is expected due to the Y-Δ transformer (30 degree phase shift). Additionally, it is important to note the effect of the transformer inductance in terms of filtering most of the harmonics generated by the converter.

Figure 36: Grid Side Voltage, Converter Side Voltage, and Reference Waveform

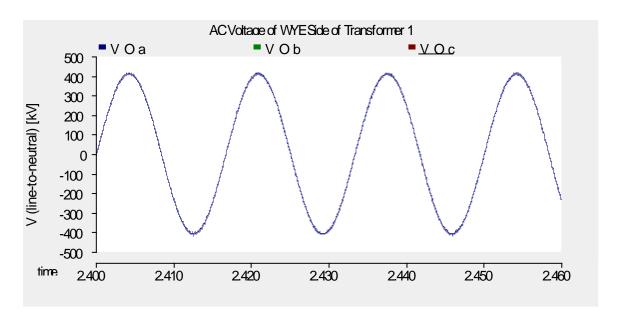

Figure 37: Grid Side of Transformer Line-to-Neutral AC Voltage

The grid side AC voltage can be seen isolated in Figure 37, and as is clearly apparent, is very smooth and free of harmonics. According to IEEE 519, to which a transmission converter must adhere, the total harmonic distortion (THD) at the point of interconnection can be no more

than 1.5% [25]. Analyzing the grid side AC voltage waveform, once the system reached steady state with power flow, it was found that the THD for this converter is less than 0.01%. This analysis was performed using the fast Fourier transform and THD calculation components in PSCAD, and verifies that the converter model designed meets the IEEE 519 specified criteria. Thus, 10 cells per arm is adequate for model simplification of the modular multilevel converter.

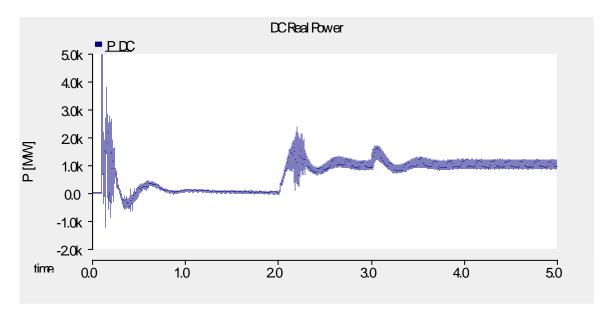

The final portion of this validation analysis presents the power flow characteristics of the converter. The DC power demand was required to be 1000 MW at 2 seconds, after a steady state voltage was achieved at approximately 1 second according to Figure 26. Steady state power flow is achieved at approximately 2.5 seconds according to Figure 38. Upon the event of stepping the voltage regulator reference at 3 seconds, steady state power flow is regained approximately half a second later. As discussed previously, the DC power flow was controlled by a power regulator at the receiving end converter. The resulting DC power flow can be seen in Figure 38.

Figure 38: DC Power Transfer

### 2.3 CONCLUSION