# ERROR CHARACTERIZATION AND CORRECTION TECHNIQUES FOR RELIABLE STT-RAM DESIGNS

by

# Wujie Wen

B.S. in Electronic Engineering,

Beijing Jiaotong University, China, 2006

M.S. in Electronic Engineering,

Tsinghua University, China, 2010

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2015

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Wujie Wen

It was defended on

June 1, 2015

and approved by

Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer

Engineering

Rami Melhem, Ph.D., Professor, Department of Computer Science

Hai Li, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Ervin Sejdic, Ph.D., Assistant Professor, Department of Electrical and Computer

Engineering

Zhi-Hong Mao, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Dissertation Director: Yiran Chen, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Copyright © by Wujie Wen2015

# ERROR CHARACTERIZATION AND CORRECTION TECHNIQUES FOR RELIABLE STT-RAM DESIGNS

Wujie Wen, PhD

University of Pittsburgh, 2015

The concerns on the continuous scaling of mainstream memory technologies have motivated tremendous investment to emerging memories. Being a promising candidate, *spin-transfer torque random access memory* (STT-RAM) offers nanosecond access time comparable to SRAM, high integration density close to DRAM, non-volatility as Flash memory, and good scalability. It is well positioned as the replacement of SRAM and DRAM for on-chip cache and main memory applications. However, reliability issue continues being one of the major challenges in STT-RAM memory designs due to the process variations and unique thermal fluctuations, *i.e.*, the stochastic resistance switching property of magnetic devices.

In this dissertation, I decoupled the reliability issues as following three-folds: First, the characterization of STT-RAM operation errors often require expensive Monte-Carlo runs with hybrid magnetic-CMOS simulation steps, making it impracticable for architects and system designs; Second, the state of the art does not have sufficiently understanding on the unique reliability issue of STT-RAM, and conventional error correction codes (ECCs) cannot efficiently handle such errors; Third, while the information density of STT-RAM can be boosted by multi-level cell (MLC) design, the more prominent reliability concerns and the complicated access mechanism greatly limit its applications in memory subsystems.

Thus, I present a novel through solution set to both characterize and tackle the above reliability challenges in STT-RAM designs. In the first part of the dissertation, I introduce a new characterization method that can accurately and efficiently capture the multi-variable design metrics of STT-RAM cells; Second, a novel ECC scheme, namely, content-dependent

ECC (CD-ECC), is developed to combat the characterized asymmetric errors of STT-RAM at  $0\rightarrow 1$  and  $1\rightarrow 0$  bit flipping's; Third, I present a circuit-architecture design, namely state-restricted multi-level cell (SR-MLC) STT-RAM design, which simultaneously achieves high information density, good storage reliability and fast write speed, making MLC STT-RAM accessible for system designers under current technology node. Finally, I conclude that efficient robust (or ECC) designs for STT-RAM require a deep holistic understanding on three different levels—device, circuit and architecture. Innovative ECC schemes and their architectural applications, still deserve serious research and investigation in the near future.

# TABLE OF CONTENTS

| 1.0 | IN  | TROI   | DUCTION                                                        | 1  |

|-----|-----|--------|----------------------------------------------------------------|----|

|     | 1.1 | МОТ    | TIVATION                                                       | 1  |

|     |     | 1.1.1  | Challenge 1: Error Characterization of STT-RAM                 | 2  |

|     |     | 1.1.2  | Challenge 2: Asymmetric Error Correction of SLC STT-RAM        | 3  |

|     |     | 1.1.3  | Challenge 3: High-Reliable High-Performance MLC STT-RAM Design | 4  |

|     | 1.2 | Disse  | rtation Contribution and Outline                               | 5  |

| 2.0 | ST  | ATIS'  | TICAL METHODOLOGY-PS3-RAM                                      | 8  |

|     | 2.1 | Prelin | minary                                                         | 8  |

|     |     | 2.1.1  | STT-RAM Basics                                                 | 8  |

|     |     | 2.1.2  | Operation Errors of MTJ                                        | 9  |

|     |     |        | 2.1.2.1 Persistent errors                                      | 9  |

|     |     |        | 2.1.2.2 Non-persistent errors                                  | 10 |

|     | 2.2 | PS3-l  | RAM Method                                                     | 11 |

|     |     | 2.2.1  | Sensitivity Analysis on MTJ Switching                          | 11 |

|     |     |        | 2.2.1.1 Threshold voltage variation                            | 11 |

|     |     |        | 2.2.1.2 Sensitivity analysis on variations                     | 13 |

|     |     |        | 2.2.1.3 Variation contribution analysis                        | 15 |

|     |     |        | 2.2.1.4 Simulation results of sensitivity analysis             | 16 |

|     |     | 2.2.2  | Write Current Distribution Recovery                            | 18 |

|     |     | 2.2.3  | Statistical Thermal Analysis                                   | 19 |

|     | 2.3 | Appli  | ication 1: Write Reliability Analysis                          | 21 |

|     |     | 2.3.1  | Reliability Analysis of STT-RAM Cells                          | 21 |

|     |     | 2.3.2 Array Level Analysis and Design Optimization | 24 |

|-----|-----|----------------------------------------------------|----|

|     | 2.4 | Application 2: Write Energy Analysis               | 26 |

|     |     | 2.4.1 Write Energy Without Variations              | 26 |

|     |     | 2.4.2 PS3-RAM for Statistical Write Energy         | 29 |

|     | 2.5 | Computation Complexity Evaluation                  | 31 |

|     | 2.6 | Appendix                                           | 32 |

|     |     | 2.6.1 Sensitivity Analysis Model Deduction         | 32 |

|     |     | 2.6.2 Analytic Results Summary                     | 34 |

|     |     | 2.6.3 Validation of Analytic Results               | 36 |

|     | 2.7 | Chapter 2 Summary                                  | 39 |

| 3.0 | CO  | NTENT-DEPENDENT ECC DESIGNS                        | 40 |

|     | 3.1 | Research Motivations                               | 40 |

|     |     | 3.1.1 Asymmetric STT-RAM Write Errors              | 40 |

|     |     | 3.1.2 Related Work                                 | 41 |

|     | 3.2 | Asymmetric Write Channel                           | 43 |

|     |     | 3.2.1 Asymmetric Write Channel (AWC) Model         | 43 |

|     |     | 3.2.1.1 Parametric Asymmetric Stages (PAS)         | 43 |

|     |     | 3.2.1.2 Random Asymmetric Stages (RAS)             | 44 |

|     |     | 3.2.1.3 Construction of AWC Model                  | 45 |

|     |     | 3.2.2 Utilization of AWC model                     | 47 |

|     | 3.3 | Content-dependent ECC (CD-ECC)                     | 49 |

|     |     | 3.3.1 Typical-Corner-ECC (TCE)                     | 49 |

|     |     | 3.3.1.1 Static Differential Coding                 | 50 |

|     |     | 3.3.1.2 Dynamic Differential Coding                | 51 |

|     |     | 3.3.1.3 Typical-Corner-ECC Design                  | 52 |

|     |     | 3.3.2 Worst-Corner-ECC                             | 53 |

|     |     | 3.3.2.1 The Codec of Worst-Corner-ECC              | 54 |

|     |     | 3.3.2.2 Efficacy of Worst-Corner-ECC               | 55 |

|     | 3.4 | Evaluation of CD-ECC                               | 57 |

|     |     | 3.4.1 Reliability                                  | 57 |

|            |               | 3.4.2 | Performance Overhead                                | 59 |

|------------|---------------|-------|-----------------------------------------------------|----|

|            | 3.5           | Chap  | ter 3 Summary                                       | 61 |

| 4.0        | $\mathbf{ST}$ | ATE-  | RESTRICT MLC STT-RAM DESIGNS FOR HIGH-RELIABLE      |    |

|            | HI            | GH-P  | PERFORMANCE MEMORY SYSTEM                           | 62 |

|            | 4.1           | Back  | ground and Motivation                               | 63 |

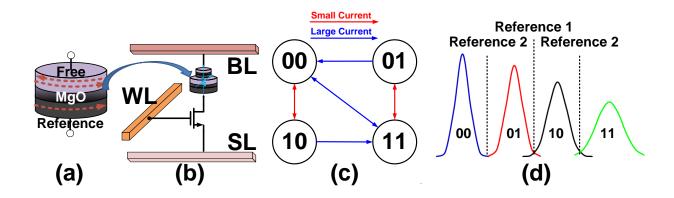

|            |               | 4.1.1 | MLC STT-RAM Basics                                  | 63 |

|            |               | 4.1.2 | Reliability of MLC STT-RAM Cells                    | 64 |

|            |               |       | 4.1.2.1 Write errors of MLC STT-RAM                 | 64 |

|            |               |       | 4.1.2.2 Read errors of MLC STT-RAM                  | 64 |

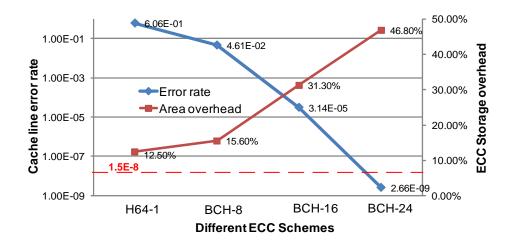

|            |               |       | 4.1.2.3 Practicability of ECC schemes               | 65 |

|            | 4.2           | SR-N  | ILC STT-RAM Design                                  | 66 |

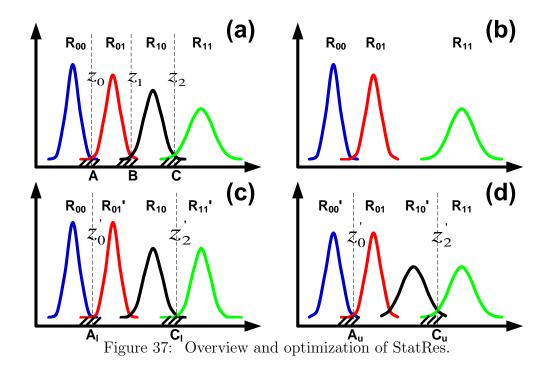

|            |               | 4.2.1 | State Restriction (StatRes)                         | 67 |

|            |               |       | 4.2.1.1 Basic concept of state restriction          | 67 |

|            |               |       | 4.2.1.2 Optimization of StatRes                     | 67 |

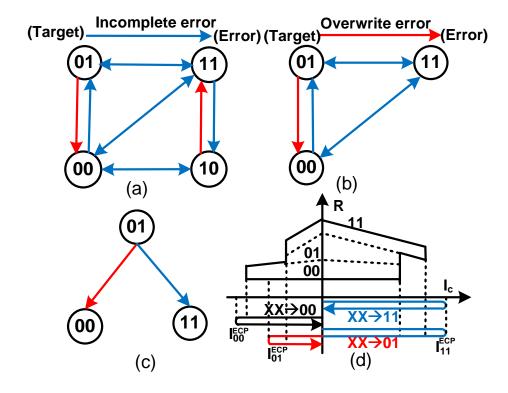

|            |               | 4.2.2 | Error-pattern Removal (ErrPR)                       | 70 |

|            |               |       | 4.2.2.1 Basic concept of ErrPR                      | 70 |

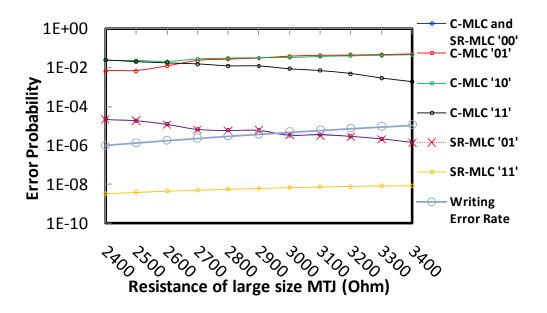

|            |               |       | 4.2.2.2 Reliability evaluation of SR-MLC with ErrPR | 72 |

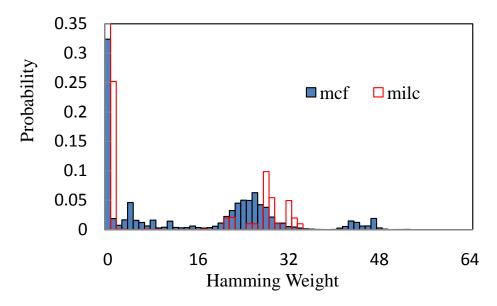

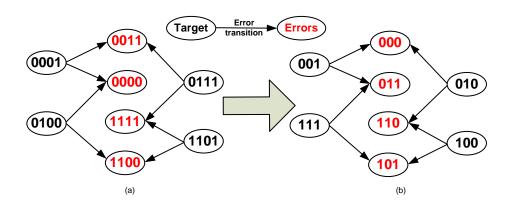

|            |               | 4.2.3 | Ternary Coding (TerCode)                            | 73 |

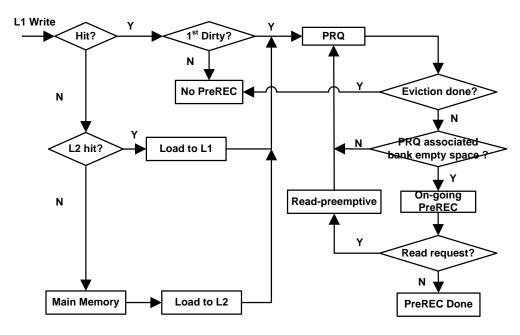

|            | 4.3           | State | Pre-recovery (PreREC)                               | 74 |

|            |               | 4.3.1 | Motivation of PreREC                                | 75 |

|            |               | 4.3.2 | Design of PreREC                                    | 75 |

|            | 4.4           | Evalu | nation of SR-MLC STT-RAM                            | 77 |

|            |               | 4.4.1 | Experiment Setup                                    | 77 |

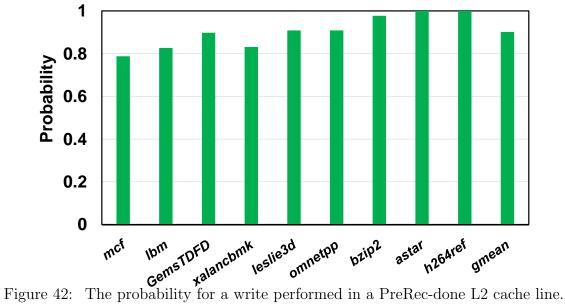

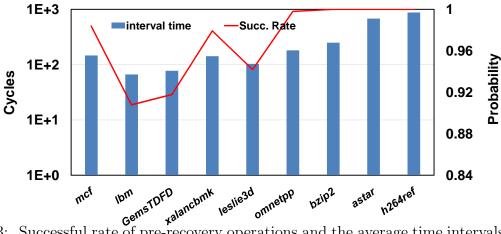

|            |               | 4.4.2 | Evaluation of PreREC                                | 79 |

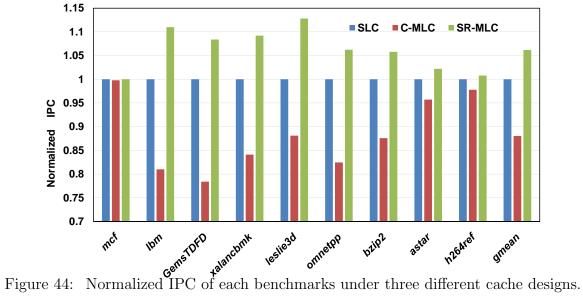

|            |               | 4.4.3 | Performance Comparison                              | 79 |

|            | 4.5           | Chap  | ter 4 Summary                                       | 81 |

| <b>5.0</b> | CO            | NCL   | USION AND FUTURE WORK                               | 82 |

|            | 5.1           | Disse | rtation Conclusion                                  | 82 |

|            |               | 5.1.1 | Conclusion of Chapter 2                             | 83 |

|            |               | 519   | Conclusion of Chapter 3                             | 85 |

|       | 5.1.3 Conclusion of Chapter 4    | 84 |

|-------|----------------------------------|----|

| 5.5   | 2 Future Work                    | 85 |

|       | 5.2.1 Facts and Observations     | 85 |

|       | 5.2.2 Multi-bit ECC Design       | 87 |

|       | 5.2.3 Non-uniform ECC Design     | 88 |

|       | 5.2.4 Architecture Investigation | 89 |

| 5.3   | 3 Research Summary and Insight   | 89 |

| BIBLI | IOGRAPHY                         | 90 |

# LIST OF TABLES

| 1 | Simulation parameters and environment setting                 | 12 |

|---|---------------------------------------------------------------|----|

| 2 | Parameter definition                                          | 32 |

| 3 | Summary of variation contribution                             | 35 |

| 4 | The configuration of the microprocessor and baseline          | 58 |

| 5 | Delay/overhead characterization of ECC schemes                | 59 |

| 6 | Binary-to-Ternary storage mapping                             | 74 |

| 7 | System configuration                                          | 78 |

| 8 | Different configurations of STT-RAM L2 cache                  | 78 |

| 9 | Reliability comparison of mixed-line, hard-line and soft-line | 87 |

# LIST OF FIGURES

| 1  | STT-RAM basics. (a) Parallel (low resistance). (b) Anti-parallel (high resis-       |    |

|----|-------------------------------------------------------------------------------------|----|

|    | tance). (c) 1T1J cell structure                                                     | 9  |

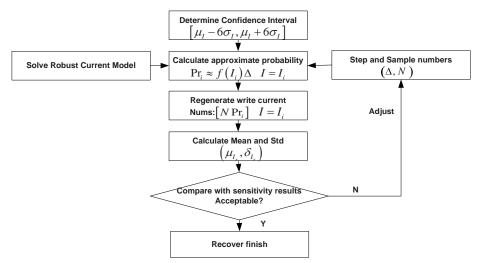

| 2  | Overview of PS3-RAM                                                                 | 12 |

| 3  | The normalized contributions under different $W$ at '1' $\rightarrow$ '0' switching | 17 |

| 4  | The normalized contributions under different $W$ at '0' $\rightarrow$ '1' switching | 17 |

| 5  | Basic flow for MTJ switching current recovery                                       | 19 |

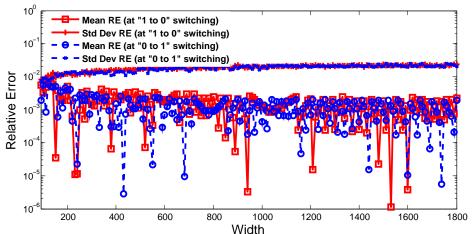

| 6  | Relative Errors of the recovered $I$ w.r.t. the results from sensitivity analysis.  | 19 |

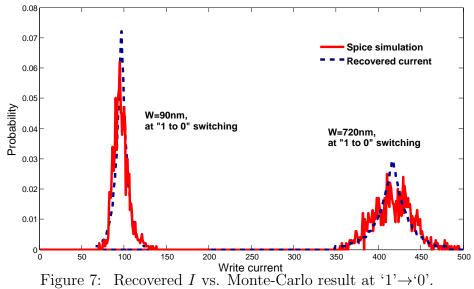

| 7  | Recovered $I$ vs. Monte-Carlo result at '1' $\rightarrow$ '0'                       | 20 |

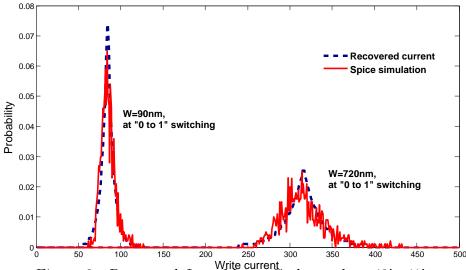

| 8  | Recovered $I$ vs. Monte-Carlo result at '0' $\rightarrow$ '1'                       | 20 |

| 9  | Write failure rate at '0' $\rightarrow$ '1' when T=300K                             | 22 |

| 10 | Write failure rate at '1' $\rightarrow$ '0' when T=300K                             | 22 |

| 11 | $P_{WF}$ under different temperatures at '0' $\rightarrow$ '1'                      | 23 |

| 12 | STT-RAM design space exploration at '0' $\rightarrow$ '1'                           | 23 |

| 13 | Write yield with ECC's at '0' $\rightarrow$ '1', $T_w$ =15ns                        | 25 |

| 14 | Design space exploration at '0' $\rightarrow$ '1'                                   | 25 |

| 15 | Average Write Energy under different write pulse width when T=300K                  | 28 |

| 16 | Average Write Energy vs write pulse width under different temperature               | 28 |

| 17 | Statistical Write Energy vs write pulse width at '1'→'0'                            | 30 |

| 18 | Statistical Write Energy vs write pulse width at '0' $\rightarrow$ '1'              | 30 |

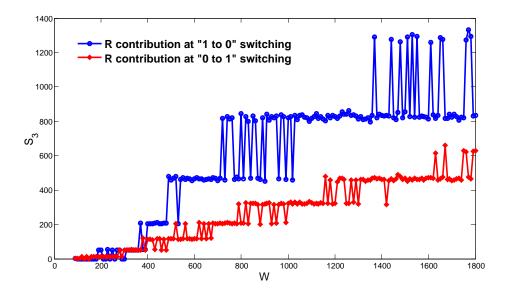

| 19 | Contributions from $W$                                                              | 36 |

| 20 | Contributions from $L$                                                              | 37 |

| 21 | Contributions from R                                                                | 37 |

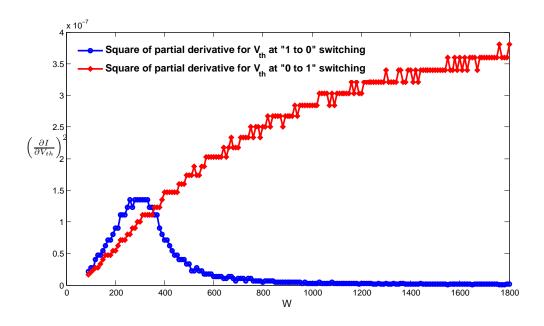

| 22 | Square partial derivatives for $V_{th}$                                                         |  |  |

|----|-------------------------------------------------------------------------------------------------|--|--|

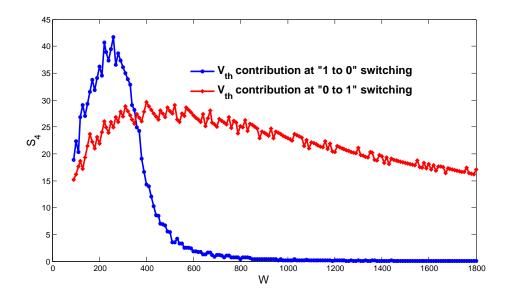

| 23 | Contributions from $V_{th}$                                                                     |  |  |

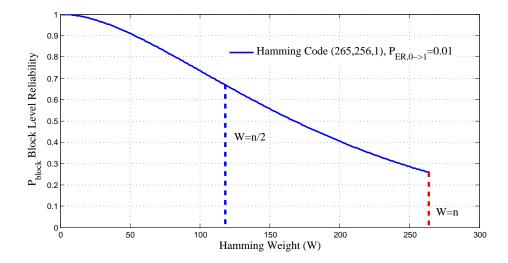

| 24 | The relationship between block level reliability $P_{block}$ and Hamming weight $W$             |  |  |

|    | for asymmetric errors                                                                           |  |  |

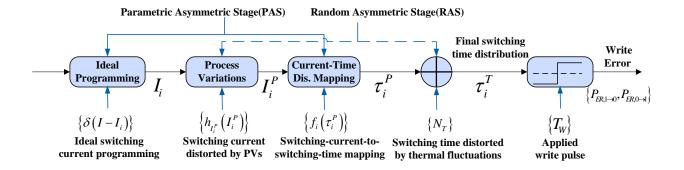

| 25 | Overview of the proposed asymmetric write channel (AWC) model                                   |  |  |

| 26 | Step breakdowns of AWC Model                                                                    |  |  |

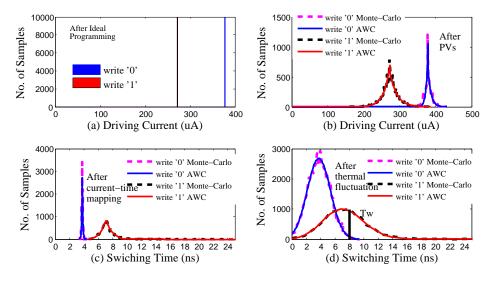

| 27 | Asymmetric error rate ratio $R$ at different $T_w$                                              |  |  |

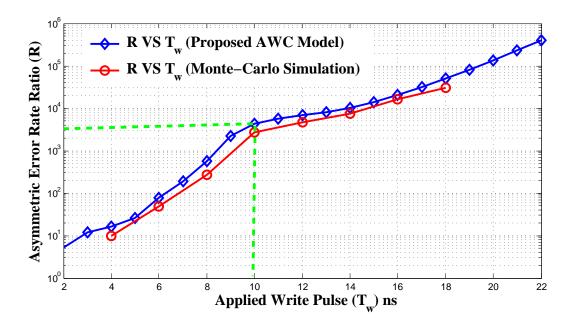

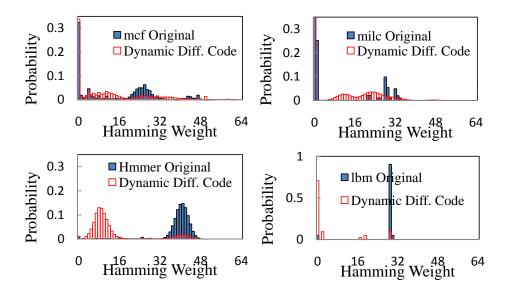

| 28 | Normalized distribution of the Hamming weight of the cache data from benchmark $mcf$ and $milc$ |  |  |

| 29 | Simulated Hamming weight distributions comparison before and after dynamic                      |  |  |

|    | differential coding                                                                             |  |  |

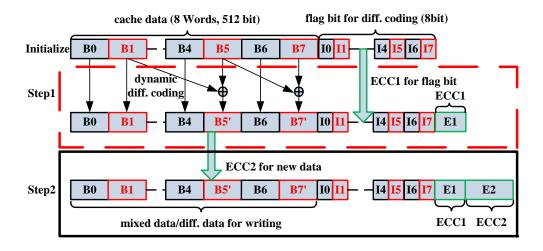

| 30 | Overview of typical-corner-ECC                                                                  |  |  |

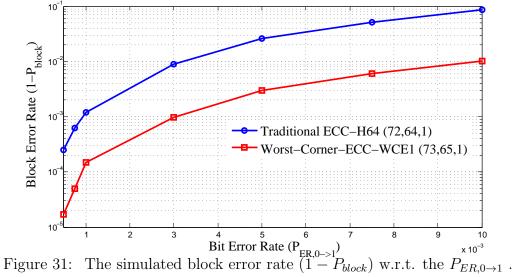

| 31 | The simulated block error rate $(1 - P_{block})$ w.r.t. the $P_{ER,0\rightarrow 1}$             |  |  |

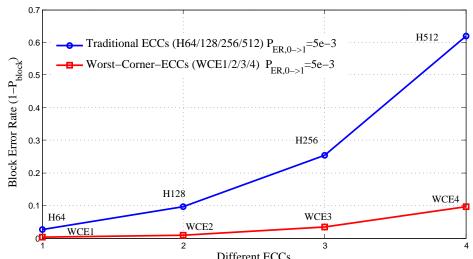

| 32 | The simulated block error rate $(1 - P_{block})$ for Worst-Corner-ECCs and Ham-                 |  |  |

|    | mings at $P_{ER,0\to 1} = 5 \times 10^{-3}$                                                     |  |  |

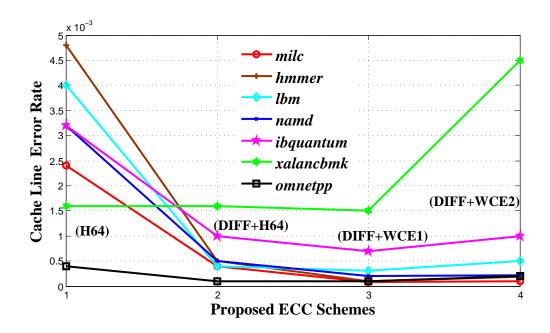

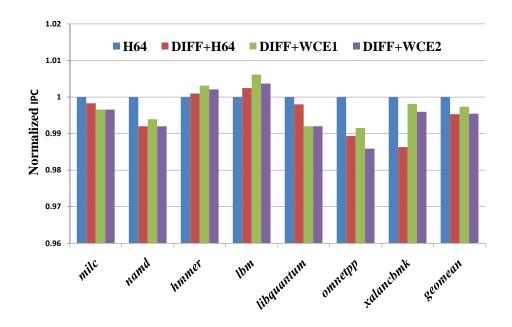

| 33 | Cache line error rate under different schemes                                                   |  |  |

| 34 | Normalized IPC of each benchmark under different schemes                                        |  |  |

| 35 | Illustrations of (a) MTJ. (b) MLC STT-RAM cell. (c) Two-step write scheme.                      |  |  |

|    | (d) Two-step read scheme.                                                                       |  |  |

| 36 | Comparison of different ECCs                                                                    |  |  |

| 37 | Overview and optimization of StatRes                                                            |  |  |

| 38 | (a) 10 error patterns of C-MLC, (b) 6 error patterns of SR-MLC, (c) 2 error                     |  |  |

|    | patterns of SR-MLC with ErrPR, (d) Overview of ErrPR                                            |  |  |

| 39 | Error rate comparison of SR-MLC vs C-MLC cells                                                  |  |  |

| 40 | (a) Error patterns of the state transitions of two SR-MLC cells, (b) Error                      |  |  |

|    | patterns mapped to the 3-bit binary data                                                        |  |  |

| 41 | Overview of PreREC                                                                              |  |  |

| 42 | The probability for a write performed in a PreRec-done L2 cache line                            |  |  |

| 43 | Successful rate of pre-recovery operations and the average time intervals be-                   |  |  |

|    | tween two consecutive reads                                                                     |  |  |

| 44 | Normalized IPC of each benchmarks under three different cache designs | 80 |

|----|-----------------------------------------------------------------------|----|

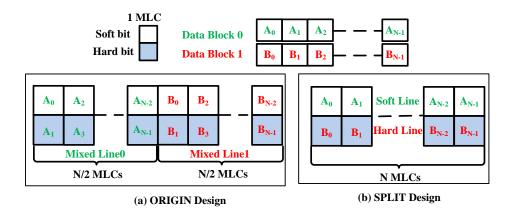

| 45 | Illustration of ORIGINAL design vs. SPLIT design structure            | 86 |

#### **PREFACE**

This dissertation is submitted in partial fulfillment of the requirements for Wujie Wen's degree of Doctor of Philosophy in Electrical and Computer Engineering. It contains the work done from September 2011 to May 2015. My advisor is Yiran Chen, University of Pittsburgh, 2010 – present.

The work is to the best of my knowledge original, except where acknowledgement and reference are made to the previous work. There is no similar dissertation that has been submitted for any other degree at any other university.

Part of the work has been published in the conference:

- 1. **DAC2014**: **W. Wen**, Y. Zhang, M. Mao and Y. Chen, "State-Restrict MLC STT-RAM Designs for High-Reliable High-Performance Memory System," Design Automation Conference (DAC), Jun. 2014, pp. 1-6 (Best Paper Award Nomination, 1 out of 42 in track, 2.4%).

- 2. **ICCAD2013**: **W. Wen**, M. Mao, X. Zhu, S. Kang, D. Wang and Y. Chen, "CD-ECC: Content-Dependent Error Correction Codes for Combating Asymmetric Nonvolatile Memory Operation Errors," International Conference on Computer Aided Design (ICCAD), Nov. 2013, pp. 1-8. (acceptance rate: 92/354 = 26%).

- 3. **DAC2012**: **W. Wen**, Y. Zhang, Y. Chen, Y. Wang and Y. Xie, "PS3-RAM: A Fast Portable and Scalable Statistical STT-RAM Reliability Analysis Method," Design Automation Conference (DAC), Jun. 2012, pp. 1191-1196. (acceptance rate: 168/741 = 23%).

- 4. **ASP-DAC2013**: **W. Wen**, Y. Zhang, L. Zhang and Y. Chen, "Loadsa: A Yield-Driven Top-Down Design Method for STT-RAM Array," 18th Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 2013, pp. 291-296.

- 5. **ISCE2014**: **W. Wen**, Y. Zhang, M. Mao and Y. Chen, "STT-RAM Reliability Enhancement through ECC and Access Scheme Optimization", International Symposium on Consumer Electronics, Jun. 2014, pp. 1-2.

- 6. **DAC2014**: M. Mao, **W. Wen**, Y. Zhang, H. Li and Y. Chen, "Exploration of GPGPU Register File Architecture Using Domain-wall-shift-write based Racetrack Memory," Design Automation Conference (DAC), Jun. 2014, pp. 1-6. (acceptance rate: 174/787 = 22.1%).

- 7. **DAC2014**: E. Eken, Y. Zhang, **W. Wen**, R. Joshi, H. Li and Y. Chen, "A New Field-Assisted Access Scheme of STT-RAM with Self-Reference Capability,", Design Automation Conference (DAC), Jun. 2014, pp. 1-6.

- 8. **ICCAD2012**: Y. Zhang, L. Zhang, **W. Wen**, G. Sun and Y. Chen, "Multi-level Cell STT-RAM: Is It Realistic or Just a Dream?" International Conference on Computer Aided Design (ICCAD), Nov. 2012, pp. 526-532. (acceptance rate: 82/338 = 24.3%).

- 9. **DATE2013**: J. Guo, **W. Wen**, and Y. Chen, "DA-RAID-5: A Disturb Aware Data Protection Technique for NAND Flash Storage Systems," Design, Automation & Test in Europe (DATE), Mar. 2013, pp. 380-385.

- 10. **ISCAS2013**: Y. Zhang, X. Bi, **W. Wen**, and Y. Chen, "STT-RAM Design Considering Probabilistic and Asymmetric MTJ Switching," IEEE International Symposium on Circuits and Systems (ISCAS), May 2013, pp. 113-116.

- 11. **INTERMAG2012**: Y. Zhang, **W. Wen**, and Y. Chen, "The Prospect of STT-RAM Scaling from Read ability Perspective," IEEE International Magnetics Conference (INTERMag), May. 2012, BB-03.

Part of the work has been published in journal publications:

- 1. **TCAD2014**: **W. Wen**, Y. Zhang, Y. Chen, Y. Wang and Y. Xie, "PS3-RAM: A Fast Portable and Scalable Statistical STT-RAM Reliability/Energy Analysis Method," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Nov., 2014, vol. 33, no.11, pp.1644-1656.

- 2. **TMAG2014**: E. Eken, Y. Zhang, **W. Wen**, R. Joshi, H. Li, and Y. Chen, "A Novel Self-reference Technique for STT-RAM Read and Write Reliability Enhancement," IEEE Transaction on Magnetics (TMAG), Nov. 2014, vol. 50, no. 11, 3401404.

- 3. **TMAG2012**: Y. Zhang, **W. Wen**, and Y. Chen, "The Prospect of STT-RAM Scaling from Read ability Perspective," IEEE Transaction on Magnetics (TMAG), vol. 48, no.1, Nov. 2012, pp. 3035-3038.

- 4. **JETC2013**: Y. Chen, W. Wong, H. Li, C.-K. Koh, Y. Zhang, and **W. Wen**, "On-chip Caches built on Multi-Level Spin-Transfer Torque RAM Cells and Its Optimizations," ACM Journal on Emerging Technologies in Computing Systems (JETC), vol. 9, no 2, article 16, May 2013.

- 5. **SPIN2013**: Y. Zhang, **W. Wen**, and Y. Chen, "STT-RAM Cell Design Considering MTJ Asymmetric Switching," SPIN, vol. 2, no. 3, Nov. 2013, 1240007.

#### ACKNOWLEDGEMENTS

I would like to acknowledge the support of my advisor, Yiran Chen, whose support made this work possible, and to 49th Design Automation Conference (DAC 2012) A. Richard Newton Scholarship, Samsung Global MRAM Innovation (SGMI 2014) Program, and National Science Foundation Project (NSF CCF-1217947) for directly providing much of the financial support. I'd like to thank Professor Yiran Chen and Professor Hai (Helen) Li for their excellent guidance during the research. Professor Yiran Chen gives me guidance of emerging nonvolatile memory designs from device modeling, circuit implementation, CAD tool development to architecture simulations and validations. Special thanks go to Professor Rami Melhem, Professor Ervin Sejdic, Professor Zhi-Hong Mao, and Professor Hai (Helen) Li for being my committee members. I also would like to thank Professor Yuan Xie from University of California at Santa Barbara, for his guidance and encouragement during my Ph.D. study.

Besides, I'd like to express my gratitude to the members from Evolutional Intelligent (EI) lab at Swanson School of Engineering, especially Mengjie Mao, Yaojun Zhang, Xiang Chen and Jie Guo, for their consistent supports during my research. Finally, I'd like to thank my wife, Shuchun Yang, the MBA student in Arizona State University (ASU) and my parents in China for their great encouragement during the whole Ph.D. research.

### 1.0 INTRODUCTION

#### 1.1 MOTIVATION

In modern computer systems, the demand on memory capacity grows sharply due to the exponentially increased data processing capability. However, the technology scaling of conventional memories, such as SRAM and DRAM, is facing severe challenges like the prominent leakage power consumption and the significant degradation in device reliability. The concerns on the continuous scaling of these mainstream technologies have motivated tremendous investment to emerging memories [1, 2, 3, 4, 5, 6], including *Phase Change RAM* (PCRAM), *Magnetic RAM* (MRAM), and *Resistive RAM* (RRAM) etc..

Being one promising candidate, spin-transfer torque random access memory (STT-RAM) has demonstrated great potentials in embedded memory and on-chip cache designs [7, 8, 9, 10, 11] through a good combination of the non-volatility of Flash, the comparable cell density to DRAM, and the nanosecond programming time like SRAM. In the past decade, many STT-RAM test chips ranging from 4Kb to 64Mb [4] have been successfully demonstrated by major semiconductor and data storage companies [2, 12, 13, 14, 15, 16, 17]. In November 2012, Everspin started shipping 64MB STT-RAM in DDR3 DIMM format [18], commencing the commercialization era of STT-RAM. Simultaneously, Crocus unveiled thermal-assisted STT-RAM chips to store transaction data on smartphones and smartcards [19].

In STT-RAM, the data is represented as the resistance state of a magnetic tunneling junction (MTJ) device. The MTJ resistance state can be programmed by applying a switching current with different polarizations. Compared to the charge-based storage mechanism of conventional memories, the magnetic storage mechanism of STT-RAM shows less dependency on the device volume and hence, better scalability.

Although STT-RAM demonstrates many attractive features, reliability issue remains as one of the main challenges in STT-RAM design and greatly hinders its wide applications. Process variations, for example, induce deviations of the electrical characteristics of MOS transistors and MTJs from their nominal values, leading to read and write errors of memory [20, 21, 22]. In addition, the resistance switching mechanism of MTJs suffers from a special source of randomness—thermal fluctuation, which generates the uncertainty of the MTJ switching time. As one major difference between STT-RAM and SRAM reliability concerns, the asymmetric structure of the popular one-transistor-one-MTJ (a.k.a. 1T1J) STT-RAM cell results in extremely unbalanced write error rates at the bit flipping's of  $0\rightarrow 1$  and  $1\rightarrow 0$ . Finally, the emergence of some advanced technologies in STT-RAM development, such as  $multi-level\ cell\ (MLC)\ design\ [23, 24]$ , further squeezes the safety margins of the read and write operations.

To summarize, in this dissertation, the complexity of reliability issue is further decoupled as following three-folds:

- 1. The difficulty of STT-RAM operation error characterization;

- 2. The inefficiency of the popular ECCs to repair the unique STT-RAM operation errors;

- 3. The infeasibility of system designers to leverage the advanced technologies for high reliable and high performance applications, e.g. multi-level cell (MLC), under current technology node.

# 1.1.1 Challenge 1: Error Characterization of STT-RAM

As pointed out by many prior arts [9, 21, 25, 26], the unreliable write operation and high write energy are to be the major issues in STT-RAM designs. And these design metrics are significantly impacted by the prominent statistical factors of STT-RAM, including CMOS/MTJ device process variations under scaled technology and the probabilistic MTJ switching behaviors. In particular, thermal fluctuations in the magnetization process introduce uncertainty to the MTJ switching time, leading to intermittent write failures if the actual MTJ switching time is longer than the applied write pulse width.

Many studies were performed to evaluate the impacts of process variations and thermal fluctuations on STT-RAM reliability [27, 28, 29]. The general error characterization flow is the follows: First, Monte-Carlo SPICE simulations are run extensively to characterize the distribution of the MTJ switching current I during the STT-RAM write operations, by considering the device variations of both MTJ and MOS transistor; Then I samples are sent into the macro-magnetic model to obtain the MTJ switching time  $(\tau_{th})$  distributions under thermal fluctuations; Finally, the  $\tau_{th}$  distributions of all I samples are merged to generate the overall MTJ switching performance distribution. A write failure happens when the applied write pulse width is shorter than the needed  $\tau_{th}$ . Nonetheless, there are two limitations here: 1) The costly Monte-Carlo runs and the dependency on the macro-magnetic and SPICE simulations incur huge computation complexity of such a method, limiting the application of such a simulation method at the early stage STT-RAM design and optimization; 2) The method is simply performed on the STT-RAM cells with fixed variation configurations, which means one variation configuration one simulation, and significantly reduces its scalability and portability. Meanwhile, the modeling of write energy in STT-RAM was also studied extensively [25]. However, many such works only assume that the write energy of STT-RAM is deterministic and cannot successfully take into account its statistical characteristic induced by process variations and thermal fluctuations.

# 1.1.2 Challenge 2: Asymmetric Error Correction of SLC STT-RAM

Error correction code (ECC) has been proven a "must-have" technology in STT-RAM designs [30, 31, 32, 33, 34, 35, 36]. However, the uniqueness of STT-RAM designs generates many new challenges in development of ECC scheme. We do not believe that the state of the art has sufficiently deep understanding on the reliability issue of STT-RAM operations, and conventional ECCs, can efficiently handle the highly asymmetric writing errors at different bit-flipping directions. The major limitations of conventional ECCs are: 1) Unable to differentiate the asymmetric bit error rate; 2) Extremely unbalanced block reliability after coding; and 3) High cost wasted on guaranteeing few worst corner blocks. Moreover, high operational error rate in STT-RAM designs (which indeed relies on the storage patterns) de-

mands for a very strong ECC scheme. However, such strong ECC usually implies long data encoding/decoding latency, which is usually against the requirement of the delay-sensitive on-chip cache applications.

# 1.1.3 Challenge 3: High-Reliable High-Performance MLC STT-RAM Design

Similar to other nonvolatile memory technologies, the information density of STT-RAM can be boosted by the advanced technology—*multi-level cell* (MLC) design, e.g., stacking two MTJ devices vertically [11]. However, the reliability concern [20] and the complicated access mechanism [37] greatly limit the application of MLC STT-RAM.

Compared to single-level cell (SLC) design, the reliability concerns of MLC STT-RAM are mainly from two perspectives: first, MLC STT-RAM cells often have narrower distinction between resistance states, resulting in a smaller sense margin of read operations; second, MLC STT-RAM cells have a higher write error rate because of more complex failure mechanisms, i.e., incomplete write or overwrite (which is new for MLC STT-RAM cells [20]) and two-step write operations. Based on [20], the read and write error rates of conventional MLC STT-RAM can be as high as  $10^{-2}$  and  $10^{-4}$ , respectively, which are far beyond the error correction capability of common simple error correction code (ECC) like single-error-correction-double-error-detection (SEC-DED) [31, 38, 39]. Applying stronger ECC like Bose-Chaudhuri-Hocquenghem (BCH) code, however, is usually impractical for on-chip applications due to the associated high area and performance overheads.

Two-step write scheme is required in conventional MLC STT-RAM to program each digit of the 2-bit data in sequence [37]. Hence, the write access time of an MLC STT-RAM cell can be at least 2× longer than that of an SLC STT-RAM cell, resulting in considerable performance penalty [40].

## 1.2 DISSERTATION CONTRIBUTION AND OUTLINE

According to above three challenges, our proposed work can be also decoupled as following three main research scopes: 1) Statistical simulation approaches to characterize the write reliability and write energy under both process variations and the intrinsic randomness in the physical mechanisms (e.g., thermal fluctuations); 2) New design concept based ECCs to tolerate the highly asymmetric write errors of STT-RAM; 3) A holistic circuit-architecture solution set to promote the early adoption of MLC STT-RAM in high reliable and high performance applications under current technology node.

For research scope 1, we proposed "PS3-RAM" – a fast, portable and scalable statistical STT-RAM reliability/energy analysis method, which includes three integrated steps: 1) characterizing the MTJ switching current distribution under both MTJ and CMOS device variations; 2) recovering MTJ switching current samples from the characterized distributions in MTJ switching performance evaluation; and 3) performing the simulation on the thermal-induced MTJ switching variations based on the recovered MTJ switching current samples. Our major technical contributions of PS3-RAM are:

- We developed a sensitivity analysis technique to capture the statistical characteristics of the MTJ switching at scaled technology nodes. It achieves multiple orders-of-magnitude (> 10<sup>5</sup>) run time cost reduction with marginal accuracy degradation, compared to SPICE-based Monte-Carlo simulations:

- We proposed using dual-exponential model for the fast and accurate recovery of MTJ switching current samples in statistical STT-RAM thermal analysis;

- We released PS3-RAM from SPICE and macro-magnetic modeling and simulations, and extended its application into the array-level reliability analysis and the design space exploration of STT-RAM.

- We introduced the concept of statistical write energy of STT-RAM and performed the statistical analysis on write energy by leveraging our PS3-RAM.

For research scope 2, we developed an analytical asymmetric write channel (AWC) model to provide a detailed step-by-step analysis to answer the questions where and how such asym-

metric write errors of STT-RAM come from. Both cell-to-cell device variations and cycle-to-cycle stochastic MTJ switching variations are considered. To address such unique errors, we carefully demonstrated the inefficiency of the traditional worst-case view based ECC design and proposed the *content-dependent ECC* (CD-ECC) by leveraging the new probabilistic ECC design view, to balance the error correcting capability at both bit-flipping directions. Two CD-ECC schemes – *typical-corner-ECC* (TCE) and *worst-corner-ECC* (WCE), are designed for the codewords with different bit-flipping distributions. The main contributions of the research scope 2 are:

- We systematically decoupled the asymmetric factors into "parametric asymmetric stages" (PAS) and "random asymmetric stages" (RAS) in AWC model, both of which are described with mathematical modeling. The AWC model can provide a quick microscopic analysis for the step-by-step accumulated asymmetry phenomena;

- We proposed CD-ECC technique to improve and balance the block-level error rate for different data patterns. Two ECC schemes – typical-corner-ECC and worst-corner-ECC, are designed for the codewords with different bit-flipping distributions;

- We evaluated the efficacy of CD-ECC technique at circuit-design and architecture levels.

Our simulation results show that CD-ECC can improve STT-RAM write reliability by 10 30× with very marginal instruction-per-cycle (IPC) performance degradation and low hardware overhead.

For research scope 3, we proposed an circuit-architecture co-optimization solution to address the multi-objective optimization problem of MLC STT-RAM on reliability, performance and integration density. The major contributions can be summarized as:

- We proposed a novel MLC STT-RAM design, namely, state-restrict MLC STT-RAM (SR-MLC STT-RAM), which can dramatically reduce the read error rate by  $\sim 10^4 \times$ .

- We developed error-pattern removable (ErrPR) technique that can significantly reduce both the number of write error patterns (from 6 to 2) and write error rate of an SR-MLC cell by  $\sim 10\times$ .

- We developed a fast and low cost *ternary coding* (TerCode) technique to make efficient transition between binary data and the tri-state SR-MLC based storage system.

• We proposed state *pre-recovery* (PreREC) technique to virtually eliminate the costly two-step programming of SR-MLC STT-RAM. Compared to *single-level cell* (SLC) STT-RAM, SR-MLC STT-RAM based cache design can boost the system performance by 6.2% on average by leveraging the increased cache capacity at the same area and the improved write and read latency.

For future work directions, we will further focus on the reliability, performance and power issues of the promising MLC STT-RAM, for example, the low-latency and cost multi-bit ECCs may need be seriously investigated due to the increased occurrence probability of the multi-bit errors in performance-driven MLC STT-RAM designs.

The outline of this dissertation is summarized as follows: Chapter 1 presents the overall picture of this dissertation, including the research motivations, research scopes and the research contributions; Chapter 2 gives the details of the proposed fast, portable, scalable and statistical method—"PS3-RAM", as well as its applications on reliability and write energy characterization; Chapter 3 describes the developed asymmetric write channel (AWC) to analyze the unique asymmetric operation errors of SLC STT-RAM, as well as the corresponding customized ECC design (CD-ECC) to tolerate such errors; Chapter 4 demonstrates the benefits of our proposed circuit architecture solution—SR-MLC, to provide intelligent balance between performance, reliability and density for MLC STT-RAM based storage system under current technology node. Chapter 5 finally summarizes the research work and presents the potential future research directions, as well as our insights for robust (or ECC) designs of emerging nonvolatile memories.

### 2.0 STATISTICAL METHODOLOGY-PS3-RAM

In this chapter, we will present the details of our error characterization methodology—PS3-RAM. The structure of this chapter is organized as the follows: Section 2.1 gives the preliminary of STT-RAM; Section 2.2 presents the details of PS3-RAM method; Section 2.3 presents the application of our PS3-RAM on cell and array level reliability analysis and design space exploration; Section 2.4 shows the deterministic/statistical write energy analysis based on our PS3-RAM; Section 2.5 discusses the computation complexity; Section 2.6 gives the detailed theatrical model deduction and its numerical validation for sensitivity analysis; Section 2.7 concludes this chapter.

# 2.1 PRELIMINARY

#### 2.1.1 STT-RAM Basics

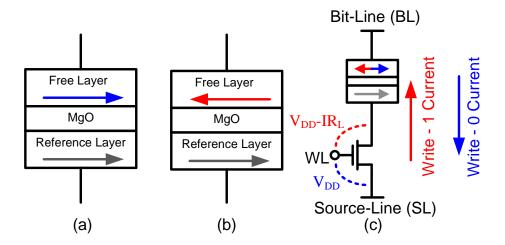

Fig. 1(c) shows the popular "one-transistor-one-MTJ (1T1J)" STT-RAM cell structure, which includes a MTJ and a NMOS transistor connected in series. In the MTJ, an oxide barrier layer (e.g., MgO) is sandwiched between two ferromagnetic layers. '0' and '1' are stored as the different resistances of the MTJ, respectively. When the magnetization directions of two ferromagnetic layers are parallel (anti-parallel), the MTJ is in its low (high) resistance state. Fig. 1(a) and (b) shows the low and the high MTJ resistance states, which are denoted by  $R_L$  and  $R_H$ , respectively. The MTJ switches from '0' to '1' when the switching current drives from reference layer to free layer, or from '1' to '0' when the switching current drives in the opposite direction.

Figure 1: STT-RAM basics. (a) Parallel (low resistance). (b) Anti-parallel (high resistance). (c) 1T1J cell structure.

# 2.1.2 Operation Errors of MTJ

In general, the MTJ switching time decreases when the switching current increases. A write failure happens when the MTJ switching does not complete before the switching current is removed. There are two reasons can cause this failure:

2.1.2.1 Persistent errors The current through the MTJ is affected by the process variations of both transistor and MTJ. For example, the driving ability of the NMOS transistor is subject to the variations of transistor channel length (L), width (W), and threshold voltage  $(V_{th})$ . The MTJ resistance variation also affects the NMOS transistor driving ability by changing its bias condition. The degraded MTJ switching current leads to a longer MTJ switching time and consequently, results in an incomplete MTJ switching before the write pulse ends. This kind of errors is referred to as "persistent" errors, which are mainly incurred by only device parametric variations. Persistent errors can be measured and repeated after the chip is fabricated.

2.1.2.2 Non-persistent errors Another kind of errors is called "non-persistent" errors, which happen intermittently and may not be repeated. The non-persistent errors of STT-RAM are mostly caused by the intrinsic thermal fluctuations during MTJ switching [41]. In general, the impact of thermal fluctuations can be modeled by the thermal induced random field  $h_{fluc}$  in stochastic Landau-Lifshitz-Gilbert (LLG) equation (Eq. 2.1) [42, 43, 44] as

$$\frac{d\overrightarrow{m}}{dt} = -\overrightarrow{m} \times (\overrightarrow{h}_{eff} + \overrightarrow{h}_{fluc}) + \alpha \overrightarrow{m} \times (\overrightarrow{h}_{eff} + \overrightarrow{h}_{fluc})) + \frac{\overrightarrow{T}_{norm}}{M_s}$$

(2.1)

Where  $\overrightarrow{m}$  is the normalized magnetization vector. Time t is normalized by  $\gamma M_s$ ;  $\gamma$  is the gyro-magnetic ratio and  $M_s$  is the magnetization saturation.  $\overrightarrow{h}_{eff} = \frac{\overrightarrow{H_{eff}}}{M_s}$  is the normalized effective magnetic field.  $\overrightarrow{h}_{fluc}$  is the normalized thermal agitation fluctuating field at finite temperature which represent the thermal fluctuation.  $\alpha$  is the LLG damping parameter.  $\overrightarrow{T}_{norm} = \frac{\overrightarrow{T}}{M_s V}$  is the spin torque term with units of magnetic field. And the net spin torque  $\overrightarrow{T}$  can be obtained through microscopic quantum electronic spin transport model. Due to thermal fluctuations, the MTJ switching time will not be a constant value but rather a distribution even under a constant switching current.

#### 2.2 PS3-RAM METHOD

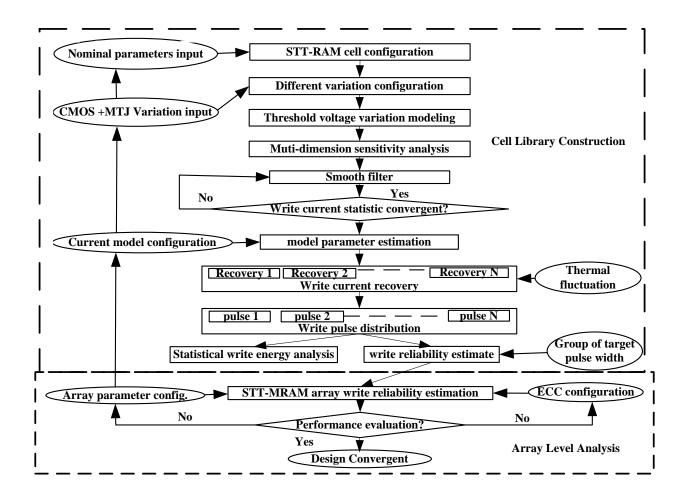

Fig. 2 depicts the overview of our proposed PS3-RAM method, mainly including the sensitivity analysis for MTJ switching current (I) characterization, the I sample recovery, and the statistical thermal analysis of STT-RAM. The first step is to configure the variation-aware cell library by inputting both the nominal design parameters and their corresponding variations, like the channel length/width/threshold voltage of NMOS transistor, as well as the thickness/area of MTJ device. Then a multi-dimension sensitivity analysis will be conducted to characterize the statistical properties of I, followed by an advanced filtering technology – smooth filter, to improve its accuracy. After that, the write current samples can be recovered based on the above characterized statistics and current distribution model. The write pulse distribution will be generated after mapping the switching current samples to the write pulse samples by considering the thermal fluctuations. Finally, the statistical write energy analysis and the STT-RAM cell write error rate can be performed based on the samples of the write current once the write pulse is determined. Array-level analysis and design optimizations can be also conducted by using PS3-RAM.

# 2.2.1 Sensitivity Analysis on MTJ Switching

In this section, we present our sensitivity model used for the characterization of the MTJ switching current distribution. We then analyze the contributions of different variation sources to the distribution of the MTJ switching current in details. The definitions of the variables used in our analysis are summarized in TABLE 1.

2.2.1.1 Threshold voltage variation The variations of channel length, width and threshold voltage are three major factors causing the variations of transistor driving ability.  $V_{th}$  variation mainly comes from random dopant fluctuation (RDF) and line-edge roughness (LER), the latter of which is also the source of some geometry variations (i.e., L and W) [45, 46]. It is known that the  $V_{th}$  variation is also correlated with L and W and its variance decreases when the transistor size increases.

Figure 2: Overview of PS3-RAM.

Table 1: Simulation parameters and environment setting

| Parameters        | Mean                                      | Standard Deviation                    |

|-------------------|-------------------------------------------|---------------------------------------|

| Channel length    | $\overline{L} = 45 \mathrm{nm}$           | $\sigma_L = 0.05\overline{L}$         |

| Channel width     | $\overline{W} = 90 \sim 1800 \text{nm}$   | $\sigma_W = 0.05\overline{L}$         |

| Threshold voltage | $\overline{V}_{th} = 0.466 V$             | by calucaltion                        |

| Mgo thickness     | $\overline{\tau} = 2.2 \mathrm{nm}$       | $\sigma_{\tau} = 0.02\overline{\tau}$ |

| MTJ surface area  | $\overline{A} = 45 \times 90 \text{nm}^2$ | by calculation                        |

| Resistance low    | $R_L = 1000\Omega$                        | by calculation                        |

| Resistance high   | $R_H = 2000\Omega$                        | by calculation                        |

The deviation of the  $V_{th}$  from the nominal value following the change of L ( $\Delta L$ ) can be modeled by [46]:

$$\Delta V_{th} = \Delta V_{th0} + V_{ds} exp(-\frac{L}{l'}) \cdot \frac{\Delta L}{l'}.$$

(2.2)

Then the standard deviation of  $V_{th}$  can be calculated as:

$$\sigma_{V_{th}}^2 = \frac{C_1}{WL} + \frac{C_2}{\exp(L/l')} \cdot \frac{W_c}{W} \cdot \sigma_L^2. \tag{2.3}$$

Here  $W_c$  is the correlation length of non-rectangular gate (NRG) effect, which is caused by the randomness in sub-wavelength lithography.  $C_1$ ,  $C_2$  and l' are technology dependent coefficients. The first term in Eq. (2.3) describes the RDF's contribution to  $\sigma_{V_{th}}$ . The second term in Eq. (2.3) represents the contribution from NRG, which is heavily dependent on Land W. Following technology scaling, the contribution of this term becomes prominent due to the reduction of L and W.

2.2.1.2 Sensitivity analysis on variations Although the contributions of MTJ and MOS transistor parametric variabilities to the MTJ switching current distribution cannot be explicitly expressed, it is still possible for us to conduct a sensitivity analysis to obtain the critical characteristics of the distribution. Without loss of generality, the MTJ switching current I can be modeled by a function of W, L,  $V_{th}$ , A, and  $\tau$ . A and  $\tau$  are the MTJ surface area and MgO layer thickness, respectively. The 1<sup>st</sup>-order Taylor expansion of I around the mean values of every parameter is:

$$I(W, L, v_{th}, A, \tau) \approx I(\overline{W}, \overline{L}, \overline{V}_{th}, \overline{A}, \overline{\tau}) + \frac{\partial I}{\partial W}(W - \overline{W})$$

$$+ \frac{\partial I}{\partial L}(L - \overline{L}) + \frac{\partial I}{\partial V_{th}}(V_{th} - \overline{V}_{th})$$

$$+ \frac{\partial I}{\partial A}(A - \overline{A}) + \frac{\partial I}{\partial \tau}(\tau - \overline{\tau}).$$

(2.4)

Here W, L and  $\tau$  generally follow Gaussian distribution [27], A is the product of two independent Gaussian distributions,  $V_{th}$  is correlated with W, L, as shown in Eq. (2.2) and (2.3). Because the MTJ resistance  $R \propto \frac{e^{\tau}}{A}$  [27], we have:

$$\frac{\partial I}{\partial A}\Delta A + \frac{\partial I}{\partial \tau}\Delta \tau = \frac{\partial I}{\partial R} \left( \frac{\partial R}{\partial A}\Delta A + \frac{\partial R}{\partial \tau}\Delta \tau \right)

= \frac{\partial I}{\partial R}\Delta R.$$

(2.5)

Eq. (2.5) indicates that the combined contribution of A and  $\tau$  is the same as the impact of MTJ resistance. The difference between the actual I and its mathematical expectation  $\mu_I$  can be calculated by:

$$I(W, L, V_{th}, R) - E\left(I\left(\overline{W}, \overline{L}, \overline{V}_{th}, \overline{R}\right)\right) \approx$$

$$\frac{\partial I}{\partial W} \Delta W + \frac{\partial I}{\partial L} \Delta L + \frac{\partial I}{\partial V_{th}} \Delta V_{th} + \frac{\partial I}{\partial R} \Delta R.$$

(2.6)

Here we assume  $\mu_I \approx E\left(I\left(\overline{W}, \overline{L}, \overline{V}_{th}, \overline{R}\right)\right) = I\left(\overline{W}, \overline{L}, \overline{V}_{th}, \overline{R}\right)$  and the mean of MTJ resistance  $\overline{R} \approx R\left(\overline{A}, \overline{\tau}\right)$ . Combining Eq. (2.2), (2.3), and (2.6), the standard deviation of  $I\left(\sigma_I\right)$  can be calculated as:

$$\sigma_{I}^{2} = \left(\frac{\partial I}{\partial W}\right)^{2} \sigma_{W}^{2} + \left(\frac{\partial I}{\partial L}\right)^{2} \sigma_{L}^{2} + \left(\frac{\partial I}{\partial R}\right)^{2} \sigma_{R}^{2}$$

$$+ \left(\frac{\partial I}{\partial V_{th}}\right)^{2} \left(\frac{C_{1}}{WL} + \frac{C_{2}}{exp\left(L/l'\right)} \cdot \frac{W_{c}}{W} \cdot \sigma_{L}^{2}\right)$$

$$+ 2\frac{\partial I}{\partial L} \frac{\partial I}{\partial V_{th}} \rho_{1} \sqrt{\frac{C_{1}}{WL}} \sigma_{L} + 2\frac{\partial I}{\partial W} \frac{\partial I}{\partial V_{th}} \rho_{2} \sqrt{\frac{C_{1}}{WL}} \sigma_{W}$$

$$+ 2\frac{\partial I}{\partial L} \frac{\partial I}{\partial V_{th}} V_{ds} exp\left(-\frac{L}{l'}\right) \frac{\sigma_{L}^{2}}{l'}. \tag{2.7}$$

Here  $\rho_1 = \frac{\text{cov}(V_{th0}, L)}{\sqrt{\sigma_{v_{th0}}^2 \sigma_L^2}}$  and  $\rho_2 = \frac{\text{cov}(V_{th0}, W)}{\sqrt{\sigma_{V_{th0}}^2 \sigma_W^2}}$  are the correlation coefficients between  $V_{th0}$  and L or W, respectively [46].  $\sigma_{V_{th0}}^2 = \frac{C_1}{WL}$ . Our further analysis shows that the last three terms at the right side of Eq. (2.7) are significantly smaller than other terms and can be safely ignored in the simulations of STT-RAM normal operations.

The accuracy of the coefficient in front of the variances of every parameter at the right side of Eq. (2.7) can be improved by applying window based smooth filtering. Take W as an example, we have:

$$\left(\frac{\partial I}{\partial W}\right)_{i} = \frac{I\left(\overline{W} + i\Delta W, L, V_{th}, R\right) - I\left(\overline{W} - i\Delta W, L, V_{th}, R\right)}{2i\Delta W},\tag{2.8}$$

where i = 1, 2, ...K. Different  $\frac{\partial I}{\partial W}$  can be obtained at the different step i. K samples can be filtered out by a windows based smooth filter to balance the accuracy and the computation complexity as:

$$\frac{\overline{\partial I}}{\partial W} = \sum_{i=1}^{K} \omega_i \left( \frac{\partial I}{\partial W} \right)_i.$$

(2.9)

Here  $\omega_i$  is the weight of sample i, which is determined by the window type, i.e., Hamming window or Rectangular window [47].

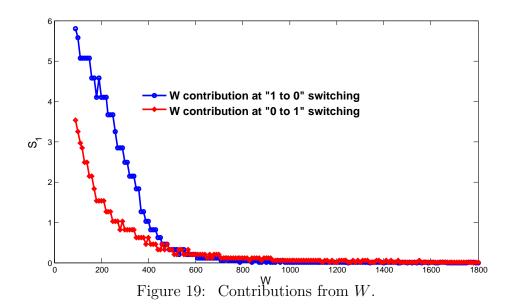

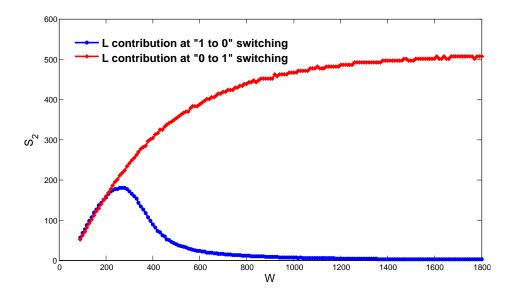

**2.2.1.3** Variation contribution analysis The variations' contributions to I are mainly represented by the first four terms at the right side of Eq (2.7) as:

$$S_{1} = \left(\frac{\partial I}{\partial W}\right)^{2} \sigma_{W}^{2}, S_{2} = \left(\frac{\partial I}{\partial L}\right)^{2} \sigma_{L}^{2}, S_{3} = \left(\frac{\partial I}{\partial R}\right)^{2} \sigma_{R}^{2}$$

$$S_{4} = \left(\frac{\partial I}{\partial V_{th}}\right)^{2} \left(\frac{C_{1}}{WL} + \frac{C_{2}}{exp\left(L/l'\right)} \cdot \frac{W_{c}}{W} \cdot \sigma_{L}^{2}\right). \tag{2.10}$$

As pointed out by many prior-arts [36, 48, 49], an asymmetry exists in STT-RAM write operations: the switching time of '0' $\rightarrow$ '1' is longer than that of '1' $\rightarrow$ '0' and suffers from a larger variance. Also, the switching time variance of '0' $\rightarrow$ '1' is more sensitive to the transistor size changes than '1' $\rightarrow$ '0'. As we shall show later, this phenomena can be well explained by using our sensitivity analysis. To the best of our knowledge, this is the first time the asymmetric variations of STT-RAM write performance and their dependencies on the transistor size are explained and quantitatively analyzed.

As shown in Fig. 1, when writing '0', the word-line (WL) and bit-line (BL) are connected to  $V_{dd}$  while the source-line (SL) is connected to ground.  $V_{gs} = V_{dd}$  and  $V_{ds} = V_{dd} - IR$ . The NMOS transistor is mainly working in triode region. Based on short-channel BSIM model, the MTJ switching current supplied by a NMOS transistor can be calculated by:

$$I = \frac{\beta \cdot \left[ (V_{dd} - V_{th}) (V_{dd} - IR) - \frac{a}{2} (V_{dd} - IR)^2 \right]}{1 + \frac{1}{v_{sat}L} (V_{dd} - IR)}.$$

(2.11)

Here  $\beta = \frac{\mu_0 C_{ox}}{1 + U_0 (V_{dd} - V_{th})} \frac{W}{L}$ .  $U_0$  is the vertical field mobility reduction coefficient,  $\mu_0$  is electron mobility,  $C_{ox}$  is gate oxide capacitance per unit area, a is body-effect coefficient and  $v_{sat}$  is carrier velocity saturation. Based on short-channel PTM model [50] and BSIM model [51, 52], we derive  $\left(\frac{\partial I}{\partial W}\right)^2$ ,  $\left(\frac{\partial I}{\partial L}\right)^2$ , and  $\left(\frac{\partial I}{\partial V_{th}}\right)^2$  as:

$$\left(\frac{\partial I}{\partial W}\right)_0^2 \approx \frac{1}{\left(A_1W + B_1\right)^4}, \quad \left(\frac{\partial I}{\partial L}\right)_0^2 \approx \frac{1}{\left(\frac{A_2}{W} + B_2W + C\right)^2}$$

$$\left(\frac{\partial I}{\partial R}\right)_0^2 \approx \frac{1}{\left(\frac{A_3}{W} + B_3\right)^4}, \quad \left(\frac{\partial I}{\partial V_{th}}\right)_0^2 \approx \frac{1}{\left(\frac{A_4}{\sqrt{W}} + B_4\sqrt{W}\right)^4}.$$

Our analytical deduction shows that the coefficients  $A_{1-4}$ ,  $B_{1-4}$  and C are solely determined by W, L,  $V_{th}$ , and R. The detailed expressions of coefficients  $A_{1-4}$ ,  $B_{1-4}$  and C can be found in the appendix. Here R is the high resistance state of the MTJ, or  $R_H$ . For a NMOS transistor at '0' $\rightarrow$ '1' switching, the MTJ switching current is:

$$I = \frac{\beta}{2a} \left[ (V_{dd} - IR - V_{th}) - \frac{I}{W C_{ox} v_{sat}^2} \right]^2.$$

(2.12)

Here R is the low resistance state of the MTJ, or  $R_L$ . We have:

$$\left(\frac{\partial I}{\partial W}\right)_{1}^{2} \approx \frac{1}{\left(A_{5}W + B_{5}\right)^{4}}, \quad \left(\frac{\partial I}{\partial L}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{6}}{W} + B_{6}\right)^{2}} \\

\left(\frac{\partial I}{\partial R}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{7}}{W} + B_{7}\right)^{4}}, \quad \left(\frac{\partial I}{\partial V_{th}}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{8}}{W} + B_{8}\right)^{2}}$$

Again,  $A_{5-8}$  and  $B_{5-8}$  can be expressed as the function of W, L,  $V_{th}$ , and R and the detailed expressions of those parameters can be found in the appendix.

In general, a large  $S_i$  corresponds to a large contribution to I variation. When W is approaching infinity, only  $S_3$  is nonzero at '1' $\rightarrow$ '0' switching while both  $S_2$  and  $S_3$  are nonzero at '0' $\rightarrow$ '1' switching. It indicates that the residual values of  $S_1$ - $S_4$  at '0' $\rightarrow$ '1' switching is larger than that at '1' $\rightarrow$ '0' switching when  $W \rightarrow \infty$ . In other words, '0' $\rightarrow$ '1' switching suffers from a larger MTJ switching current variation than '1' $\rightarrow$ '0' switching when NMOS transistor size is large.

2.2.1.4 Simulation results of sensitivity analysis Sensitivity analysis [53] can be used to obtain the statistical parameters of MTJ switching current, i.e., the mean and the standard deviation, without running the costly SPICE and Monte-Carlo simulations. It can be also used to analyze the contributions of different variation sources to I variation in details. The normalized contributions  $(P_i)$  of variation resources, i.e., W, L,  $V_{th}$ , and R, are defined as:

$$P_i = \frac{S_i}{\sum_{i=1}^4 S_i}, i = 1, 2, 3, 4 \tag{2.13}$$

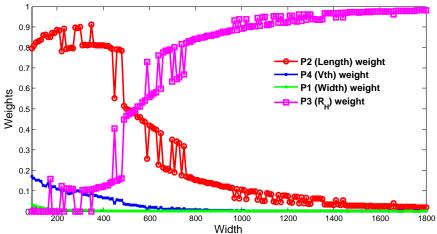

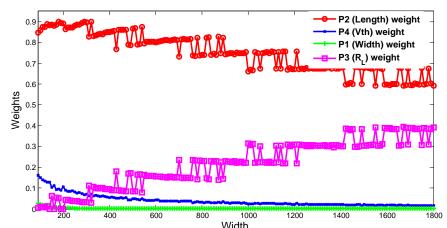

Figure 3: The normalized contributions under different W at '1' $\rightarrow$ '0' switching.

Figure 4: The normalized contributions under different W at '0' $\rightarrow$ '1' switching.

Fig. 3 and Fig. 4 show the normalized contributions of every variation source at '0' $\rightarrow$ '1' and '1' $\rightarrow$ '0' switching's, respectively, at different transistor sizes. We can see that L and  $V_{th}$  are the first two major contributors to I variation at both switching directions when W is small. At '1' $\rightarrow$ '0' switching, the contribution of L raises until reaching its maximum value when W increases, and then quickly decreases when W further increases. At '0' $\rightarrow$ '1' switching, however, the contribution of L monotonically decreases, but keeps being the dominant factor over the simulated W range. At both switching directions, the contributions of R ramps up when W increases. At '1' $\rightarrow$ '0' switching, the normalized contribution of R becomes almost 100% when W is really large.

# 2.2.2 Write Current Distribution Recovery

After the I distribution is characterized by the sensitivity analysis, the next question becomes how to recover the distribution of I from the characterized information in the statistical analysis of STT-RAM reliability. We investigate the typical distributions of I in various STT-RAM cell designs and found that dual-exponential function can provide the excellent accuracy in modeling and recovering these distributions. The dual-exponential function we used to recover the I distributions can be illustrated as:

$$f(I) = \begin{cases} a_1 e^{b_1(I-u)} & I \le u, \\ a_2 e^{b_2(u-I)} & I > u. \end{cases}$$

(2.14)

Here  $a_1$ ,  $b_1$ ,  $a_2$ ,  $b_2$  and u are the fitting parameters, which can be calculated by matching the first and the second order momentums of the actual I distribution and the dual-exponential function as:

$$\int f(I)dI = 1,$$

$$\int If(I)dI = E(I),$$

$$\int I^{2}f(I)dI = E(I)^{2} + \sigma_{I}^{2}.$$

(2.15)

Here  $E\left(I\right)$  and  $\sigma_{I}^{2}$  are obtained from the sensitivity analysis.

The recovered I distribution can be used to generate the MTJ switching current samples, as shown in Fig. 5. At the beginning of the sample generation flow, the confidence interval for STT-RAM design is determined, e.g.,  $[\mu_I - 6\sigma_I, \mu_I + 6\sigma_I]$  for a six-sigma confidence interval. Assuming we need to generate N samples within the confidence interval, say, at the point of  $I = I_i$ , a switching current sequence of  $[NPr_i]$  samples must be generated. Here  $Pr_i \approx f(I_i) \Delta$ .  $\Delta$  equals  $\frac{12\sigma_I}{N}$ , or the step of sampling generation.  $f(I_i)$  is the dual-exponential function.

Fig. 6 shows the relative errors of the mean and the standard deviation of the recovered I distribution w.r.t. the results directly from the sensitivity analysis (as Eq. (2.6) and (2.7) show). The maximum relative error  $< 10^{-2}$ , which proves the accuracy of our dual-exponential model.

Figure 5: Basic flow for MTJ switching current recovery.

Figure 6: Relative Errors of the recovered  $\overset{\mathsf{Width}}{I}$  w.r.t. the results from sensitivity analysis.

Fig. 7 and Fig. 8 compare the probability distribution functions (PDF's) of I from the SPICE Monte-Carlo simulations and from the recovery process based on our sensitivity analysis at two switching directions. Our method achieves good accuracy at both representative transistor channel widths (W = 90nm or W = 720nm).

# 2.2.3 Statistical Thermal Analysis

The variation of the MTJ switching time  $(\tau_{th})$  incurred by the thermal fluctuations follows Gaussian distribution when  $\tau_{th}$  is below 10~20ns [48]. In this range, the distribution of

Figure 8: Recovered I vs. Monte-Carlo result at '0' $\rightarrow$ '1'.

$\tau_{th}$  can be easily constructed after the I is determined. The distribution of MTJ switching performance can be obtained by combining the  $\tau_{th}$  distributions of all I samples.

## 2.3 APPLICATION 1: WRITE RELIABILITY ANALYSIS

In this section, we conduct the statistical analysis on the write reliability of STT-RAM cells by leveraging our PS3-RAM method. Both device variations and thermal fluctuations are considered in the analysis. We also extend our method into array-level evaluation and demonstrate its effectiveness in STT-RAM design optimizations.

## 2.3.1 Reliability Analysis of STT-RAM Cells

The write failure rate  $P_{WF}$  of a STT-RAM cell can be defined as the probability that the actual MTJ switching time  $\tau_{th}$  is longer than the write pulse width  $T_w$ , or  $P_{WF} = P\left(\tau_{th} > T_w\right)$ .  $\tau_{th}$  is affected by the MTJ switching current magnitude, the MTJ and MOS device variations, the MTJ switching direction, and the thermal fluctuations. The conventional simulation of  $P_{WF}$  requires costly Monte-Carlo runs with hybrid SPICE and macro-magnetic modeling steps. Instead, we can use PS3-RAM to analyze the statistical STT-RAM write performance. The corresponding simulation environment is also summarized in TABLE 1.

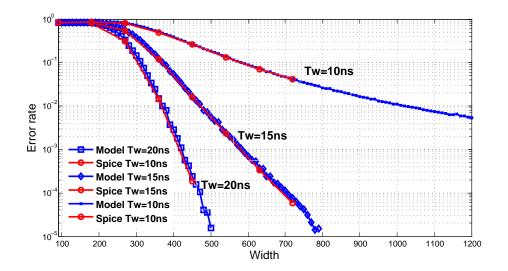

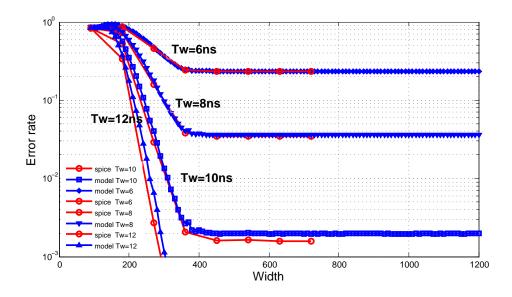

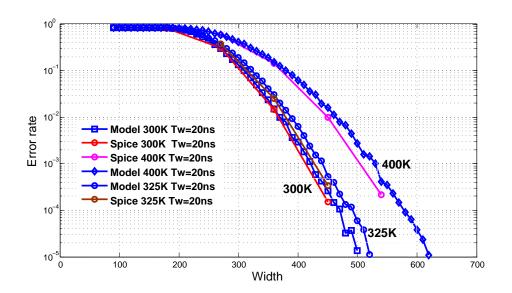

Fig. 9 and 10 depict the  $P_{WF}$ 's simulated by PS3-RAM for both switching directions at 300K. For comparison purpose, the Monte-Carlo simulation results are also presented. Different  $T_w$ 's are selected at either switching directions due to the asymmetric MTJ switching performances [48], i.e.,  $T_w = 10, 15, 20ns$  at '0' $\rightarrow$ '1' and  $T_w = 6, 8, 10, 12ns$  at '1' $\rightarrow$ '0'. Our PS3-RAM results are in excellent agreement with the ones from Monte-Carlo simulations.

Since '0' $\rightarrow$ '1' is the limiting switching direction for STT-RAM reliability, we also compare the  $P_{WF}$ 's of different STT-RAM cell designs under different temperatures at this switching direction in Fig. 11. The results show that PS3-RAM can provide very close but pessimistic results compared to those of the conventional simulations. PS3-RAM is also capable to precisely capture the small error rate change incurred by a moderate temperature shift (from T=300K to T=325K).

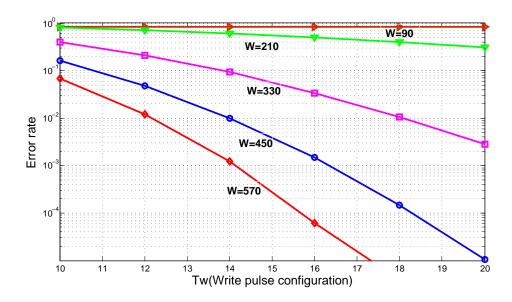

It is known that prolonging the write pulse width and increasing the MTJ switching current (by sizing up the NMOS transistor) can reduce the  $P_{WF}$ . In Fig. 12, we demonstrate an example of using PS3-RAM to explore the STT-RAM design space: the tradeoff curves

Figure 9: Write failure rate at '0' $\rightarrow$ '1' when T=300K.

Figure 10: Write failure rate at '1' $\rightarrow$ '0' when T=300K.

between  $P_{WF}$  and  $T_w$  are simulated at different W's. For a given  $P_{WF}$ , for example, the corresponding tradeoff between W and  $T_w$  can be easily identified on Fig. 12.

Figure 11:  $P_{WF}$  under different temperatures at '0' $\rightarrow$ '1'.

Figure 12: STT-RAM design space exploration at '0' $\rightarrow$ '1'.

# 2.3.2 Array Level Analysis and Design Optimization

We use a 45nm 256Mb STT-RAM design [39] as the example to demonstrate how to extend our PS3-RAM into array-level analysis and design optimizations. The number of bits per memory block  $N_{bit} = 256$  and the number of memory blocks  $N_{word} = 1$ M. ECC (error correction code) is applied to correct the random write failures of memory cells. Two types of ECC's with different implementation costs are being considered, i.e., single-bit-correcting Hamming code and a set of multi-bits-correcting BCH codes. We use (n, k, t) to denote an ECC with n codeword length, k bit user bits being protected (256 bit here) and t bits being corrected. The ECC's corresponding to the error correction capability t from 1 to 5 are Hamming code (265, 256, 1) and four BCH codes – BCH1 (274, 256, 2), BCH2 (283, 256, 3), BCH3 (292, 256, 4) and BCH4 (301, 256, 5), respectively. The write yield of the memory array  $Y_{wr}$  can be defined as:

$$Y_{wr} = P(n_e \le t) = \sum_{i=0}^{t} C_n^i P_{WF}^i (1 - P_{WF})^{n-i}.$$

(2.16)

Here,  $n_e$  denotes the total number of error bits in a write access.  $Y_{wr}$  indeed denotes the probability that the number of error bits in a write access is smaller than that of the error correction code can fix.

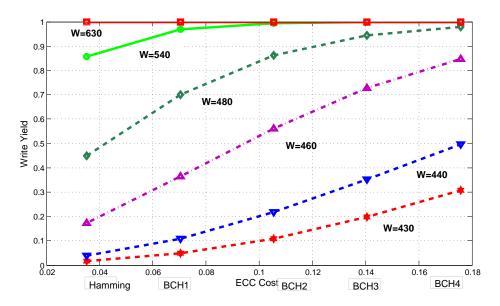

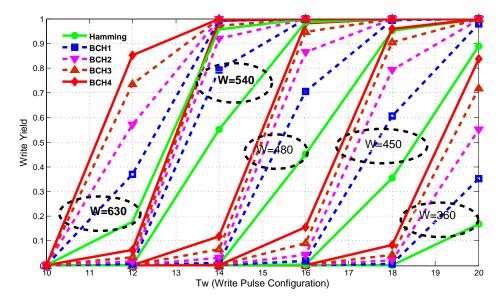

Fig. 13 depicts the  $Y_{wr}$ 's under different combinations of ECC scheme and W when  $T_w = 15$ ns at '0' $\rightarrow$ '1' switching. The ECC schemes required to satisfy  $\sim 100\% \ Y_{wr}$  for different W are: (1) Hamming code for W = 630nm; (2) BCH2 for W = 540nm; and (3) BCH4 for W = 480nm. The total memory array area can be estimated by using the STT-RAM cell size equation Area<sub>cell</sub> =  $3(W/L + 1)(F^2)$  [54]. Calculation shows that combination (3) offers us the smallest STT-RAM array area, which is only 88% and 95% of the ones of (1) and (2), respectively. We note that PS3-RAM can be seamlessly embedded into the existing deterministic memory macro models [54] for the extended capability on the statistical reliability analysis and the multi-dimensional design optimizations on area, yield, performance and energy.

Fig. 14 illustrates the STT-RAM design space in terms of the combinations of  $Y_{wr}$ , W,  $T_{sw}$  and ECC scheme. After the pair of  $(Y_{wr}, T_w)$  is determined, the tradeoff between W

and ECC can be found in the corresponding region on the figure. The result shows that PS3-RAM provides a fast and efficient method to perform the device/circuit/architecture co-optimization for STT-RAM designs.

Figure 13: Write yield with ECC's at '0'—'1',  $T_w$ =15ns.

Figure 14: Design space exploration at '0' $\rightarrow$ '1'.

## 2.4 APPLICATION 2: WRITE ENERGY ANALYSIS

In addition to write reliability analysis, our PS3-RAM method can also precisely capture the write energy distributions influenced by the variations of device and working environment. In this section, we first prove that there is a sweet point of write pulse width for the minimum write energy without considering any variations. Then we introduce the concept of statistical write energy of STT-RAM cells considering both process variations and thermal fluctuations, and perform the statistical analysis on write energy using our PS3-RAM method.

## 2.4.1 Write Energy Without Variations

The write energy of a STT-RAM cell during each programming cycle without considering process and thermal variations is deterministic and can be modeled by Eq. (2.17) as:

$$E_{av} = I^2 R \tau_{th}. \tag{2.17}$$

Here I denotes the switching current at either '0' $\rightarrow$ '1' or '1' $\rightarrow$ '0' switching,  $\tau_{th}$  is the corresponding MTJ switching time and R is the MTJ resistance value, i.e.,  $R_L$  ( $R_H$ ) for '0' $\rightarrow$ '1'('1' $\rightarrow$ '0') switching. As discussed in prior art [48], the switching process of an STT-RAM cell can be divided into three working regions:

$$I = \begin{cases} I_{C_0} \left( 1 - \frac{\ln(\tau_{th}/\tau_0)}{\Delta} \right), & \tau_{th} > 10 \text{ns} \\ I_{C_0} + C \ln\left(\frac{\pi}{2\theta}\right) / \tau_{th}, & \tau_{th} < 3 \text{ns} \\ \frac{P}{\tau_{th}} + Q. & 3 \le \tau_{th} \le 10 \text{ns} \end{cases}$$

$$(2.18)$$

Here  $I_{C_0}$  is the critical switching current,  $\Delta$  is thermal stability,  $\tau_0 = 1$ ns is the relax time,  $\theta$  is the initial angle between the magnetization vector and the easy axis, and C, P, Q are fitting parameters.

For a relatively long switching time range ( $\tau_{th} \approx 10 \sim 300 \text{ns}$ ), the undistorted write energy  $P_{av}$  can be calculated as:

$$E_{av} = I_{C_0}^2 \left( 1 - \frac{\ln \tau_{th}}{\Delta} \right)^2 R \tau_{th}$$

$$= \frac{I_{C_0}^2 R}{\Delta^2} (\Delta - \ln \tau_{th})^2 \tau_{th}. \tag{2.19}$$

In the long switching time range, we have  $\ln \tau_{th} < 0$ . Thus,  $(\Delta - \ln \tau_{th})^2 \tau_{th}$  or  $E_{av}$  monotonically raises as the write pulse  $\tau_{th}$  increases and the minimized write energy  $E_{av}$  occurs at  $\tau_{th} = 10$ ns.

In the ultra-short switching time range ( $\tau_{th} < 3 \text{ns}$ ),  $E_{av}$  can be obtained as:

$$E_{av} = \left[ I_{C_0} + C \ln \left( \frac{\pi}{2\theta} \right) \middle/ \tau_{th} \right]^2 R \tau_{th}$$

$$= 2I_{C_0} R C \ln \left( \frac{\pi}{2\theta} \right) + I_{C_0}^2 R \tau_{th} + \frac{C^2 \ln^2 \left( \pi / 2\theta \right) R}{\tau_{th}}$$

$$\geq 2I_{C_0} R C \ln \left( \frac{\pi}{2\theta} \right) + 2 \sqrt{I_{C_0}^2 R^2 C^2 \ln^2 \left( \pi / 2\theta \right)}$$

$$\geq 4I_{C_0} R C \ln \left( \frac{\pi}{2\theta} \right)$$

$$(2.20)$$

As Eq. (2.20) shows, the minimum of  $E_{av}$  can be achieved when  $\tau_{th} = \frac{C \ln(\pi/2\theta)}{I_{C_0}}$ . However, for the ultra-short switching time range (usually  $\frac{C \ln(\pi/2\theta)}{I_{C_0}} > 3$ ns),  $E_{av}$  monotonically decreases as  $\tau_{th}$  increases.

Similarly, in the middle switching time range (3  $\leq \tau_{th} \leq$  10ns),  $E_{av}$  can be expressed as:

$$E_{av} = \left(\frac{P}{\tau_{th}} + Q\right)^{2} R \tau_{th}$$

$$= \left(\frac{P}{\sqrt{\tau_{th}}} + Q\sqrt{\tau_{th}}\right)^{2} R.$$

$$\geq 4PQR \tag{2.21}$$

Again, the minimized  $E_{av}$  occurs at  $\tau_{th} = \frac{P}{Q}$ . Here  $\frac{P}{Q} \ge 10$ ns based on our device parameters characterization [48]. Thus, the write energy  $P_{av}$  in this range monotonically decreases as  $\tau_{th}$  grows.

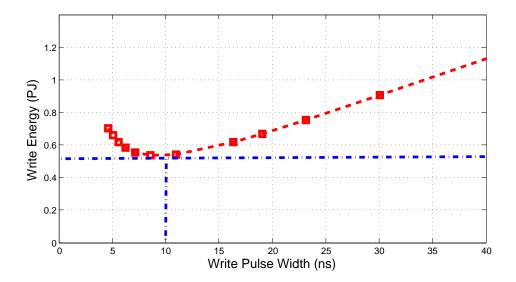

According to the monotonicity of  $E_{av}$  in the three regions, the most energy-efficient switching point of  $E_{av}$  should be at  $\tau_{th} = 10$ ns. To validate above theoretical deduction for the sweet point of  $E_{av}$ , we also conduct the SPICE simulations. Here the STT-RAM device model without considering process and thermal variations is also adopted from [48].

Fig. 15 shows the simulated write energy  $E_{av}$  over different write pulse at '0' $\rightarrow$ '1' switching. As Fig. 15 shows,  $E_{av}$  monotonically decreases in the ultra-short switching range and

Figure 15: Average Write Energy under different write pulse width when T=300K.

Figure 16: Average Write Energy vs write pulse width under different temperature.

continues decreasing in the middle range, but becomes monotonically increasing after entering the long switching time range. The sweet point of  $E_{av}$  occurs around  $\tau_{th} = 10$ ns, which validates our theoretical analysis for the write energy without considering any variations.

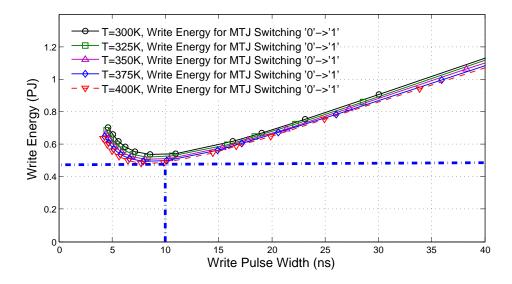

We also present the simulated  $E_{av}$ – $\tau_{th}$  curve under different temperatures in Fig. 16. The trend and sweet point of  $E_{av}$ – $\tau_{th}$  curves remain almost the same when the temperature increases from T=300K to T=400K. In fact, the write energy  $E_{av}$  decreases a little bit as the temperature increases. The reason is that the driving ability loss of the NMOS transistor (I) dominates  $E_{av}$  though the MTJ switching time ( $\tau_{th}$ ) slightly increases when the working temperature raises.

# 2.4.2 PS3-RAM for Statistical Write Energy

As discussed in Section 2.4.1, the write energy of a STT-RAM cell can be deterministically optimized when all the variations are ignored. However, since the switching current I, the resistance R, and the switching time  $\tau_{th}$  in Eq. (2.17) may be distorted by CMOS/MTJ process variations and thermal fluctuations, the deterministic value will not longer be able to represent the statistic nature of the write energy of a STT-RAM cell. Accordingly, the optimized write energy at sweet point ( $\tau_{th} = 10$ ns) shown in Fig. 15 should be expanded as a distribution.

Similar to the write failure analysis in Section 2.3, we conduct the statistical write energy analysis using our PS3-RAM method. We choose the mean of NMOS transistor width W = 540nm. The remained device parameters and variation configurations keep the same as TABLE 1.

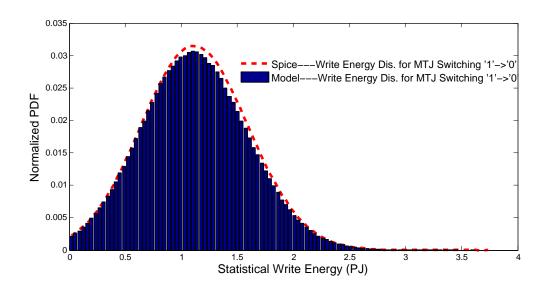

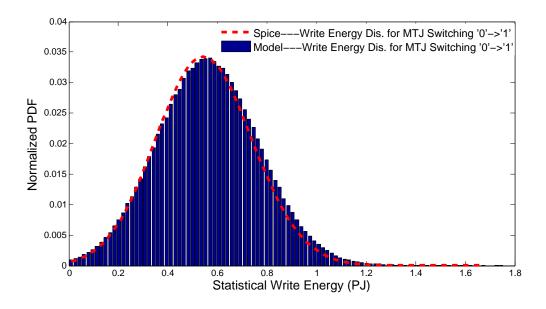

Fig. 17 and 18 show the simulated statistical write energy by PS3-RAM for both switching directions at 300K. For comparison, the SPICE simulation results are also presented. As shown in those two figures, the distribution of write energy captured by our PS3-RAM method are in excellent agreement with the results from SPICE simulations at both '1' $\rightarrow$ '0' and '0' $\rightarrow$ '1' switching's.

Figure 17: Statistical Write Energy vs write pulse width at '1' $\rightarrow$ '0'.

Figure 18: Statistical Write Energy vs write pulse width at '0' $\rightarrow$ '1'.

## 2.5 COMPUTATION COMPLEXITY EVALUATION

We compared the computation complexity of our proposed PS3-RAM method with the conventional simulation method. Suppose the number of variation sources is M, for a statistical analysis of a STT-RAM cell design, the numbers of SPICE simulations required by conventional flow and PS3-RAM are  $N_{std} = N_s^M$  and  $N_{PS3-RAM} = 2KM + 1$ , respectively. Here K denotes the sample numbers for window based smooth filter in sensitivity analysis,  $N_s$  is average sample number of every variation in the Monte-Carlo simulations in conventional method,  $K \ll N_s$ . The speedup  $X_{speedup} \approx \frac{N_s^M}{2KM}$  can be up to multiple orders of magnitude: for example, if we set  $N_s = 100$ , M = 4, (note:  $V_{th}$  is not an independent variable) and K = 50, the speed up is around  $2.5 \times 10^5$ .

## 2.6 APPENDIX

In this appendix, we give the details on the model deduction in sensitivity analysis and the summary of the analytic results involved in the PS3-RAM development. We also present the validation of our analytic results based on Monte-Carlo simulations. TABLE 2 [51] summarizes some additional parameters used in this section.

# 2.6.1 Sensitivity Analysis Model Deduction

The sensitivity analysis model is developed based on the electrical MTJ model and the simplified BSIM model [52, 51]. At '1'→'0' switching, the MTJ switching current supplied by an NMOS transistor working in the triode region is:

$$I = \frac{\beta \cdot \left[ (V_{dd} - V_{th}) (V_{dd} - IR) - \frac{a}{2} (V_{dd} - IR)^2 \right]}{1 + \frac{1}{v_{sat}L} (V_{dd} - IR)}.$$

(2.22)

Here  $\beta = \frac{\mu_0 C_{ox}}{1 + U_0 (V_{dd} - V_{th})} \frac{W}{L}$ . As summarized in Table 2,  $U_0$  is the vertical field mobility reduction coefficient,  $\mu_0$  is electron mobility,  $C_{ox}$  is gate oxide capacitance per unit area, a is body-effect coefficient and  $v_{sat}$  is carrier velocity saturation. The MTJ is in its high resistance state, or  $R = R_H$ .

Table 2: Parameter definition

| Variable  | Definition                                    |  |  |

|-----------|-----------------------------------------------|--|--|

| $U_0$     | Vertical field mobility reduction coefficient |  |  |

| $\mu_0$   | $\mu_0$ Electron mobility                     |  |  |

| $C_{ox}$  | $C_{ox}$ Gate oxide capacitance per unit area |  |  |

| a         | a Body-effect coefficient                     |  |  |

| $v_{sat}$ | Carrier velocity saturation                   |  |  |

Based on PTM [50] and BSIM [51], the partial derivatives in Eq. (2.6) can be calculated by ignoring the minor terms in the expansion of Eq. (2.22) as:

$$\left(\frac{\partial I}{\partial W}\right)_{0}^{2} \approx \frac{1}{\left(A_{1}W + B_{1}\right)^{4}}, \quad \left(\frac{\partial I}{\partial L}\right)_{0}^{2} \approx \frac{1}{\left(\frac{A_{2}}{W} + B_{2}W + C\right)^{2}}, \\

\left(\frac{\partial I}{\partial R}\right)_{0}^{2} \approx \frac{1}{\left(\frac{A_{3}}{W} + B_{3}\right)^{4}}, \quad \left(\frac{\partial I}{\partial V_{th}}\right)_{0}^{2} \approx \frac{1}{\left(\frac{A_{4}}{\sqrt{W}} + B_{4}\sqrt{W}\right)^{4}}.$$

Here,

$$A_{1} = \sqrt{\frac{\mu_{0}C_{ox}V_{dd}(V_{dd} - V_{th})}{L}}R,$$

$$B_{1} = \sqrt{\frac{L}{\mu_{0}C_{ox}V_{dd}(V_{dd} - V_{th})}},$$

$$A_{2} = \frac{L^{2}}{\mu_{0}C_{ox}V_{dd}(V_{dd} - V_{th})},$$

$$B_{2} = R^{2}\mu_{0}C_{ox}\frac{V_{dd} - V_{th}}{V_{dd}},$$

$$A_{3} = \frac{L}{\mu_{0}C_{ox}\sqrt{V_{dd}}(V_{dd} - V_{th})},$$

$$B_{3} = \frac{R}{\sqrt{V_{dd}}}, C = \frac{2LR}{V_{dd}},$$

$$A_{4} = \sqrt{\frac{L}{\mu_{0}C_{ox}V_{dd}}},$$

$$B_{4} = \sqrt{\frac{\mu_{0}C_{ox}}{LV_{dd}}}R(V_{dd} - V_{th}).$$

At '0'---'1' switching, the NMOS transistor is working in the saturation region. The current through the MTJ is:

$$I = \frac{\beta}{2a} \left[ (V_{dd} - IR - V_{th}) - \frac{I}{W C_{ox} v_{sat}^2} \right]^2.$$

(2.23)

The MTJ is in its low resistance state, or  $R = R_L$ . the derivatives can be also calculated as:

$$\left(\frac{\partial I}{\partial W}\right)_{1}^{2} \approx \frac{1}{\left(A_{5}W + B_{5}\right)^{4}}, \quad \left(\frac{\partial I}{\partial L}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{6}}{W} + B_{6}\right)^{2}},$$

$$\left(\frac{\partial I}{\partial R}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{7}}{W} + B_{7}\right)^{4}}, \quad \left(\frac{\partial I}{\partial V_{th}}\right)_{1}^{2} \approx \frac{1}{\left(\frac{A_{8}}{W} + B_{8}\right)^{2}}.$$