# **CONTINUOUS ONLINE MEMORY DIAGNOSTIC**

by

**Musfiq Niaz Rahman**

Bachelor of Science, Bangladesh University of Eng and Tech, 2005 Master of Science, University of Pittsburgh, 2013

Submitted to the Graduate Faculty of

the Kenneth P. Dietrich School of Arts and Sciences in partial

# fulfillment

of the requirements for the degree of

# **Doctor of Philosophy**

in Computer Science

University of Pittsburgh 2016

# UNIVERSITY OF PITTSBURGH

# KENNETH P. DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Musfiq Niaz Rahman

It was defended on

December 8th 2016

and approved by

Dr. Bruce R. Childers, Dietrich School of Arts and Sciences

Dr. Rami Melhem, Dietrich School of Arts and Sciences

Dr. Wonsun Ahn, Dietrich School of Arts and Sciences

Dr. Kartik Mohanram, Swanson School of Engineering

Dissertation Director: Dr. Bruce R. Childers, Dietrich School of Arts and Sciences

Copyright © by Musfiq Niaz Rahman 2016

#### **CONTINUOUS ONLINE MEMORY DIAGNOSTIC**

Musfiq Niaz Rahman, PhD

University of Pittsburgh, 2016

Today's computers have gigabytes of main memory due to improved DRAM density. As density increases, smaller bit cells become more susceptible to errors. With an increase in error susceptibility, the need for memory resiliency also increases. Self-testing of memory health can proactively check for errors to improve resiliency. Developing a memory diagnostic is challenging due to requirements for transparency, scalability and low performance overheads. In my thesis, I developed a software-only self-test to continuously test memory. I present the challenges and the design for two approaches, called COMeT and Asteroid, that are built on a common software framework for memory diagnostic and target chip multiprocessors. COMeT tests memory health simultaneously with single-threaded and multi-threaded application execution in anticipation of memory allocation requests. The approach guarantees that memory is tested within a fixed time interval to limit exposure to lurking errors. On the SPEC CPU2006 and the PARSEC benchmarks, COMeT has a low 4% average performance overhead.

Despite the promising results, COMeT showed poor scalability on multi-programmed workload environment with high memory pressure. I developed another novel approach, Asteroid, which can adapt at runtime to workload behavior and resource availability to maximize test quality while reducing performance overhead. Asteroid is designed to support control policies to dynamically configure a diagnostic. Asteroid is seamlessly integrated with a hierarchical memory allocator in modern operating systems and is optimized to achieve higher memory test speed than COMeT. Using an adaptive policy, in a 16-core server, Asteroid has modest overhead of 1% to 4% for workloads with low to high memory demand. For these workloads, Asteroid's adaptive policy shows good error coverage and can thoroughly test memory. Thorough evaluation of my techniques provides experimental justification that a transparent and online software-based strategy for memory diagnostic can be achievable by utilizing over-provisioned system resources.

# TABLE OF CONTENTS

| PRI | EFAC | <b>E</b>                                           |

|-----|------|----------------------------------------------------|

| 1.0 | INT  | <b>RODUCTION</b>                                   |

|     | 1.1  | Requirements of a Good Solution                    |

|     | 1.2  | Challenges                                         |

|     | 1.3  | Research Overview                                  |

|     | 1.4  | Contributions                                      |

|     | 1.5  | Thesis Organization                                |

| 2.0 | BAC  | <b>CKGROUND AND RELATED WORK</b> 8                 |

|     | 2.1  | Traditional Memory Testers                         |

|     | 2.2  | Memory Error Detection and Correction              |

|     | 2.3  | OS Memory Management                               |

|     |      | 2.3.1 Application <i>malloc()</i>                  |

|     |      | 2.3.2 Kernel Memory Management                     |

|     | 2.4  | OS Scalability Issues                              |

|     | 2.5  | Related Work                                       |

| 3.0 | ON   | LINE MEMORY DIAGNOSTICS                            |

|     | 3.1  | Observations Influencing Online Memory Diagnostics |

|     | 3.2  | My Approach For Online Memory Diagnostic           |

|     |      | 3.2.1 Operation                                    |

|     |      | 3.2.2 Test Guarantee and Replenishment             |

|     | 3.3 | Assun                | nptions                                  | 22 |

|-----|-----|----------------------|------------------------------------------|----|

|     | 3.4 | Frame                | work for Online Memory Diagnostic        | 23 |

| 4.0 | ONI | L <mark>INE</mark> N | IEMORY DIAGNOSTIC IN SMALL-SCALE SYSTEMS | 27 |

|     | 4.1 | Archit               | tecture                                  | 28 |

|     |     | 4.1.1                | Allocation Monitor                       | 29 |

|     |     | 4.1.2                | Guarantee Timer and Handler              | 30 |

|     |     | 4.1.3                | Global Allocation Timer and Handler      | 31 |

|     |     | 4.1.4                | Global Tester                            | 32 |

|     |     | 4.1.5                | Adaptive Test Rate                       | 33 |

|     |     | 4.1.6                | Page Migration                           | 36 |

|     | 4.2 | Evalua               | ation                                    | 37 |

|     |     | 4.2.1                | Methodology                              | 39 |

|     |     | 4.2.2                | Overall Results                          | 40 |

|     |     | 4.2.3                | Configuration                            | 44 |

|     |     | 4.2.4                | Test Guarantee and Replenishment         | 46 |

|     |     | 4.2.5                | Overload Behavior                        | 48 |

|     |     | 4.2.6                | Sensitivity to Test Latency              | 49 |

|     |     | 4.2.7                | Multi-threaded Workload                  | 50 |

| 5.0 | ONI | LINE N               | MEMORY DIAGNOSTIC IN LARGE-SCALE SYSTEMS | 55 |

|     | 5.1 | Astero               | bid                                      | 58 |

|     | 5.2 | Comp                 | onents of Asteroid                       | 59 |

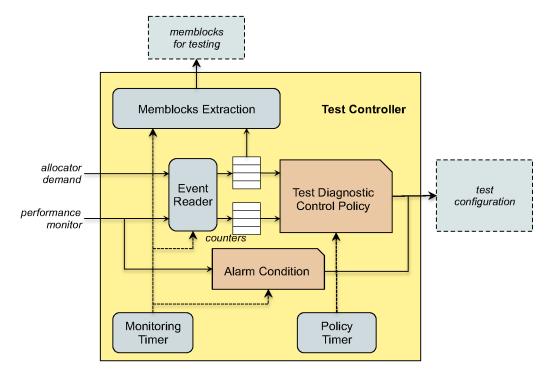

|     |     | 5.2.1                | Test Controller (TC)                     | 60 |

|     |     | 5.2.2                | Test Dispatcher (TD)                     | 61 |

|     |     | 5.2.3                | Concurrent Tester Threads (CTT)          | 61 |

|     |     |                      | 5.2.3.1 Core-local on-demand test        | 62 |

|     |     |                      | 5.2.3.2 Page cache recycling             | 63 |

|     |     |                      | 5.2.3.3 Skip middle-ranked blocks        | 64 |

|     |     |                      | 5.2.3.4 Cache indirect test              | 64 |

|     |      | 5.2.4   | Test Controller and Diagnostic Control Policy | 65 |

|-----|------|---------|-----------------------------------------------|----|

|     |      |         | 5.2.4.1 Operation                             | 66 |

|     |      |         | 5.2.4.2 Determining Memory Blocks to Test     | 66 |

|     |      |         | 5.2.4.3 Determining Test Configuration        | 67 |

|     |      |         | 5.2.4.4 Fixed Policy                          | 70 |

|     |      |         | 5.2.4.5 Adaptive Policy                       | 71 |

|     | 5.3  | Experi  | mental Evaluation                             | 73 |

|     |      | 5.3.1   | Methodology                                   | 73 |

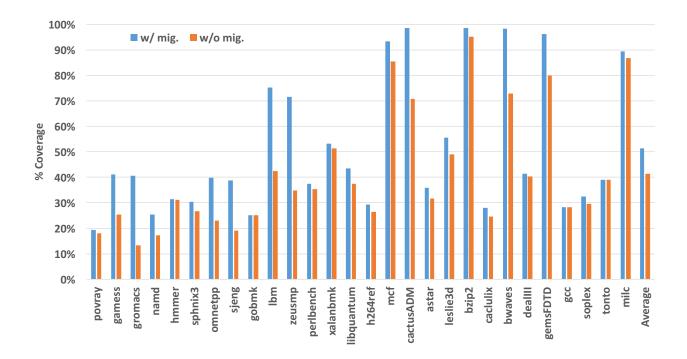

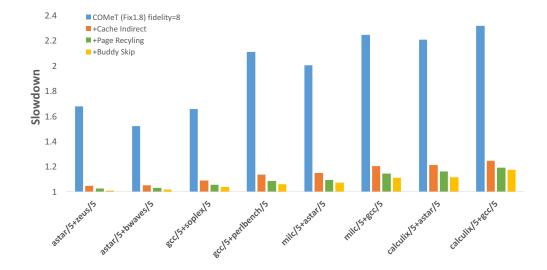

|     |      | 5.3.2   | Effect of Optimizations                       | 75 |

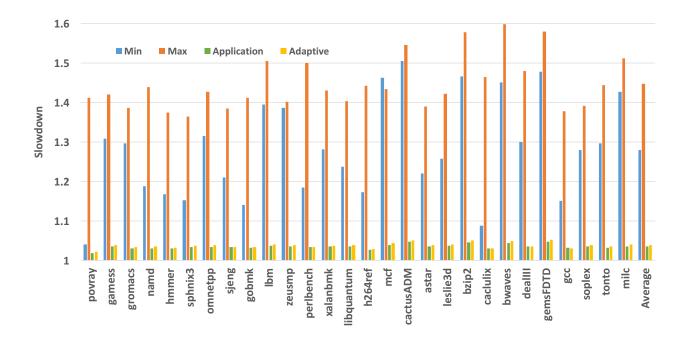

|     |      | 5.3.3   | Fixed Configuration                           | 77 |

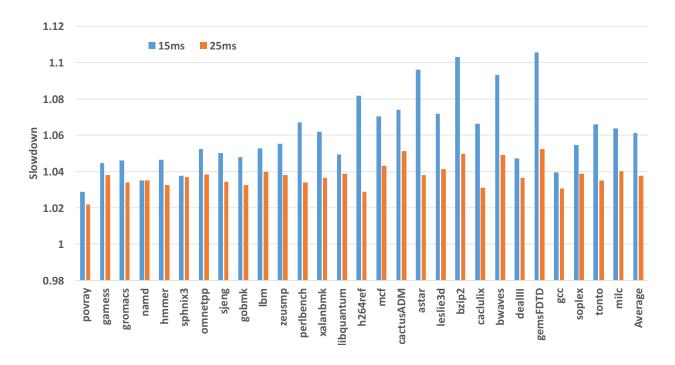

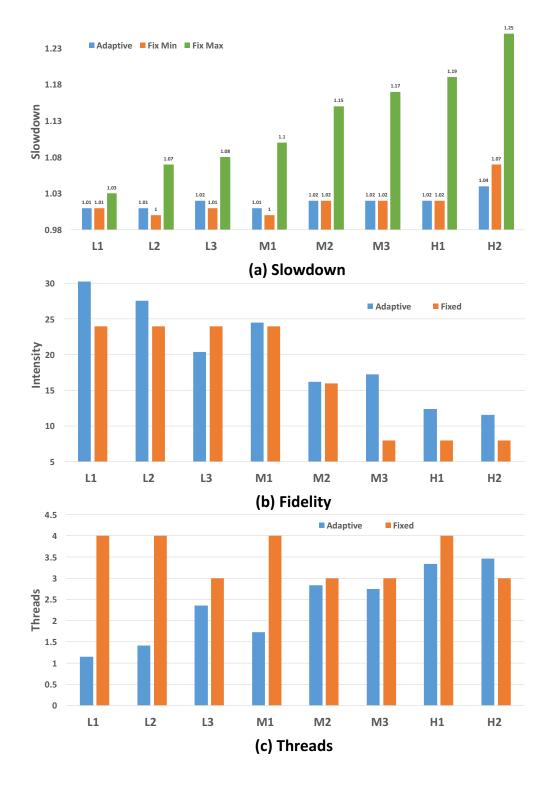

|     |      | 5.3.4   | Adaptive Configuration                        | 79 |

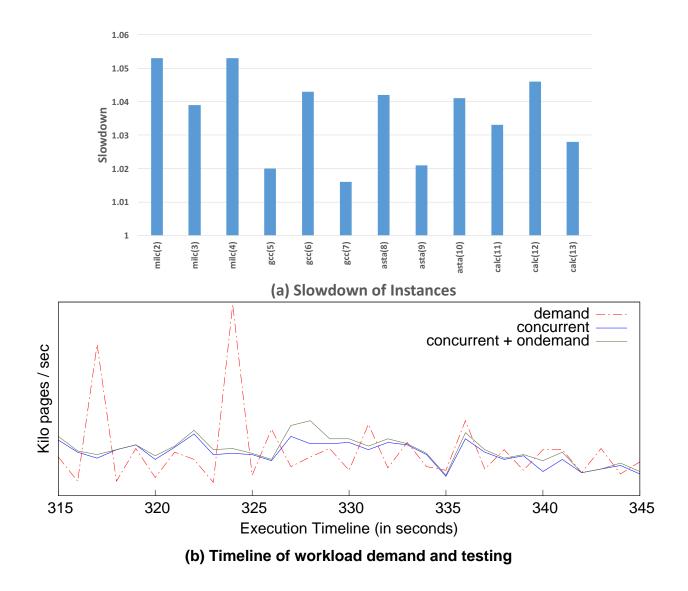

|     |      | 5.3.5   | Underlying Behavior                           | 81 |

| 6.0 | CON  | ICLUS   | ION AND FUTURE WORK                           | 85 |

|     | 6.1  | Summ    | ary of Contributions                          | 86 |

|     | 6.2  | Future  | Work                                          | 87 |

| AP  | PEND | IX A. I | NOTES ON IMPLEMENTATION                       | 89 |

|     | A.1  | Core K  | Kernel Modifications                          | 89 |

|     |      | A.1.1   | More out of Buddy System                      | 90 |

|     |      | A.1.2   | Per-CPU Page-Cache (PCP)                      | 90 |

|     |      | A.1.3   | Statistics Counters                           | 91 |

|     | A.2  | Kernel  | Module of the framework                       | 91 |

|     |      | A.2.1   | Administrator Control Knobs                   | 92 |

|     |      | A.2.2   | Testing a Page                                | 92 |

|     |      | A.2.3   | Page Timestamps                               | 92 |

|     |      | A.2.4   | Making a Page Uncachable                      | 93 |

|     |      | A.2.5   | Page Migration                                | 93 |

|     |      | A.2.6   | TLB Shootdowns                                | 94 |

| AP  | PEND | IX B. I | DEBUGGING AND TOOLS                           | 95 |

| BIBLIO      | GRAPHY                                 | 97 |

|-------------|----------------------------------------|----|

| B.3         | Miscellaneous Tools                    | 96 |

| B.2         | Using Vim Code Navigator and Callgraph | 95 |

| <b>B</b> .1 | Kernel Debugging                       | 95 |

# LIST OF TABLES

| 1 | Configuration                                                             | 37 |

|---|---------------------------------------------------------------------------|----|

| 2 | Experimental setting                                                      | 38 |

| 3 | SPEC CPU2006 Benchmark Statistics (table is sorted by memory utilization) | 38 |

| 4 | Energy consumption                                                        | 43 |

| 5 | Slowdown or Out-of-Memory (OOM) under overload                            | 49 |

| 6 | Test Controller and Diagnostic Control Policy Parameters                  | 70 |

| 7 | Workload Mixes.                                                           | 74 |

| 8 | Slowdown for Adaptive and Fix: Fidelity 8 and 16                          | 77 |

| 9 | Slowdown for Adaptive and Fix: Fidelity 24 and 32                         | 78 |

# LIST OF FIGURES

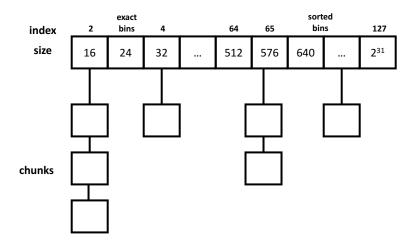

| 1  | Objects of the same size grouped into bins                                  | 12 |

|----|-----------------------------------------------------------------------------|----|

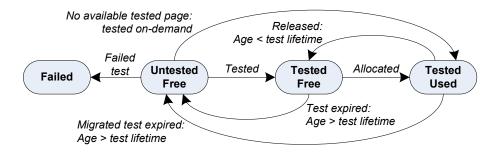

| 2  | Page State Diagram                                                          | 19 |

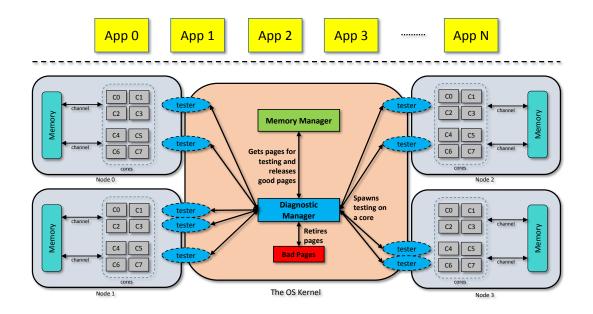

| 3  | High-Level Design of COMeT                                                  | 24 |

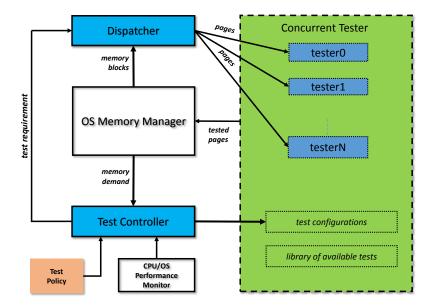

| 4  | Framework Components                                                        | 25 |

| 5  | Design of COMeT                                                             | 28 |

| 6  | Check expiration of <i>tested used</i> pages                                | 30 |

| 7  | Handler for global allocation timer                                         | 31 |

| 8  | Tester for global allocation                                                | 33 |

| 9  | State Transition during Test Rate Change                                    | 34 |

| 10 | Adjust buddy order's replenishment rate                                     | 35 |

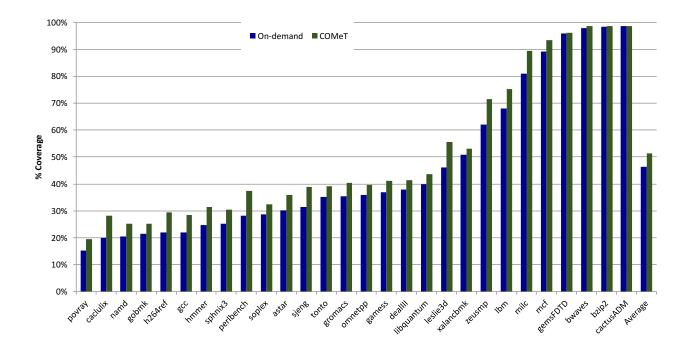

| 11 | Page coverage (percentage of physical pages tested)                         | 40 |

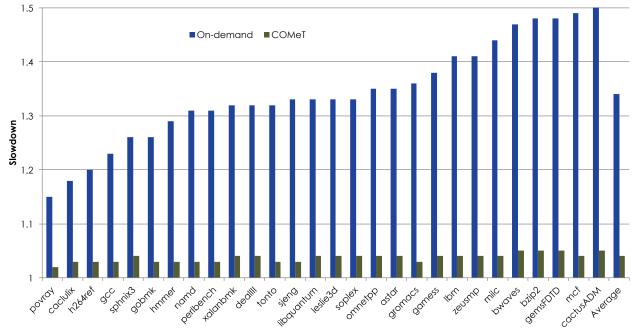

| 12 | Slowdown relative to baseline without testing.                              | 41 |

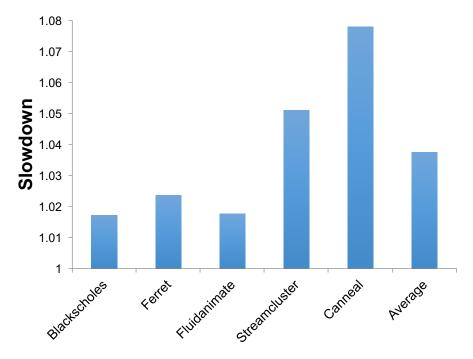

| 13 | Slowdown relative to baseline without testing on selected PARSEC benchmarks | 43 |

| 14 | Effect of $replenish-\delta$                                                | 46 |

| 15 | Page coverage due to migration                                              | 47 |

| 16 | Effect of replenishment rates                                               | 48 |

| 17 | Sensitivity to test latency                                                 | 50 |

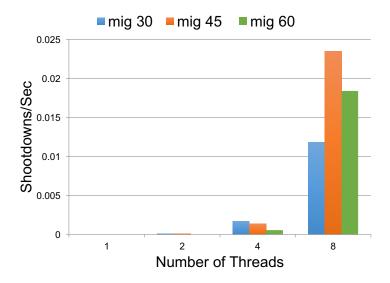

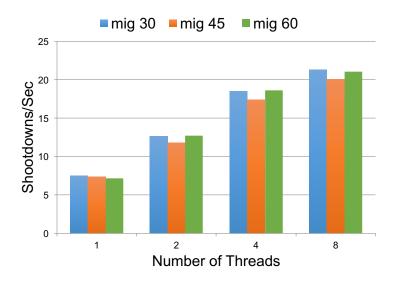

| 18 | Slowdown on Multi-threaded Benchmarks: Canneal                              | 51 |

| 19 | Slowdown on Multi-threaded Benchmarks: Streamcluster                        | 51 |

| 20 | Slowdown on Multi-threaded Benchmarks: <i>Ferret</i>                        | 52 |

| 21 | Rate of TLB shootdowns on Multi-threaded Benchmarks: Canneal                       | 52 |

|----|------------------------------------------------------------------------------------|----|

| 22 | Rate of TLB shootdowns on Multi-threaded Benchmarks: Streamcluster                 | 53 |

| 23 | Rate of TLB shootdowns on Multi-threaded Benchmarks: Ferret                        | 53 |

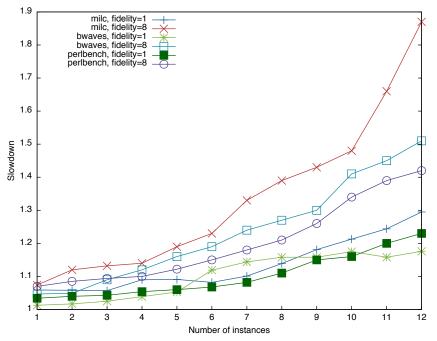

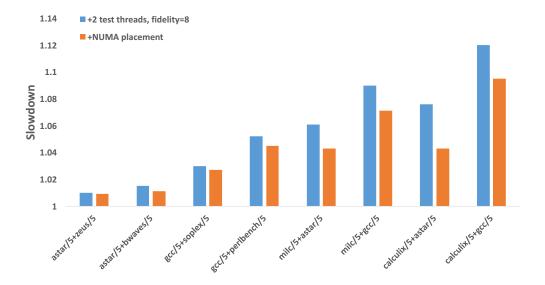

| 24 | COMeT slowdown on selected multi-instance SPEC CPU2006 workloads                   | 55 |

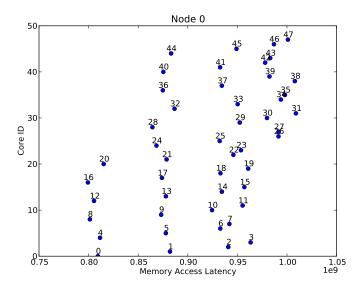

| 25 | Memory Access Latency in NUMA                                                      | 57 |

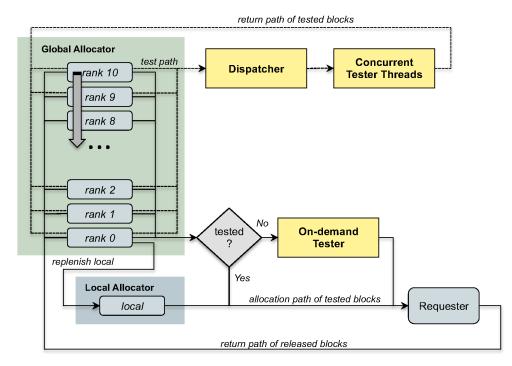

| 26 | Asteroid memory diagnostic framework                                               | 59 |

| 27 | Paths for tested pages (dashed line) and requested pages (solid line)              | 62 |

| 28 | Example MARCH test using cache indirect testing with one pattern                   | 65 |

| 29 | Software architecture and information flow for TC                                  | 66 |

| 30 | Adaptive policy to find test configuration                                         | 71 |

| 31 | Impact of cache indirect testing, page recycling and skipping middle ranks for CTT | 75 |

| 32 | Impact of node local dispatch by TD                                                | 76 |

| 33 | Comparison of performance, fidelity and threads for Adaptive and Fix               | 80 |

| 34 | Slowdown of individual benchmark instances in H2 workload                          | 82 |

# PREFACE

I like to dedicate my dissertation to my parents (Mizanur Rahman and Zeenat Jahan Begum), my wife (Meher Nigar) and my son (Shayan Rahman). Without their encouragement and support, none of this would be possible. I like to thank my committee for their valuable feedback to mature the work done in my dissertation. I am thankful to the Computer Science Department for all the help I received during my research. Finally, I am very thankful to my advisor (Dr. Bruce R. Childers) for his enormous support and feedback throughout my research. My dissertation is based upon work supported by the National Science Foundation under grant numbers CCF-1422331 and CNS-1012070.

#### **1.0 INTRODUCTION**

Due to a good balance of cost, power, performance and density, DRAM has long been used for main memory. With technology scaling, however, evidence is mounting that reliable operation is becoming a significant challenge for DRAM. Microsoft, Google, AMD and others have found indications that transient and permanent multi-bit errors are prevalent in DRAM [8, 38, 50, 66, 71]. At increasingly small device scales and operating voltages, it is probable that these errors will become even more common at technology node sizes below 22*nm*. Hence, there is a growing need for new resiliency techniques to mitigate memory errors.

A *memory diagnostic* is a resiliency technique that can play a valuable role in error mitigation for memory: A diagnostic exercises memory under varying scenarios to expose marginal locations. A diagnostic's strength is it can exercise memory in *many* ways to expose errors that only manifest themselves in specific conditions. Memory diagnostics are complementary to error mitigation; a diagnostic provides information to guide mitigation. They can be used to assist in online repair and recovery, forestall memory replacement, and direct error correction. For example, page retirement is used in Solaris and Linux to implement error avoidance of "bad" memory locations. It has also been proposed for managing failed memory pages in emerging technologies, such as phase-change memory [22].

When an error is discovered, the physical page frame containing the error is quarantined to avoid future use. A diagnostic could indicate the pages to retire as a triage measure to hold off on replacing a DRAM DIMM until an operator can access the machine. Similarly, diagnostic results can guide error correction. For example, ArchShield is a strong error correction scheme for future memory technologies with high rates of transient and permanent errors [49]. It uses a memory

diagnostic to build a fault map of locations that need extra redundancy for repair. Error correction (ECC) can also guide the diagnostic: When ECC is triggered with a relatively high frequency (i.e., to correct a bit error with a single-error-correction, double-error-detection, SECDED, code) for some region of memory, a diagnostic can be run to more thoroughly test the memory, particularly to check whether the memory is actively failing (i.e., possibility of multi-bit errors that cannot be corrected).

While memory diagnostics extract useful information, they tend to consume significant resources (e.g., bandwidth) and require unfettered access to physical memory. A diagnostic performs write, read and compare operations with test bit patterns in multiple sweeps through the memory. The process is inherently memory bound and time consuming, particularly for the most advanced diagnostics that apply several bit patterns in many sweeps. Consequently, most memory diagnostics are done offline when the system is not actively serving a workload, such as during boot-up [4] or periods of low utilization (e.g., overnight) [65]. However, with server consolidation keeping machines busier and the growing error rates, there is a need for *online* diagnostics that operate while the system does actual work. Of course, a memory failure can happen at any moment, and an online diagnostic will be more responsive than an offline one.

Contemporary computing systems are equipped with a number of processing cores and large main memory capacity to execute a wide range of applications. Over the past few decades applications have become diverse in CPU, memory and IO usage. Therefore, system designers often over-provision system resources to handle workload variations. This over-provisioning provides an opportunity to use under-utilized system resources to perform various system diagnostics that protect the system from potential failures before they take place. One over-provisioned resource is idle processor cycles. These idle cycles can be utilized to test the system memory for errors and thereby minimizing the vulnerability of the system to an error. The primary goal of a memory diagnostic is to increase resiliency for many application types and, hence, it needs to handle and scale for multi-programmed and multi-threaded workloads with similar efficiency. *In this research, my hypothesis is a diagnostic can be integrated into the live OS so that over-provisioned system resources are utilized to make the system more reliable to the user.*

#### 1.1 REQUIREMENTS OF A GOOD SOLUTION

To help address memory resiliency, in this research I designed and developed an online memory diagnostic inspired by conventional standalone memory testers (e.g., Memtest86+ [4] and PC BIOS Power-on Self Test). These conventional approaches usually operate in a non-transparent and offline setting. To make an online diagnostic a good solution, four requirements should be maintained in it.

The first requirement of a good solution to designing and developing this diagnostic is to check memory health online in a system. Because memory can fail at any time, a solution should aim to check memory health in a deployed system, as it is actively serving a workload. Indeed, the actual conditions, e.g., temperature, age and utilization under which the system is operated can influence the appearance of errors and failure. An online test will check the health in an actual operating context, similar to a wearable heart rate or blood sugar monitor.

The second requirement is the diagnostic must minimize its impact on performance of the system. Due to memory access latency and using processor cycles to access memory, a software-based diagnostic can pose considerable impact on system performance. Given these constraints, the diagnostic aims to maximize test rate and thoroughness.

The third requirement is that the diagnostic must be transparent to applications and the OS. Changes in the OS need to be minimized so that the diagnostic does not hamper original OS functionalities. At the same time, applications must be kept unchanged. This requirement also ensures that the diagnostic will become a good candidate for a quick adoption by the user community.

The last requirement is to test memory constantly and thoroughly in a way that stresses the memory to expose marginal behavior, which may or may not actually manifest itself during application execution. A good solution ensures that the test includes the entire memory subsystem and guarantees that memory health is regularly checked. Failures can happen in many places of the memory system, ranging from the memory controller, to the interconnect, to the DIMMs, and individual chips. Even with error correction and scrubbing techniques, marginally faulty locations can behave in a way that is not covered by the error correction. For example, SECDED is com-

monly used to protect the memory chips. However, this code can only correct a single bit error, but multi-bit errors are possible. The aim is to test the memory for marginality; it is not to provide fault tolerance. By proactively testing the memory, resiliency can be improved.

#### **1.2 CHALLENGES**

To meet the requirements for a good solution to a memory diagnostic, five challenges must be addressed. These challenges influence various aspects of my diagnostic approach such as its design, operation, and implementation. The challenges are described below.

The first challenge lies in developing a testing strategy. Memory pages can be tested ahead of time of allocation concurrently with running applications or they can be tested on-demand at the time of a page allocation request. Another strategy can be designed that combines these two possibilities. These strategies will have different impacts on performance degradation of the system.

The second challenge is deriving test parameters for my memory diagnostic. There are a number of parameters (e.g., test rate, page expiration time, etc.) that influence testing. During runtime, the diagnostic needs to set and dynamically adjust values for these parameters to ensure performance efficiency and provide a guarantee that memory health is regularly checked.

The third challenge is scaling the diagnostic to large systems. The diagnostic needs to handle multi-threaded and multi-programmed workloads and increasing number of CPUs and memory capacity. It must test large memory capacity in large systems with similar efficiency as small systems.

The fourth challenge is meeting performance constraints. Given a performance budget, the diagnostic should maximize test rate and guarantee a regular health check of the entire memory.

The final challenge is the implementation of the diagnostic. It will be highly dependent on the OS memory management which is a complex piece of software. So, the implementation needs to be carefully crafted and integrated so that the functionalities and subtleties of the OS design and

implementation are not adversely disturbed. Further, the implementation should aim to localize any OS changes, given the complex, monolithic structure of most modern OSes.

#### **1.3 RESEARCH OVERVIEW**

In my dissertation, I developed Continuous Online Memory Testing (COMeT), a software framework that can be used to create online memory diagnostic to perform error diagnosis on physical memory. This diagnostic can sweep through memory at regular intervals with a MARCH test [76, 80]. A MARCH test writes specific bit patterns on physical locations of memory, reads them back, and verifies the correctness of the values to determine marginal erroneous locations. Typically, a more thorough test with many bit patterns can discover more lurking error conditions including unusual but possible ones. Memory pages with detected errors can be retired, scrubbed or possibly salvaged for small kernel buffers [77]. By avoiding pages with errors, especially ones with errors that are uncorrectable by hardware mechanisms (e.g., multi-bit errors for SECDED), reliability is improved. COMeT exercises the entire memory system, including the memory controller(s), memory interconnect, DIMMs, and associated glue logic.

The implementation of COMeT retrofits the OS memory manager with a memory diagnostic capability. COMeT consists of a test controller and tester threads. The test controller works as an intermediary between the memory manager and the memory tester threads. It is designed to be adaptive to memory pressure in the system. A tester thread is responsible for executing MARCH tests on a given memory page. A set of testers can be executed per node which consists of a number of cores and memory. When testing is finished, the tester thread returns fault-free pages to the memory manager. A bad memory page is marked unusable and isolated from the OS by the test controller. COMeT is highly configurable by system administrator who can set resource limitation for COMeT. The design of COMeT aims to minimize the performance impact by fairly distributing testing tasks among tester threads depending on their processing capacity and current load while

staying within the resource limit. In addition, COMeT provides functionalities to thoroughly evaluate diagnostic efficiency and performance impact on the system where it is deployed.

## **1.4 CONTRIBUTIONS**

My dissertation makes a number of contributions to the challenges of online memory diagnostic.

First, I presented the design of a software-only process to continuously test main memory's health while the system is up and running. I developed techniques to test memory ahead-of-allocation in a CMP and adaptively adjust test rate to minimize overhead, while achieving a guaranteed bound on the maximum time between successive tests of a page.

Second, I demonstrated a number of parameters which can be used to control an online testing behavior effectively. I provided in-depth guidance to system administrators on proper setting of these parameters based on their target system of deployment.

Third, I developed new algorithms which work with OS memory management to permit the diagnostic and memory management to work in harmony. These algorithms show how to integrate different test parameters to achieve a maximum memory test rate.

Fourth, I addressed COMeT's scalability issues through a set of a novel techniques in Asteroid. Using numerous experiments, I showed how Asteroid can scale a memory diagnostic on multiprogrammed workload with a wide range of memory demands. My techniques also addressed non-uniform memory access while testing in large multi-core systems.

Fifth, I showed a number of interesting optimization techniques which can be crucial to meet the given performance budget of any software-based online diagnostic. Some of these optimization techniques also provide helpful insight into OS memory allocation and access pattern in general.

Sixth, I evaluated performance, energy, and resiliency of COMeT to memory errors, including an analysis of important design and configuration choices. Additionally, I showed COMeT's effectiveness to reduce system downtime by proactively isolating bad memory pages. Finally, I provided a description of how COMeT can be structured and integrated with an OS kernel. This description can be used as a reference for the OS developer community with ideas and subtle design issues on memory diagnostic in the OS.

#### 1.5 THESIS ORGANIZATION

Rest of my dissertation is organized into four chapters. In Chapter 2, motivation and background of my work are described. Relevant works by other researchers on memory diagnostics are also mentioned in this chapter. Chapter 3 introduces my diagnostic framework and provides a high-level overview of components of the framework. Chapter 4 presents COMeT which is a memory diagnostic based on my framework for small-scale systems. COMeT's effectiveness, evaluation and limitations are discussed in detail in this chapter. The corresponding work is published in [56–58]. Asteroid is presented in Chapter 5 which provides an in depth discussion on my novel techniques to eliminate scalability limitations of COMeT in large-scale systems. This chapter also presents a number of interesting optimization techniques in Asteroid to achieve higher test speed than COMeT. The corresponding work is published in [54, 55]. In conclusion, Chapter 6 summarizes the work and contributions of my dissertation and highlights potential future work.

#### 2.0 BACKGROUND AND RELATED WORK

For several decades, DRAM has been the best choice for main memory due to its relatively low cost, aggressive scalability, low power and good performance. Continued decreases in bit cell size have led to large main memories–a laptop can be purchased with several gigabytes of memory, while a server can easily have tens of gigabytes. The capacity enabled by DRAM has had a direct consequence on the applications, execution models and processors employed today. While the relentless scaling of DRAM has been a key enabler, it also has a down side. As cell size and operating voltage are decreased, the memory becomes more susceptible to errors [10, 40, 78]. Background radiation may lead to more "single event upsets" (i.e., independent random bit flips) in a small cell size. Other error types, such as interdependent multi-bit transient and hard errors, are also possible, and indeed probable, at the extreme scales used in high-density DRAM [8, 71]. With new materials, smaller device geometry and increased process variations, these error types may become as important as single event upsets, particularly at operating margins [15, 34, 36, 72]. A program will be corrupted only if a memory location with an error is accessed and the "bad value" is propagated to sensitive state [36, 37, 47, 48].

A two and half year study of reliability in Google's data centers revealed that nearly one third of their machines and 8% of memory modules—using today's memory technology—experienced at least one memory error [66]. The study suggested that the errors were inter-related, and thus, unlikely caused by independent bit flips. This result is even more surprising given that memory with uncorrectable errors was quickly replaced. Further, in another study [50] by researchers from Microsoft analyzed Windows crash reports collected from thousands of consumer PCs to discover the dominant causes of failure. Consumer PCs usually lack the support for error handling (e.g., ECC). Their study revealed that DRAM error is one of the three major causes of crash and these errors are recurrent. Their error statistics is collected over only about 1.5% of the average memory capacity across several thousands of consumer PCs. Hence, they suspected that the number of DRAM errors in the entire memory is much worse. They also observed a positive correlation between CPU speed and DRAM errors due to the package temperature. While the CPU speed continues to increase, the package temperature will promote more DRAM errors in future. An overarching conclusion of both of these studies was resiliency techniques are necessary to successfully manage memory reliability.

Two very recent large scale studies [8, 71] have revealed a further interesting trend in DRAM faults. Authors in [71] made two important conclusions. First, SECDED ECC is poorly suited to modern DRAM subsystems and the rate of undetected errors is too high to justify the use of SECDEC ECC in very large scale systems. Second, the choice of DRAM vendor is an important consideration for system reliability. In [8], the authors found that correcting codes optimized for adjacent bit errors are less effective. They also noticed that the number of multi-bit corruptions between 7am and 6pm is double the number of multi-bit corruptions during the night. Their conclusion is that the evidence of SDC occurring in an isolated and independent fashion, making it extremely hard to detect and/or predict. Without proper diagnostic, these errors will have significant adverse impact on system by causing crash and silent data corruption. Memory diagnostic techniques will become vital as DRAM node size is further decreased.

While these studies strongly motivate my work, they do not propose a specific technique to combat errors that occur in DRAM chips. Numerous studies have investigated mechanisms for error diagnosis and recovery [36, 37, 64], checkpointing and rollback [52, 70], detection and repair of bugs [18, 25, 51, 53, 59, 63], software fault tolerance [46, 60, 62, 82] and online self test [26, 39]. Many of these methods, including SWAT [36, 64], SWIFT [61], core self testing [26, 39] and duplicated threads [60, 82], rely on free resources (cores, functional units, etc.). However, these approaches target the processor rather than main memory with added hardware support, application modification, compiler support, and/or replicated state.

#### 2.1 TRADITIONAL MEMORY TESTERS

Traditional testers (e.g., Memtest86+ [4], POST by BIOS, etc.) repeatedly execute write, read and verify operations on physical memory locations. Different bit patterns are written and read back to check for the potential and presence of various error types, including multi-bit errors. The advantage to these techniques is they can stress memory with many patterns to find marginal locations that have errors only in particular situations. Memory testers are used during manufacture, boot up, or machine malfunction (for diagnosis). They are not designed to determine memory health in a live system. Because the testers sweep through the whole memory, they can have large test latency. During manufacture, test time is expensive and may be done for only a short burn-in period [14]. Similarly, it can take a long time to thoroughly test memory during the boot process.

## 2.2 MEMORY ERROR DETECTION AND CORRECTION

Computer memories are often protected by some form of parity-check code. In a parity-check code, information symbols within a word are processed to generate check symbols. These two symbols together form the coded word which is called ECC (error correcting code). Given the fact that soft errors and hard errors are prevalent in DRAMs, ECC has been used to detect and correct such errors in server computers. Most memory controllers use Single Error Correction Double Error Detection (SECDED) ECC because of its low overhead and easy implementation. ECC uses Hamming codes to encode memory bits and Hamming distance to distinguish between valid and invalid Hamming codes. SECDED uses a combination of SEC Hamming code and parity checking where parity checking augments Hamming code to provide double-bit error detection.

For main memory, the most viable hardware approach relies on embedding some form of information redundancy in DRAM. Such redundancy provides a check on data integrity and/or a capability to restore the original data on detecting an error(s). For example, the most popular DRAM protection practice employs error correction codes (ECC) at the DRAM module level. A typical ECC is capable of correcting a single-bit error and detecting two errors in a single error correction unit (typically 64 bits), commonly referred to as SECDED. Other schemes [21, 83] distribute memory content (and redundancy) across different chips (or different DIMMs) to provide stronger protection against multiple bit errors. For example, IBM's chipkill [21] can scatter memory bits in a single ECC unit to multiple chips. A smart "virtualized" embodiment of the ECC scheme [81] was recently proposed to decouple the actual ECC from the data in memory and separate the process of detecting errors from the rare need to also correct errors (to save energy). Similar "smart" encoding schemes have been applied to caches [7, 28, 29]. Other encoding schemes have also been proposed to reduce bit-flips in DRAM [67] and in emerging non-volatile memory technologies, e.g., phase-change-memory [42–44, 68].

### 2.3 OS MEMORY MANAGEMENT

The memory diagnostic in a live system must work closely with the OS memory management. The diagnostic will depend on the OS memory manager to collect memory pages for testing. The fundamental concept on how applications and the OS kernel manages their memory is briefly described below.

#### **2.3.1** Application malloc()

*malloc()* is a function for efficient management of dynamic objects in memory. During execution of a process, different objects sizes in memory need to be allocated and released. Without proper management, memory allocation becomes slow, dynamic memory becomes fragmented and memory utilization drops. Further, dynamically allocated memory in Symmetric Multiprocessors (SMPs) can lead to performance degradation due to false sharing of cache lines among threads of a process running on separate cores or processors [9, 35]. Depending on these performance factors (e.g.,

Figure 1: Objects of the same size grouped into bins

speed, memory fragmentation and locality, cache utilization etc.) on various hardware platforms, different variants of *malloc()* have been developed. Fundamentally these implementations create a cache of pre-allocated objects in a memory area called 'heap' in the process address space. These objects are grouped together based on their sizes in the heap. Figure 1 shows a cache with size groups called 'bins'. Each bin contains a list of free objects of corresponding size. Inside a bin, two neighboring free objects might be coalesced to form a free object of larger size and moved to corresponding bin at a higher index. This design was proposed by Doug Lea [33] and used in the GNU C Library. During allocation, objects are taken out of 'smallest-first' object-size bin that 'best-fits' the size of allocation and handed to the requesting process. On release, free objects are put back to the specific-sized bin they belong to. The heap can be extended using the *sbrk()* system call in case a process requires more objects than can fit in the heap capacity. For requests larger than 32 pages, *malloc()* employs *mmap()* to allocate a corresponding number of virtual pages from the OS [35].

#### 2.3.2 Kernel Memory Management

The Linux kernel handles its free memory in two techniques. In the first technique, the kernel uses "Buddy System" to keep track of its free memory pages [20, 41, 45]. Memory allocation is partitioned among global and per-CPU page frame cache (PCP) allocators. Each allocator has free lists that hold blocks of contiguous unused pages. The global allocator uses buddy lists, where a free list is an *order* of rank *i* that holds free blocks of size  $2^i$ , where  $0 \le i \le 10$ . Modification to buddy blocks during memory allocation and release is done using the *Buddy Algorithm* [32]. For PCP allocation, there are separate free lists (hot and cold) for each core, which locally cache free blocks of size one page. The allocators have separate free lists for different memory zones (DMA, normal and high). Allocation is hierarchical: the PCP allocator is tried first. If this fails, then the global allocator is tried.

The second technique is called "Slab Allocator" [12] which is essentially another implementation of *malloc()*. Each slab in a slab allocator acts as a bin. The slab allocator has all the advantages of application-level *malloc()*. Additionally, to improve cache utilization, the slab allocator uses object coloring to pack objects in a slab at different starting addresses. It reduces the probability that objects from the same slab are stored at the same location in the cache and conflict.

A memory diagnostic must work co-operatively with memory management functionalities provided by the OS. There are several ways a memory diagnostic can be implemented. For example, a diagnostic can be a stand-alone user-mode application which allocates memory using standard library functions, e.g., *malloc()* and test that memory. However, such diagnostic lacks control on the location of the memory pages allocated by the library and the OS. Another technique is to modify the memory management libraries to provide memory testing functionalities. The drawback of this technique is that applications need to be modified and re-built with new libraries. A more effective way is that the diagnostic can be integrated within the kernel as a kernel module or a kernel thread. Such diagnostic has privileged access to system memory and can test memory in background while applications are running. Some code change in the kernel may be required for this diagnostic to gain a better access over system memory resources.

#### 2.4 OS SCALABILITY ISSUES

Contemporary OSes (e.g., Linux, Windows, Solaris) use numerous locking mechanisms (e.g., spinlocks, reader-writer locks, etc.) to synchronize access control to shared resources. For simplicity, these locks were developed to be coarse-grained. Eventually, they were not scalable on multicore machines with more than eight CPU cores [17, 79]. The OS community developed more scalable locks, e.g., RCU locks, MCS locks, etc. and now the community is shifting their focus to the direction where access synchronization scalability is achieved using light-weight message passing [11, 16, 17, 30]. Regardless, these new OSes still need time to mature in design and go through a time-consuming development and rigorous testing before they are used in consumer systems. Further, NUMA is becoming more prevalent in newer systems to manage and scale with increased memory capacity and multiple CPU cores efficiently. Newer Linux kernels support NUMA and provide user-mode libraries (*libnuma* [31]) so that application programmers can use NUMA features. In addition to improved locking and NUMA support, Linux introduced local run queues [6] in process scheduling and improved load-balancing [2] in multicore systems. These improvements and features in the OS can be utilized to make a memory diagnostic scalable with large amount of memory.

#### 2.5 RELATED WORK

Researchers have predicted [13, 15] and observed [8, 19, 50, 66, 66, 71] high incidences of errors in processors and memory chips built at nanometer-scale. Both smaller transistor geometry and higher chip density aggravate the problem. A field study revealed that DRAM error rates are surprisingly high, with 25,000 to 70,000 errors per billion device hours per Mbit and dominated by hard errors [66]. This study found more than 8% of memory modules affected by errors per year. Another study found evidence of SDC occurring in an isolated and independent fashion, making it

extremely hard to detect and/or predict [8]. Other studies [27, 38, 73] made similar observations. This past work motivates COMeT, but does not propose how to combat errors.

Two previous schemes are related to my work, Elm et al. [23] and Singh et al. [69]; like my work, they propose a software memory test strategy. While both proposals implement OS memory testing, the goals and strategies are different than COMeT. First, the past proposals assume ECC and test memory occasionally to catch faults with no consideration for page migration. Instead, COMeT is agnostic to the presence of ECC—it can work both with or without ECC support. If ECC is present, it can be used to triage memory regions that are weak to identify them for more aggressive testing by COMeT. Alternatively, if ECC is not present, COMeT can test memory continuously as described in the paper. Second, neither proposal is adaptive; they allocate a fixed chunk of memory for testing at a fixed rate assigned by the system administrator. They do not relate test strategy parameters and error coverage. Third, they do not study memory test performance on individual programs. For example, Elm et al. [23] measured and reported "system performance degradation" (essentially, lost cycles) due to their memory tester during a one-week experiment with 25 complete tests of a 32MB main memory. Singh et al. [69] employed two programs but detailed memory access behaviors were not discussed or related with the coverage results. Lastly, these previous studies did not consider CMPs.

More recent research (e.g., RAMpage [65] and FlipSphere [24]) has shown progress on software online memory testing. In RAMpage [65], an online scheme is described to test memory during low utilization; it does not guarantee the vulnerability window nor adapt test strategy. RAMpage relies on OS memory allocator interface to get memory pages to test while COMeT is integrated much deeper with the OS memory allocator to sample system memory usage behavior at runtime and get untested memory pages for testing. FlipSphere [24], on the other hand, is a library which provides error detection and correction to malloc system call. It offloads ECC calculation to off-chip hardware accelerator (Intel Xion Phi co-processors [5]). Their technique is on-demand memory testing and suffers from very high performance overhead (85%). COMeT's techniques are orthogonal to FlipShpere and as a future improvement, COMeT can use FlipSphere's hardwarebased ECC calculation approach to make MARCH tests more efficient by using off-chip hardware.

#### 3.0 ONLINE MEMORY DIAGNOSTICS

An online memory diagnostic is a software process that checks for errors in physical memory. Errors in DRAM can manifest themselves at any point [8, 71], which necessitates that physical pages are constantly checked. Memory pages with detected errors can be retired and isolated by the OS. By avoiding pages with errors, especially ones with errors that are uncorrectable by hardware mechanisms (e.g., multi-bit errors for SECDED), reliability is improved. In essence, an online memory diagnostic sweeps through memory at regular intervals with a MARCH test [76, 80]. A MARCH test writes specific bit patterns on physical locations of memory, reads them back, and verifies the correctness of the values to determine marginal erroneous locations. Typically, a more thorough test with many bit patterns can discover more lurking error conditions including unusual but possible ones. Multiple MARCH tests can be used with varying periodicity to check for different error types.

## 3.1 OBSERVATIONS INFLUENCING ONLINE MEMORY DIAGNOSTICS

Although conceptually simple, there are numerous ways that memory testing can be structured and integrated as an online and software-only method. Four observations influenced my design and implementation:

1. The frequency at which memory pages are tested impacts the likelihood that an application will

encounter a page with an error—the more recent an actively used page is tested, the less likely an application will hit an error on the page. Thus, the amount of time between successive tests on the same physical page determines a "vulnerability window" during which a memory access could suffer an error. To test the entire memory capacity can be time consuming, which can lead to a long vulnerability window. However, the vulnerability window should be minimized for a better error resiliency.

- 2. Memory errors can equally affect single-threaded and multi-threaded applications. An application is vulnerable only to errors on pages that are used. Pages that are allocated, or will be allocated in the near future, must be tested, but unused ones do not have to be checked. Thus, depending on memory utilization, only a portion of physical memory actually needs to be tested. By checking a smaller number of used pages, test frequency can be increased to reduce the vulnerability window. Alternatively, the test frequency can be set for total memory capacity, and less memory could be tested to reduce overhead.

- 3. Applications often have high page turnover. A page may be requested, allocated and then released quickly. After a page is released, the vulnerability window for that page may not have been reached yet. Thus, a page that has been recently tested and returned does not have to be tested again until the guaranteed duration of the vulnerability window is reached. In essence, this reduces the amount of testing that has to be done. Some pages may be held for a long period and must be tested while they are being used.

- 4. The test rate only partially determines the actual error exposure of an application. An error may appear shortly after a page is tested, but before the page is tested again. A program will be corrupted only if the error location is accessed and the "bad value" is propagated to sensitive state [36, 37, 47, 48]. Thus, even a modest limit on the vulnerability window duration can be effective.

#### 3.2 MY APPROACH FOR ONLINE MEMORY DIAGNOSTIC

Based on these observations, one way to do memory testing is "on demand". An on-demand strategy can reduce the amount of testing by focusing on pages that are actually allocated. A physical page is tested on-demand when it is allocated and mapped to a virtual page. A page that is held for longer than the vulnerability window is periodically tested by migrating the page to one that is tested.

However, an on-demand strategy is naïve: It introduces large performance overhead since it is inherently sequential. In particular, on a page allocation, the amount of time spent to test a page is fully observed because an application is paused while waiting for its allocation request to be satisfied. Similarly, when page migration is done sequentially with program execution, the program has to wait. Although some migration latency can be masked by testing and copying pages during blocked periods for an application, this process is too unpredictable to guarantee the vulnerability window.

A less time consuming and more predictable approach can check page health *concurrently* to program execution in *anticipation* of allocation. With available idleness in a typical commodity CMP, a free core (or cores) can be used to constantly test memory from which allocation requests are satisfied. Migration can be used to copy long-held pages to ones that are already tested before migration begins. This "ahead-of-time" strategy plans for allocation by executing MARCH tests on pages before requests are placed.

### 3.2.1 Operation

The key to ahead-of-time diagnostic is the maintenance of a pool of *unused tested pages* from which memory allocation requests are satisfied. The allocation requests may come from an application's memory usage patterns or the test processes employed by the strategy. The tested pages in the pool must be regularly replenished (i.e., newly tested pages are added as pages are removed or grow old). This strategy cooperatively works with the OS memory allocator to provide tested

Figure 2: Page State Diagram

pages and gather feedback about memory demand to adjust the replenishment rate.

The ahead-of-time diagnostic guarantees that every page used by an application has had its health checked within a fixed time interval. To express this guarantee, I defined age(p) as the amount of time elapsed since physical page p was last tested. My approach guarantees  $age(p)+\delta < test\_lifetime$  for all pages p used by an application.  $\delta$  is a small constant to allow the diagnostic to check for page expiration prior to it happening. In this way, a bound, determined by  $test\_lifetime$ , is placed on the vulnerability window which assures a sound memory health.

To understand ahead-of-time diagnostic, first consider a simplified memory allocator. Assume this allocator has a single free list and maintains a page in one of two states – *free* or *used*. A *free* page is on the free list and available for allocation. Physical memory pages are transitioned between these states based on allocation and de-allocation requests. The diagnostic adds states and transitions to the simplified allocator's state diagram to track whether a page is tested or untested. Figure 2 shows state diagram for the diagnostic. age(p) is the amount of time that page p spends in a *tested* state (free or used). Initially, p is *untested free*. At some point, p is selected to be tested and transitioned to *tested free* or *failed*. On a successful test, p is moved to *tested free* and remains in this state until it is allocated or  $age(p) + \delta \ge test\_lifetime$ . A page that does not pass the test is retired and put in the *failed* state.

When a *tested free* page p is requested, it is transitioned to *tested used*. However, it is possible for p to remain in *tested free* long enough that  $age(p) + \delta \ge test\_lifetime$ , which is called "test expiration". To maintain its guarantee, the diagnostic must inspect p's age to ensure the page has not expired. If p expired, then it is transitioned to *untested free* to refresh its test. A different unexpired *tested free* page, q, is selected instead to satisfy the memory request.

Similarly, a *tested used* page p can also expire. In this case, the diagnostic should replace p with a *tested free* page q before p expires. p is migrated to q, and the states of p and q are updated to *untested free* and *tested used*, respectively. This diagnostic must periodically check p's age while the page is in use. Thus, the transition from *tested used* to *untested free* happens on a regular time interval during application execution.

Finally, a transition happens from *untested free* to *tested used* when there are not enough pages in *tested free* to satisfy a memory request. It causes a page to be tested on-demand at the moment of a request, incurring overhead. This diagnostic tries to avoid this transition maintaining enough *tested free* pages to meet instantaneous demand. Although, in reality, errors can manifest while a page is being used by an application, the diagnostic does not handle the situation.

#### 3.2.2 Test Guarantee and Replenishment

My "ahead-of-time" diagnostic relies on two rates. The first rate, termed the "guarantee rate", controls how often to check whether *tested used* pages expire. The second rate—the "replenishment rate"—determines how often to replenish *tested free* pages.

The **guarantee rate** is determined by  $test\_lifetime$ . To maintain  $age(p) + \delta < test\_lifetime$ , the rate must be at least  $\frac{1}{test\_lifetime-\delta}$ . This rate represents only how often my approach needs to check whether *tested used* pages should be migrated and released. Pages that are *tested free* can have their age checked at time of allocation, as previously described. To set the guarantee rate,  $test\_lifetime$  has to be determined. A simple strategy based on physical memory capacity and utilization can be used:

$$test\_lifetime = \alpha \times \frac{\left(\frac{mem\_cap}{page\_size}\right) \times mem\_util \times test\_latency}{test\_res}$$

In this equation,  $\alpha \ge 1$  is an adjustment factor set by the system administrator to scale *test\_lifetime* according to system needs. A larger power or performance budget means a higher test rate can be

used. A low error rate would normally permit a slower test rate than the one solely established by memory capacity.

$mem\_cap$  is the memory capacity and  $page\_size$  is the memory page size. These parameters reflect the physical memory configuration.  $mem\_util$  is the average percentage of used memory.  $mem\_util = 1.0$  sets the guarantee rate conservatively enough that the entire capacity can be tested. However, the whole memory may not be fully utilized (i.e., all pages in *tested used*) at any moment, and the guarantee rate could be set higher by adjusting  $mem\_util$ . The slack from less than peak utilization can alternatively be exploited to reduce the performance and energy cost of checking memory health since fewer pages have to be checked in unit time.

*test\_latency* is the amount of time needed to test one page. This latency depends on what tests are done. For example, a comprehensive MARCH test that makes multiple passes over physical memory to read and write different bit patterns could take upwards of 1ms per page (there is no caching!). *test\_res* influences the test rate—the more computational time that the diagnostic is allowed for testing, the faster the guarantee rate. In a "core rich environment", we may be able to dedicate a core(s) to test memory and set *test\_res* = 1.0. In contrast,  $\alpha$  can enforce a high test rate even under low memory pressure.

Unlike the guarantee rate, the **replenishment rate** does not effect the vulnerability of an application to errors. Instead, it determines how often the pool of tested unused pages is filled. Its purpose is to avoid the "demand transition" in the page state diagram. To replenish the pool, a set of *untested free* pages need to be acquired, a MARCH test done, and the pages returned. When the pages are released, they are put in the *tested free* state. The page tests are done concurrently to application execution. The higher the replenishment rate, the more likely that an application request can be satisfied with *tested free* pages and the on-demand transition in Figure 2 can be avoided. However, a high replenishment rate puts more load on the memory subsystem. It also removes more pages on average from the memory allocator, impacting the allocator's ability to satisfy requests in overload situations. It also causes the allocator's performance to suffer due to locking and internal bookkeeping (e.g., breaking buddy blocks into smaller ones). If the replenishment rate is set too low, there may not be enough *tested free* pages available, which can cause

overhead due to the on-demand transition.

The "ahead-of-time" diagnostic walks the tight rope between a high and a low replenishment rate by monitoring memory requests to adjust the rate. As described later, my implementation uses an adaptive strategy based on recent history of memory requests to determine a current replenishment rate. The rate by itself is insufficient since it can be satisfied in different ways. Two parameters determine the replenishment rate:  $block\_demand$  and  $replenish-\delta$ .  $block\_demand$  is number of pages to test every interval of  $replenish-\delta$  time. My approach dynamically determines  $block\_demand$ , but  $replenish-\delta$  is statically fixed.

## 3.3 ASSUMPTIONS

Several assumptions are made to isolate the fundamental concepts and strategies of my approach from its implementation details in real systems. My assumptions are stated below.

First, my techniques will not test memory that belongs to the OS kernel. The kernel memory is assumed to be fault-free and can be tested with appropriates changes to the OS memory manager. I developed a general methodology for online memory testing and apply that methodology to application memory.

Second, my approach targets detecting hard errors in DRAM including the ones which only manifest under certain operational conditions (e.g., low power budget, temperature, stress on DRAM cells due to reading and writing certain MARCH test patterns, etc.). Detection of SEUs and similar short term transient errors is not a goal of my approach.

Third, on a fault discovery, a memory page is isolated and flagged unusable by the OS instead of replacing the memory module.

Fourth, my approach assumes that the system memory controller exposes information on DRAM row buffer open and close operations. This information is used by tester to ensure test patterns land in DRAM cells from DRAM row buffer during MARCH test.

Fifth, if the target system uses Non-Uniform Memory Access (NUMA) architecture, then the underlying topology is assumed to be known. It can be either automatically collected from the BIOS or manually derived by calculating speed of memory accesses on different nodes from different cores. Discovery of the NUMA topology is not a focus.

Lastly, the target systems are assumed to be over-provisioned and there will be time periods when system recourses are available to perform the diagnostic. However, I evaluated my approaches in overloaded systems to understand how the diagnostic behaves and affects applications in a stressful high-load situation.

#### 3.4 FRAMEWORK FOR ONLINE MEMORY DIAGNOSTIC

In this research, I developed a diagnostic framework, COMeT, which performs error diagnosis on physical memory and scales to multi-core system. At the core, this diagnostic sweeps through memory at regular intervals with a MARCH test. Memory pages with detected errors can be retired, scrubbed or possibly salvaged for small kernel buffers [77]. COMeT exercises the entire memory system, including the memory controller(s), memory interconnect, DIMMs, and associated glue logic.

Figure 3 shows my proposed high-level design of the framework. In this figure, the *Diagnostic Manager* module retrofits the OS memory manager with a memory diagnostic capability. The Diagnostic Manager works as an intermediary between the memory manager and the memory tester threads. A tester thread is responsible for executing MARCH tests on a given memory page. A set of testers can be executed per node which consists of a number of cores and memory. The memory manager is responsible for managing the memory associated with a node. To determine the number of memory pages to test in a given amount of time, the Diagnostic Manager depends on the following five parameters.

1. The **Memory Capacity** of the system.

Figure 3: High-Level Design of COMeT

- 2. The **Memory Utilization** which indicates the level memory pressure the system is currently undergoing.

- 3. The **Test Latency** to test a memory page depending on the MARCH test.

- 4. The **CPU Share** the tester threads will get depending on system workload.

- 5. The **Scalability Requirement** which impacts performance due to testing on large-scale multicore and multi-socket systems.

After determining the number of pages to test, the Diagnostic Manager pulls pages out of the memory manager and hands those pages to a tester thread. When testing is finished, the tester thread notifies the Diagnostic Manager which returns fault-free pages to the memory manager. A bad memory page is marked unusable and isolated from the OS by the Diagnostic Manager. My design of the framework aims to minimize the performance impact by fairly distributing testing tasks among tester threads depending on their processing capacity and current load.

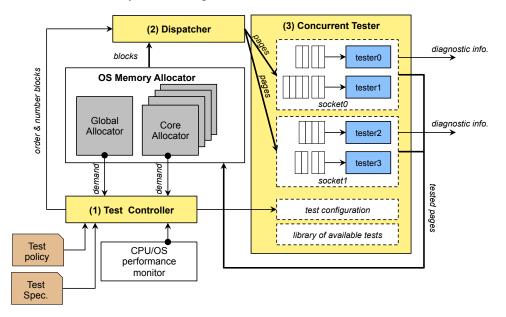

Figure 4 gives an overview of framework components. It is integrated in the OS kernel and works collaboratively with memory allocation. There are three components: 1) Test Controller

Figure 4: Framework Components

(TC), 2) Test Dispatcher (TD), and 3) Concurrent Tester Threads (CTT).

TC determines *how* memory should be tested and sets diagnostic parameters, or *configuration*, accordingly. A *Test Policy* is incorporated in the Test Controller to set the configuration; the policy is developed by the administrator for a target system. The Test Policy is responsible for only configuring the diagnostic; it decides *how* to test, rather than *what* and *how much* to test. Depending on Test Policy and memory demand information from the OS, TC determines how much and what to test and passes this information to TD. TD extracts physical pages frames from the memory allocator and distributes them to software threads that do memory tests, CTT. CTT is a collection of kernel threads that test memory. TD is node-aware for multi-processor systems and balances work distribution. This design not only ensures scalability but also enables an administrator to implement system-specific diagnostic control policies and memory test algorithms.

The design of the framework is flexible enough to optimize a diagnostic for small-scale systems with limited resource availability or to maximize a diagnostic to support various diagnostic policies on large-scale systems. COMeT is not a substitute for hardware ECC, which should be used whenever possible. COMeT can work cooperatively with hardware ECC to proactively and thoroughly test memory. In this case, it would operate post ECC to triage memory modules to determine degree of marginality and potential for uncorrected multi-bit errors. Similarly, COMeT can be used to focus checkpointing on marginal memory modules. In the following chapter, I describe how COMeT framework can be used to design and implement diagnostic policy suitable for single-threaded applications on small-scale systems.

#### 4.0 ONLINE MEMORY DIAGNOSTIC IN SMALL-SCALE SYSTEMS

The requirements for an online diagnostic (i.e., transparent operation in a live system, low performance overhead, support for both single-threaded and multi-threaded programming models and bounded memory error vulnerability) pose important questions about its design, operation, and implementation. In this chapter, I answer these questions, including: 1) what is an appropriate design that is both performance efficient and can guarantee that memory health is regularly checked; 2) how should an online diagnostic be implemented and integrated in an actual system; 3) is a software-only memory diagnostic feasible from an implementation and performance perspective and can it improve memory resiliency; and, 4) is this diagnostic capable enough to handle multithreaded workloads.

For small-scale systems, COMeT is designed to work with both single-threaded and multithreaded applications. COMeT operates along-side an OS memory manager. So, many of its design choices depend on OS memory manager functionalities. Next sections describe these design choices including the architecture and algorithms behind COMeT. The choices are made in the context of a prototype in Linux that examines how the approach can be integrated with a modern operating system. The design is discussed below.

Figure 5: Design of COMeT

## 4.1 ARCHITECTURE

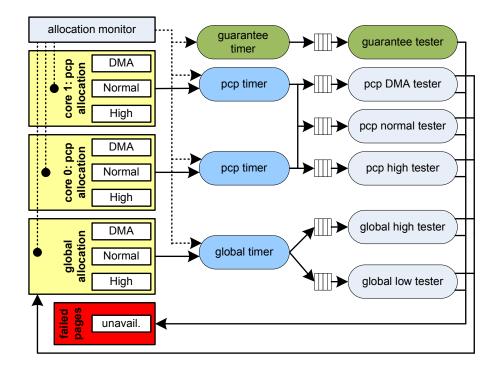

Figure 5 shows COMeT's implementation, which adds several timers and threads to the OS kernel. As the figure shows, memory allocation is partitioned in a modern OS (e.g., Linux) among global and per-CPU page frame cache (PCP) allocators. Each allocator has free lists that hold blocks of contiguous unused pages. The global allocator uses buddy lists, where a free list is an *order* of rank *i* that holds free blocks of size  $2^i$ . There are orders  $0 \le i \le 10$  in Linux. For PCP allocation, there is a separate free list for each core, which locally caches free blocks of size 1. The allocators have separate free lists for different memory zones (DMA, normal and high). Allocation is hierarchical: the PCP allocator is tried first, and if this fails, then the global allocator is tried.

Most changes made to the OS kernel for COMeT are independent of the actual memory allo-

cators, with three exceptions. First, I added interfaces to the memory allocators to request untested blocks and insert tested blocks into free lists. These interfaces can be invoked only by kernel threads. Second, I changed the memory allocators to gather and expose information about memory request demand. Finally, the allocators are modified to return a tested block for an allocation request. If a tested block is unavailable, then the allocator invokes a MARCH test on a block to satisfy the request. This change implements the demand transition from Figure 2.

COMeT introduces new kernel timers to guarantee the vulnerability window and to replenish the free lists with tested pages. Figure 5 shows four timers: one for the vulnerability window guarantee ("guarantee timer"), one for global allocation ("global timer"), and two for per-core allocation on each core ("pcp timer"). When the guarantee timer expires, physical pages are checked for test expiration. When an allocation timer expires, its handler pulls untested blocks, based on monitored demand, from the appropriate free lists to be tested.

New kernel threads are also added to do the actual testing (e.g., "pcp normal tester" and "global low order tester"). Each thread has an input work queue used to accept blocks for testing. The threads are arranged by zone and buddy order rank. For PCP allocation, there are three threads – one tests DMA pages, one tests normal pages, and the last one tests high pages. Similarly, for global allocation, one thread tests the low buddy orders and the other tests the high orders. This organization localizes testing and permits different thread priorities based on latency and importance to satisfying memory requests.

The timer handlers pass memory blocks to these threads for testing. The testers check the blocks, and return blocks to the allocators. When a test finds a page with an error, the page is put into a fault map of failed pages. A page is never allocated again once in the fault map.

#### 4.1.1 Allocation Monitor

The allocation monitor holds a buffer of counters to track allocation events. The counters record memory demand over the time interval *replenish-* $\delta$ . Each free list has its own counters because demand varies per list. There are two counters for each list: *allocated* counts the number of blocks allocated and *tested* counts number of free tested blocks. The counters are set by the allocation

timer handlers. Each counter is 16 bits which rarely saturates for small *replenish-* $\delta$  values.

## 4.1.2 Guarantee Timer and Handler

Figure 6 shows pseudo-code for the guarantee timer's handler. The handler checks whether a page is about to expire (i.e.,  $age(p) + \delta \ge test\_lifetime$ ). To check for test expiration, the handler compares the current time to a *timestamp* for each allocated physical page. When a page, p, is allocated, its *timestamp* is set to  $t_{alloc}(p) + test\_lifetime - \delta$ . On line 1, the current time, *time*, is queried. FIND-EXPIRED-PAGES returns a list of pages whose  $timestamp \ge time$  on line 2.

GUARANTEE-HANDLER()

- 1 TimeStamp time = GET-TIME()

- 2 PageList *expired* = FIND-EXPIRED-PAGES(*time*)

- 3 foreach Page page in expired

- 4 Page newpage = ALLOCATE(0)

- 5 MARK-PTE-MIGRATING(page)

- 6 COPY(*newpage*, *page*)

- 7 UPDATE-PTE(*newpage*, *page*)

- 8 RELEASE(*page*,0)

- 9 Set-timer( $\delta (\text{Get-time})$ )

Figure 6: Check expiration of tested used pages

Lines 3 to 8 migrate an expired page by allocating a new tested page and copying the old one to it. During migration, page table entries (PTEs) for the old page are flagged. This action causes a process to fault when it touches a migrating page and to be paused until the migration completes. Once the old page is copied to the new one, the associated PTEs are updated and the old page is released. Line 9 re-arms the timer which is set to expire in  $\delta$  time, taking page migration latency into account. As long as the handler finishes in  $\delta$ , the promise on the vulnerability window is satisfied. However, my implementation does not guarantee this condition.  $\delta$  is large enough (e.g., 10 seconds) that the migration will likely be completed before the next timer event. If such a "deadline miss" actually arises, then migration can be parallelized for better performance.

### 4.1.3 Global Allocation Timer and Handler

To replenish the pool of tested pages, COMeT regularly extracts and tests blocks of pages. Figure 7(a) shows pseudo-code for this process. Each global allocation zone has a timer. When a timer expires, GLOBAL-HANDLER is invoked with an identifier for the zone (zone).<sup>1</sup> GLOBAL-HANDLER forms two lists: *lowlist* and *highlist* (lines 1 and 2) that collect untested blocks based on order rank. Blocks put into the lists are tested by the global tester (Section 4.1.4). Lines 3 to 18 build the two lists. The **for** loop iterates over the buddy orders. A descriptor for an order is accessed on line 4.

GLOBAL-HANDLER(MemoryZone zone)

```

1 PageBlockList lowlist = NIL

2 PageBlockList highlist = NIL

3 for Integer id = 0 to MAX-ORDER(zone)

BuddyOrder order = zone.freelist[id]

4

5

ADJUST-REPLENISH-RATE(order)

6

Integer blockdemand = BLOCKS-TO-TEST(order)

7

if blockdemand \neq 0

8

PageBlock block = TAIL(order)

9

while block \neq HEAD(order) and blockdemand > 0

10

PageBlock prevblock = PREV(block, order)

if IS-TESTED(block) == FALSE

11

12

REMOVE(block, order)

13

if order \leq \text{LOW-ORDER}

14

ENQUEUE(block, lowlist)

15

else

ENQUEUE(block, highlist)

16

N = N - 1

17

18

block = prevblock

19 SIGNAL-WORK(LOW-TEST-THREAD, lowlist)

20 SIGNAL-WORK(HIGH-TEST-THREAD, highlist)

```

```

21 Set-timer(this, replenish-\delta)

```

Figure 7: Handler for global allocation timer

Next, in line 5, ADJUST-REPLENISH-RATE adjusts the replenishment rate (discussed in Section 4.1.5). Once the new rate is set, the number of blocks, *blockdemand*, to test to meet the rate is determined (line 6). BLOCKS-TO-TEST retrieves the replenishment rate which is updated by ADJUST-REPLENISH-RATE at each *replenish-* $\delta$  interval. If blocks need to be tested (line 7), then

<sup>&</sup>lt;sup>1</sup>Although not shown, the actual implementation is re-entrant to handle two or more timer expirations.

up to *blockdemand* untested blocks are extracted from the order (lines 8 to 18). The **while** loop on line 9 iterates through the order's free list from tail to head. The list is processed in reverse because it is more likely that untested blocks will be at the list's end (these are the "older" blocks). An untested block is removed from the free list on line 12. If this block came from a low order (determined by the constant LOW-ORDER), then it is put into *lowlist* for testing. Otherwise, it is added to *highlist*. Lines 19 and 20 signal the low and high global tester threads that new blocks are available. Finally, line 21 resets the global timer to *replenish-* $\delta$ . This parameter controls how frequently pages are pulled for testing; the page quantity (in blocks) is determined from the demand during the last *replenish-* $\delta$  interval. Unlike the guarantee rate, the replenishment rate does not have to be exact. Thus, the timer is set to expire in *replenish-* $\delta$  time.

## 4.1.4 Global Tester

GLOBAL-TESTER, shown in Figure 8(a), is the routine that tests page blocks. It consumes the list of blocks produced by the global timer's handler. GLOBAL-TESTER waits until the handler has produced work, and then it invokes TEST-BLOCK on each block in the work list.<sup>2</sup>

A MARCH test is done by TEST-BLOCK. Lines 2-5 test each page in a block with MARCH-TEST. The page is marked uncacheable prior to the MARCH test to avoid the caches filtering accesses to physical memory. The MARCH test operates on virtual addresses that are known to be mapped to the physical page. If the MARCH test fails, then the **foreach** loop terminates and lines 6 to 9 are done. Line 7 splits the block with the failed page into two or more smaller blocks. The block is split at the failed page. SPLIT-LIST-AT ensures that the new blocks have an appropriate number of pages (i.e., an integral power of 2). The new blocks are put in the work list on line 8 and the failed page is retired on line 9. If the test succeeded, then the block is released back to the allocator on line 11. A small block from a split is released to the appropriate buddy order (this step is not shown, but implied by RELEASE on line 11). Line 12 increments the *tested* counter for the block's order.

<sup>&</sup>lt;sup>2</sup>GLOBAL-TESTER handles delivery of new blocks during test, although this is not shown.

GLOBAL-TESTER(Signal *sig*, PageBlockList *work*)

- 1 while (TRUE)

- 2 WAIT-ON-SIGNAL(*sig*)

- 3 **while** (*work*  $\neq$  NIL)

- 4 PageBlock block = DEQUEUE(work)

- 5 TEST-BLOCK(*block*, *work*)

(a) Test each block in work list

TEST-BLOCK(PageBlock *block*, PageBlockList *work*)

```

1 Boolean isfailed = FALSE

```

- 2 foreach Page page in block and isfailed == FALSE

- 3 MARK-UNCACHEABLE(*page*)

- 4 isfailed = MARCH-TEST(page)

- 5 MARK-CACHEABLE(page)

- 6 if isfailed

- 7 PageList frags =SPLIT-LIST-AT(page, block)

- 8 ENQUEUE(frags, work)

- 9 **PERMANENTLY-RETIRE**(*page*)

10 **else**

- 11 **RELEASE**(*block*)

- 12 *monitor*. INCREMENT-TESTED(GET-ORDER(*block*))

(b) Test blocks and release good ones

Figure 8: Tester for global allocation

# 4.1.5 Adaptive Test Rate

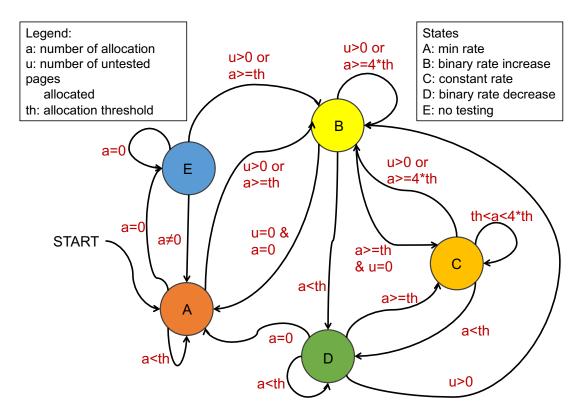

To change the test rate according to application memory requirements at runtime, COMeT uses an adaptive algorithm. This algorithm introduces five states for each of the free lists for each order. Each state tracks how the current memory demand affects the test rate on that free list. These five states are:

- 1. **State A:** The test rate is set to a minimum value that is configured during COMeT's initialization. The default minimum rate depends on the usage of the free list.

- 2. **State B:** The current test rate is doubled. This state usually signifies that COMeT is responding to increased memory demand.

- 3. State C: The current test rate is kept constant. This state signifies that memory demand has

been reduced but still high enough not to drop the test rate.

- 4. **State D:** The current test rate is decreased by half. This state signifies that memory demand is low enough to decrease the rate. If the rate falls below the minimum rate, the minimum rate is set for that free list.

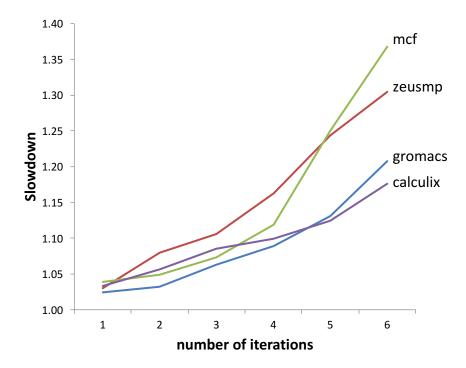

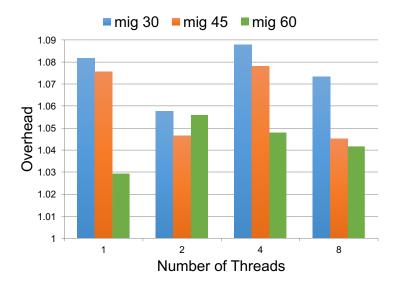

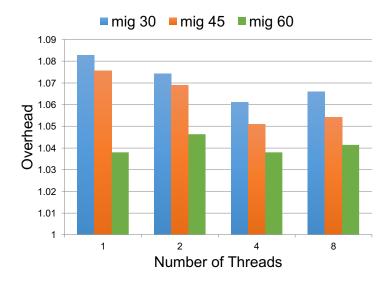

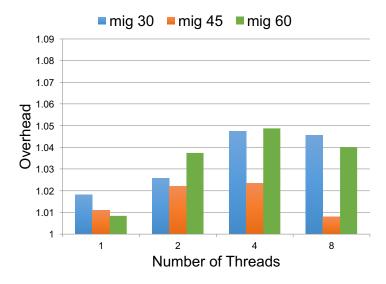

- 5. **State E:** The current test rate is set to 0. This state signifies that there are enough tested pages in the free list and memory demand is also low.