# IMPROVING THE PERFORMANCE OF HYBRID MAIN MEMORY THROUGH SYSTEM AWARE MANAGEMENT OF HETEROGENEOUS RESOURCES

by

# Juyoung Jung

B.S. in Information Engineering, Korea University, 2000Master in Computer Science, University of Pittsburgh, 2013

Submitted to the Graduate Faculty of

the Kenneth P. Dietrich School of Arts and Sciences in partial

fulfillment

of the requirements for the degree of

Doctor of Philosophy in Computer Science

University of Pittsburgh

2016

# UNIVERSITY OF PITTSBURGH

### KENNETH P. DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Juyoung Jung

It was defended on

December 7, 2016

and approved by

Rami Melhem, Ph.D., Professor at Department of Computer Science

Bruce Childers, Ph.D., Professor at Department of Computer Science

Daniel Mosse, Ph.D., Professor at Department of Computer Science

Jun Yang, Ph.D., Associate Professor at Electrical and Computer Engineering

Dissertation Director: Rami Melhem, Ph.D., Professor at Department of Computer Science

# IMPROVING THE PERFORMANCE OF HYBRID MAIN MEMORY THROUGH SYSTEM AWARE MANAGEMENT OF HETEROGENEOUS RESOURCES

Juyoung Jung, PhD

University of Pittsburgh, 2016

Modern computer systems feature memory hierarchies which typically include DRAM as the main memory and HDD as the secondary storage. DRAM and HDD have been extensively used for the past several decades because of their high performance and low cost per bit at their level of hierarchy. Unfortunately, DRAM is facing serious scaling and power consumption problems, while HDD has suffered from stagnant performance improvement and poor energy efficiency. After all, computer system architects have an implicit consensus that there is no hope to improve future system's performance and power consumption unless something fundamentally changes.

To address the looming problems with DRAM and HDD, emerging Non-Volatile RAMs (NVRAMs) such as Phase Change Memory (PCM) or Spin-Transfer-Toque Magnetoresistive RAM (STT-MRAM) have been actively explored as new media of future memory hierarchy. However, since these NVRAMs have quite different characteristics from DRAM and HDD, integrating NVRAMs into conventional memory hierarchy requires significant architectural re-considerations and changes, imposing additional and complicated design trade-offs on the memory hierarchy design. This work assumes a future system in which both main memory and secondary storage include NVRAMs and are placed on the same memory bus.

In this system organization, this dissertation work has addressed a problem facing the efficient exploitation of NVRAMs and DRAM integrated into a future platform's memory hierarchy. Especially, this dissertation has investigated the system performance and lifetime

improvement endowed by a novel system architecture called Memorage which co-manages all available physical NVRAM resources for main memory and storage at a system-level. Also, the work has studied the impact of a model-guided, hardware-driven page swap in a hybrid main memory on the application performance. Together, the two ideas enable a future system to ameliorate high system performance degradation under heavy memory pressure and to avoid an inefficient use of DRAM capacity due to injudicious page swap decisions.

In summary, this research has not only demonstrated how emerging NVRAMs can be effectively employed and integrated in order to enhance the performance and endurance of a future system, but also helped system architects understand important design trade-offs for emerging NVRAMs based memory and storage systems.

## TABLE OF CONTENTS

| 1.0 | IN'                             | INTRODUCTION                                            |    |  |  |  |  |  |

|-----|---------------------------------|---------------------------------------------------------|----|--|--|--|--|--|

|     | 1.1                             | Recent Trends of Memory Hierarchy Design                | 2  |  |  |  |  |  |

|     | 1.2                             | Research Overview and Contributions                     | 6  |  |  |  |  |  |

|     |                                 | 1.2.1 An NVRAM-based System Platform                    | 6  |  |  |  |  |  |

|     |                                 | 1.2.2 Problem Overview                                  | 9  |  |  |  |  |  |

|     |                                 | 1.2.2.1 Effective Handling of Memory Pressure           | 9  |  |  |  |  |  |

|     |                                 | 1.2.2.2 Efficient Utilization of Fast DRAM Resources    | 10 |  |  |  |  |  |

|     |                                 | 1.2.2.3 How Are Both Problems Related To Each Other?    | 12 |  |  |  |  |  |

|     |                                 | 1.2.3 Research Contributions                            | 12 |  |  |  |  |  |

|     |                                 | 1.2.3.1 Contributions to the External Page Swap Problem | 12 |  |  |  |  |  |

|     |                                 | 1.2.3.2 Contributions to In-Memory Page Swap Problem    | 13 |  |  |  |  |  |

|     | 1.3                             | Dissertation Organization                               | 14 |  |  |  |  |  |

| 2.0 | BA                              | CKGROUND                                                | 15 |  |  |  |  |  |

|     | 2.1 Emerging NVRAM Technologies |                                                         |    |  |  |  |  |  |

|     | 2.2                             | System Hardware Interfaces to NVRAM-based SSD           | 18 |  |  |  |  |  |

|     | 2.3                             | OS Memory Management and I/O Stack                      | 20 |  |  |  |  |  |

|     |                                 | 2.3.1 OS Memory Management                              | 20 |  |  |  |  |  |

|     |                                 | 2.3.2 OS I/O Stack                                      | 21 |  |  |  |  |  |

|     | 2.4                             | OS Page Movement Techniques                             | 22 |  |  |  |  |  |

| 3.0 | UN                              | IFIED MANAGEMENT OF SYSTEM'S NVRAM RESOURCES .          | 24 |  |  |  |  |  |

|     | 3.1                             | Motivation and A Studied System Architecture            | 24 |  |  |  |  |  |

|     | 3.2                             | The Memorage Architecture                               | 27 |  |  |  |  |  |

|            |     | 3.2.1 Memorage Philosophy                                             | 27 |

|------------|-----|-----------------------------------------------------------------------|----|

|            |     | 3.2.2 Key Design Goals                                                | 29 |

|            |     | 3.2.3 Memorage Design and Implementation                              | 30 |

|            |     | 3.2.3.1 Managing Resource Information                                 | 30 |

|            |     | 3.2.3.2 Memory Expansion and Shrinkage                                | 33 |

|            |     | 3.2.4 Comparison with Possible Alternatives                           | 36 |

|            |     | 3.2.5 Further Discussions                                             | 37 |

|            | 3.3 | Experimental Results                                                  | 38 |

|            |     | 3.3.1 Evaluation Methodology                                          | 38 |

|            |     | 3.3.2 Characterization of Platform Performance                        | 42 |

|            |     | 3.3.3 Software Latency of a Page Fault                                | 44 |

|            |     | 3.3.4 Application Performance                                         | 46 |

|            | 3.4 | System Lifetime Model of NVRAM Resource Sharing                       | 51 |

|            |     | 3.4.1 Modeling Main Memory Lifetime                                   | 51 |

|            |     | 3.4.2 System Lifetime Analysis via Model                              | 54 |

|            | 3.5 | Related Work                                                          | 57 |

|            | 3.6 | Summary                                                               | 58 |

| <b>4.0</b> | HA  | RDWARE-DRIVEN PAGE SWAP IN HYBRID MAIN MEMORY                         | 60 |

|            | 4.1 | Motivation                                                            | 60 |

|            | 4.2 | Analytical Model of Hardware-driven Page Swap in Hybrid Main Memory . | 63 |

|            |     | 4.2.1 A Studied System Architecture and Model Parameters              | 63 |

|            |     | 4.2.2 Baseline CPI Model without In-Memory Page Swap                  | 65 |

|            |     | 4.2.3 New CPI Model with In-Memory Page Swap                          | 67 |

|            |     | 4.2.4 Profitability of page swap                                      | 68 |

|            | 4.3 | Comparing Model with Simulation                                       | 69 |

|            |     | 4.3.1 Experimental Setup and Simulation Methodology                   | 69 |

|            |     | 4.3.2 Evaluation Results                                              | 71 |

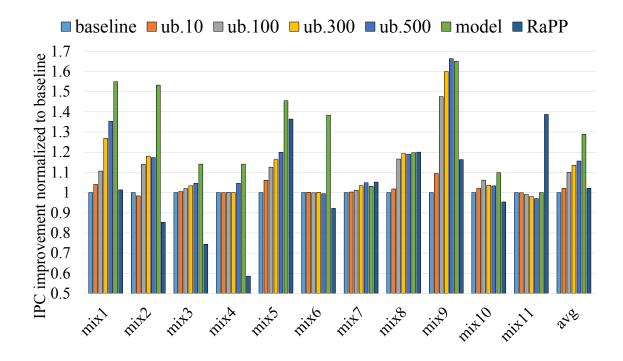

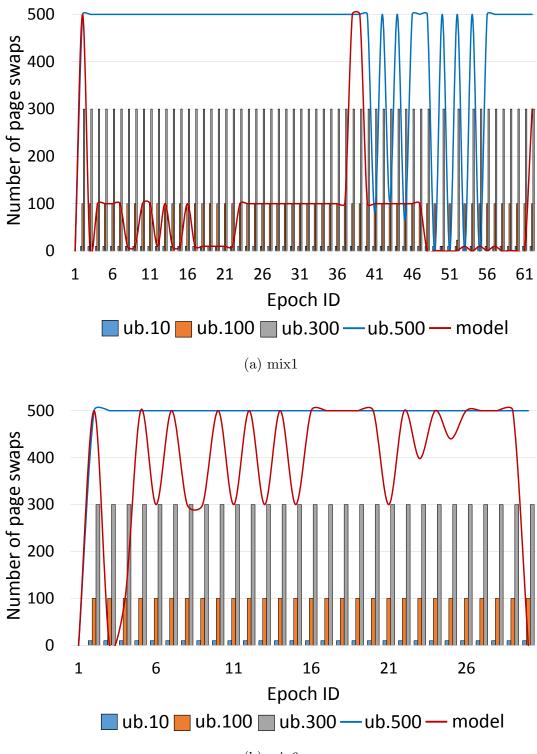

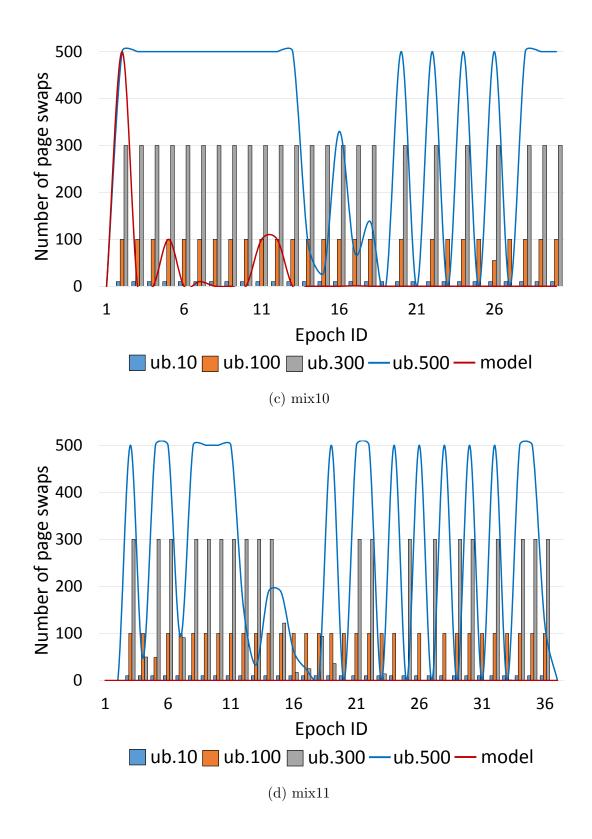

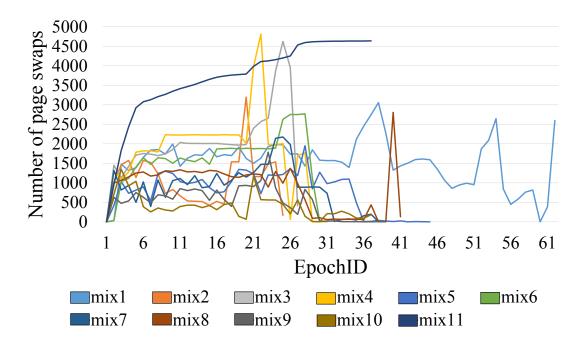

|            | 4.4 | Model-guided Hardware-driven Page Swap                                | 77 |

|            |     | 4.4.1 Simulation Methodology                                          | 79 |

|            |     | 4.4.2 Evaluation Results                                              | 79 |

|     | 4.5 Related Work            | 85 |

|-----|-----------------------------|----|

|     | 4.6 Summary                 | 89 |

| 5.0 | CONCLUSIONS AND FUTURE WORK | 91 |

|     | 5.1 Concluding Remarks      | 91 |

|     | 5.2 Future Work             | 92 |

| BIE | BLIOGRAPHY                  | 94 |

## LIST OF TABLES

| 1 | Technology comparisons           | 16 |

|---|----------------------------------|----|

| 2 | Memorage emulator platform       | 39 |

| 3 | Evaluated memory configurations  | 42 |

| 4 | Performance Model Parameters     | 66 |

| 5 | Simulation configuration         | 70 |

| 6 | Multiprogrammed workloads        | 71 |

| 7 | The considered page swap schemes | 78 |

## LIST OF FIGURES

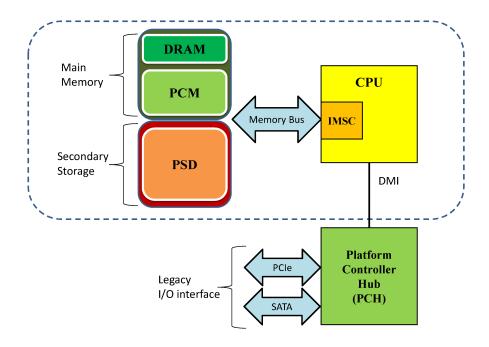

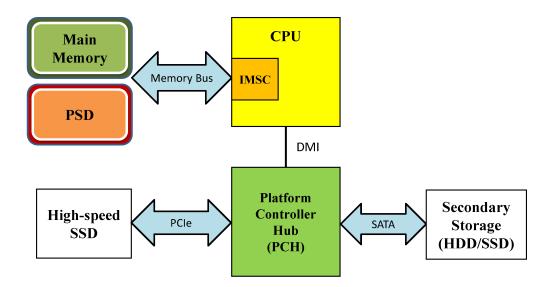

| 1  | An illustration of a future platform with hybrid memory and PSD $\ldots$ . | 7  |

|----|----------------------------------------------------------------------------|----|

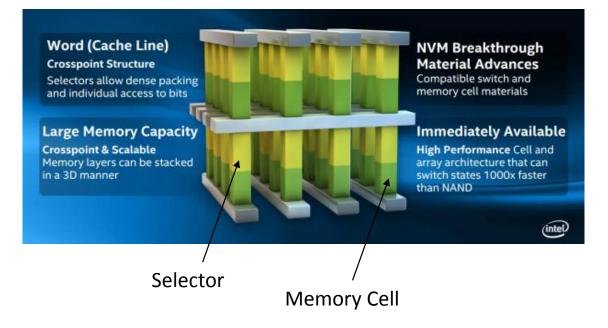

| 2  | 3D XPoint technology                                                       | 17 |

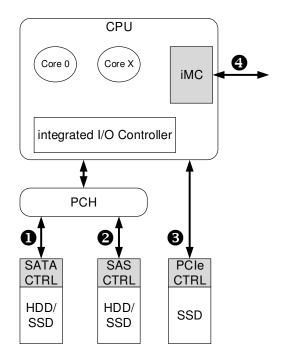

| 3  | Hardware interfaces for storage devices                                    | 19 |

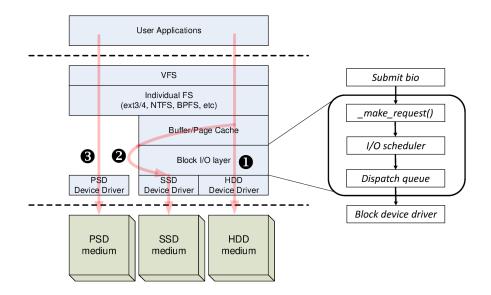

| 4  | Linux I/O stack                                                            | 21 |

| 5  | Linux page movement syscalls                                               | 23 |

| 6  | A future system platform with NVRAM memory and storage                     | 26 |

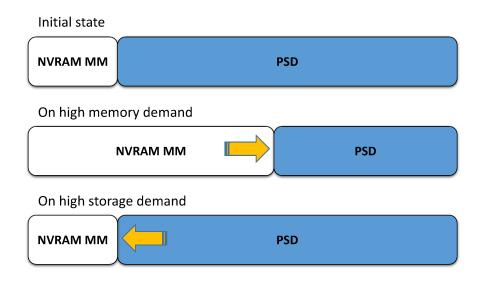

| 7  | Illustration of Memorage concept                                           | 27 |

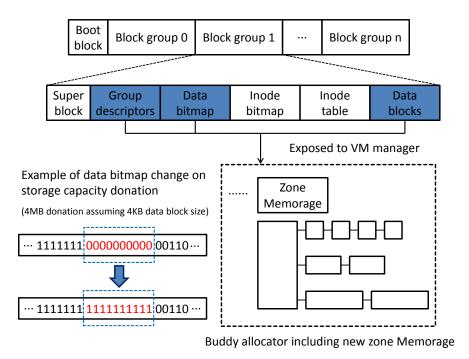

| 8  | Memorage zone seen by OS buddy allocator                                   | 32 |

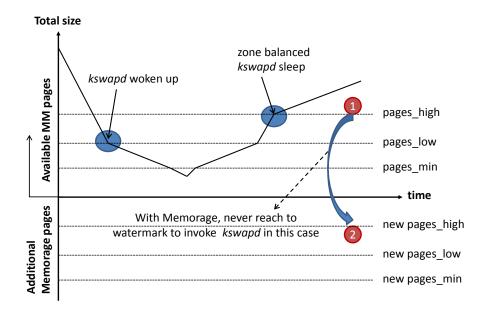

| 9  | Effect of Memorage on page reclamation thresholds                          | 34 |

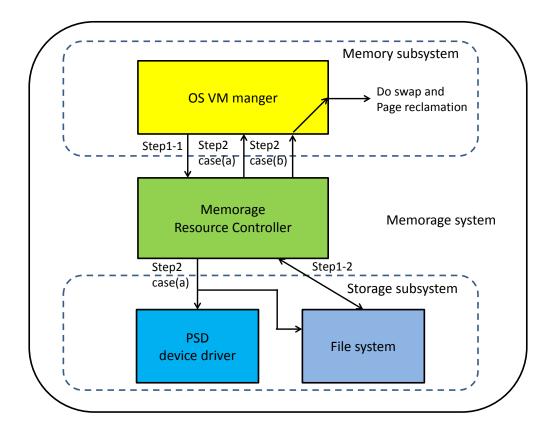

| 10 | Cooperation between OS VM manager and storage subsystem                    | 35 |

| 11 | Illustration of emulation methodology.                                     | 40 |

| 12 | Unloaded platform characterization                                         | 43 |

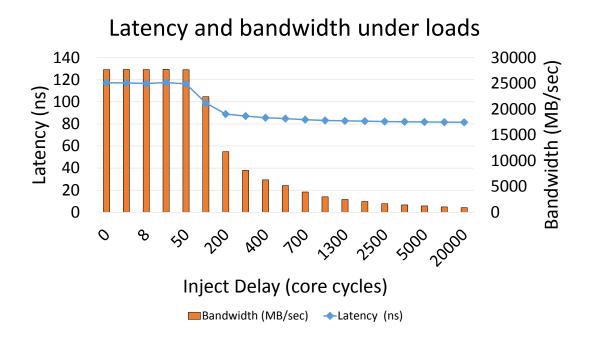

| 13 | Loaded platform characterization                                           | 44 |

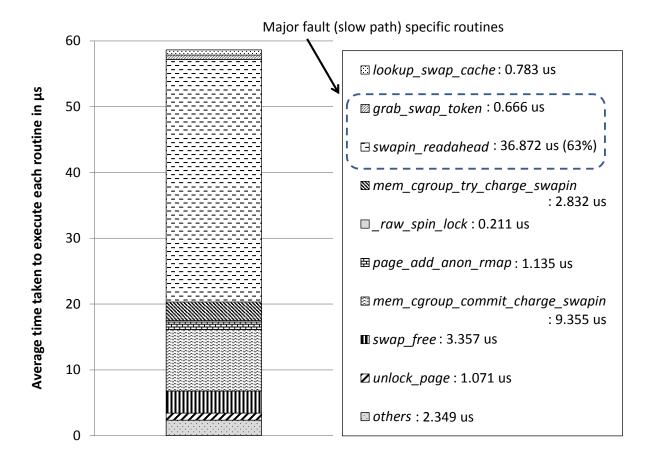

| 14 | Breakdown of software latency of the Linux page fault handler              | 45 |

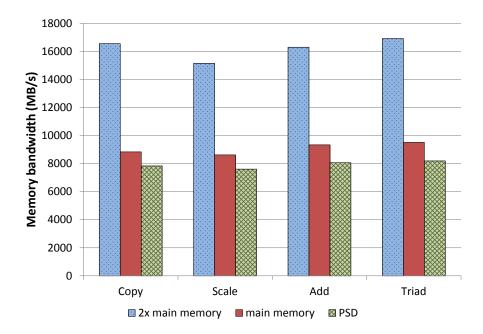

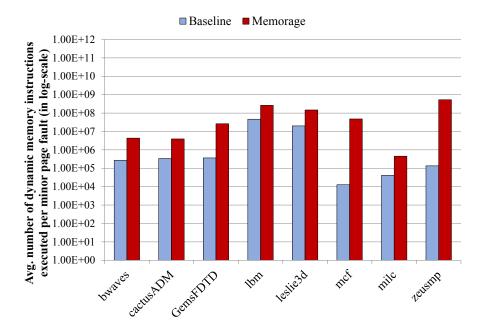

| 15 | Bandwidth performance difference between main memory and PSD               | 46 |

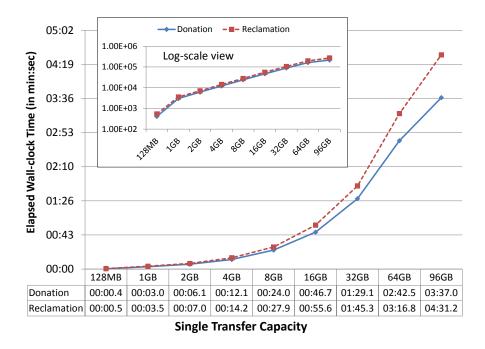

| 16 | Latencies for Memorage to offer and retrieve PSD resource                  | 47 |

| 17 | Application performance improvement by Memorage                            | 48 |

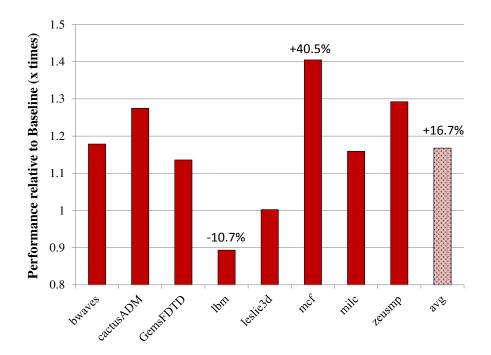

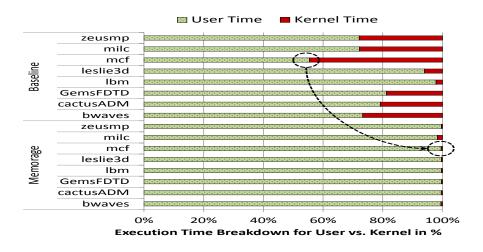

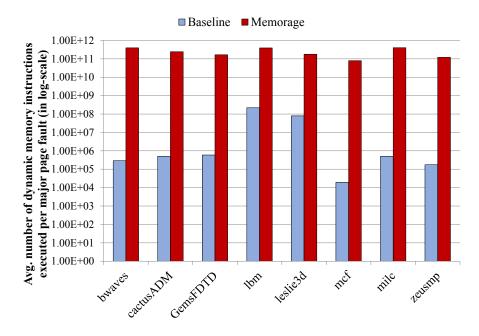

| 18 | A portion of kernel time over total execution time                         | 49 |

| 19 | Impact on the number of page faults and the increased inter-fault distance | 50 |

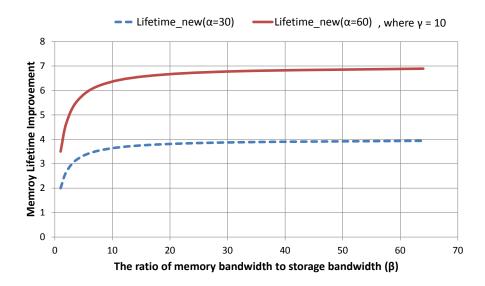

| 20 | Main memory lifetime improvement.                                          | 53 |

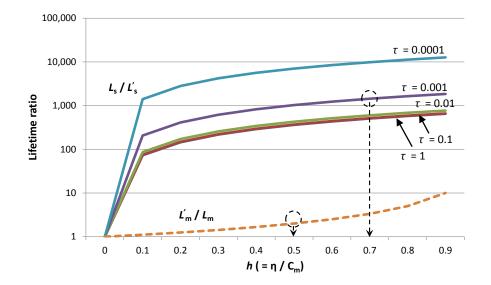

| 21 | PSD lifetime degradation                                                   | 56 |

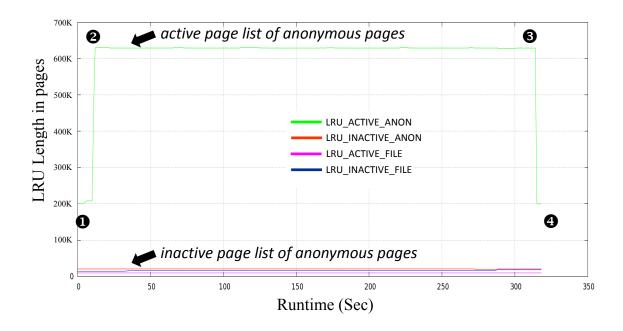

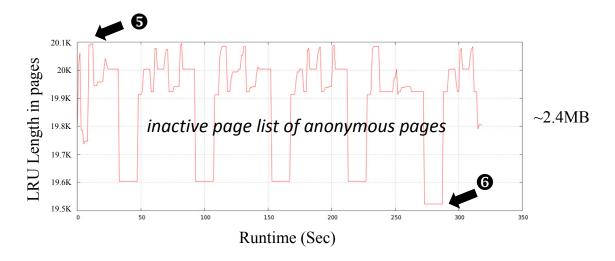

| 22 | OS LRU length change while running 429.mcf                                 | 62 |

| 23 | OS LRU length change for inactive pages while running 429.mcf $\ldots$ | 62 |

|----|------------------------------------------------------------------------|----|

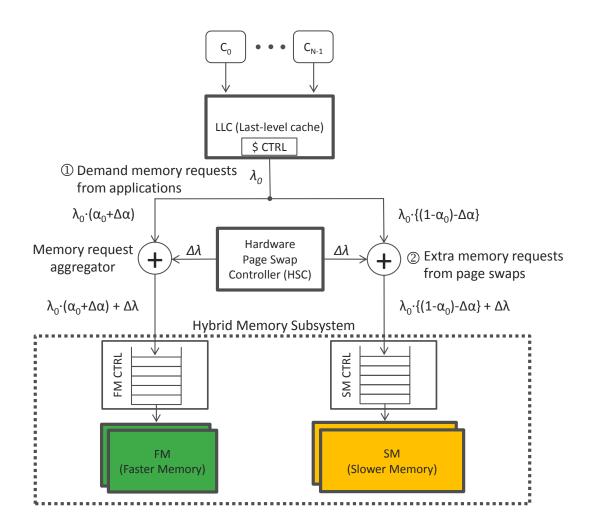

| 24 | Architecture illustration                                              | 64 |

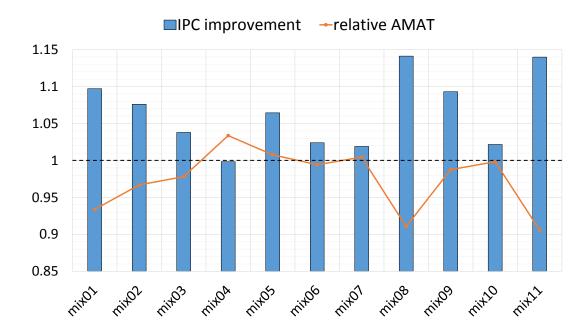

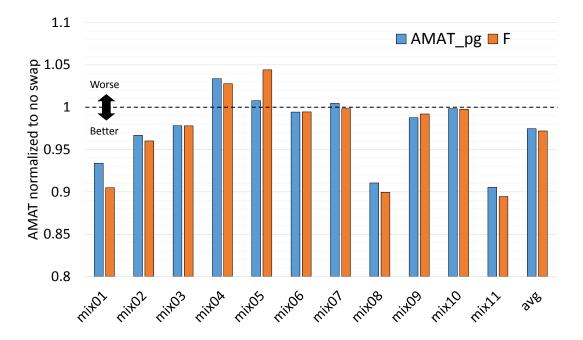

| 25 | IPC and AMAT Improvement of a static page swap                         | 72 |

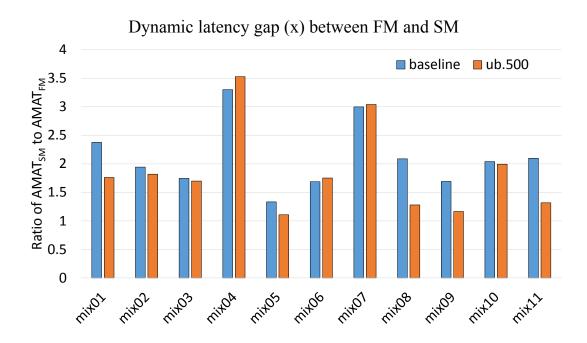

| 26 | Dynamic access latency gap $x$ between two memories                    | 73 |

| 27 | Error rate b.t.w. simulation and model                                 | 74 |

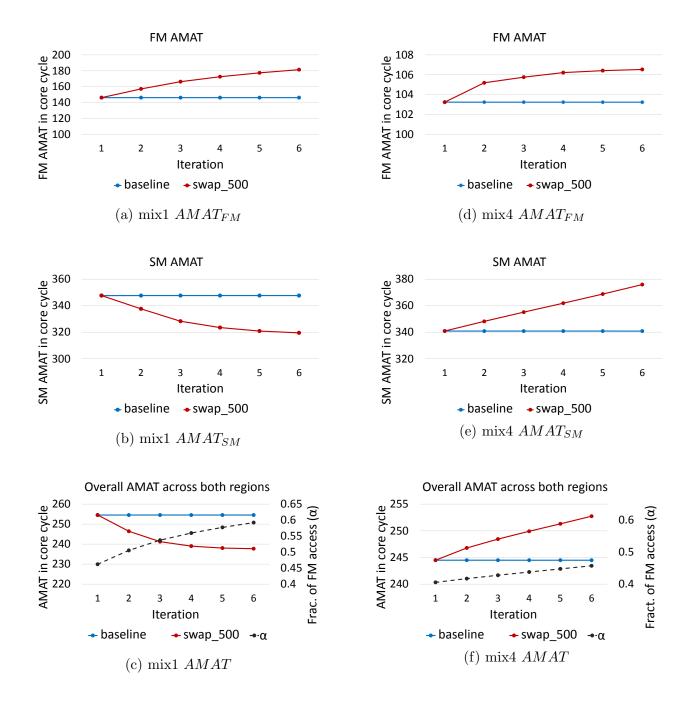

| 28 | AMAT and $\alpha$ change for mix01 and mix04                           | 75 |

| 29 | Validation of IPC and ROB fullness improvement                         | 76 |

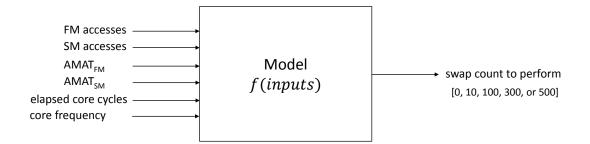

| 30 | Input/output of model-guided page swap                                 | 77 |

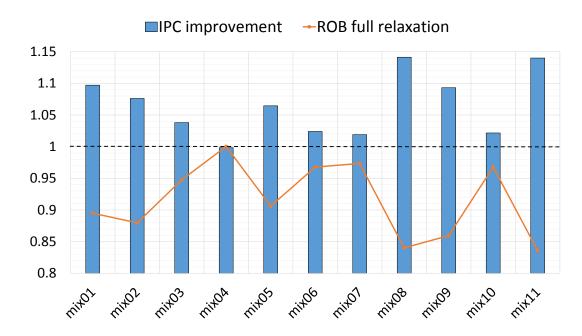

| 31 | IPC improvement                                                        | 80 |

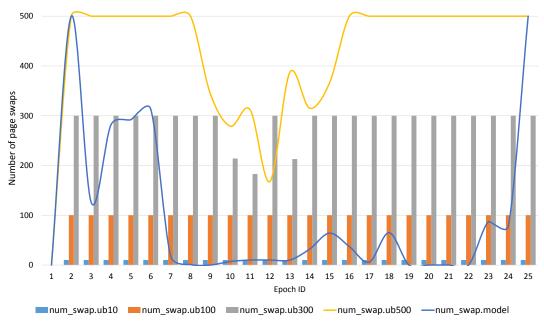

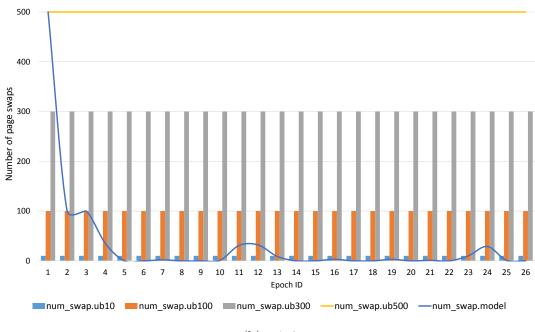

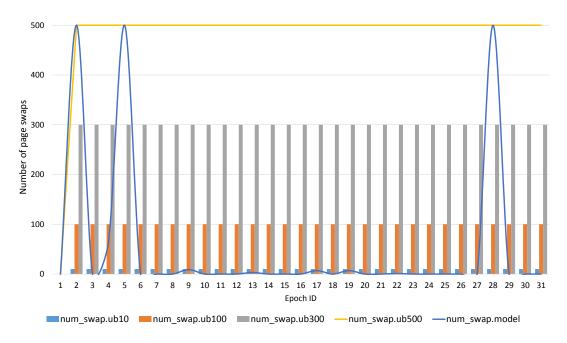

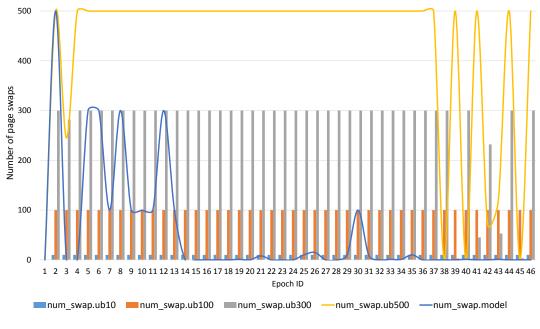

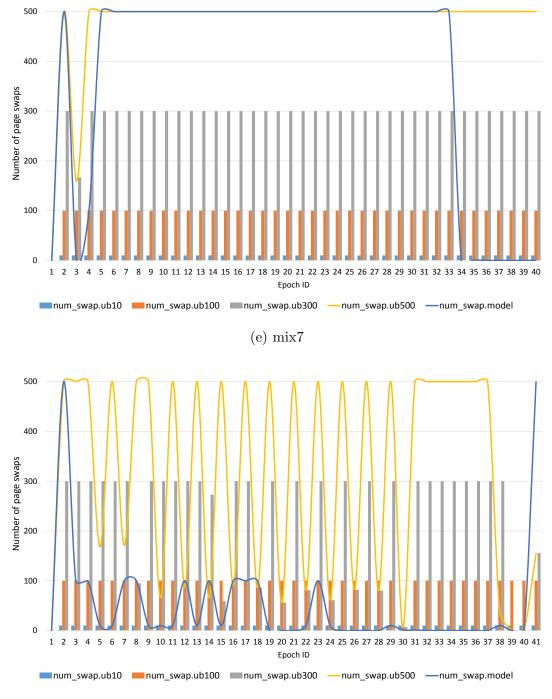

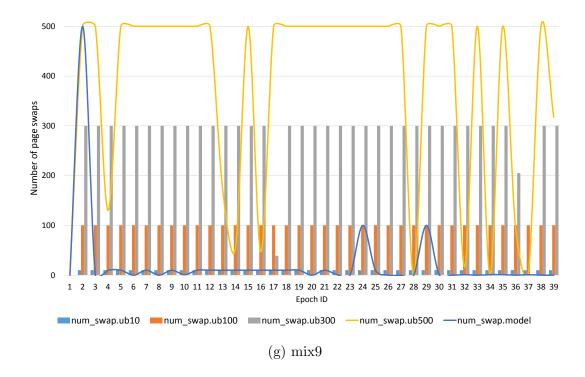

| 32 | Number of page swaps over epoch                                        | 83 |

| 33 | Number of page swaps in RaPP                                           | 84 |

| 34 | Number of page swaps over epoch for other workloads                    | 89 |

|    |                                                                        |    |

#### 1.0 INTRODUCTION

The memory hierarchy of modern computing systems beyond processor cache hierarchies has a hierarchical organization which is comprised of the system main memory and secondary storage subsystem. DRAM and HDD have been the best technologies for the main memory and storage, respectively, for the past several decades, because they provide a satisfactory performance and cost-per-bit required at each level of the hierarchy. Unfortunately, the DRAM popularity is being challenged by the scaling problem and limited power budget of DRAM technology. Similarly, the HDD keeps disappointing system designers with its slow yearly performance improvement rate and power-burning mechanical operation.

To address these problems, researchers recently started exploring the use of emerging persistent or non-volatile RAMs (shortly, PRAM, PM, or NVRAMs)<sup>1</sup> as a new medium of the memory hierarchy design. The emerging NVRAMs such as Phase Change Memory (PCM) and STT-RAM are differentiated from the traditional DRAM and HDD technology in that they are scalable, byte-addressable, persistent, and energy-efficient. Because of their many desirable characteristics other than the DRAM and HDD, a future platform is anticipated to include NVRAMs as main memory, storage, or both. However, emerging NVRAMs also have their drawbacks, and system designers must cautiously take care of them. For example, PCM technology has slower access latency than DRAM, an unbalanced read and write performance, and a limited cell endurance. Therefore, the integration of emerging NVRAMs into the conventional memory hierarchy necessitates new architectural changes and support to fully exploit their strengths while hiding the aforementioned shortcomings.

<sup>&</sup>lt;sup>1</sup>The terminology NVRAM may cause confusion because many studies have often used the term to represent NAND flash memory technology which is neither byte-addressable nor scalable. As such, to avoid the confusion, we explicitly call the NAND flash memory as an *existing* NVRAM, not *emerging* NVRAM with which this dissertation work deals. The NVRAM denotes an *emerging* NVRAM unless otherwise mentioned.

In this dissertation, we have investigated the integration of emerging NVRAMs into the existing memory hierarchy, and tackled the lack of NVRAM awareness in the traditional memory hierarchy design to improve the performance and lifetime of an NVRAM-based future system. Specifically, a primary goal throughout this study is to improve the performance of main memory, which is a dominant system component that greatly influences the overall system performance. Other advantages of emerging NVRAMs such as the energy efficiency and non-volatility are also interesting to explore, but we will leave them as our future work.

#### 1.1 RECENT TRENDS OF MEMORY HIERARCHY DESIGN

In modern computer systems, having DRAM main memory and HDD secondary storage has been a de-facto standard organization of memory hierarchy design. However, computer system designers are recently facing critical challenges on the memory hierarchy design due to the changed computing environment.

First and most importantly, there are much larger memory demands in a system than ever before. Keeping up with Moore's Law [101, 84], multi-core [85, 73] and many-core processors [45, 40, 104] with multi-level cache hierarchies have become a mainstream of processor design in the last decade, and the processors produce a great deal of memory requests to service within a given time by running multiple applications on multiple cores simultaneously. To make matters worse, the memory footprint size of applications continues to grow and is unlikely to stop increasing in the near future [69, 117]. To meet the increased memory demand without a detrimental application performance degradation, contemporary memory systems have multiple memory channels to serve numerous memory requests concurrently and independently, and exploit the memory-level parallelism among them. Also, the memory controllers associated with these memory channels have been integrated into a processor chip and the DRAM device control signals are now generated completely on chip. This integration enables cores to speed up communications between cores and memory controllers and as a result, achieve performance improvement [8, 61]. However, a continuing growth of the memory demand requires current memory systems to further increase memory bandwidth and bus speed in addition to memory capacity. To increase the memory bandwidth and link speed, researchers are exploring the use of distributed, master-slave memory controllers which control a large aggregate capacity of memory devices [28, 42]. Two factors differentiate this approach from the traditional memory system design. First, only a master memory controller is integrated into a processor, and many other smaller slave memory controllers reside on a system motherboard off-chip. Second, the interconnect among memory devices is based on a fast, point-to-point, serial link technology rather than a conventional parallel bus interconnect. While the bandwidth and link speed of a memory subsystem can be improved with the techniques just described, increasing a memory device's density is not as easy as bandwidth or links. The DRAM technology for system memory faces the scaling wall of process technology in which a DRAM cell's feature size – the minimum transistor length – cannot shrink further to increase a DRAM chip density (and hence memory capacity) in a functionally correct and cost-effective way [35].

The choice of researchers to address the DRAM scaling problem largely falls into two approaches. Some researchers are investigating three dimensional (3D) die stacking technology as a promising means to increase a per-device memory capacity [75, 97]. For example, Hyrid Memory Cube (HMC) and High Bandwdith Memory (HBM) increase a per-chip memory capacity by stacking conventional DRAM dies [30, 53]. This can also improve the performance and dynamic power consumption of the memory chips because it shortens the signaling distance, which is enabled by the through-silicon via (TSV) technology [38, 87]. However, in addition to these advantages, this approach also has some negative effects which not only increase the vertical dimension of DRAM chips but also aggravate the thermal-induced problems caused by a heat dissipation in a vertical direction [81, 116]. Although the 3D stacked DRAM technology can increase the per-chip DRAM capacity, it does not fix the more fundamental problem. The problem unable to continually scale down a DRAM cell size remains unresolved until the DRAM technology itself is replaced by another. For that reason, other researchers are actively looking for new scalable memory technologies and they think that emerging NVRAM technologies are possible candidates for DRAM replacements or complements. Since a transistor feature size of these NVRAMs can be shrunk with an advancement in process technology, emerging NVRAMs can pack more bits in the same die area without increasing chip dimension. Moreover, it is also possible to apply 3D stacking technology to the NVRAMs in order to further increase the chip capacity. For example, Intel and Micron have recently announced that their 3D XPoint ("crosspoint") memory would be ten times denser than the conventional DRAM [52]. Hence, the approach which adopts emerging NVRAMs has been considered a better solution to solve the DRAM scaling problem.

Second, in the contemporary computing environment, the power consumption has been regarded as one of the most important design considerations in a computer system design, because the cost of electricity gradually becomes a major component of the total operating expense of modern computer systems [10, 26]. However, it is not surprising that a fraction of the power consumption of the DRAM memory and HDD storage to the overall system power is already significant. For instance, previous research showed that the DRAM main memory in a server system accounted for more than 30% of a total server power consumption [80, 66]. In addition, the power consumption of the DRAM memory, while a system is idle, is rapidly increasing and becoming comparable to the dynamic power consumption. For example, in a mobile system, the DRAM power consumption exceeds 30% of a total power consumption of a system in a stand-by mode. This is due to the fact that a DRAM cell must be periodically refreshed to prevent data loss caused by the leakage current |114|. Even worse, the power consumption by the wasteful DRAM refresh operations is projected to account for 50% of the total power consumption of a memory system with future 64Gb DDR4 DRAM devices [72, 93]. Meanwhile, the HDD storage system contributes to a system power consumption of an additional 20-30% [10, 58] and exacerbates the problem of overly high power dissipation in the memory hierarchy. As such, achieving power efficiency in the memory hierarchy is another crucial problem to address, and needs to be accomplished at both the memory and storage along the memory hierarchy. Though system architects will likely continue to harness and improve the existing architectural techniques in order to reduce the power consumption for DRAM memory and HDD storage, a large power consumption within the memory hierarchy is fundamentally attributed to the underlying technologies, DRAM and HDD, to build the memory and storage system. For instance, the HDD consumes a lot of power for performing the required mechanical operations such as spinning platters and moving actuators. Therefore, building the main memory and storage system with other energy efficient technologies is better solution to reduce the power consumption of the memory hierarchy. In response of the need, emerging NVRAM technologies have been explored for constructing an energy-efficient memory hierarchy.

Third, the performance gap between DRAM memory and HDD storage system has never decreased and is growing. Even if the HDD technology's capacity improvement rate has managed to keep up with the annual growth rate of data volume to store, the performance improvement of the technology is quite disappointing. For example, the HDD's capacity has increased by 40% annually, but an annual increase in the random I/O performance of the HDD drive is as low as 2% [29]. To address this problem, recent systems attempt to diminish the performance gap with solid-state storage device (SSD) drives that are built with NAND flash memory chips. Since the NAND flash memory is faster and more energy efficient than the magnetic disk media, some of the traditional HDD spans have gradually been superseded by SSD drives. In addition, an MLC (multi-level cell) NAND flash memory has surpassed the areal density of HDD [48, 79]. As a result, the SSD in current systems is gradually taking the role of fast swap devices, file caching devices, a whole HDD replacement, and main memory extension devices [9, 83]. However, the NAND flash memory cell has a very poor endurance limit as well as scaling issue. For example, an MLC NAND flash memory cell can tolerate at most about 3000 writes 110. In addition, since there is still a large performance gap between main memory and storage even with NAND SSD, researchers believe that NAND flash memory will eventually be superseded by emerging NVRAM technologies because they provide even better operational characteristics than NAND flash for all aspects but cost per GB. As such, emerging NVRAM based SSD storage devices such as Intel's Optane are under prototype-level tests, awaiting mass production to enter the market [6, 34, 52].

In summary, DRAM and HDD have exposed their technological limits which cannot satisfy unwieldy demands of the current computing environment. To overcome the limits and meet the needs, the adoption of emerging NVRAMs into memory hierarchy is being examined carefully. Although DRAM and HDD will not suddenly disappear from the memory hierarchy, system architects are making preparations for featuring emerging NVRAM technologies in both the main memory and storage system in future computer platforms.

#### 1.2 RESEARCH OVERVIEW AND CONTRIBUTIONS

In this section, we present an overview of our research problems and contributions. We first describe an emerging NVRAM-based system model which we have studied throughout this dissertation. Then, we explain two research problems which we have addressed for the given system model, and highlight our contributions. Lastly, we describe the organization of this dissertation.

#### 1.2.1 An NVRAM-based System Platform

Before we describe the challenging problems to solve in this dissertation work, we outline the memory organization in a future NVRAM platform that we envision. According to a recent ITRS [35, 36] technology projection, a future system is expected to feature mature NVRAM technologies across the entire memory hierarchy by 2020. In particular, when the emerging NVRAM technologies become fully mature, their performance may not only be comparable to DRAM, but also accomplish a significant enhancement of per-chip density. For instance, current commercial PCM uses a single-level cell (SLC) technology which represents two states per bit (logic '0' and '1'), but it is anticipated to pack more than two logic states into a cell in the form of a multi-level cell (MLC) [7, 12, 55, 90]. When both main memory and secondary storage in a future platform are built with emerging NVRAMs, we foresee that the main memory will be built with SLC technology to provide higher performance, whereas the storage will be established by MLC technology to provide larger capacity.

When using PCM as a basic building block of the main memory, the system needs to handle an imbalanced read/write performance, and the limited lifetime of PCM cells. In particular, the  $2\times$  and  $10\times$  slower read and write latency than that of DRAM, and the limited write endurance around  $10^{6}$ – $10^{8}$  are critical problems that hamper a wide adoption of PCM main memory. To properly manage the challenges, computer architects have proposed a main memory in which a small amount of DRAM is collocated with a large capacity PCM main memory either as an OS-invisible hardware cache or as an independently addressable memory region [15, 16, 68, 91, 92]. Following this reasonable design approach, our future

Figure 1: A future platform built with a DRAM/PCM hybrid memory and a PCM storage. The IMSC stands for an integrated memory and storage controller, while the PSD denotes an emerging **P**ersistent RAM based solid state **S**torage **D**evice.

platform assumes that a small amount of DRAM may be used to mitigate the drawbacks of NVRAM, forming the main memory with heterogeneous memories.

Figure 1 illustrates our envisioned future platform and its memory hierarchy. Different from a conventional system, the dotted box shows that the platform has a main memory comprised of DRAM and PCM, a PCM storage (called PSD, a persistent RAM based solid state storage device), and a memory bus interface to connect them to a processor. Even though the figure depicts the platform with a specific type of NVRAM technology, PCM, we also envision that other emerging NVRAM (e.g. 3D XPoint) may be adopted in lieu of PCM in the architecture. However, even in this case, we envision that the organization of the memory hierarchy from the figure will remain mostly unchanged.

Hybrid main memory, not DRAM cache: if DRAM assumes the role of a memorylevel hardware cache by posing itself in front of PCM memory, this hierarchically organized memory is classified as the DRAM cache main memory. This organization has an advantage of making a hardware implementation simple and enabling the use of some familiar processor caching policies. However, it has several crucial shortcomings that may offset the benefits. For example, the given DRAM resources are invisible to the OS memory manager, possibly making their addressable space unnecessarily wasted. In addition, unlike the SRAM used for storing the processor cache's tags, the DRAM device is inappropriate for supporting fast cache tag lookup operations, which are on a critical path. On the contrary, a flat organization which equally treats DRAM and PCM can better and more flexibly utilize the given DRAM resources by exposing them to the OS for allocation and deallocation. For example, the OS may sometimes differentiate the usage of DRAM resources as a special high performing and write-absorbing addressable region, adapting to a system's needs. This flat organization is classified as a hybrid main memory. Since recent research showed that a hybrid main memory outperformed a hierarchical DRAM cache main memory [94, 16], the main memory in our future platform is organized as a hybrid main memory.

Storage connected to a fast, high bandwidth bus: Since the access latency of PSD is much faster than the traditional HDD or even NAND flash memory SSD, we believe that the PSD storage shall interface with the memory bus which is the fastest, highest bandwidth interconnect in a system platform. In this way, a system can exploit the full advantage of the unprecedentedly fast NVRAM based storage. As seen in Figure 1, the organization results in slotting storage into the same bus where the main memory resides. Even now, without a commodity PSD storage device, it is not uncommon to have a storage device on the memory bus in recent high-end server systems. For example, data center server platforms are gradually equipped with the NAND flash memory SSDs in a form of NVDIMM (Non-Volatile Dual-Inline Memory Module) [46, 21]. This enables the storage subsystem to achieve higher bandwidth and shorter latency than the conventional I/O interconnects by sharing the memory bus with DRAM main memory. In line with this trend, therefore, our studied future platform features the secondary storage, PSD, which is closely integrated with the main memory. Since the modern processor architecture does not have the north-bridge chip, the PSD-host interconnection may be one of the memory channels. However, note that the system may still include other conventional storage devices via the legacy I/O interconnect such as PCIe (Peripheral Component Interconnect Express) [18] or SATA (Serial ATA) [98].

#### 1.2.2 Problem Overview

In this dissertation, we address two imminent challenges which a given future NVRAM system model will undergo while integrating NVRAMs into conventional system architectures. The first challenge is to mitigate a dramatic, sometimes intolerable degradation of the system performance under high memory pressure. The second challenge is to improve the utilization of the small, fast DRAM resources in a hybrid main memory and boost the applications performance via page swaps.

1.2.2.1 Effective Handling of Memory Pressure The memory organization in our NVRAM system from Figure 1 adheres to the traditional memory hierarchy of the main memory and storage which is stratified by media access latency. The choice allows system designers to embrace emerging NVRAM technologies without making radical changes to current system design methodologies. On the other hand, unless we make some architectural changes, it also means that the future platform inherits an inefficiency from a conventional system to handle high memory pressure, which may considerably damage the overall system performance [9, 99]. Since modern applications constantly call for larger system memory capacity to meet the required performance and throughput targets, it is evident that future applications will put far more demand onto memory subsystems. As a result, they have a high likelihood of suffering from a worse system performance due to the increased memory pressure. For this reason, it is critically important that a system designer improves the main memory performance of future computing systems.

Meanwhile, the problem of the memory pressure is also related to the storage system. When a conventional system experiences high memory pressure, it initiates the page reclamation by moving the contents of the infrequently referenced pages from the main memory to a swap space on the secondary storage. This process is called *demand paging* or *page swapping*, and produces free pages that can be used for new page allocations from applications. However, because of a large performance gap between the main memory (DRAM) and storage (HDD), frequent external page swaps significantly impair the overall system performance, slowing down the actual execution of user applications. While a system has to reduce the number of page swaps to storage in order to prevent system performance downfall, there is no other way to avoid the swapping under high memory pressure in a conventional system. Without timely disk swaps, the unmanaged memory pressure will result in a catastrophic situation in which the OS would arbitrarily kill one or more running user applications. Since each page swap requires to access the sluggish storage device, it is important to improve the swap process so that a system can not only ensure the persistent execution of applications (instead of being randomly killed) but also avoid an intolerable performance drop under heavy memory pressure.

In addition, it is important to understand the system-level implications of the future NVRAM-based memory hierarchy compared to a conventional system. Recent studies found that the system software latency to access files on an emerging NVRAM-based storage device accounts for larger portions of overall latency than the hardware access latency to an NVRAM device [19, 58]. For instance, a conventional OS I/O scheduler anticipatorily waits for the coming requests to merge with current I/O requests in order to reduce the number of expensive HDD accesses. However, the waiting delay may be longer than the access latency of emerging NVRAM-based storage. In case that the storage access is on a critical path, the conventional I/O access behavior worsens the overall system performance. Therefore, it is justifiable that an access to NVRAM-based storage device bypasses the I/O scheduler and is directly sent to the storage.

In summary, while keeping NVRAM-awareness in mind, it is imperative to study how we can further **improve traditional page swapping mechanisms between the main memory and NVRAM-based storage in order to prevent an excessive system performance degradation under high memory pressure**. This challenge is a problem of the interplay of the main memory and storage in a future NVRAM-based system, aiming at improving the overall system performance.

**1.2.2.2 Efficient Utilization of Fast DRAM Resources** As seen in our envisioned system model from Figure 1, system designers for a future platform cannot stay with a traditional DRAM-only approach to build a system memory due to a scaling wall and power inefficiency of DRAM technology. Instead, the system memory will be a hybrid main mem-

ory being comprised of DRAM and emerging NVRAM. As such, a future system needs to carefully orchestrate the heterogeneous characteristics of the two disparate memories by supplementing a shortcoming of one memory with a strength of the other, so that the system can achieve better performance. For example, even if emerging NVRAMs are scalable and are pushing the limits of increasing the system memory capacity, an emerging NVRAM such as PCM has an imbalanced, slower read/write performance in addition to the limited cell endurance than DRAM. Especially, the access latency slower than DRAM is the NVRAM's Achilles's heel that a hybrid main memory must hide from a system's critical path.

Meanwhile, as mentioned in Section 1.1, previous research [94, 102] have proposed a hybrid memory organization in which a small amount of DRAM is collocated with a large capacity of PCM main memory as a normal addressable region. However, even though this research showed that a hybrid main memory outperformed a DRAM cache organization by providing the system software/hardware with the flexibility of a choice of the memory type for a page allocation and placement, it is believed that there are still much room to further improve the application performance in the hybrid main memory through better page placement [15, 88, 94, 102]. Therefore, a momentous challenge of a DRAM/PCM hybrid main memory is to achieve the optimal page placement for boosting application performance at runtime. A system featuring a hybrid memory should be able to determine hot pages to be placed onto a small, fast DRAM region, and cold pages to be replaced onto a large, slow PCM region. If a system places frequently referenced pages onto the slower PCM region mistakenly, it may result in a tremendous degradation of the overall system performance due to the wrong page mapping to the memory type. Hence, it is imperative to investigate efficient mechanisms that not only accurately identify hot/cold pages, but also place only the hottest pages on the small, fast DRAM region throughout a program execution.

Unfortunately, recent research on a hybrid main memory have made an over-simplified assumption in devising their page placement/replacement strategies [92, 94, 115]. Specifically, they commonly overlook the overhead of page replacement between DRAM and PCM. As a result, the implications of the OS-managed page information on the hybrid main memory have not been studied well so far. Therefore, it is important to fill up the research hole by investigating a diversity of page swap schemes at the system level, and by evaluating the effect of the page swap on the performance of a hybrid main memory. In summary, the problem to address is to improve the application performance when executing on a DRAM-NVRAM hybrid memory through better utilization of a small, fast DRAM region so as to approach the performance of running on a system with the DRAM-only main memory.

1.2.2.3 How Are Both Problems Related To Each Other? The aforementioned two problems are closely related to each other in that they are both dealing with a page swap between two system components. While the first problem from Section 1.2.2.1 addresses the inefficiency of page swapping between the main memory and storage, the second problem from Section 1.2.2.2 deals with the page swapping between two disparate memories in the main memory. In addition, both problems shall be handled through the system-aware management rather than a conventional approach to tackle them at the corresponding levels of the memory hierarchy. Whenever it is necessary to differentiate the two types of page swaps, the page swap in a hybrid main memory is called as an in-memory page swap, and the one between the memory and storage as an external page swap.

#### **1.2.3** Research Contributions

In this dissertation, we addressed the two problems described in Section 1.2.2. For each problem, the contributions of this dissertation can be summarized as follows:

**1.2.3.1 Contributions to the External Page Swap Problem** Most of this work was published in ICS 2013 [58] and CF 2011 [56].

- 1. We proposed and designed the Memorage architecture to improve the mechanism of handling high memory pressure in future NVRAM-based systems.

- 2. We implemented a prototype system of Memorage architecture in commodity Linux operating system, and evaluated it for application performance.

- 3. We developed an analytical model to investigate the effect of Memorage architecture on the lifetime of the main memory and storage system. We also showed that the model

was a useful tool to estimate the lifetime of a system or the part replacement period.

- 4. We developed a unique experimental methodology on a real platform to study future NVRAM-based systems, which was emulated with a commodity two socket server system. This compensated for the limitation of a simulation-only approach for studying emerging NVRAM-based systems.

- 5. We quantified and analyzed the OS software overhead to resolve high memory pressure through the demand-paging mechanism of state-of-the-art Linux OS. We confirmed that the OS software latency accounted for a large portion of disk swap latency.

**1.2.3.2 Contributions to In-Memory Page Swap Problem** These contributions were published in SBAC-PAD 2016 [59].

- 1. We developed an analytical model to investigate the effect of a page swap in a hybrid main memory on the application performance. Specifically, the model takes a queuingtheoretic, flow-control approach to improve page swap, and explicitly considers the profitability of a page swap, which distinguishes it from prior studies.

- 2. We compared the outcome of the model with the results from an existing architecture simulator [63] that was validated against a real hardware. Also, we showed that the model is useful to understand the effect of a page swap while analyzing the simulation results.

- 3. We proposed a model-guided, hardware-driven page swap mechanism, and evaluated its effectiveness by comparing with other page swap schemes. Furthermore, we showed how the model can be integrated into a micro-architecture.

- 4. We observed that OS-managed LRU lists is not able to identify hot and cold pages for page swap while running memory-intensive applications. This finding should guide other researchers not to blindly trust what appeared to be a conventional belief.

#### 1.3 DISSERTATION ORGANIZATION

The remaining chapters of this dissertation are organized as follows. First, we present the background of this dissertation work in Chapter 2. In Chapter 3, we describe the design and implementation of the Memorage architecture which overcomes memory pressure by an integrated management of the main memory and storage NVRAM resources, and evaluate the performance improvement endowed by the architecture. Chapter 3 also gives analytical models to qualitatively analyze the impact of the Memorage architecture on the main memory and system lifetime, and show the usefulness of the developed models with realistic usage scenarios. Chapter 3 then summarizes related work. Chapter 4 explains an efficient hardware-driven page swap in a hybrid memory, presents an analytical model to investigate the effect of page swap on the application performance. In addition, Chapter 4 evaluates the usefulness of the model as well as a model-guided, hardware-driven page swap mechanism through extensive simulations. Then, Chapter 4 presents related work. Lastly, we summarize and conclude this dissertation, and discuss the future work in Chapter 5.

#### 2.0 BACKGROUND

DRAM has been exclusively used as a platform's main memory for decades, thanks to its high performance and low cost per bit. However, DRAM main memory already accounts for 20% to 40% of the system power consumption and this fraction is growing [4]. Furthermore, according to the ITRS reports [35, 36], there is no known path for the DRAM technology to scale below 20nm. Eventually, DRAM may no longer be the best technology for main memory, with new memory technologies emerging to take over its role. In response to this problem, researchers have recently started exploring the use of emerging Non-Volatile RAM (NVRAM) as a DRAM replacement [118, 68, 92]. Another technological breakthrough is coming with emerging NVRAM technologies.

#### 2.1 EMERGING NVRAM TECHNOLOGIES

Since DRAM and HDD technology have a looming challenge of performance, scalability, and power consumption, a handful of emerging NVRAM (also called storage class memory or SCM [37]) technologies are being actively developed by industry. Table 1 lists and compares three promising NVRAM technologies with DRAM, NAND flash and HDD technologies: PCM, STT-MRAM (spin-transfer-torque magnetoresistive RAM) and ReRAM (Resistive RAM) [95, 103, 111, 106]. Basically, NVRAMs' operations are based on sensing the resistance of a cell material rather than electrical charge. PCM is considered to be the closest (among all NVRAM technologies) to mass production, with commercial and sample chips available at high densities (1 to 8 Gbits) [37, 95, 3, 24].

NVRAMs have several desirable properties in common. Unlike DRAM, they are non-

|            |                   | Latency          |                   | Program | Access | Non-     | Write            | Cell          |

|------------|-------------------|------------------|-------------------|---------|--------|----------|------------------|---------------|

|            | read              | write            | erase             | energy  | unit   | volatile | endurance        | $density^*$   |

| PCM        | 20ns              | 100ns            | N/A               | 100 pJ  | byte   | Yes      | $10^8 \sim 10^9$ | $5F^2$        |

| STT-MRAM   | 10ns              | 10ns             | N/A               | 0.02 pJ | byte   | Yes      | $10^{15}$        | $4F^2$        |

| ReRAM      | 10ns              | 20ns             | N/A               | 2 pJ    | byte   | Yes      | $10^{6}$         | $6F^{2}$      |

| DRAM       | 10ns              | 10ns             | N/A               | 2 pJ    | byte   | No       | $10^{16}$        | $(2/3)F^2$    |

| NAND flash | $25 \mu s$        | $200 \mu s$      | $1.5 \mathrm{ms}$ | 10 nJ   | page   | Yes      | $10^4 \sim 10^6$ | $4{\sim}5F^2$ |

| HDD        | $8.5 \mathrm{ms}$ | $9.5\mathrm{ms}$ | N/A               | N/A     | sector | Yes      | N/A              | $2\sim 3F^2$  |

Table 1: Comparison of emerging NVRAMs and existing memory/storage technologies [65]. \*F is the minimum feature size of a given process technology.

volatile. Compared with NAND flash, they are byte-addressable and have faster speeds. Meanwhile, NVRAMs have known shortcomings; NVRAMs like PCM and ReRAM have limited write cycles, requiring aggressive wear-leveling in write-intensive applications. Moreover, their access latencies are longer than DRAM, and in certain cases, write latency is much longer than read latency. Likewise, write energy can be disproportionately large. Therefore, system designers must pay extra caution to hide and reduce write operations [23].

Meanwhile, ITRS [35] is anticipating multi-level cell (MLC) solutions of NVRAMs. Multi-level cell (MLC) designs effectively reduce the cost per bit by packing more bits per memory cell. While a single-level cell (SLC) can represent two logic values, '0' and '1' (with two resistance levels), an MLC cell stores more than two logical symbols. Future high-density MLC NVRAMs may store more than two bits per cell [35, 27, 90, 22].

Introducing MLC NVRAM to a platform has several implications. First, MLC NVRAM will be slower than SLC NVRAM. Reportedly, MLC PCM read and write are 2 to 4 times slower [32, 91]. This is mainly due to more sensing levels for read and an iterative programming process for write [12]. The second implication is the lower write endurance of MLC NVRAM because: (1) the iterative write process accelerates cell wearing; and (2) reduced resistance margins between different symbols make it harder to precisely control programming, especially when the cell is partially worn out.

Because of its higher density and lower performance, MLC NVRAM is more suitable for use in a NVRAM-based SSD than in main memory. If a NVRAM-based SSD employs MLC NVRAM and main memory uses SLC NVRAM, there is a latency gap between the two

Figure 2: Intel and Micron's 3D XPoint Technology [52].

resources. Still, this gap ( $<10\times$ ) is not as significant as the gap between DRAM and HDD ( $10^5\times$ ). There are also techniques to opportunistically enhance the speed of MLC NVRAM, e.g., by treating an MLC PCM device like an SLC device when the system's capacity demand is low [32, 12, 91, 41].

Even if there are currently few details about its cell-level operational principle, a command set, and media characteristics, the most up-to-date progress of emerging NVRAMs has come from the announcement from Intel and Micron. Figure 2 illustrates a simplified cell structure of 3D XPoint memory [52]. It is reported that a 3D XPoint cell is three orders of magnitude faster and has three orders of magnitude longer lifetime than the current NAND flash memory. In addition, it is ten times denser than DRAM memory. All these information seems to nearly be in lined with the NVRAM technology projection.

#### 2.2 SYSTEM HARDWARE INTERFACES TO NVRAM-BASED SSD

In today's commodity platforms for consumer and enterprise applications, HDDs are the slowest hardware component connected through either a relatively slow serial ATA (SATA) or serial SCSI (SAS) interface. The SATA [98] and SAS [49] are a communication protocol that moves data between host and storage devices and use ATA and ATAPI (ATA Packet Interface) command set and a SCSI command set, respectively. Both SATA and SAS replace with a serial point-to-point connection technology their predecessors, parallel ATA and parallel-attached SCSI which revealed the limitation of data bandwidth due to parallel wires' slow signaling and cross-talk, and as a result achieve orders of magnitude faster than prior interfaces for rotating HDDs. Even if the protocols continue to improve their performance and features, with SATA and SAS, a disk access request must pass through multiple chips and buses (front-side bus to host bus adapter to SATA/SAS controller) before it reaches the storage medium, incurring long latency. For example, the most recent SAS 3.0 protocol support at most 12Gbps interface speed and SATA 3.1 specification can achieve up to 6Gbps throughput performance.

Early NAND flash SSD offerings provide a direct migration path from HDDs based on the legacy interface like SATA and SAS. According to Gartner 2010 report, SAS protocol accounts for 37%, while SATA takes about 20% out of total SSD interfaces. However, both enterprise and consumer SSDs have quickly saturated the SATA bandwidth. Recent highspeed SSDs are attached via the higher-bandwidth PCI Express (PCIe) interface [39]. To further improve the performance, the industry consortium has defined and released NVM Express (NVMe) interface for PCIe interfaced SSDs [112]. The NVMe specification allows SSD vendors to standardize SSD's host interface and make it efficient through the registerlevel communication.

Likewise, it is reasonable to predict that PSDs will interface with faster buses than PCIe because NVRAMs have superior performance to flash memory. To accommodate fast PSDs, a new higher-performance I/O standard may be created. However, in this case, or with legacy interfaces, the byte-addressability of a NVRAM-based SSD is lost. In addition, the memory bus is the highest-bandwidth bus of a platform. Hence, a NVRAM-based SSD will

Figure 3: System hardware interfaces for NVRAM storage devices.

be most likely and best co-located with NVRAM memory modules on a platform's memory bus.

We expect that future platforms will continue supporting legacy PCIe and SATA interfaces. It is quite conceivable that multiple heterogeneous storage devices may co-exist. For instance, the HDD could provide ample capacity to store large file data while the NVRAMbased SSD provides fast I/O for hot data. A particular storage configuration will be chosen based on the cost, performance and capacity trade-offs made by the user.

Figure 3 displays possible hardware interfaces <sup>1</sup> to attach a storage device to current system platforms. Conventional storage systems are connected to host CPUs via Platform Controller Hub (PCH). Each interface bus is marked by a circled number in chronological order, and higher number also implies higher throughput performance.

<sup>&</sup>lt;sup>1</sup>Even though we showed all storage interfaces in today's systems, note that we do not exclude the possibility that new interfaces between 3 and 4 may be defined. In this case, however, we classify them as variants of PCIe interface because their hardware capabilities are inferior to 4.

#### 2.3 OS MEMORY MANAGEMENT AND I/O STACK

Our descriptions in this section focus on Linux OS because of its relevance to our experimental study. However, other modern OSes also implement the key concepts explained here possibly with some modifications.

#### 2.3.1 OS Memory Management

User applications request necessary memory resources via system calls such as malloc() or *mmap()* which are served by OS virtual memory manager (VMM). Basically, all physical memory resources (or pages) on a system are registered as free pages into buddy allocators after a kernel gets allocated essential memory resources during the boot process. Since the kernel classifies physical page frames into zones with different properties (eg. DMA zone) for it purpose, each zone has its own buddy allocator [17, 74, 77]. Then, the zoned buddy allocator takes a responsibility of de/allocating memory pages from its zone. However, if there is no free page to allocate under high memory pressure, OS VMM performs the page reclamation to make room for the new page. Since the new page allocation request causes a page fault, VMM moves to swap space anonymous pages which is not backed by file storage or simply de-allocate clean mapped pages backed by file storage in the process of page fault handling. The manager detects the status of scant free memory by three thresholds or watermarks, and recovers the level of a violated watermark through iterative page reclamation operations. At the end, the buddy allocator produces free pages for new allocations. Unfortunately, a page fault handling involved with page swap operations takes a long time to execute, and thus significantly degrades the system performance. This is due to the fact that it has to not only perform page table walking and manipulation, but also access slow storage device.

Meanwhile, Linux VMM manages the information of page reference recency, modification, and others in page tables. When a page reclamation and swap is required, VMM refers to this information in order to select less important pages for disk swap. Specifically, Linux VMM maintains two types of LRU lists, the active list and the inactive list, for anonymous and file

Figure 4: Linux I/O software stack. An I/O request from user applications in conventional systems goes through a full layer of software stacks before storage devices can service it.

pages, respectively. While anonymous pages are allocated for head, stack, and copy-on-write, file pages are for file-backed data such as binaries and data files. These lists keep track of hot and cold pages that have been recently referenced and not referenced, respectively [77]. Thus, VMM swaps out pages belonging to inactive page lists when **pageout** swap routine is called. However, if the inactive lists do not have enough number of pages to swap out, VMM first replenishes the lists by moving pages from active list to inactive list, then moves pages in inactive lists to a swap area as usual.

#### 2.3.2 OS I/O Stack

Figure 4 displays I/O software stack in Linux. Since the traditional OS I/O software stack and file systems have been designed for rotating HDDs, storage optimizations are mainly devoted to reducing disk seek time through efficient I/O scheduling. For example, a read or write request in a conventional OS I/O stack must first go to the block I/O layer that is responsible for I/O scheduling. The request then waits (in anticipation) for other requests that can be merged together to reduce accesses to the slow HDD ( $\bigcirc$ ). The Linux's default "completely fair queuing" (CFQ) scheduler [17] does this. By comparison, SSDs without mechanical rotation benefit little from such HDD-centric optimizations. Depending on the target configuration, it makes sense to bypass the block I/O scheduler and the block device driver (e.g., SCSI subsystem) all together (2). As a result, system designers have customized the OS I/O software stack with SSDs in mind and design new file systems [19, 54, 99]. This trend of retrofitting I/O stack can be also found even with PCIe PCM SSD [6]. Since PSDs are byte-addressable and even faster than SSDs, further changes to I/O stack can occur. For example, Linux's DAX (Direct Access) enabled file system bypasses OS file cache and directly accesses data on block I/O device, further reducing storage access latency [51] (3).

#### 2.4 OS PAGE MOVEMENT TECHNIQUES

There has been extensive research on page movement techniques in the context of a classic shared memory multi-processors (SMPs) [67, 86, 107]. The latency non-uniformity in SMPs is incurred by a CPU-to-memory affinity rather than memory media disparities like a hybrid memory. Due to a distance difference from CPUs to memory modules, a process running on a core in a CPU socket experiences different memory access latency from when the process is rescheduled to a core in another socket. To dynamically exploit the access latency difference in a memory system, a system can move a frequently accessed, distant page to a location closer to a core executing the program. This is very analogous to the need of page swap in a hybrid main memory.

A page movement in today's systems requires the OS to manipulate a page table in order to update the memory mapping information of pages in the movement. For this, the VMM first disables the write permission to the two pages to be swapped, whereas write access to other pages are not banned. Next, a (destination) page to accommodate an incoming page is allocated and mapped to an address. Once page data transfer completes, the original pages in the page movement will be unmapped, and released to a memory pool. Last, the write permission of the pages is reactivated. In current Linux implementation, VMM's **migrate\_pages** and **move\_pages** system calls can perform this page movement. The former

```

long migrate_pages (

int pid,

// process ID

unsigned long maxnode,

// max number of new locations

const unsigned long *old_nodes, // old locations

const unsigned long *new nodes // new locations

);

long move_pages (

int pid,

// process ID

unsigned long count, // the number of pages to move

void **pages,

// array of pointers to pages to move

const int *nodes,

// array of new locations

int *status,

// array of move result status per page

// specifying type of page to move

int flags

);

```

Figure 5: Linux's page movement system calls.

is used for moving all pages associated with the specified process ID to a new location, while the later is used for moving the given list of pages to the specified new location. Figure 5 displays the APIs for these system calls. For this dissertation work, it is worthy of seeing what kind of information the OS expects for the software-based page movement.

Unfortunately, this OS-driven process may sometimes bring about a considerable overhead by frequent TLB shootdown [108] and cache line flushes which may offset the benefit of a page movement. In addition, not all requested page movements succeed, and any failed trial fruitlessly incurs extra overhead.

## 3.0 UNIFIED MANAGEMENT OF SYSTEM'S MEMORY AND STORAGE NVRAM RESOURCES

In this chapter, we present our noble observations on an envisioned NVRAM-based future system to motivate this work. Using them, then, we propose and evaluate Memorage architecture to better handle heavy memory pressure in the future system. Also, we examine the impact of Memorage architecture on the system-level lifetime via an analytical modeling.

#### 3.1 MOTIVATION AND A STUDIED SYSTEM ARCHITECTURE

As described in Chapter 1 earlier, we envision in this study that a *future emerging NVRAM* based systems will have to manage the NVRAM main memory and the NVRAM storage resources in an integrated manner to make the best performance and cost trade-offs. In a realization of the idea, the physical memory resource manager will need to book-keep the status of the storage resources as well as the memory resources. The integration of resource management will allow the system to flexibly provision the available resources across the memory and storage boundary for better performance and reliability. The following technology trends support this argument:

# • There will be little device characteristic distinctions between main memory resources and storage resources

Note that there are independent research and development efforts on scalable NVRAM main memory and fast "Persistent RAM solid-state Storage Devices" (or "PSDs") using highdensity NVRAM chips. If scaling predictions of ITRS [35] are realized (from 22nm flash half pitch in 2011 to 8nm in 2024) and given that the PCM cell density is comparable to that of NAND flash (see Table 1), a single PCM die can pack 256 Gbits by year 2024. This chip capacity, estimated conservatively, enables building a small form-factor memory module carrying hundreds of gigabytes. Stacked multi-chip packaging techniques have matured and packages containing 8 to 16 chips are already commercially feasible [96].

In addition, fully exploiting the high bandwidth of the NVRAM modules in a platform requires that all the capacity be interfaced via the main memory bus. Researchers have already explored the benefit of placing flash memory on the main memory bus [62]. Suppose that both main memory and system storage are comprised of NVRAM and are on the same memory bus; then the main memory and storage resources are no more heterogeneous than DRAM and hard disk drive (HDD) in today's systems, but are quite homogeneous. This offers an unprecedented, practical opportunity for the system to manage the resources in an integrated manner.

## • Reducing software overhead out of an overall I/O service latency becomes even more important than in the past

Many software artifacts have been incorporated in a conventional OS to deal with the slow, block-oriented HDDs. For example, complex I/O scheduling algorithms have been implemented in the block I/O layer of the Linux OS [17]. If the current software stack is unchanged, however, the major difference in data access latency between NVRAM main memory and a PSD will be dominated by the overhead of the software stack that handles I/O requests. For example, a 4-KB data transfer between a PSD and main memory can be done in hardware in a microsecond, whereas the software overhead of an I/O operation—from a user I/O request to the OS file system to the block I/O layer to the device driver and vice versa—amounts to tens of microseconds [68, 65, 19, 27]! This software overhead has been acceptable because the same data transfer operation with a HDD typically takes milliseconds and the software overhead is only a fraction of the latency.

## • Storage density grows exponentially and a typical user underutilizes the available storage capacity

HDD and NAND flash density improvement rates have outpaced Moore's Law [47, 64]. While there are different storage usage scenarios such as PC, embedded and server environments,

Figure 6: NVRAM main memory and a PSD share the memory bus. IMSC represents Integrated Memory and Storage Controller. Note that not all storage devices in this figure have to be present simultaneously.

the entire capacity of a given storage device is rarely filled up, leaving some space unused during its lifetime. Agrawal et al. [5] measured the file system fullness and quantified the annual file system size growth rate to be only 14% on average. Moreover, the storage administrator usually performs careful storage capacity provisioning to ensure there is room for the stored data set to grow. Provisioned but unused storage capacity is, in a sense, the lost resources.

Based on the above observations, we make a case for *Memorage*, a system architecture that utilizes the system-wide NVRAM resources in an integrated manner in order to efficiently mitigate the performance degradation of a system under high memory pressure. Figure 6 illustrates a studied future system platform, which features NVRAM-only <sup>1</sup> main memory and PSD storage device on a memory bus.

<sup>&</sup>lt;sup>1</sup>The main memory may be a hybrid memory in the near future. However, Memorage with NVRAM-only main memory foresees the long-term research, when NVRAM technology becomes mature and achieves the performance comparable to DRAM.

Figure 7: Illustration of Memorage concept. Memorage dynamically expands or shrinks the capacity of main memory (denoted "MM") and PSD on demand.

### **3.2 THE MEMORAGE ARCHITECTURE**

In this section, we propose Memorage architecture and explain its underlying principles and design goals. In addition, we detail the design and implementation of the proposed Memorage architecture which can effectively be integrated into a conventional memory hierarchy.

# 3.2.1 Memorage Philosophy

Memorage tackles the inefficiency of NVRAM resource utilization by collapsing the traditional static boundary between main memory and storage resources (see Figure 7). The Memorage approach is motivated by the fact that fast NVRAM storage resources will likely remain underutilized if a system is designed based on the traditional dichotomy of memory and storage. It also enables us to mitigate the problem of NVRAM's limited endurance with a global wear-leveling strategy that involves all available NVRAM resources.

Storage capacity in a drive has increased with the improvement in storage density. Studies like Meyer et al. [82] and Agrawal et al. [5] show however that storage utilization has not been growing with the increasing storage capacity. Meyer et al. analyzed vast file system content data collected for over four weeks in 2009 in a large corporation. Agrawal et al. collected their data from 2000 to 2004 in the same company. According to their results, storage capacity has increased by almost two orders of magnitude, but the mean utilization of the capacity has actually decreased by 10% from 53% to 43%. Furthermore, 50% of the users had drives less than 40% full while 70% of the users had their drives no more 60% full. These studies clearly suggest that a storage device in a system is likely to have *substantial unused space* during its lifetime.

The Memorage architecture aims to effectively address the above wastefulness by suggesting the following principles:

## 1. Don't swap, give more memory

Under high memory pressure, a conventional OS virtual memory (VM) manager swaps out previously allocated pages into the storage to respond to memory requests. Significant performance penalty is incurred when frequent swap in and swap out operations occur. In Memorage, main memory borrows directly accessible memory resources from the PSD to cope with memory shortages. Offering more memory capacity effectively eliminates the need for costly swap operations.

## 2. Don't pay for physical over-provisioning

To guarantee reasonable lifetime, reliability and performance of the NVRAM main memory, robust wear-leveling and garbage collection with over-provisioned capacity is required. Flash SSDs commonly resort to over-provisioning of as much as 20% of the (advertised) capacity. Over-provisioned capacity is typically hidden from the user, and may remain inefficiently utilized. In Memorage, as long as capacity planning of the PSD allows, the PSD can donate its free capacity to the main memory to relax the limited write endurance problem and facilitate wear-leveling. Effectively, Memorage offers "logical" or "virtual" over-provisioning without hiding any capacity from the user or incurring additional cost for physical overprovisioning.

To summarize, we expect two important benefits from the Memorage principles. First, by granting more directly accessible memory capacity to the physical memory pool (principle 1), the system can decrease the frequency of page faults. Because NVRAM is orders of magnitude faster than traditional HDDs, avoiding the software overheads of page faults can lead to significant performance improvement. Second, by dynamically trading resources between the main memory and the storage (principles 2), lifetime becomes more manageable because the write traffic to the main memory and the storage can be re-distributed with software control.

# 3.2.2 Key Design Goals

In this subsection, we discuss three design goals that have guided the design and implementation of Memorage.

## • Transparency to existing applications

It is impractical to require re-compiling all existing applications for a new system feature to be enabled. To ensure its seamless adoption, we encapsulate Memorage inside the OS kernel and do not modify application-level interfaces. While not required, the user may configure Memorage parameters to tune resource management policies according to particular systemlevel objectives. Our goal is to have a Memorage system autonomously and intelligently manage the underlying NVRAM resources, considering user preferences.

#### • Small development efforts

Meeting the transparency goal may impose additional complexities on system software design, especially the memory and storage subsystem of an OS. The complexities hinder the fast adoption of Memorage architecture. Thus, we aim at avoiding long development time by reusing the existing system software infrastructures whenever possible. In Section 3.3.1, we describes our prototype design in detail so that other researchers and developers can easily implement Memorage in their systems.

### • Low system overheads

An implementation of Memorage may incur performance and memory overheads because it adds a new layer of resource control. The performance overheads are incurred when NVRAM resources are transferred from the storage side to the main memory side, and vice versa. The space overheads come from book-keeping and sharing resource usages across the two sides. In this work, we design a prototype Memorage system by reusing kernel-level functions and data structures to achieve this goal. We note that the performance overheads are paid fairly infrequently, only when NVRAM resources are exchanged under memory pressure situations.

# 3.2.3 Memorage Design and Implementation

We now discuss our Memorage prototype, integrated in a recent Linux kernel. The prototype Memorage system runs on a non-uniform memory architecture (NUMA) platform with a large system memory that emulates a PSD, as will be explained in Section 3.3.1. The general strategies used in our implementation will also apply to other OSes.

We focus on how the first principle—*Don't swap, give more memory*—is incorporated in our implementation because today's Linux kernel has no provisions for memory wearleveling. However, we will separately study via analytical modeling how Memorage helps improve the efficiency of wear-leveling in Section 3.4. That said, incorporating the first Memorage principle requires two major changes in an OS. First, it requires managing the status of NVRAM resources in both memory and storage together. Second, it calls for developing a strategy to dynamically expand and shrink the main memory capacity. We subsequently expatiate our design approaches to accommodate the two changes.

**3.2.3.1** Managing Resource Information As we discussed in Section 3.2.2, the Memorage prototype extensively reuses existing memory management infrastructures of Linux in order to reduce the development efforts. For example, key data structures to keep track of the state of a node (representing per-CPU memory resources), a zone (expressing a memory region in a node) or a page remain unchanged. The existing node descriptor, *struct pglist\_data*, still contains the information of a node that includes the Memorage zone, while the zone descriptor, *struct zone*, keeps holding the information of the list of active and inactive pages in the Memorage zone. Besides, the status of a page is recognized by the page descriptor, *struct page* as usual (see [17] for more details).

To acquire the status information of resources in the Memorage zone, virtual memory manager works closely with the PSD device driver and the file system. The PSD device driver builds on a custom ramdisk driver to emulate the PSD with the system DRAM memory, and can perform both block I/O operation and page-level allocation from the designated node resources. In addition, it supports popular file systems such as ext3/ext4, and POSIX file access APIs as a traditional storage block driver. It takes as input the size of the Memorage zone, the resource amount to lend/reclaim at a time, and the memory node ID to contain the Memorage zone. The PSD device driver utilizes the Linux memory hotplug facility [1], which significantly simplifies the task of updating the OS-level information of available memory resources as they are traded between the main memory and PSD storage.

#### **PSD** resource detection

An important design question that arose is: When should the Memorage zone be prepared? Linux for the x86 architecture obtains the memory resource information from the BIOS during the boot process and sets the memory related system-wide parameters like maximum number of page frames accordingly. To keep a system's resource discovery process consistent, our prototype system assumes that PSD resources are similarly detected at boot time and the OS book-keeps the PSD's physical resource information in addition to system memory resources. However, resource information relevant to PSD is marked to be unavailable on loading the PSD device driver that is also performed as a part of the boot process. As a result, OS's VM manager has the full information of PSD resources but cannot allocate a page from it until Memorage explicitly pumps in the predefined amount of NVRAM resources from the PSD under memory pressure. Our prototype PSD device driver carries this out by hot-removing PSD region (which is a memory node) during its initialization. However, the offlined PSD region is logically removed from VM manager rather than physically from the system.

## File system metadata exposure

When Memorage donates some capacity to main memory by transferring its resource to VM manager, the file system must catch and log such resource allocation events so that it does not allocate donated resources for new file data. For further illustration, Figure 8 depicts the basic on-disk layout of a file system (e.g., ext3) as well as its interaction with the buddy allocator system. The file system partitions the storage space into block groups, and each block group is comprised of *superblock*, group descriptors, data block bitmap, inode bitmap, inode table and data blocks. From each block group information, the following field information should be passed to the buddy memory allocator:

Figure 8: Memorage exposes free data blocks from a (mounted) file system to VM manager as a new zone. Buddy allocator treats the new Memorage zone the same way as other zones.

- 1. *Group descriptors* that specify the status of individual block groups such as the number of free blocks;

- 2. Data block bitmap that identifies which blocks within a block group are free blocks; and

- 3. Data blocks that stores file data in the file system.

The inode-related information does not have to be changed because blocks or pages in the PSD are free blocks with no file data on them. Given this information from the file system, the buddy allocator manages the Memorage zone just as other zones during memory allocation and deallocation. In our prototype, the Memorage zone is conceptually a node in the NUMA model that most modern operating systems support. Thus, the memory allocator can utilize the fact that cost of accessing main memory nodes may be different according to the geometric distance from the requesting core.

## Clean up on system reboot

In response to a normal system shutdown request, Memorage mandates the file system to nullify the bitmap information previously marked for PSD donations because we assume memory data lifetime is over along with system reboot. By doing so, a file system consistency checker (e.g., fsck) can avoid reporting unwanted check result in a subsequent boot process. However, to address unexpected power failure, our prototype further needs to modify current fsck implementation, letting it invalidate the inconsistent bitmap information rather than trying to fix them up and slowing down the boot process.