# AUTONOMOUS SUPPORT AND EFFICIENCY OPTIMIZATION OF SERIES RESONANT CONVERTER

by

## **Christopher Thomas Scioscia**

Bachelor of Science in Electrical Engineering, University of Pittsburgh, 2014

Submitted to the Graduate Faculty of

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

2017

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

Christopher Thomas Scioscia

It was defended on

June 12, 2017

and approved by

Brandon M. Grainger, PhD, Research Assistant Professor Department of Electrical and Computer Engineering

Gregory F. Reed, PhD, Professor Department of Electrical and Computer Engineering

Zhi-Hong Mao, PhD, Associate Professor Department of Electrical and Computer Engineering

William E. Stanchina, PhD, Professor Department of Electrical and Computer Engineering

Thesis Co-Advisor: Brandon M. Grainger, PhD, Research Assistant Professor Thesis Co-Advisor: Professor Gregory F. Reed, PhD, Professor Department of Electrical and Computer Engineering Copyright © by Christopher Thomas Scioscia

2017

## AUTONOMOUS SUPPORT AND EFFICIENCY OPTIMIZATION OF SERIES RESONANT CONVERTER

Christopher Thomas Scioscia, M.S.

University of Pittsburgh, 2017

As the electrical grid moves towards modernization and the prevalence of DC architectures, microgrids, and distributed generation increases, the interactions and performances of these DC topologies must be understood and evaluated. Focusing on microgrids, these independent electrical entities typically have distributed generation, local load, some form of energy storage, and a connection with the electrical grid. When instabilities arise on either the grid or the microgrid, the connection can be severed, allowing the microgrid to operate self-sufficiently. While the microgrid is in isolation, resource management is of primary importance as the grid is no longer electrically connected to make up deficits in power that might arise.

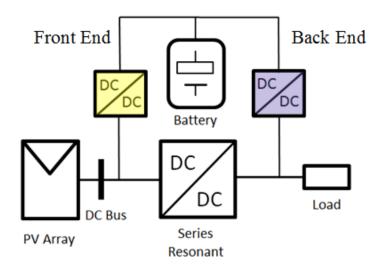

This research focuses on utilizing a power management algorithm to maximize the efficiency of an isolated microgrid, as to minimize the losses of the system while limited resources are available. The microgrid consists of photovoltaic generation, local load, a series resonant load converter, and energy storage. The energy storage is placed in parallel with the load converter and is interfaced via bi-directional converters to the front and back ends of the load converter. Utilizing the energy storage as a functional load or source, the operational point of the load converter can be adjusted and consequently the efficiency of the converter can be optimized.

In the work that follows, the design, control, and operation of the aforementioned system are detailed, as well as the autonomous power management logic, which governs the allocation of microgrid resources for optimization of the load converter and thus the microgrid system.

## TABLE OF CONTENTS

| AC  | KNO | WLED  | GEMENTS                           | .XV |

|-----|-----|-------|-----------------------------------|-----|

| 1.0 |     | INTR  | ODUCTION                          | 1   |

| 2.0 |     | SERI  | ES RESONANT CONVERTER             | 5   |

|     | 2.1 | (     | CONVERTER OVERVIEW                | 5   |

|     | 2.2 | (     | CONVERTER DESIGN                  | 7   |

|     | 2.3 | S     | SRC CONTROL METHODS               | 8   |

|     |     | 2.3.1 | Frequency Control                 | 8   |

|     |     | 2.3.2 | Conduction Angle Control          | 8   |

|     |     | 2.3.3 | Current-mode Control (ASDTIC)     | 9   |

|     |     | 2.3.4 | Optimal Trajectory Control        | 9   |

|     | 2.4 | (     | CONTROLLER DESIGN                 | 9   |

|     |     | 2.4.1 | Hybrid Control                    | 11  |

|     |     | 2.4.2 | PI Controller Tuning              | 14  |

|     |     | 2.4.3 | Dead Time                         | 22  |

|     | 2.5 | S     | SIMULATION AND VERIFICATION       | 23  |

|     | 2.6 | S     | SRC PERFORMANCE EVALUATION        | 27  |

|     | 2.7 | (     | COMPONENT SIZING AND REEVALUATION | 30  |

|     |     | 2.7.1 | Power Electronics Sizing          | 30  |

|     |     | 2.7.2 LC Tank Sizing                        | 31 |

|-----|-----|---------------------------------------------|----|

|     |     | 2.7.3 SRC Performance Reevaluation          | 32 |

| 3.0 |     | BATTERY INTERFACING CONVERTER               | 34 |

|     | 3.1 | BIDIRECITONAL BUCK-BOOST CONVERTER OVERVIEW | 34 |

|     | 3.2 | BIDIRECITONAL BUCK-BOOST CONTROL METHODS    | 36 |

|     | 3.3 | BATTERY DESIGN                              | 37 |

|     | 3.4 | BIDIRECITONAL BUCK-BOOST CONVERTER DESIGN   | 38 |

|     |     | 3.4.1 Back End Battery Converter            | 39 |

|     |     | 3.4.2 Front End Battery Converter           | 41 |

|     | 3.5 | CONTROLLER DESIGN                           | 44 |

|     |     | 3.5.1 Back End Converter PI Design          | 45 |

|     |     | 3.5.2 Front End Converter PI Design         | 48 |

|     |     | 3.5.3 Dead Time                             | 50 |

|     | 3.6 | SIMULATION AND VERIFICATION                 | 51 |

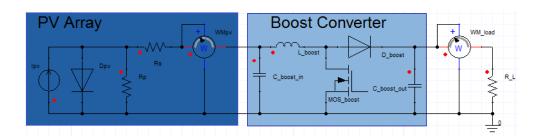

| 4.0 |     | PHOTOVOLTAIC ARRAY                          | 56 |

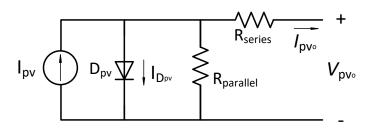

|     | 4.1 | PV MODEL                                    | 57 |

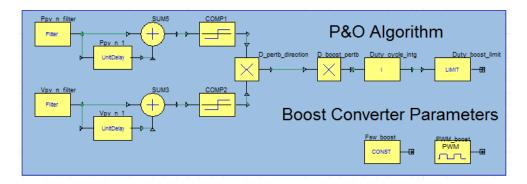

|     | 4.2 | MAXIMUM POWER POINT TRACKING                | 61 |

|     | 4.3 | PV ARRAY BOOST CONVERTER                    | 63 |

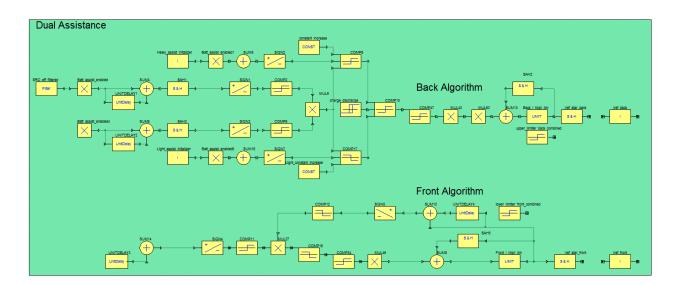

| 5.0 |     | ASSISTANCE LOGIC                            | 66 |

|     | 5.1 | FRONT ASSISTANCE LOGIC                      | 67 |

|     | 5.2 | BACK ASSISTANCE LOGIC                       | 70 |

|     |     | 5.2.1 Strong (Ideal) Source                 | 72 |

|     |     | 5.2.2. Weak (Non-ideal) Source              | 74 |

|     | 5.3  | DUAL ASSISTANCE                      | 76  |

|-----|------|--------------------------------------|-----|

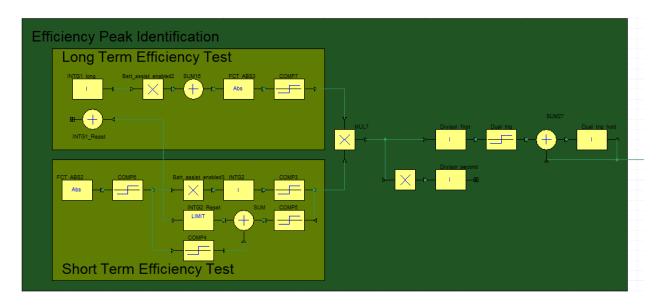

|     | 5.4  | SUPPLEMENTARY ALGORITHM FEATURES     | 78  |

|     |      | 5.4.1 Efficiency Peak Identification | 79  |

|     |      | 5.4.2 Voltage Support                | 82  |

| 6.0 |      | RESULTS                              | 83  |

|     | 6.1  | LIGHT LOAD TEST CASE                 | 84  |

|     | 6.2  | HEAVY LOAD TEST CASE                 | 89  |

|     | 6.3  | PV DROPOUT TEST CASE                 | 94  |

| 7.0 |      | CONCLUSION                           | 101 |

| API | PENI | DIX A                                | 102 |

| API | PENI | DIX B                                | 108 |

| RIR | LIO  | GRAPHY                               | 114 |

## LIST OF TABLES

| Table 1. SRC Converter Parameters                                | 7  |

|------------------------------------------------------------------|----|

| Table 2. Frequency Boundaries for SRC Hybrid Control             | 12 |

| Table 3. Frequency Ranges for SRC Hybrid Control                 | 13 |

| Table 4. Operating Cases for PI Tuning                           | 16 |

| Table 5. Gain and Phase Margins for PI Operating Cases           | 19 |

| Table 6. SRC PI Controller Gains                                 | 20 |

| Table 7. Verification Cases for Operation of SRC                 | 24 |

| Table 8. Constraints for SRC Semiconductor Devices               | 31 |

| Table 9. Constraints for SRC Tank Components                     | 32 |

| Table 10. Back Buck-Boost Converter Parameters                   | 40 |

| Table 11. Critical Inductance for Back Buck-Boost Converter      | 40 |

| Table 12. Front Buck-Boost Converter Parameters                  | 43 |

| Table 13. Critical Inductance for Front Buck-Boost Converter     | 43 |

| Table 14. Back Converter PI Gains                                | 46 |

| Table 15. Front Converter PI Gains                               | 49 |

| Table 16. Verification Cases for Operation of Back End Converter | 51 |

| Table 17. Verification Simulation Results for Back End Converter | 52 |

| Table 18. Canadian Solar CS6P-260M Panel Characteristics                   | 59  |

|----------------------------------------------------------------------------|-----|

| Table 19. PV Boost Converter Parameters                                    | 64  |

| Table 20. System Control Layers                                            | 67  |

| Table 21. Example Efficiency and Perturbation Thresholds for EPI Operation | 80  |

| Table 22. Infineon FF11mR12W1M1_B11 Half-Bridge SiC MOSFET Module          | 108 |

| Table 23. ON Semiconductor MBR20H150CTG Power Recftifier Si Diode          | 109 |

| Table 24. International Rectifier AUIRFR4615 HEXFET Si Power MOSFET        | 111 |

| Table 25. Infineon IPZ60R040C7 CoolMOS C7 Si MOSFET                        | 112 |

## LIST OF FIGURES

| Figure 1. Isolated Microgrid under Study                                                                            |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 2. Series Resonant Converter                                                                                 |

| Figure 3. Switching diagram of SRC hybrid control scheme from max load (top left) to very light load (bottom right) |

| Figure 4. SRC Frequency Response under Heavy Conditions                                                             |

| Figure 5. SRC Frequency Response under Boundary 1 Conditions                                                        |

| Figure 6. SRC Frequency Response under Boundary 2 Conditions                                                        |

| Figure 7. SRC Frequency Response of PI Compensated Control-to-Output                                                |

| Figure 8. Nyquist Diagram of SRC PI Compensated Control-to-Output                                                   |

| Figure 9. SRC Capacitor Output Voltage Regulated to 80 V during Verification Cases                                  |

| Figure 10. Output of SRC PI Frequency Controller during Verification Cases                                          |

| Figure 11. Measured SRC Phase Shift during Verification Cases                                                       |

| Figure 12. SRC Performance Over Load Range for Varying Input Voltage                                                |

| Figure 13. SRC Performance with Losses Over Load Range for Varying Input Voltage 33                                 |

| Figure 14. Bidirectional Buck-Boost Converter                                                                       |

| Figure 15. Switching operation of Buck-Boost                                                                        |

| Figure 16. Duty Cycle for Two Modes of Buck-Boost Operation under Unified Scheme 36                                 |

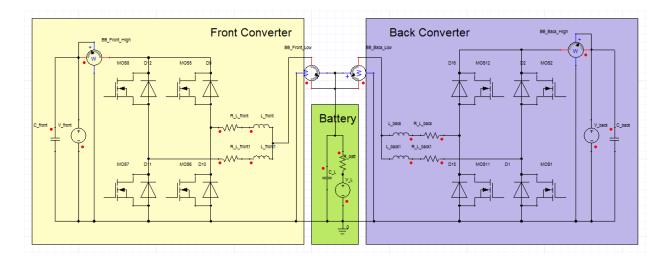

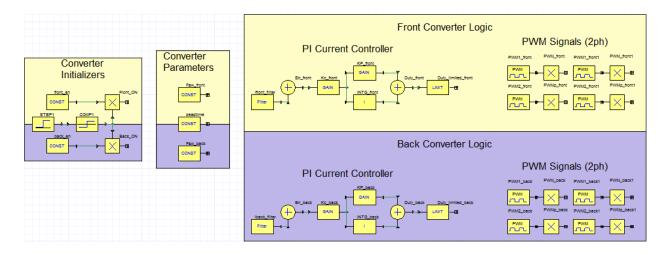

| Figure 17. Back End Two Phase Bi-directional Buck-Boost Converter and Battery 41                                    |

| Figure 18. Back Converter Frequency Response of Filtered Control-to-Inductor Current                                                  | 46 |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 19. Back Converter Frequency Response of PI Compensated System                                                                 | 47 |

| Figure 20. Back Converter Nyquist Diagram of PI Compensated System                                                                    | 47 |

| Figure 21. Front Converter Frequency Response of Filtered Control-to-Inductor Current                                                 | 48 |

| Figure 22. Front Converter Frequency Response of PI Compensated System                                                                | 49 |

| Figure 23. Front Converter Nyquist Diagram of PI Compensated System                                                                   | 50 |

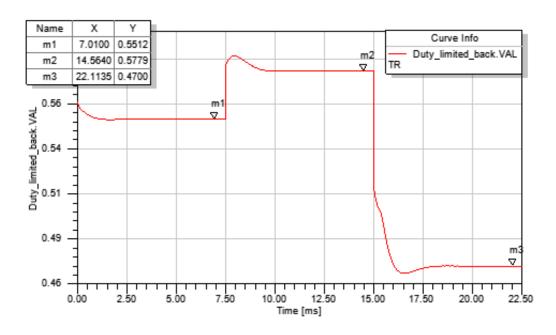

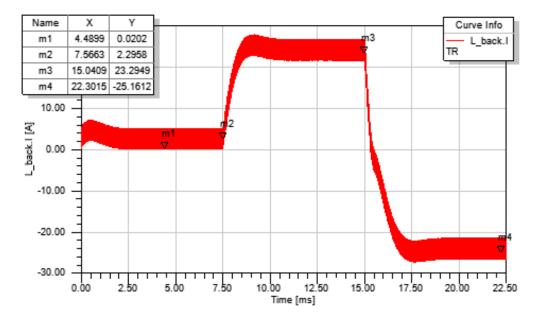

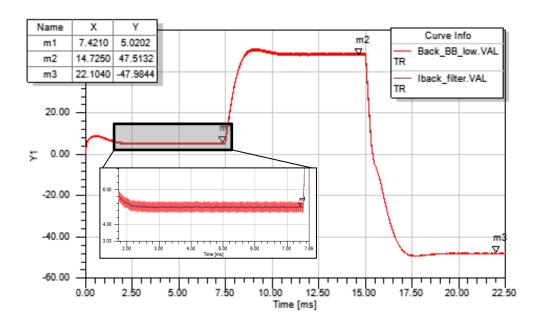

| Figure 24. Simulated Non-Idealized Duty Cycle of Back Battery Converter                                                               | 53 |

| Figure 25. Simulated Non-Idealized Per Phase Inductor Current of Back Battery Converter                                               | 53 |

| Figure 26. Simulated Non-Idealized Total Inductor Current of Back Battery Converter (red) a Filtered Inductor Current Signal (purple) |    |

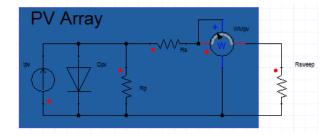

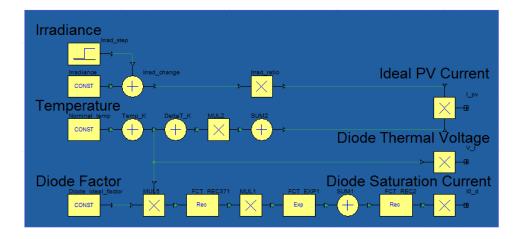

| Figure 27. Single Diode Model of a PV Cell                                                                                            | 57 |

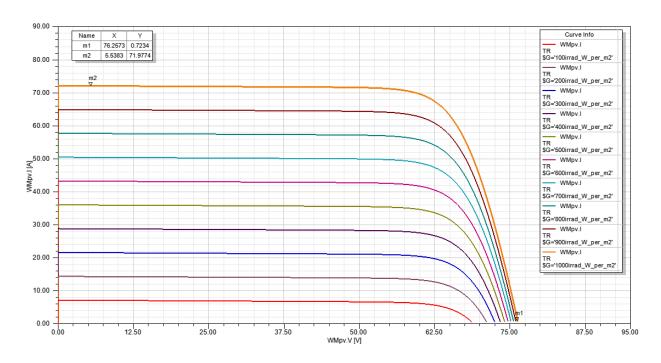

| Figure 28. IV Curve of 4.16 kW PV Array for Varying Irradiance                                                                        | 60 |

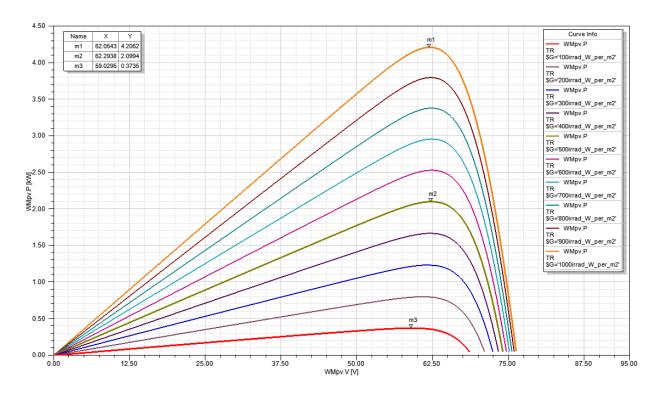

| Figure 29. PV Curve of 4.16 kW PV Array for Varying Irradiance                                                                        | 61 |

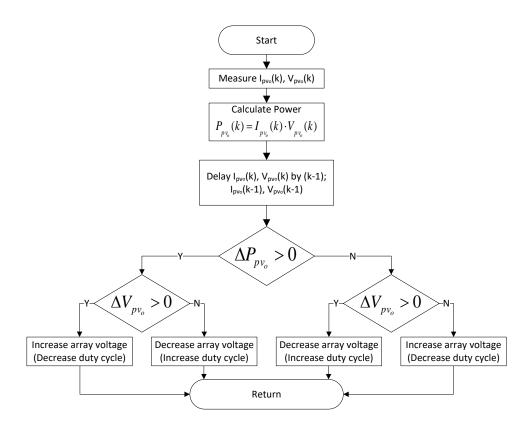

| Figure 30. P&O Maximum Power Point Algorithm                                                                                          | 63 |

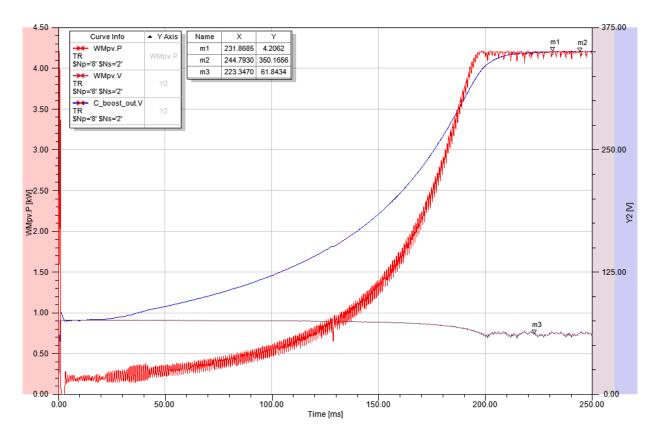

| Figure 31. Array Power (Red), Array Voltage (Purple), and Boost Output Voltage (Blue) in MPP Verification                             |    |

| Figure 32. Boost Converter Duty Cycle for MPP Verification                                                                            | 65 |

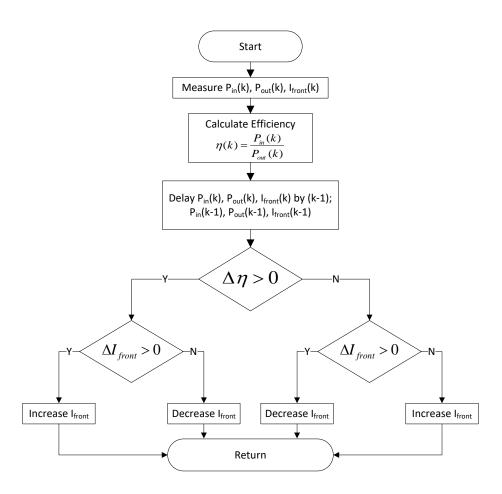

| Figure 33. Front Assistance Algorithm Logic                                                                                           | 68 |

| Figure 34. Example Operation of Front Assist Algorithm                                                                                | 69 |

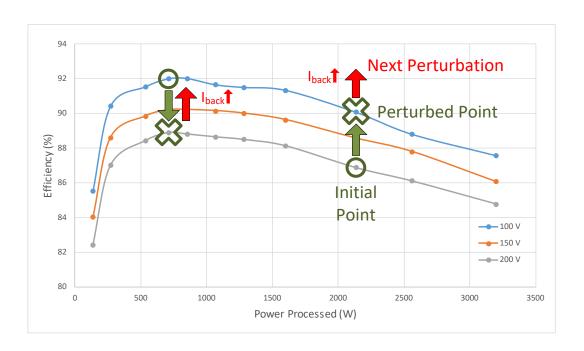

| Figure 35. Back Assistance Algorithm Logic                                                                                            | 72 |

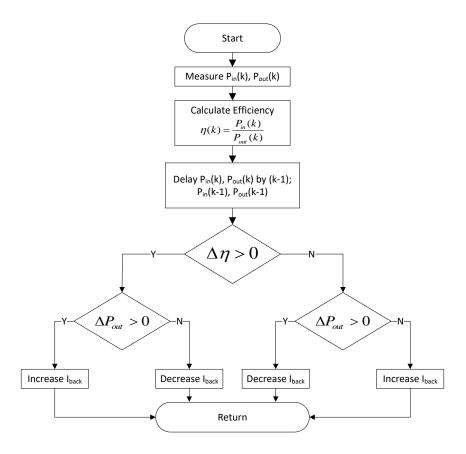

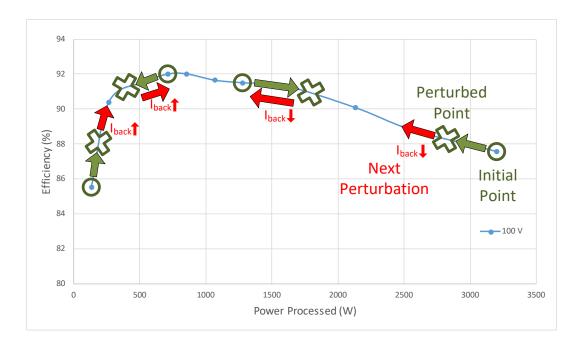

| Figure 36. Example Operation of the Back Assist Algorithm with a Strong Source                                                        | 73 |

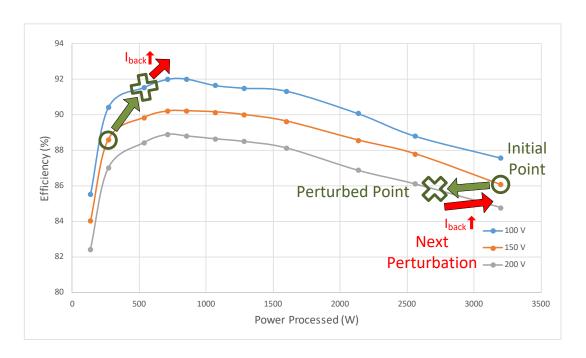

| Figure 37. Example Operation of the Back Assist Algorithm with a Weak Source                                                          | 75 |

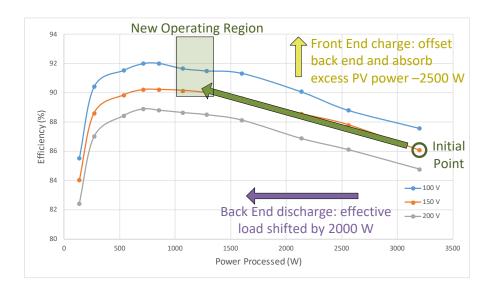

| Figure 38. Example Operation of Dual Assistance for Heavy Loading and a Weak Source                                                   | 77 |

| Figure 39. Dual Assistance Algorithm Logic                                                                                            | 78 |

| Figure | 40. Example of EPI Operation Showing Back End Current (top) and SRC Efficience (bottom)                 |                |

|--------|---------------------------------------------------------------------------------------------------------|----------------|

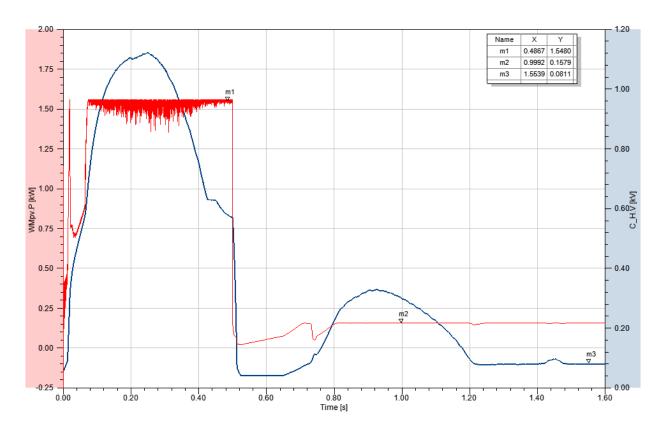

| Figure | 41. PV Array Output Power (red) and PV Converter Output Voltage (navy) during Lig Load Test             |                |

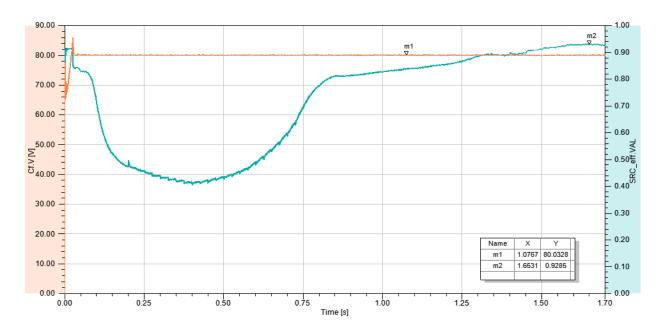

| Figure | 42. Load Voltage (orange) and SRC Efficiency (light blue) during Light Load Test 8                      | 37             |

| Figure | 43. Back End Converter Power Processed during Light Load Test                                           | 37             |

| Figure | 44. System Efficiency during Light Load Test                                                            | 38             |

| Figure | 45. SRC Performance Profile for Light Load Test                                                         | 38             |

| Figure | 46. PV Array Output Power (red) and PV Converter Output Voltage (navy) during Heav Load Test            | -              |

| Figure | 47. Load Voltage (orange) and SRC Efficiency (light blue) during Heavy Load Test 9                      | <b>)</b> 1     |

| Figure | 48. Front End Converter (yellow) and Back End Converter (purple) Power Processed during Heavy Load Test |                |

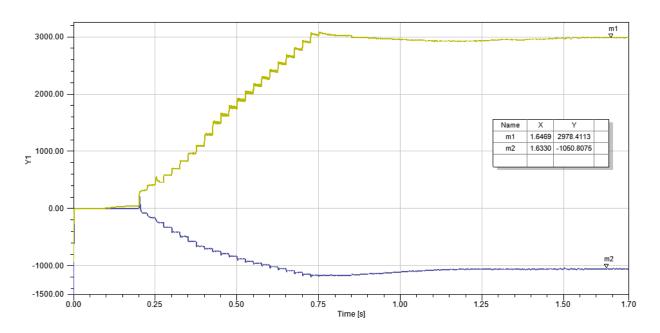

| Figure | 49. Battery Current during Heavy Load Test                                                              | <del>)</del> 3 |

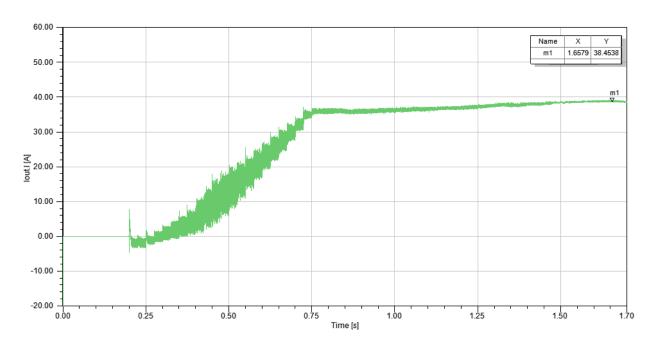

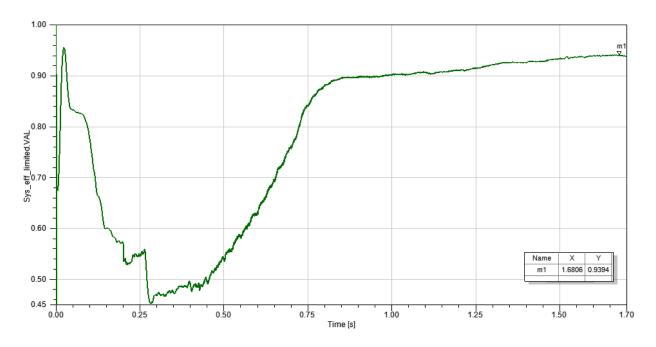

| Figure | 50. System Efficiency during Heavy Load Test                                                            | €              |

| Figure | 51. SRC Performance Profile for Heavy Load Test                                                         | <b>)</b> 4     |

| Figure | 52. PV Array Output Power (red) and PV Converter Output Voltage (navy) during P Dropout Test            |                |

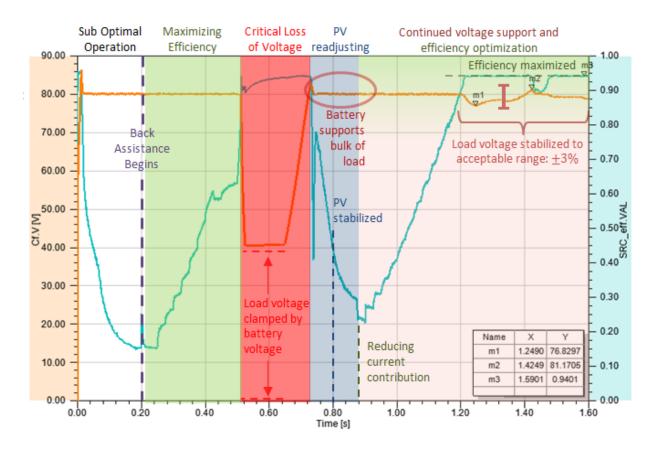

| Figure | 53. SRC Efficiency (light blue) and Load Voltage (orange) during PV Dropout Test 9                      | <del>)</del> 7 |

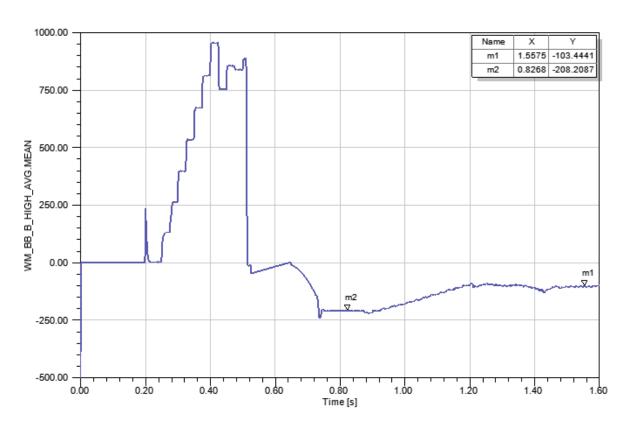

| Figure | 54. Back End Converter Power Processed during PV Dropout Test                                           | <b>)</b> 9     |

| Figure | 55. System Efficiency during PV Dropout Test                                                            | 9              |

| Figure | 56. SRC Performance Profile for Heavy Load Test                                                         | )()            |

| Figure | 57. SRC Verification Circuit                                                                            | )2             |

| Figure | 58. SRC Frequency and Phase Shift Control Logic                                                         | )3             |

| Figure | 59. Front and Back Bidirectional Converter and Battery Verification Circuit                             | )3             |

| Figure | 60. Front and Back Bidirectional Converter Control Logic                                                | 14             |

| Figure 61. PV Array Sweep Verification Circuit               | 104 |

|--------------------------------------------------------------|-----|

| Figure 62. PV Array Parameter Calculations                   | 104 |

| Figure 63. PV Array and Array Converter Verification Circuit | 105 |

| Figure 64. P&O MPPT Logic                                    | 105 |

| Figure 65. Front and Back Assistance Algorithm               | 106 |

| Figure 66. Efficiency Peak Identification Logic              | 106 |

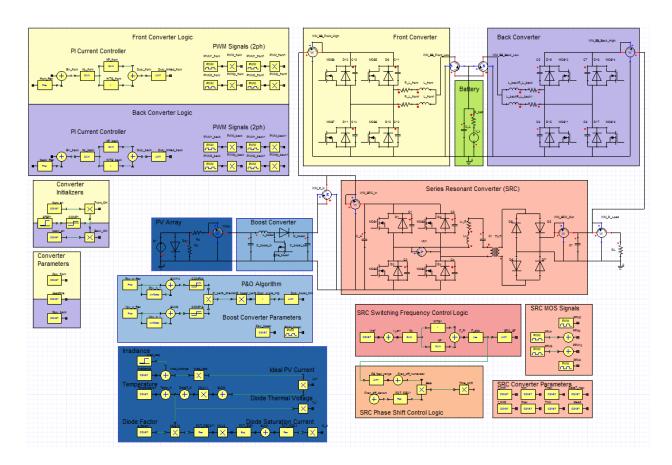

| Figure 67. Isolated Microgrid System Model                   | 107 |

#### **ACKNOWLEDGEMENTS**

First and foremost, I want to thank my loving family and friends for their support and motivation though this academic endeavor. Although none of them understand quite exactly the details of this thesis, they still showed, at least what I perceived to be, a genuine interest in my research. For all the times they asked me to explain the thesis "one more time", knowing full well that none of it would stick, I am grateful; it's the thought that counts.

I would also like to thank the professors on my committee, Dr. Reed, Dr. Stanchina and Dr. Mao, who guided me and taught me this field in both my graduate and undergraduate careers. I would also like to thank Dr. Grainger. Regretfully I was never able to learn from him in a classroom setting, however Brandon was instrumental in the crafting and development of this thesis.

Lastly, thank you to all the students in the EPSL research group. Though focusing in this group can be challenging at times amidst the virulent political discussion, the willingness of the group to help one another cannot be overstated. I am grateful for the friendships that were forged in that windowless 8<sup>th</sup> floor room.

#### 1.0 INTRODUCTION

The electrical grid is moving towards a decentralized structure in which generation meets load directly at the local level. In the transition to the new architecture, renewable generation and DC microgrids have the potential to play a prominent role. Typically microgrids have an open line with the utility grid, allowing for transfer and sharing of power should the local load exceed local generation or vice-versa. However this is not always the case and the microgrid must be adequately designed to operate as an independent entity in the cases where the grid connection must be severed; this operation is referred to as islanded mode. While in the islanded mode, efficiency and proper utilization of the resources available are of the highest importance as there is no utility connection to make up for power margins. As more microgrids are integrated into the electrical system, the occurrence of these islanded scenarios will rise. Thus there is a need to understand and evaluate the performance of these microgrids while in islanded operation.

In addition to changing grid architectures, the penetration of photovoltaics into the market has been rapidly increasing, especially in recent years. The intermittent characteristic of PV generation necessitates energy storage to accompany these installations. Thus it is not uncommon for microgrids with renewable generation to also include battery storage as it provides redundancy, power smoothing, and a secondary source of power to the PV, which is especially critical during islanded operation.

There has already been research into the performance of PV-Energy storage coupled systems and the their ability to manage energy for varying load conditions with a grid connection [1], [2] and without [3]–[5]. Also of interest are energy storage systems that add functionality to the PV system [6], [7]. Storage systems like the Active Power Distribution Node provide active power flow control and multiple points of failure, increasing system reliability and availability [8], [9]. However studies like those just mentioned typically focus on the system level impact and interactions of the energy storage with the grid. Few studies look on the impact of energy storage in a microgrid isolated scenario and its ability to supplement the performance of an individual converter. Placing energy storage in parallel with a main converter can allow the converter to operate at a superior performance over a wide range of loads, similar to the manner in which composite converters achieve optimized efficiency over wide load range [10]–[12]. In addition to performance, power rerouting, load sharing, reliability, and operational flexibility are all important metrics.

This research focuses on addressing these metrics by using an autonomous control architecture which seeks to maximize the performance of a series resonant converter (SRC) by supplementing its power delivery with a parallel energy storage system. The islanded microgrid being studied consists of local PV generation connected to a DC bus, a high power density SRC, which provides power to the local load, and parallel battery storage interfaced via bidirectional DC-DC converters to the front and back of the high density converter; the system can be seen in Figure 1. The purpose of the parallel energy storage is threefold: it removes the single point of failure by providing two paths for power to flow, increasing system reliability, it provides a means of emergency power should local generation drop out or fail, and it provides the ability to share or source load with the main converter. By acting as a source or sink of power, the battery

storage can effectively move the operating point of the main converter. Depending on conditions outside the of the system, such as weather or power demand, the generation or load may be too great or too little, resulting in power conversion at a poor efficiency point. Using the ability of the parallel storage to alter the operational point of the main converter can result in dramatic improvement to performance, reducing losses and better utilizing the limited resources available to the microgrid.

**Figure 1.** Isolated Microgrid under Study

This thesis consists of seven chapters which are organized as follows.

Chapter 1 provides the context for this research and summarizes a number of studies already conducted which examine the topic of microgrids, PV, and energy storage. This chapter also establishes the focus of this work and provides a high level overview of the research.

Chapter 2 focuses on the design and control of the high density series resonant converter as well as the evaluation of its performance.

In Chapter 3, the battery model and assumptions are presented in addition to the design and control of the bi-directional DC-DC battery interfacing converters.

Chapter 4 covers the photovoltaic model, design of the PV array, and control and implementation of a maximum power point tracking technique using a boost converter.

Chapter 5 examines the autonomous control logic which seeks to maximize the high density converter performance. It also looks at the logic necessary for ancillary features such as voltage sharing/load support.

In Chapter 6 a number of simulation based results are presented to evaluate the effect of the autonomous control architecture under varying operating conditions.

Finally Chapter 7 summarizes this research.

#### 2.0 SERIES RESONANT CONVERTER

#### 2.1 CONVERTER OVERVIEW

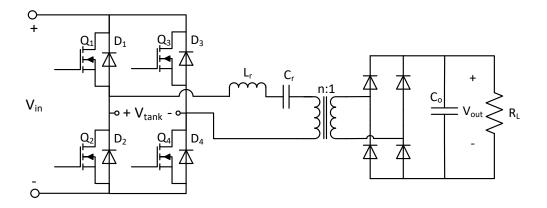

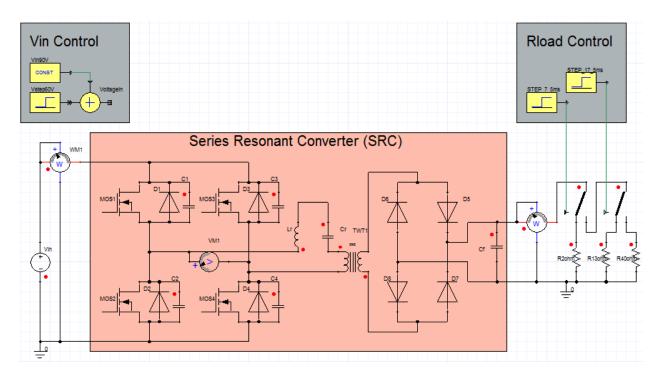

The series resonant converter was chosen as the main converter due to the high power density, high switching frequencies, excellent efficiency, and zero voltage switching features of this topology. The steady state analysis and operation of the series resonant converter has been thoroughly researched and is well understood [13]–[16]. The topology of the series resonant converter can be seen below in Figure 2. The converter consists of either a half or full bridge converter on the front end, followed by a resonant LC tank connected to a transformer. The transformer is optional and may or may not be included depending on step up/step down and isolation needs. The transformer connects to a rectifier and output capacitor which feeds the load resistor. Additionally, capacitors may be included across the front end power electronics to reduce switching loss. The converter regulates the output voltage by adjusting its switching frequency above or below the resonant frequency of the LC tank.

Figure 2. Series Resonant Converter

Operating above the resonant frequency is preferable for a few different reasons. It ensures that the converter always remains in a continuous mode of conductance, it allows for zero-voltage switching to occur, which is desirable when using MOSFETs as the switching device, and it allows for higher switching frequencies to be used [13]. Adjusting the switching frequency of the converter affects the impedance of the resonant tank, which in turn affects the conversion ratio of the converter and thus the regulation of the output voltage. The tank impedance is inversely related to the conversion ratio; as tank impedance increases the conversion ratio decreases and thus the output voltage decreases. For frequencies closer to resonance, the tank impedance is the lowest which results in the highest conversion ratio; this means the greatest amount of energy can be transferred from the input to the output. The opposite is true for frequencies far away from resonance; when tank impedance is high, the conversion ratio is low, and minimal energy can transfer from the input to output.

#### 2.2 CONVERTER DESIGN

The chosen SRC converter design parameters are summarized in Table 1. For a max power rating of 3.2 kW and a desired output voltage of 80 V, then the maximum load that the converter should be able to supply is 40 Amps, which corresponds to 2  $\Omega$  of resistance. The size of the output capacitor was chosen to sufficiently large such that the output ripple was minimized to less than 1% of the output voltage under max load. For this we assume that under max load the switching frequency f is close to resonance; the equation for voltage ripple of a full bridge rectifier is shown in (1). Finally it was desired to resonate the converter at 200 kHz; the equation for the resonant frequency of a series resonant converter is shown in (2). The resonant capacitor was calculated after choosing a value for the resonant inductor.

$$V_{ripple} = \frac{I_{load}}{f * C_0} \tag{1}$$

$$f_0 = \frac{1}{2\pi\sqrt{L_r C_r}} \tag{2}$$

**Table 1. SRC** Converter Parameters

| System Parameter         | Variable  | Value    |

|--------------------------|-----------|----------|

| Power Rating (kW)        | Prating   | 3.2      |

| Resonant Frequency (kHz) | $f_0$     | 200      |

| Input Voltage Range (V)  | $V_{in}$  | 90 - 150 |

| Output Voltage (V)       | $V_{out}$ | 80       |

| <b>Transformer Turns</b> | n         | 1        |

| Resonant Inductor (µH)   | $L_r$     | 10       |

| Resonant Capacitor (nF)  | $C_{r}$   | 63.32    |

| Output Capacitor (µF)    | $C_0$     | 500      |

#### 2.3 SRC CONTROL METHODS

There are many methods for controlling the series resonant converter, some of the most popular are frequency control, conduction angle control, current-mode control (often referred to as ASTDIC control), and optimal switching trajectory control [17]–[20]. Each means of control varies in terms of complexity, performance, stability, and range.

#### 2.3.1 Frequency Control

Frequency control is one of the most popular methods of control due to its simplicity and reasonable performance. In this method a voltage controlled oscillator is used to determine switching period necessary to regulate the output via a voltage feedback loop. However some drawbacks of this method include a slow oscillatory response at low output voltage [20] and the existence of a dynamic double pole in the frequency response of this control method, which poses a challenge in closed loop design [17].

#### 2.3.2 Conduction Angle Control

With conduction angle control the controller uses the zero-current crossings in the anti-parallel diodes to determine switch timings. This mode of control is non-linear and shares the same frequency response problems as that of the frequency control [17]. Though this has a low complexity level, the performance and response of this method is poor and has instability issues when operating above resonance in the continuous conduction region [20].

#### 2.3.3 Current-mode Control (ASDTIC)

ASDTIC control rectifies the tank inductor current and compares it to a control signal. The error in the difference between these signals is integrated and this resulting output is a periodic waveform with zero crossings. These crossings determine the actuation times for the MOSFETs to properly regulate the output voltage. The complexity level of this method is noticeably higher than the previous two mentioned and requires two impedance loops instead of one [17]. Additionally there is a well-documented "static-instability" with this method in cases where the impedances of the two loops are not identical [17], [18], [20].

#### 2.3.4 Optimal Trajectory Control

This control method compares the tank voltage and current against the desired trajectory of the tank voltage and current in a two-dimensional state plane. It uses the error in this state-plane analysis to determine transistor conduction timings. The implementation of this method is the most complex and requires the greatest computation but delivers the greatest controller performance out of the methods mentioned [17], [20].

#### 2.4 CONTROLLER DESIGN

For this research, frequency control was chosen as the preferred control method due to balance between simplicity and performance. In this scheme, the duty cycle of the active switches is locked to 50% and the switching frequency is varied over a range above the resonant tank

frequency. In designing an appropriate controller for the SRC, small-signal transfer functions are a vital component. However due to the complex resonant switching characteristics of this converter and the existence of a dynamic double pole in the frequency domain, closed form equations have not been available as they are highly complicated and are unique to each individual design [20], [21]. However recent developments in equivalent circuit modeling have resulted in approximations of the closed form small-signal transfer functions for the series resonant converter [22]. The small-signal equations are functions of the equivalent tank impedance  $X_{\text{eq}}$ , equivalent tank resistance  $R_{\text{eq}}$ , and the equivalent tank inductance  $L_{\text{e}}$ , which are shown in (3), (4), and (5), where  $L_r$  refers to the resonant tank inductance,  $C_r$  refer to the resonant tank capacitance, and  $\Omega_s$  refers to the switching frequency in radians/sec. The control-to-output (frequency-to-output) and the input-to-output small-signal equations derived in [22] are shown below in (6) and (7), respectively, with  $\Omega_0$  corresponding to the resonant frequency in radians/sec. By conducting bode plot analysis on these small-signal equations an adequate controller can be designed. However before this can be done, the range of SRC operating frequencies must be known as the equations cannot be solved without it. And before the range of operating frequencies can be determined, certain instabilities regarding the SRC and the frequency control method must be considered, which are discussed in the following section.

$$X_{eq} = \Omega_s L_r - \frac{1}{\Omega_s C_r} \tag{3}$$

$$R_{eq} = \frac{8}{\pi^2} R_L \tag{4}$$

$$L_e = L_r + \frac{1}{C_r \Omega_s^2} \tag{5}$$

$$G_w(s) = \frac{\hat{v}_{out}(s)}{\hat{w}_s(s)} = \frac{-\frac{V_{in}}{\Omega_s} \frac{R_{eq}}{\sqrt{R_{eq}^2 + X_{eq}^2}} \frac{\Omega_s^2 + \Omega_o^2}{\Omega_s^2 - \Omega_o^2} X_{eq}^2}{(s^2 L_e^2 + s L_e R_{eq} + X_{eq}^2)(1 + s R_L C_o) + R_{eq}(s L_e + R_{eq})}$$

(6)

$$G_{v}(s) = \frac{\hat{v}_{out}(s)}{\hat{v}_{in}(s)} = \frac{\frac{R_{eq}}{\sqrt{R_{eq}^{2} + X_{eq}^{2}}} \left( sL_{e}R_{eq} + R_{eq}^{2} + X_{eq}^{2} \right)}{(s^{2}L_{e}^{2} + sL_{e}R_{eq} + X_{eq}^{2})(1 + sR_{L}C_{o}) + R_{eq}(sL_{e} + R_{eq})}$$

(7)

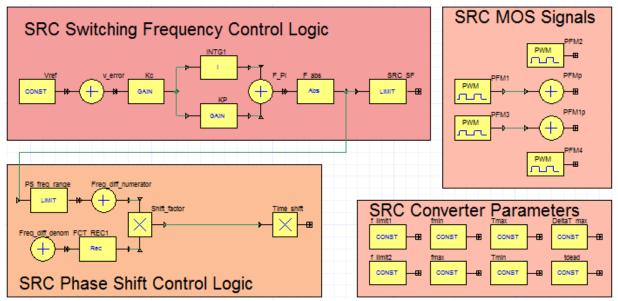

#### 2.4.1 Hybrid Control

Despite the benefits of the frequency control method, the converter still faces some issues, specifically under no load conditions. These are well documented and include loss of control at no load [17], [19] and poor efficiency at light load and no load [23]–[27], the latter of which is due to circulating tank currents and the higher switching frequencies necessary to regulate the output. One solution that addresses both issues is to use a hybrid switching scheme, with phase-shifted switching for light and no load, and frequency modulated switching (frequency control) otherwise [19], [23].

The design of a frequency based PI controller, i.e. a controller that is tuned to the control-to-output (frequency-to-output), lends itself naturally to this solution as it always outputs the expected frequency. The hybrid scheme can be implemented by limiting the switching frequency to a range between resonance  $f_0$  and a desired limiting frequency  $f_{limit1}$ . The minimum switching frequency is referred to as  $f_{min}$  and the maximum switching frequency as  $f_{limit1}$ . For the load range that encompasses this region the converter regulates the output using switching frequency control, the value of which is determined directly by the PI controller frequency  $f_{PI}$ . As the PI frequency increases past the maximum switching frequency, the converter frequency is held constant at the chosen value of  $f_{limit1}$  and the converter regulates the output using phase shift control, now using the PI frequency to determine the value of the phase shift  $\phi_{PSM}$ . The phase shift modulation occurs from the first limiting frequency  $f_{limit1}$  to a maximum frequency  $f_{limit2}$ ; at

the boundary of the first limit  $f_{limit1}$  no phase shift occurs and at the maximum frequency  $f_{limit2}$  full phase shift occurs, at which point the converter is essentially blocking the input. The equation for determining phase shift is shown in (8) and the phase shift only applies to half of the full bridge converter, specifically on switches  $Q_3$  and  $Q_4$ .

$$\Phi = \frac{f_{PI} - f_{limit1}}{f_{limit2} - f_{limit1}} * 180^{\circ}$$

(8)

The frequency limits for the hybrid control scheme of the series resonant converter are detailed in Table 2 and the switching ranges and phase shift for each control scheme are shown in Table 3. Switching diagrams for four operating points from max load to light load are displayed in Figure 3. Each diagram shows the switch activation for the high side MOSFETs Q<sub>1</sub> and Q<sub>3</sub>, as well as the theoretical voltage across the resonant tank V<sub>tank</sub> with the corresponding switching frequency f, as well as the PI frequency f<sub>PI</sub>. The four operating points are in order of decreasing load starting from top left to bottom right: max load, switching frequency/phase shifted boundary, light load, and very light load.

**Table 2.** Frequency Boundaries for SRC Hybrid Control

| Minimum Switching Frequncy                                      | $f_{min}$    | 202 <i>kHz</i> |

|-----------------------------------------------------------------|--------------|----------------|

| Maximum Switching Frequency<br>(Phase Shift Starting Frequency) | $f_{limit1}$ | 240 <i>kHz</i> |

| Full Phase Shift Frequency                                      | $f_{limit2}$ | 260 <i>kHz</i> |

Table 3. Frequency Ranges for SRC Hybrid Control

| SRC swithcing frequency             | Phase Shift                                                                                                                                    | PI frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 202 kHz < f < 240 kHz               | Ф = 0 °                                                                                                                                        | $202 \; kHz < f_{_{PI}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| f = 240  Khz                        | $\Phi = \frac{f_{PI} - f_{limit1}}{f_{limit2} - f_{limit1}} * 180^{\circ}$                                                                     | < 260 kH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Heavy/Medium                        | Load Region                                                                                                                                    | to Light Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Switching Frequence                 | cy Control SF/P                                                                                                                                | M boundry (240kHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0.5 0.5 0.0 2 4 6 8 Time (s) ×10 -6 | -0.5<br>-0.5<br>-1 0 2 4 6 8                                                                                                                   | Q 240 kHz  1 0 0 2 4 6 8 Time (s) ×10-6  Q 240 kHz  1 0 0 2 4 6 8 Time (s) ×10-6  X 10-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                     |                                                                                                                                                | to No Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                     |                                                                                                                                                | <b>→</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Q 1 240 kHz                         | 1 1 0.5                                                                                                                                        | Q 1 240 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                     | 202 kHz $< f < 240$ kHz $f = 240 \text{ Khz}$ Heavy/Medium  Switching Frequence  Q, 203 kHz  Time (s) $\times 10^{-6}$ Light Loa  Phase Modula | $f = 240 \text{ Khz} \qquad \Phi = 0^{\circ}$ $f = 240 \text{ Khz} \qquad \Phi = \frac{f_{Pl} - f_{limit1}}{f_{limit2} - f_{limit1}} * 180^{\circ}$ $Heavy/Medium Load Region$ $Switching Frequency Control$ $V_{tank}, I_{pl} = 1 = 240 \text{ Khz} (50\% \text{ Duty})$ $Q_{1} = 203 \text{ kHz}$ $Q_{2} = 240 \text{ Khz}$ $Q_{3} = 203 \text{ kHz}$ $Q_{1} = 240 \text{ Khz}$ $Q_{1} = 240 \text{ Khz}$ $Q_{2} = 240 \text{ Khz}$ $Q_{3} = 240 \text{ Khz}$ $Q_{4} = 240 \text{ Khz}$ $Q_{1} = 240 \text{ Khz}$ $Q_{2} = 240 \text{ Khz}$ $Q_{3} = 240 \text{ Khz}$ $Q_{4} = 240 \text{ Khz}$ |

**Figure 3.** Switching diagram of SRC hybrid control scheme from max load (top left) to very light load (bottom right)

### 2.4.2 PI Controller Tuning

With the operating range of frequencies defined, bode plot analysis was conducted to tune a PI controller for regulation of the output voltage for the given converter specifications. For stable regulation it is necessary to tune the PI controller for the worst case scenario, which results in least stable conditions. Thus the small-signal frequency responses of (6) and (7) should be plotted for the two ends of operations for switching frequency modulation, which correspond to heavy load and the SF/PM boundary load. The heavy scenario corresponds to the lowest input voltage, 90 V, and smallest load resistance, 2  $\Omega$ , while the boundary scenario corresponds to some unknown combination of increased voltage and/or decreased load.

Moreover to determine the frequency response of the small-signal equations more than just the input voltage and load resistance must be known. To compute (3), (4), (5), (6), and (7) one must also know what switching frequency the converter should be operating at. Unfortunately, equations solving for the expected switching frequency of the series resonant converter do not exist or are not readily available due to complexity. However [13] provides the equations for the conversion ratio of the ideal series resonant converter in terms of the mode index, subharmonic number, normalized switching frequency, and normalized load of the converter. The mode index is an integer which satisfies the equality in (9) where F is the normalized switching frequency. For a SRC operating above resonance in the continuous conduction region this integer equals zero. The subharmonic number refers to which subharmonic mode the converter is operating in, if any, and is show in (10). For operation above resonance where the mode index is zero, the subharmonic number is one. The equation for the normalized load (11) is in terms of the transformer ratio n, the load resistance, and the characteristic impedance of the resonant tank.

$$\frac{1}{k+1} < F < \frac{1}{k}, \qquad F = \frac{f_s}{f_0} \tag{9}$$

$$\xi = k + \frac{1 + (-1)^k}{2} \tag{10}$$

$$Q = n^2 \frac{\sqrt{\underline{L}}}{R_L} \tag{11}$$

With values for these converter properties the equation for conversion ratio of an ideal series resonant converter may be solved for (12); note that in this equation,  $\gamma = \pi/F$  is the angular length of half the switching period and is inversely proportional to the normalized switching frequency.

$$M = \frac{\frac{Q\gamma}{2}}{\xi^{4} * tan\left(\frac{\gamma}{2}\right)^{2} + \left(\frac{Q\gamma}{2}\right)^{2}} \left((-1)^{k+1} + \left(\xi^{2} - cos\left(\frac{\gamma}{2}\right)^{2}\right) \frac{\xi^{4} tan\left(\frac{\gamma}{2}\right)^{2} + \left(\frac{Q\gamma}{2}\right)^{2}}{\left(\frac{Q\gamma}{2}\right)^{2} cos\left(\frac{\gamma}{2}\right)^{2}}\right)$$

$$(12)$$

To determine the estimated switching frequency of the converter, (12) was solved iteratively in MathCAD to find the switching values that resulted in the correct conversion ratio. For the heavy load scenario (input of 90 V and a load of 2  $\Omega$ ) and desired output voltage of 80 V, a conversion ratio of M = 0.88 is needed; the switching frequencies that achieves this is 206.6 kHz.

As for the boundary conditions, the voltage and load values are unknown, yet the boundary frequency is known to be 240 kHz. Once again (12) was solved iteratively to find combinations of load and voltage that resulted in the correct conversion ratio at a frequency of

240 kHz. The first combination tried was the lowest voltage and some unknown load. The input voltage was held constant at 90 V at 240 kHz and the load was varied to determine which value resulted in the correct conversion ratio of M = 0.88; the load that achieves this is 14  $\Omega$ . The next scenario that was tried was max load and some unknown voltage; the load was kept at 2  $\Omega$  at 240 kHz, which results in a conversion ratio of M = 0.325. However to regulate the output voltage to 80 V at this conversion would require an input voltage 246 V, which is beyond our SRC design parameters for the upper end voltage. For the upper voltage of 150 V, this requires a conversion ratio of M = 0.533, thus the load was increased until this constraint was satisfied resulting in a load of 3.8  $\Omega$ . The two boundary scenarios as well as the heavy load scenario are summarized in Table 4.

**Table 4.** Operating Cases for PI Tuning

| Scenario   | Input Voltage | Load  | M     | Fsw       |

|------------|---------------|-------|-------|-----------|

| Heavy      | 90 V          | 2 Ω   | 0.88  | 206.6 kHz |

| Boundary 1 | 90 V          | 14 Ω  | 0.88  | 240 kHz   |

| Boundary 2 | 150 V         | 3.8 Ω | 0.533 | 240 kHz   |

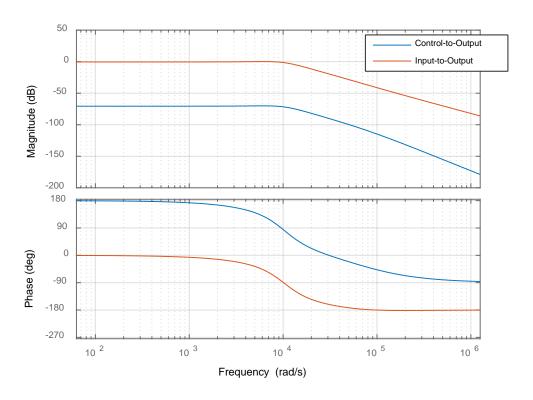

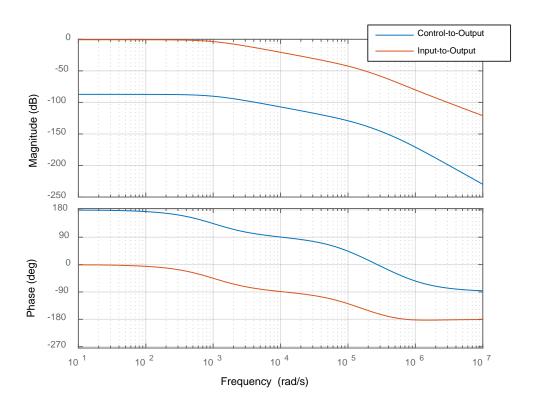

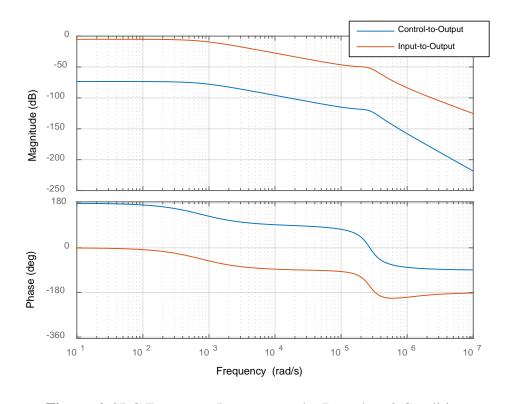

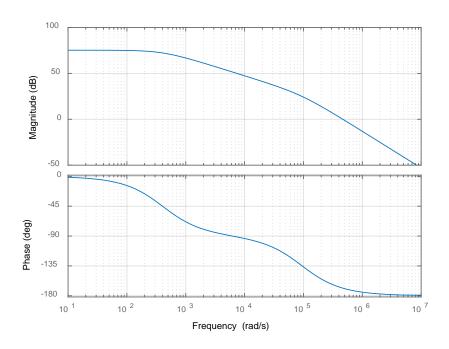

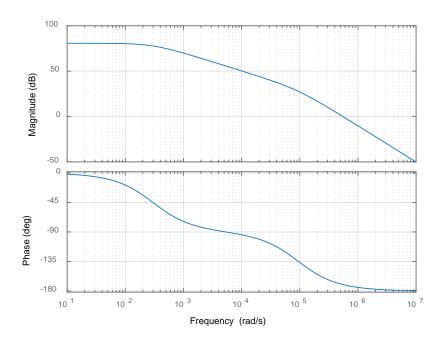

The frequency response of the control-to-output and input-to-output under heavy, boundary 1, and boundary 2 conditions are shown in Figure 4, Figure 5, and Figure 6, respectively. Observing all three graphs, it can be seen that of the two equations, the control-to-output has significantly lower magnitude, as well as a positive phase from 180° to zero. This positive phase is a result of the negative sign in the numerator of the control-to-output equation

and this must be accounted for when calculating margins by shifting the phase by -180°. Typically gain and phase margins are used to determine whether a system is stable and the measure of system stability. The gain and phase margins of the two responses are listed in Table 5. All margin values are positive indicating inherent system stability however it is desirable to have non-infinite margins for accurate control of a system. To ensure all cases have a non-infinite phase margin the case with the lowest DC gain must be satisfied, which corresponds to the control-to-output response for the first boundary scenario.

**Figure 4.** SRC Frequency Response under Heavy Conditions

Figure 5. SRC Frequency Response under Boundary 1 Conditions

Figure 6. SRC Frequency Response under Boundary 2 Conditions

Table 5. Gain and Phase Margins for PI Operating Cases

|             | Gain Margin |          |          | Phase Margin |         |         |

|-------------|-------------|----------|----------|--------------|---------|---------|

| Scenario    | Heavy       | Bndry 1  | Bndry 2  | Heavy        | Bndry 1 | Bndry 2 |

| Ctrl-to-Out | 92.9 dB     | 143.7 dB | 121 dB   | Inf.         | Inf.    | Inf.    |

| In-to-Out   | 40.3 dB     | 74.12 dB | 55.89 dB | Inf.         | Inf.    | Inf.    |

The PI controller was then tuned following the general design approach found in [28]. The transfer function for the PI controller is shown in (13). The desired phase margin  $\phi_M$  was chosen to be 50° and the value of  $K_c$  was chosen to be -2000 such that dc gain of the control-to-output would have a positive decibel value. The proportional and integral gains were then derived via (14) and (15). In these two equations,  $\omega_1$  corresponds to the frequency at which the phase of the control-to-output equals (-180° +  $\phi_M$  + 5°). The derived PI gain values are summarized in; note that the negative sign in the DC gain is to account for the negative sign in the numerator of the control-to-output equation. In practical terms this negative sign in the small-signal equation conveys that there is an inverse relationship between the frequency of the converter and the regulation of the output, as discussed earlier.

$$G_{PI}(s) = K_c(K_P + \frac{K_I}{s}) \tag{13}$$

$$K_P = \frac{1}{|K_c G_w(j\omega_1)|} \tag{14}$$

$$K_I = 0.1\omega_1 K_P \tag{15}$$

**Table 6.** SRC PI Controller Gains

| DC Gain           | K <sub>C</sub> | -2000  |

|-------------------|----------------|--------|

| Proportional Gain | $K_P$          | 0.0194 |

| Integral Gain     | K <sub>I</sub> | 63.147 |

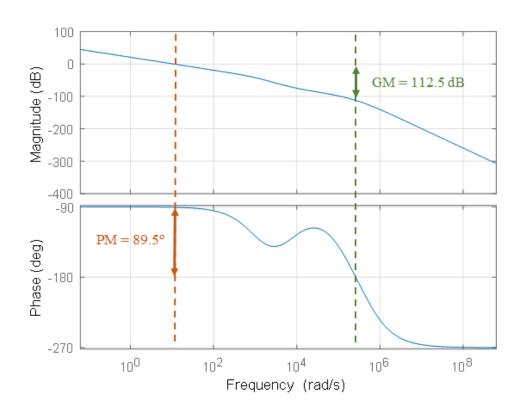

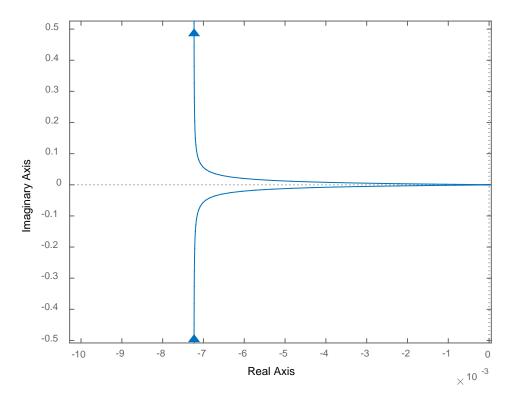

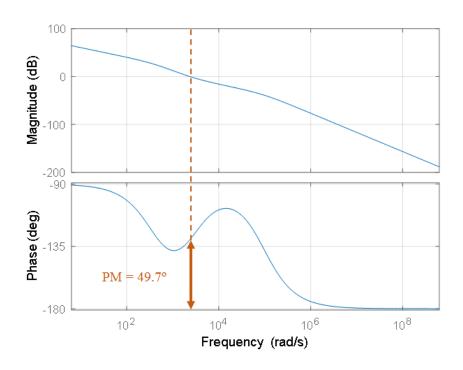

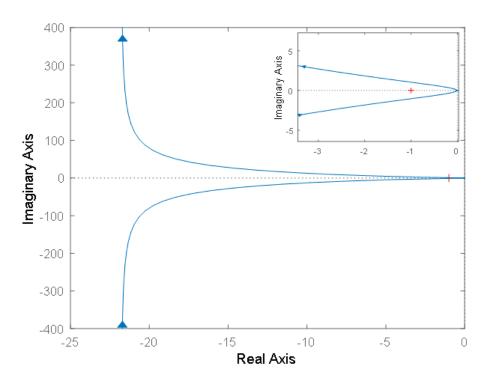

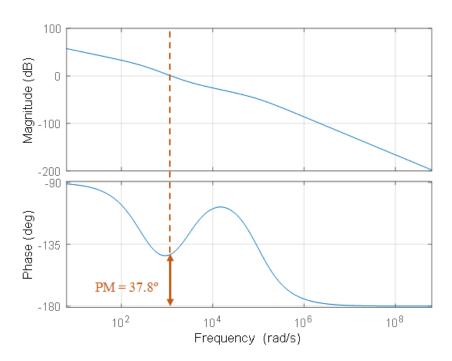

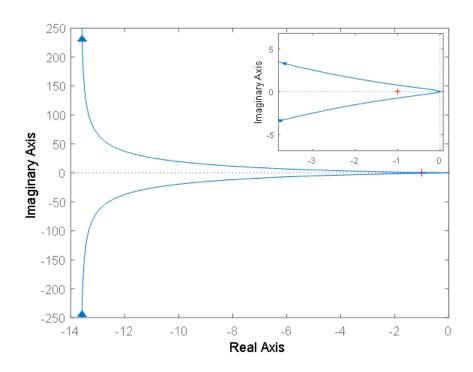

The frequency response of the control-to-output of the new PI compensated system is shown in Figure 7 and the Nyquist diagram is shown in Figure 8. Results from the bode plot show that the new gain margin for the compensated system is 112.5 dB and the new phase margin is 89.5°. Generally, an adequately compensated system has at least 8 dB and 30° of gain and phase margin, respectively [28]. Furthermore, from the Nyquist diagram it can be seen that the system model is stable as the path begins at negative infinity, converges to zero, and ends at positive infinity, but does not encompass -1;, note that the x-axis is on the scale of  $10^{-3}$ .

Figure 7. SRC Frequency Response of PI Compensated Control-to-Output

Figure 8. Nyquist Diagram of SRC PI Compensated Control-to-Output

With the PI tuned it can be expected that the controller outputs the switching frequency that the converter should operate at for a given input voltage and load resistance. For example, for increases in the output load or decreases in input voltage, the PI should lower the switching frequency towards resonance. These cases represent a scenario where the converter must move to a heavier operating point to keep the output regulated, either because a greater amount of energy is required at the load or because a lesser amount of energy is supplied to the system. For decreases in load or increases in input voltage the switching frequency should increase via the same logic.

#### 2.4.3 Dead Time

The last topic of control regarding the SRC is the introduction of dead times. Inclusion of dead times on the switches is twofold: it allows for zero voltage switching to occur and it ensures that no two MOSFETs are ever actuated at the same time as to avoid current shoot through, which can cause severe damage to the device. In practical applications the ideal amount of dead time needed is unique to the semiconductor device capacitance [29], [30], however for simulation purposes, a dead time of 4% or less of the minimum switching period achieves the desired effect without adversely affecting the output of the converter [31]. For the SRC, a dead time of 100 ns was used, which is 2.4% of the minimum switching period of 4.167 µs, the period corresponding to max switching frequency 240 kHz.

#### 2.5 SIMULATION AND VERIFICATION

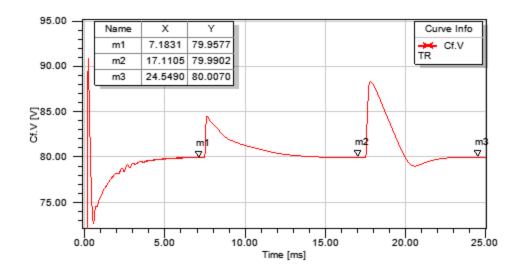

The SRC was modeled in Ansys Simplorer to verify that the circuit operates as expected and that the PI controller correctly regulates the output voltage for steady state operation. Using (12), the frequency necessary for regulation can be predicted and compared to the simulation frequency. The cases to be verified are shown in Table 7 and include max load, the switching frequency boundary, and phase shifted light load. As before, the frequency was calculated iteratively by determining the conversion ratio M that regulates the output to 80 volts. It should be expected that the simulation frequencies deviate slightly from this as (12) is for a lossless converter, and the diodes and MOSFETs used in the simulation have slight loss resulting from a forward voltage of 0.8 V and an on resistance of 1 m $\Omega$ . Frequencies can be predicted for the first two cases, however making accurate estimation of the required phase shift is challenging, as the equation exists in the complex domain and requires knowledge of the phase shift in the resonant tank to calculate phase shift for regulation [23].

Despite this a reasonable estimate of the phase shift can be made based off the size of the load compared to the load at the phase shift boundary. From (12), for the case of a 90 V input and 14  $\Omega$  (457 W load), the estimated frequency to regulate is 240 kHz, i.e. the phase shifted load boundary. The light load case has a load resistance of 40  $\Omega$  (160 W); thus this case is equivalent to 35% of the 457 W phase shift load boundary, that is, the light load case is 35% of the load which requires no phase shift. Equivalently the light load case can be seen as 65% of the full phase shifted case, i.e. no load. Via this logic, an equation for estimated phase shift based on load is derived in (16). For the light load case, the phase shift is predicted to be around 115°. This calculation was done for an input voltage 90 V; as the simulation voltage is 150 V, it is expected that the actual phase shift is greater due to a lower conversion ratio needed for regulation.

$$\Phi_{\rm est} = \left(1 - \frac{P_{PS_{boundary}}}{P_{lightload}}\right) * 180^{\circ}$$

(16)

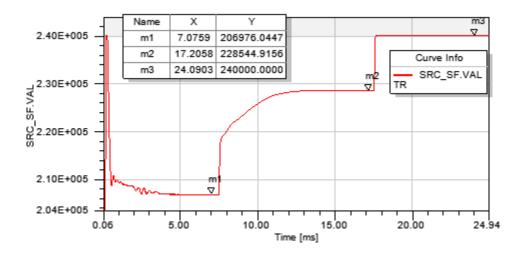

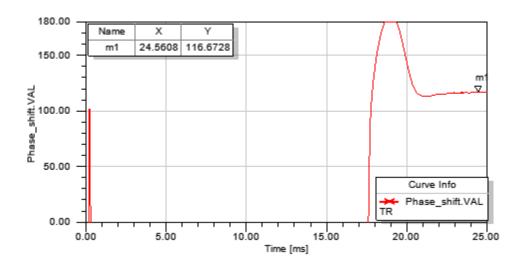

The Simplorer verification circuit can be seen in Appendix A section A.1 along with logic blocks for the hybrid control of the converter. The capacitors in parallel with the full bridge MOSFETs were included to achieve ZVS switching. Typically, device capacitance is enough to achieve this type of switching however the Simplorer semiconductor models used did not account for specific device capacitance. As per the recommendation for ZVS switching of a SRC found in [13] the value of these parallel capacitors was kept small; a capacitance of 1 nF was chosen. The circuit was simulated at a time step of 50 ns and graphs of the output capacitor voltage, PI output frequency, and phase shift are shown in Figure 9, Figure 10, and Figure 11, respectively.

Table 7. Verification Cases for Operation of SRC

| Scenario    | Duration      | Vin   | Load         | Pred      | icted       |

|-------------|---------------|-------|--------------|-----------|-------------|

|             |               |       |              | Frequency | Phase Shift |

| Max Load    | 0 - 7.5  ms   | 90 V  | 2 Ω (3200 W) | 206.6 kHz | 0 °         |

| SF Boundary | 7.5 – 17.5 ms | 90 V  | 13 Ω (492 W) | 236 kHz   | 0 °         |

| Light Load  | 17.5 – 25 ms  | 150 V | 40 Ω (160 W) | 240 kHz   | >115 °      |

Figure 9. SRC Capacitor Output Voltage Regulated to 80 V during Verification Cases

Figure 10. Output of SRC PI Frequency Controller during Verification Cases

Figure 11. Measured SRC Phase Shift during Verification Cases

Figure 9 shows that the controller is able to successfully regulate the output voltage to the target of 80 V as the simulation transitions through the verification cases. Moreover, the controller is able to return to steady state target voltage quickly, within 10 ms, for large shifts in operating points. From Figure 10 it can be seen that the simulation switching frequencies are close to the predicted values: 206.9 kHz for max load and 228.5 kHz for the SF boundary. Though there is a percent difference of -3.2% for the later test case, slight deviation from the calculated ideal frequency was expected as the simulation includes some losses. Finally, Figure 11 verifies that the phase shift control is able to correctly regulate for light load conditions; the estimate phase shift had only 1.3% difference from the simulation shift of 116.6°.

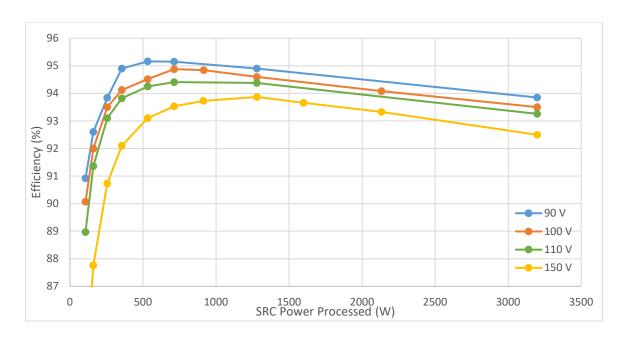

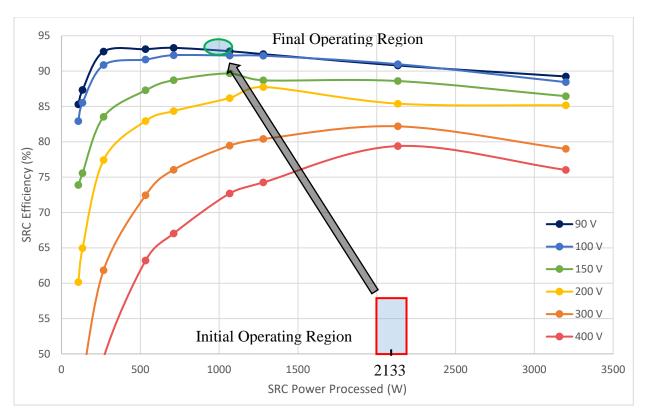

## 2.6 SRC PERFORMANCE EVALUATION

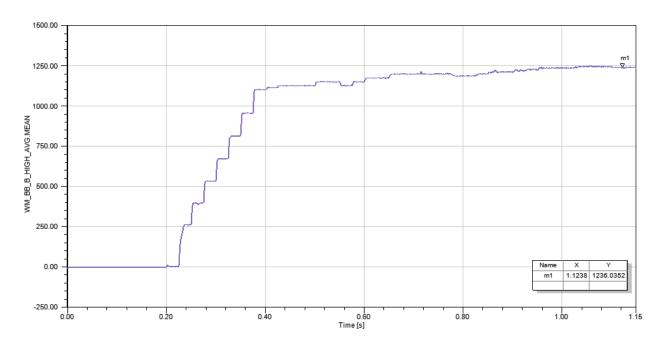

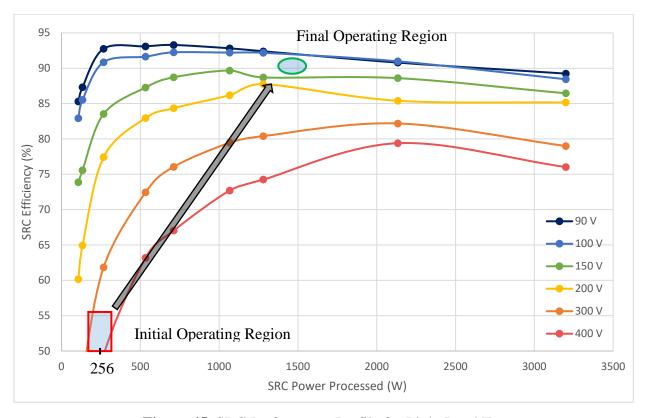

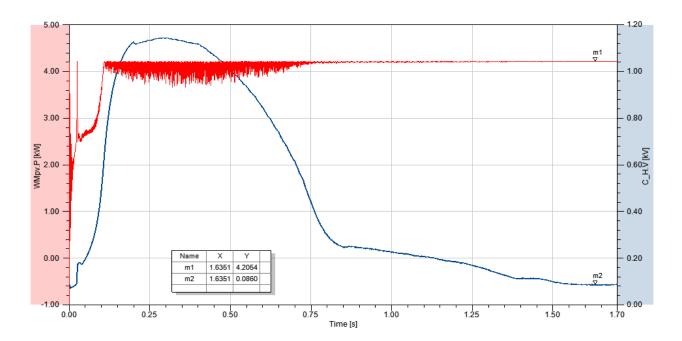

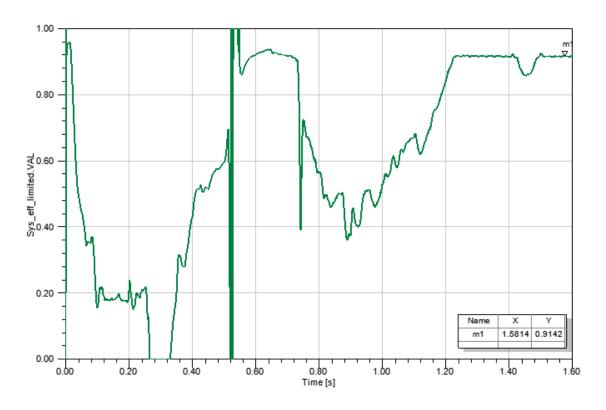

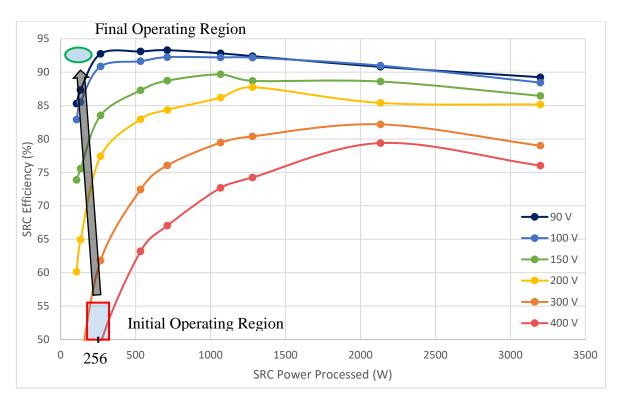

A case study was performed on the SRC to evaluate the performance across its load range for varying input voltage. The converter was swept over a load range from 133 W (60  $\Omega$ ) to 3200 W (2  $\Omega$ ) for input voltages of 90 V, 100 V, 110 V, and 150 V. Both the power into the full bridge of the SRC and out of the SRC diode bridge were averaged over 20 switching periods and the efficiency was calculated via (17) at each operating point. The resulting case study yielded the efficiency profile of the SRC shown in Figure 12.

$$\eta = \left(\frac{P_{in_{SRC}}}{P_{out_{SRC}}}\right) * 100\% \tag{17}$$

It can be seen that the converter performs sub-optimally under heavy and light loading, more so in the latter case, and that the optimal efficiency exists somewhere in the middle of the performance curve. It can also be seen that for changes in the input voltage, the general profile of the curve keeps its shape but shifts vertically, with the best efficiency curve occurring at the lowest input voltage. From these observations it can be reasoned that for a sub-optimal operating point, the SRC performance could be improved by adding or removing load to the converter, depending on the scenario. For example, the SRC supplies a load of 250 W at 150 V input for an efficiency of ~88%; if an additional load of 600 W was added to the output of the SRC, for a total load of 850 W, we should expect the operating point to shift along the 150 V curve to an

Figure 12. SRC Performance Over Load Range for Varying Input Voltage

improved efficiency of ~93.8%. Similarly, the SRC was supplies a load of 3200 W at 150 V input for an efficiency of ~92.5%; if load 2000 W of load was removed from the output, then the SRC effective load is now 1250 W at 150 V and we should expect the new efficiency improve to ~94%.

On the other hand, adding additional load to the front end of the SRC (i.e. in parallel with the SRC on the output of the source) serves to reduce input voltage, assuming a limited power source. For a non-ideal source maintaining a constant power output, an increase in the current demand results in a decrease of voltage as P = I/V must be satisfied. Thus to reduce input voltage and improve SRC performance load should only be added in parallel on the front of the SRC and only in scenarios where enough excess power exists to continue to serve the critical SRC load without issue.

Both these interactions can be taken advantage of by placing a battery in parallel with the SRC and using it as a function load, specifically by utilizing its ability to act as a current sink or current source. Transferring current between the battery and the back end of the SRC changes the effective load of the SRC, moving its operating point along a given curve. Transferring current via the battery and the front end of the SRC changes the effective input voltage to the SRC, shifting the operating point vertically between efficiency curves.

#### 2.7 COMPONENT SIZING AND REEVALUATION

## 2.7.1 Power Electronics Sizing

To achieve a more accurate picture of SRC performance, semiconductor parameters needed to be included in the simulation model to reflect realistic losses. The devices under consideration are the MOSFETs in the full bridge converter and the diode bridge. Due to the high switching frequencies of this design, Silicon Carbide (SiC) based MOSFETs are a practical choice for the full bridge, while standard low loss silicone semiconductors are sufficient for the diode bridge. For this design the three essential constraints on both devices are the DC blocking voltage V<sub>DC</sub>, continuous forward current I<sub>F</sub>, and peak-pulsed forward current I<sub>Fpeak</sub>. For the MOSFETs, the DC blocking voltage must be larger than the maximum input voltage of 150 V, while the two current constraints are determined by the current in the resonant tank inductor. For the diodes, the DC blocking voltage must be rated to block the voltage across the transformer, which is equivalent to the difference between the voltage across the full bridge and the voltage across the resonant tank; this value was determined through simulation. Current constraints for the diodes are the same as for the MOSFETs and correspond to the resonant inductor current.

The current flowing through the resonant inductor is derived in [32] and can be seen in (19), with the peak value occurring during maximum load. The specifics for the max load case were detailed earlier in section 2.4. The semiconductors rated value for peak-pulsed forward current must be larger than the peak resonant inductor current. As for the continuous forward current rating of the devices, this value must be larger than the average current flowing in the semiconductors, which is equal to the average of a half-sine wave with amplitude equal to peak

inductor current, see (20). A table of these design constrains and their values are shown in Table 8 for both the SiC MOSFETs and Si bridge diodes.

$$R_0 = \sqrt{\frac{L_r}{C_r}} \tag{18}$$

$$I_{L_r} = \frac{V_{in}}{R_0} * \left(\frac{\pi}{2}M * Q - \left(M - 1 + \frac{2}{\pi}\sqrt{1 - M^2}\right)\right)$$

(19)

$$I_{avg} = \frac{1}{\pi} I_{L_{r_{peak}}} \tag{20}$$

Table 8. Constraints for SRC Semiconductor Devices

|                         | Variable | Variable |      | aint Values |      |

|-------------------------|----------|----------|------|-------------|------|

|                         |          | MOSFET   | Eqn. | Diode       | Eqn. |

| <b>Blocking Voltage</b> | $V_{DC}$ | 150 V    | -    | 85.8 V      | Sim. |

| Peak Current            | $I_{DM}$ | 61.46 A  | (19) | 61.46 A     | (19) |

| Avg. Continuous Current | $I_D$    | 19.56 A  | (20) | 19.56 A     | (20) |

# 2.7.2 LC Tank Sizing

The losses resulting from the resonant tank were also of consideration. Component ratings were designed around max current and voltage seen on the inductor and capacitor, respectively. As mentioned previously, the maximum stress on these devices occurs while under heaviest load. The equation for resonant inductor current was shown previously and the maximum condition

current values are seen above. The equation for resonant capacitor voltage is also derived in [32] and can be seen in (21). Because the current and voltage in the resonant tank are AC signals, RMS values of the peak conditions are used to choose appropriately rated components. The design constraints for the resonant tank components are seen in Table 9.

$$V_{C_r} = V_{in} \left( \frac{\pi}{2} M * Q - \frac{2}{\pi} \sqrt{1 - M^2} \right)$$

(21)

**Table 9.** Constraints for SRC Tank Components

|                           | Peak Value | RMS Value | Equation |

|---------------------------|------------|-----------|----------|

| <b>Resonant Inductor</b>  | 61.46 A    | 42.45 A   | (19)     |

| <b>Resonant Capacitor</b> | 756.7 V    | 535 V     | (21)     |

Relevant parameters and part numbers of the chosen SRC components are detailed in Appendix B section B.1 along with a discussion of modeling of certain losses in Ansys Simplorer.

## 2.7.3 SRC Performance Reevaluation

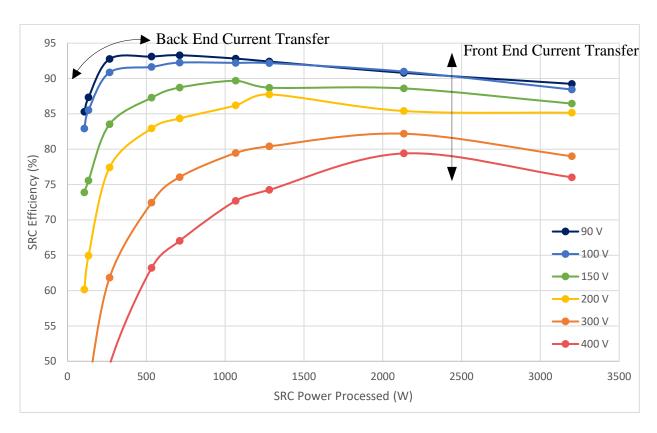

The performance case study was redone for SRC with the new loss parameters included in the simulation model. The converter was again swept over its load range from 133 W (60  $\Omega$ ) to 3200 W (2  $\Omega$ ) for a wider range of input voltages from 90 V to 400 V, see Figure 13 . The addition of losses altered the shape of the efficiency curve, however the general profile is still the same and the observations about current transfer with parallel energy storage via the front and back ends of

the SRC still apply. Arrows have been added to the graphs indicating the two methods of battery assisted current transfer and the effect each has on SRC performance. This graph provides key insights into the logic needed to design the assistance algorithm to correct optimize the SRC, in addition to providing a baseline to comparing performance with battery assistance.

Figure 13. SRC Performance with Losses Over Load Range for Varying Input Voltage

#### 3.0 BATTERY INTERFACING CONVERTER

## 3.1 BIDIRECITONAL BUCK-BOOST CONVERTER OVERVIEW

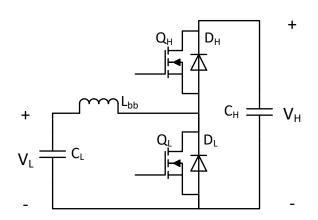

The DC/DC bidirectional buck-boost converter, also referred to as a type C chopper, was chosen as the converter to interface the SRC with the parallel battery storage. This topology is what is known as a two quadrant converter, meaning that it can transfer current in two directions depending on whether the high side or low side semiconductor is switched. In addition to bidirectionality, this topology boasts a simple circuit structure and straightforward design and control. As such, this converter is one of the most common converter designs used in conjunction with energy storage [33]–[38] and its operation is well understood [31], [38]–[40]. The circuit diagram of the bidirectional buck-boost converter can be seen in Figure 14, and it consists of a low side capacitor and inductor, half bridge converter, and high side capacitor. With regards to the larger microgrid system, the low side capacitor interfaces with the battery storage and the high side capacitor interfaces with the series resonant converter.

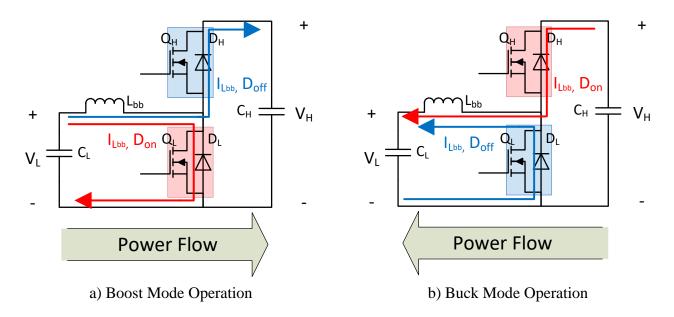

The converter has two modes of operation which correspond to the two directions of power transfer. In boost mode the low switch  $Q_L$  is actuated, resulting in current flow down through the low switch  $Q_L$  during the "on time" of the duty cycle, and current flow up through the high switch freewheeling diode  $D_H$  during the "off time" of the duty cycle. The net result is the transfer of power from the low side capacitor up to the high side capacitor, i.e. the battery is

discharged. In buck mode the high switch  $Q_H$  is actuated, resulting in current flow down through the high switch  $Q_H$  during the "on time" of the duty cycle, and current flow up through the low switch freewheeling diode  $D_L$  during the "off time" of the duty cycle. The net result is the transfer of power from the high side capacitor down to the low side capacitor, i.e. the battery is charged. The buck and boost modes of operation and the respective switching schemes are shown in Figure 15.

Figure 14. Bidirectional Buck-Boost Converter

Figure 15. Switching operation of Buck-Boost

# 3.2 BIDIRECITONAL BUCK-BOOST CONTROL METHODS

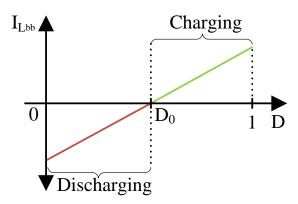

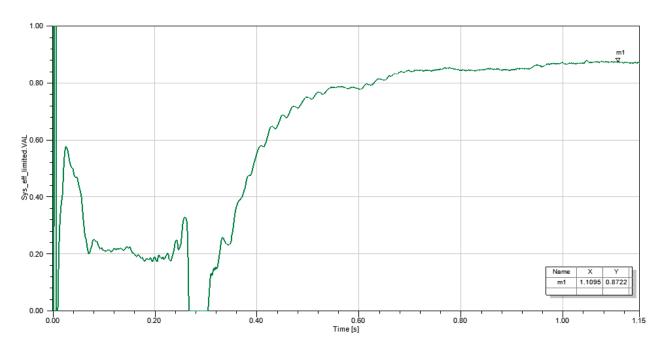

Regulation of the buck-boost converter as described above is typically done using pulse width modulation. The control is based around regulating either capacitor voltage or inductor current, however regulation requires two independent duty cycle controllers as battery charging and discharging differ from a control perspective [31], [38], [41]. For this system, the load voltage is already regulated by the SRC, thus current control of the bidirectional converters is the preferred choice. Moreover, for the purposes of injecting or absorbing power to adjust SRC performance, current control lends itself naturally to this objective as incremental adjustments to current correspond to incremental adjustments in power. Additionally [31] proposes a unified current controller which makes use of synchronous switching to regulate both charging and discharging with a single duty cycle. The relationship between duty cycle and inductor current (battery current) in this unified controller is shown in Figure 16 with the equation for the zero current duty cycle  $D_0$  in (22).

$$D_0 = \frac{V_L}{V_H} \tag{22}$$

Figure 16. Duty Cycle for Two Modes of Buck-Boost Operation under Unified Scheme

#### 3.3 BATTERY DESIGN

To adequately design a controller for the bidirectional buck-boost converter, additional information must be known about the low voltage battery storage side of the system. However modeling of a battery is quite complex as the parameters are dynamic and change with temperature, state of charge, and age [42]. This level of battery detail is outside of the scope of this research, and so a simple battery model was used, consisting of a static voltage source and static series resistance.

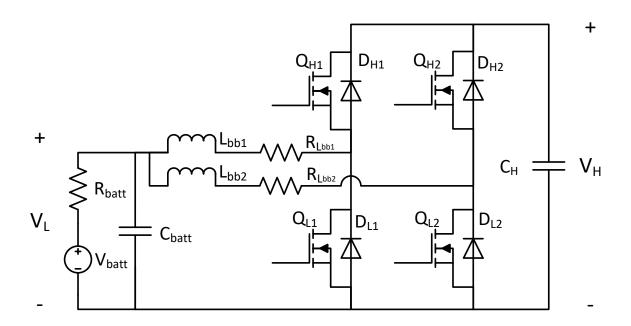

The chosen type of battery cell was a lithium ion cell which has a voltage range from 2.7 V to 4.2 V with a nominal voltage of 3.7 V [43]. Additionally lithium ion cells have a typical capacity ranging from 2 Ah to 2.5 Ah with a DC series resistance (DCR) between 15 m $\Omega$  and 35 m $\Omega$  [44]. It was desired to have a battery voltage of around half the regulated SRC output of 80 V, as this would place  $D_0$  of the back end buck-boost converter close to 50% duty cycle, allowing for equal charging and discharging ranges. Motivation for this is that the back end converter must be able to shift the load by half of the max rating of 3.2 kW in order to achieve optimal efficiency for the two extreme scenarios, full load and no load, see Figure 13. Rough estimations of the required battery capacity were done to produce relevant battery parameters and are detailed below.

To achieve a battery voltage of half the output voltage, 12 cells were stacked in series to achieve a nominal voltage of 44.4 V; a voltage of 42 V was used for the battery voltage source. To supply a maximum load of 3.2 kW at 42 volts, about 76 amps of current needed to be supplied. Assuming 2 Ah rated lithium ion cells, 38 cells were stacked in parallel to satisfy the current demand. Assuming a DCR of 35 m $\Omega$  per cell, the equivalent series resistance of the 12 by 38 cell battery was 11.05 m $\Omega$ ; a resistance of 11 m $\Omega$  was used for the battery series

resistance. With the battery parameters established the bidirectional buck-boost converter can be designed.

## 3.4 BIDIRECITONAL BUCK-BOOST CONVERTER DESIGN

The design of the front and back bidirectional converters is very similar, with the only difference being the rated power and voltage of the converters. As mentioned before the back end converter should be rated for at least half the max load of 3.2 kW. For the front converter it is desired to have the converter rated for the full power of the max load to provide voltage support on the DC bus in the case of complete PV shading. Finally it is desired to have both converters operate in the continuous conduction mode (CCM) region.

For CCM design, the first step is to determine an inductance that guarantee continuous current in the inductor for both buck and boost mode operation. Equations for minimum inductance are provided in [40] and are shown in (23) and (24) for buck and boost operation, respectively. In these equations P refers to the power processed by the converter,  $f_s$  refers to the converter switching frequency, and  $\eta$  refers to the converter efficiency, which was assumed to have a value of 0.95. The minimum inductance required for CCM is the largest of the buck and boost inductor values. It is important to note that CCM operation is not realistic for the no load power case, because as power decreases to zero the required inductance converges to infinity. Therefore a minimum power case must be chosen.

$$L_{buck} = \frac{V_L^2 \left( 1 - \frac{V_L}{V_H} * \frac{1}{\eta} \right)}{2 * f_s * P}$$

(23)

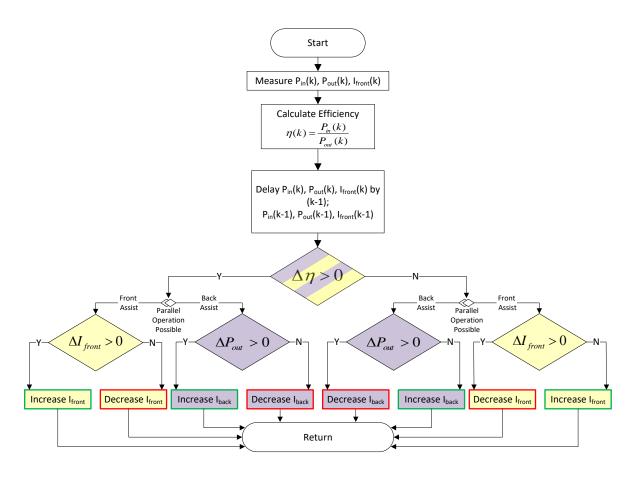

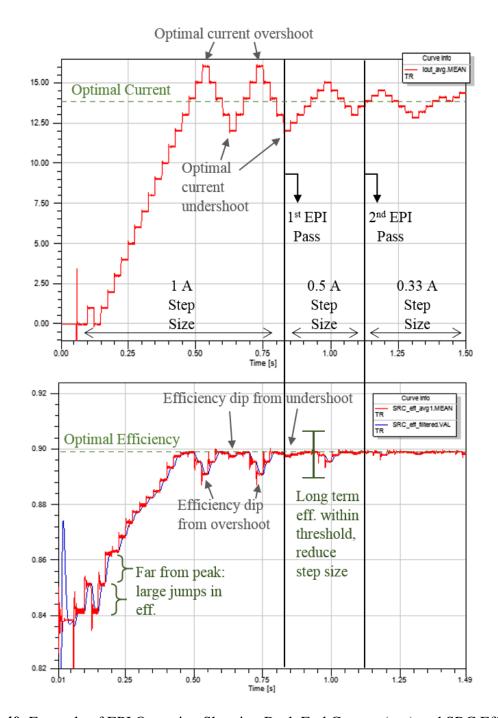

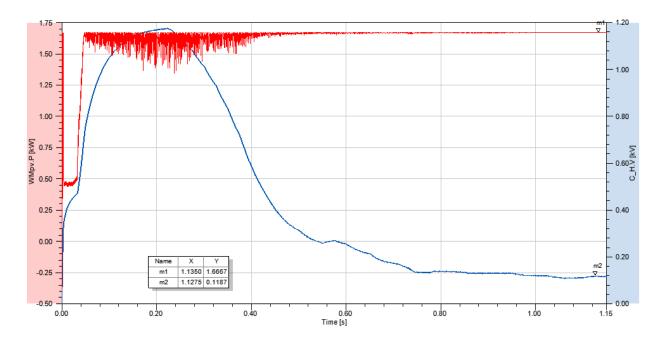

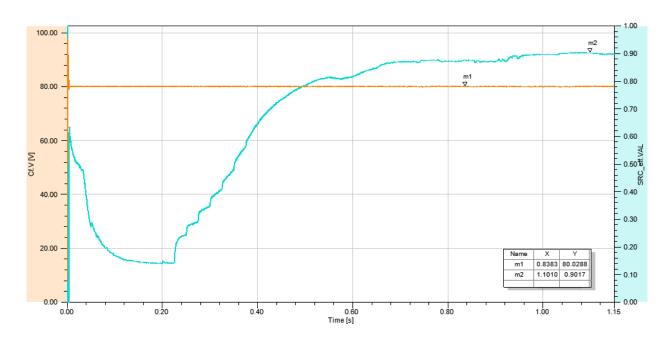

$$L_{boost} = \frac{2}{27} \frac{V_H^2}{f_s * P} \tag{24}$$