# Optimizing Embedded Software of Self-Powered IoT Edge Devices for Transient Computing

by

# Chen Pan

BS, Wuhan University of Science and Engineering, 2009

MS, Oklahoma State University, 2017

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2019

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Chen Pan

It was defended on

May 30, 2019

and approved by

Jingtong Hu, Ph.D., Assistant Professor Department of Electrical and Computer Engineering

Zhi-Hong Mao, Ph.D., Professor Department of Electrical and Computer Engineering

Samuel Dickerson, Ph.D., Assistant Professor Department of Electrical and Computer Engineering

Alex Jones, Ph.D., Professor Department of Electrical and Computer Engineering

Feng Xiong, Ph.D., Assistant Professor Department of Electrical and Computer Engineering

Youtao Zhang, Ph.D., Associate Professor Department of Computer Science

Dissertation Advisors: Jingtong Hu, Ph.D., Assistant Professor Department of Electrical and Computer Engineering

Zhi-Hong Mao, Ph.D., Professor Department of Electrical and Computer Engineering Copyright © by Chen Pan2019

# Optimizing Embedded Software of Self-Powered IoT Edge Devices for Transient Computing

Chen Pan, PhD

University of Pittsburgh, 2019

IoT edge computing becomes increasingly popular as it can mitigate the burden of cloud servers significantly by offloading tasks from the cloud to the edge. Currently, there are trillions of edge devices all over the world, and a majority of them work under power-constrained scenarios such as outdoor environmental monitoring. Considering the cost and sustainability, in the long run, self-powering through energy harvesting technology is preferred for these IoT edge devices. Nevertheless, a common and critical drawback of self-powered IoT edge devices is that their runtime states in volatile memory such as SRAM will be lost during the power outage. Thanks to the state-of-the-art non-volatile processor (NVP), the volatile states can be saved into the on-chip non-volatile memory before the power outage and recovered when harvesting power becomes available. Yet the potential of a self-powered IoT edge device is still hindered by the intrinsic low energy efficiency and reliability.

To fully exert the potentials of existing self-powered IoT edge devices, this dissertation aims at optimizing the energy efficiency and reliability of self-powered IoT edge devices through several software approaches. First, to prevent execution progress loss during the power outage, NVP-aware task schedulers are proposed to maximize the overall task execution progress especially for the atomic tasks of which the unfinished progress is subjected to loss regardless of having checkpoints. Second, to minimize checkpointing overhead on non-volatile memory, an intelligent checkpointing scheme is proposed which can not only ensure a successful checkpointing but also predict the necessity of conducting checkpointing to avoid excessive checkpointing. Third, to avoid inappropriate runtime MCU clock frequency with low energy utility, a CPU frequency modulator is proposed which adjusts the runtime CPU clock frequency adaptively. Finally, to thrive in ultra-low harvesting power scenarios, a light-weight software paradigm is proposed to help maximize the energy extraction rate. Besides, checkpointing is also optimized for more energy-efficient and light-weight operation.

## Table of Contents

| 1.0 | Int | $\mathbf{roduction}$                |

|-----|-----|-------------------------------------|

|     | 1.1 | Research Motivation                 |

|     | 1.2 | Existing Work                       |

|     |     | 1.2.1 Optimizing Power Regulator    |

|     |     | 1.2.2 Optimizing Checkpointing      |

|     |     | 1.2.3 Optimizing Run-time Execution |

|     | 1.3 | Research Contributions              |

|     | 1.4 | Dissertation Organization           |

| 2.0 | Tec | chnical Background                  |

|     | 2.1 | System Architecture                 |

|     | 2.2 | Basic Checkpointing                 |

|     | 2.3 | Voltage Monitoring                  |

|     | 2.4 | Sleep/Wake-up Managing              |

| 3.0 | Ato | omic Task Aware Task Scheduling     |

|     | 3.1 | Motivation                          |

|     | 3.2 | Related Work                        |

|     | 3.3 | System Overview                     |

|     | 3.4 | Power Prediction                    |

|     | 3.5 | Independent NVP Task Scheduler      |

|     | 3.6 | Dependent NVP Task Scheduler        |

|     | 3.7 | Experiments                         |

|     |     | 3.7.1 Evaluation of NVP Scheduler   |

|     |     | 3.7.1.1 Hardware Platform           |

|     |     | 3.7.1.2 Power Traces                |

|     |     | 3.7.1.3 Software Setup              |

|     |     | 3.7.1.4 Energy Consumption Analysis |

|     |     | 3.7.1.5 Sleep Mode vs. Working Mode     | 32 |

|-----|-----|-----------------------------------------|----|

|     |     | 3.7.1.6 Progress Comparison             | 34 |

|     |     | 3.7.1.7 Efficiency and Overhead         | 38 |

|     |     | 3.7.2 Evaluation of NTS Scheduler       | 40 |

|     |     | 3.7.2.1 Hardware Platform               | 40 |

|     |     | 3.7.2.2 Power Trace                     | 41 |

|     |     | 3.7.2.3 Software Setup                  | 41 |

|     |     | 3.7.2.4 Benchmark Setup                 | 43 |

|     | 3.8 | Summary                                 | 45 |

| 4.0 | Int | elligent Checkpointing Scheme           | 46 |

|     | 4.1 | Motivation                              | 46 |

|     | 4.2 | Related Work                            | 46 |

|     | 4.3 | Statistic based Checkpointing Avoidance | 48 |

|     |     | 4.3.1 Secure Checkpointing              | 52 |

|     | 4.4 | Experiments                             | 53 |

|     |     | 4.4.1 Experimental Setup                | 53 |

|     |     | 4.4.1.1 Hardware Platform               | 53 |

|     |     | 4.4.1.2 Power Trace                     | 53 |

|     |     | 4.4.1.3 Software Setup                  | 53 |

|     |     | 4.4.1.4 Performance of TCW              | 54 |

|     | 4.5 | Summary                                 | 56 |

| 5.0 | CP  | U Frequency Modulation                  | 57 |

|     | 5.1 | Motivation                              | 57 |

|     | 5.2 | Modeling and Analysis                   | 58 |

|     | 5.3 | Frequency Modulator                     | 60 |

|     |     | 5.3.1 Off-line Stage                    | 60 |

|     |     | 5.3.2 On-line Stage                     | 61 |

|     | 5.4 | Experiments                             | 61 |

|     |     | 5.4.1 Experimental Setup                | 61 |

|     |     | 5.4.1.1 Hardware Platform               | 61 |

|     |     | 5.4.1.2 Power Trace                                   | 62 |

|-----|-----|-------------------------------------------------------|----|

|     |     | 5.4.1.3 Benchmarks                                    | 62 |

|     |     | 5.4.2 Energy Utility Evaluation                       | 63 |

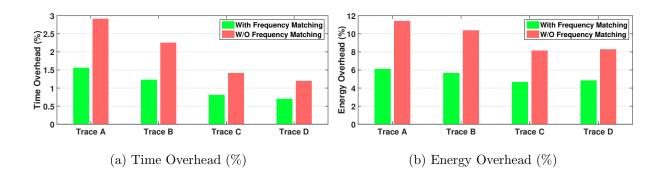

|     |     | 5.4.2.1 Overhead Analysis                             | 64 |

|     | 5.5 | Summary                                               | 65 |

| 6.0 | Th  | riving on Ultra-Low Harvesting Power                  | 66 |

|     | 6.1 | Motivation                                            | 66 |

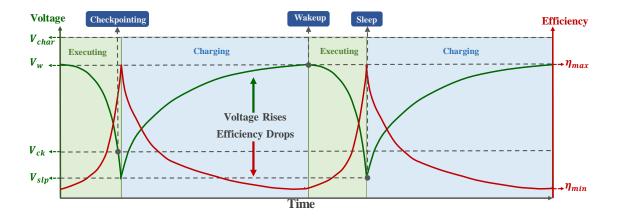

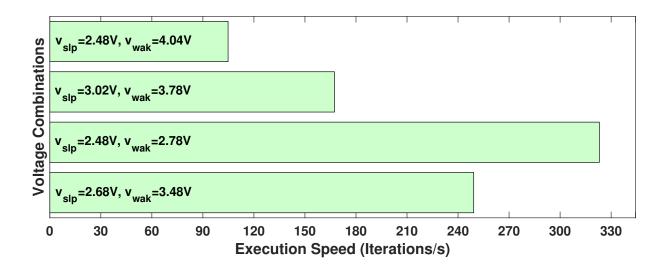

|     |     | 6.1.1 Wake-up Voltage Determines Efficiency           | 68 |

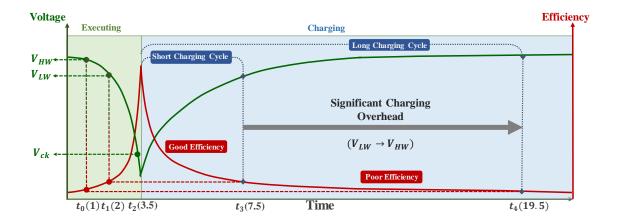

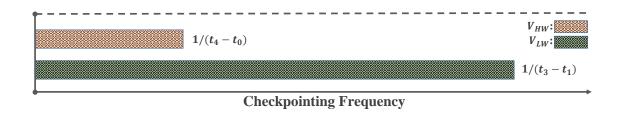

|     |     | 6.1.2 Routines vs. Efficiency                         | 71 |

|     | 6.2 | Related Work                                          | 73 |

|     |     | 6.2.1 System Architecture                             | 75 |

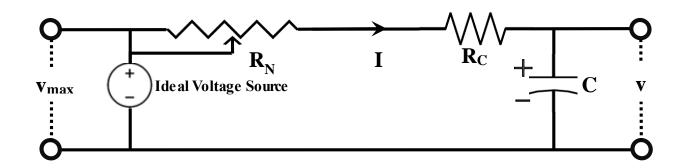

|     | 6.3 | Modeling and Analysis for $\xi(v_{Wak})$              | 75 |

|     |     | 6.3.0.1 Hardware Energy Efficiency                    | 75 |

|     |     | 6.3.0.2 Software Energy Efficiency                    | 78 |

|     |     | 6.3.0.3 Execution Energy Efficiency                   | 78 |

|     |     | 6.3.0.4 Influence of Checkpointing Data Size $\omega$ | 79 |

|     |     | 6.3.0.5 Influence of Wake-up Voltage $v$              | 79 |

|     | 6.4 | Modeling and Analysis for $\xi(v_{Wak}, v_{slp})$     | 82 |

|     |     | 6.4.1 Energy Modeling                                 | 82 |

|     |     | 6.4.1.1 Harvested Energy                              | 82 |

|     |     | 6.4.1.2 Hardware Energy Overhead                      | 82 |

|     |     | 6.4.1.3 Software Overhead                             | 83 |

|     |     | 6.4.1.4 Effective Energy                              | 84 |

|     |     | 6.4.2 Efficiency Analysis                             | 84 |

|     |     | 6.4.2.1 Formulation of $\xi$                          | 84 |

|     |     | 6.4.2.2 Optimization of $\zeta$                       | 85 |

|     |     | 6.4.2.3 Validation of modeling                        | 86 |

|     | 6.5 | Optimizing Voltages for Sleep/Wakeup                  | 88 |

|     |     | 6.5.1 Routine Handler                                 | 88 |

|     | 6.6 | Experiments                                           | 92 |

| 6         | 5.6.1 | Experir | nental Seti | ıp               |                   |            | •   | <br> | <br> |  | <br> | <br>• | 92 |

|-----------|-------|---------|-------------|------------------|-------------------|------------|-----|------|------|--|------|-------|----|

|           |       | 6.6.1.1 | Hardware    | Platforn         | n                 |            |     | <br> | <br> |  | <br> | <br>• | 92 |

|           |       | 6.6.1.2 | Power Tra   | ce               |                   |            |     | <br> | <br> |  | <br> | <br>• | 93 |

|           |       | 6.6.1.3 | Benchmar    | ks               |                   |            |     | <br> | <br> |  | <br> | <br>• | 93 |

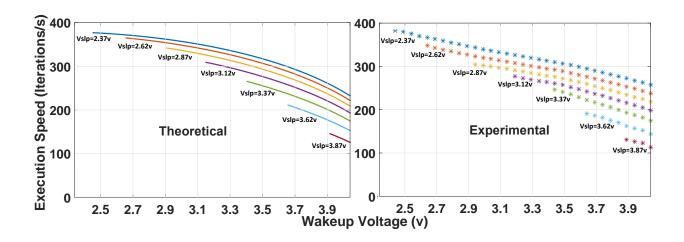

| 6         | 5.6.2 | Experir | nental Eva  | luation          |                   |            |     | <br> | <br> |  | <br> | <br>• | 93 |

|           |       | 6.6.2.1 | Observation | on of $\zeta(a)$ | $v_{slp}, v_{we}$ | $_{ak})$ . |     | <br> | <br> |  | <br> | <br>• | 93 |

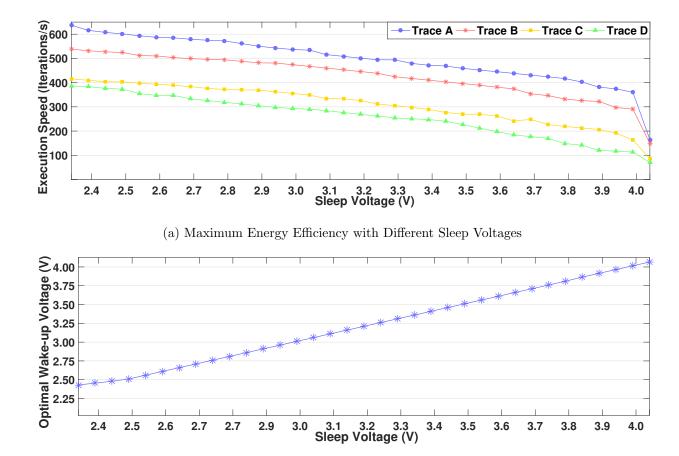

|           |       | 6.6.2.2 | Energy Ef   | ficiency         | Evalua            | ation      | ١., | <br> | <br> |  | <br> | <br>• | 95 |

| 6.7 S     | Sumn  | nary    |             |                  |                   |            |     | <br> | <br> |  | <br> | <br>• | 96 |

| 7.0 Cond  | clusi | on      |             |                  |                   |            |     | <br> | <br> |  | <br> |       | 97 |

| Bibliogra | nhv   |         |             |                  |                   |            |     |      |      |  |      |       | 98 |

## List of Tables

| 1 | Task Information (Tab) | 23 |

|---|------------------------|----|

| 2 | Task Information       | 32 |

# List of Figures

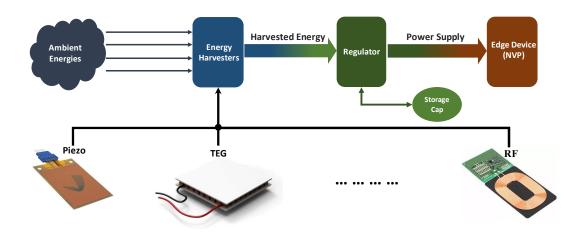

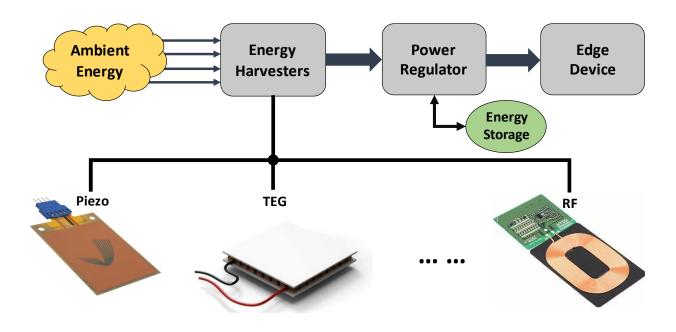

| 1  | System Architecture of Self-Powered Non-Volatile IoT Edge Device          | 8  |

|----|---------------------------------------------------------------------------|----|

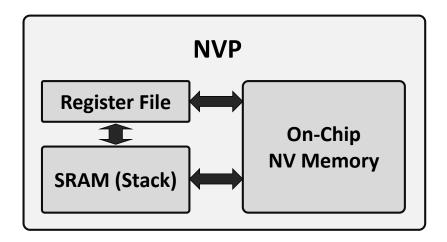

| 2  | NVP Architecture                                                          | Ć  |

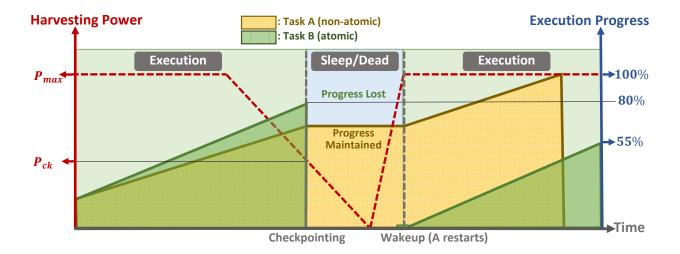

| 3  | Atomic Task B is Unfinished Before The Power Outage Resulting in Progress |    |

|    | Setback                                                                   | 14 |

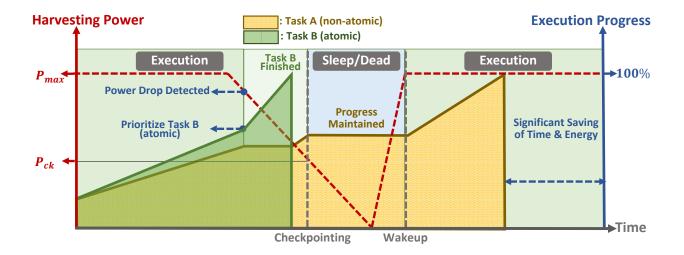

| 4  | Prioritizing atomic Task B to Finish Before The Power Outage Results in   |    |

|    | Progress Maximization                                                     | 15 |

| 5  | System Architecture                                                       | 18 |

| 6  | NVP Scheduler Overview                                                    | 22 |

| 7  | Example DAG                                                               | 29 |

| 8  | Power Trace Used for Experiments                                          | 31 |

| 9  | Power Consumption of Benchmarks                                           | 33 |

| 10 | Power Consumption of Low Power Mode vs Working Mode                       | 33 |

| 11 | Execution Speed of Register Operation                                     | 34 |

| 12 | Execution Speed of SRAM Writes                                            | 35 |

| 13 | Execution Speed of FRAM Writes                                            | 36 |

| 14 | Execution Speed of Thermometer                                            | 37 |

| 15 | Execution Speed of Accelerometer                                          | 38 |

| 16 | Execution Speed of UART communication                                     | 39 |

| 17 | Energy Efficiency                                                         | 40 |

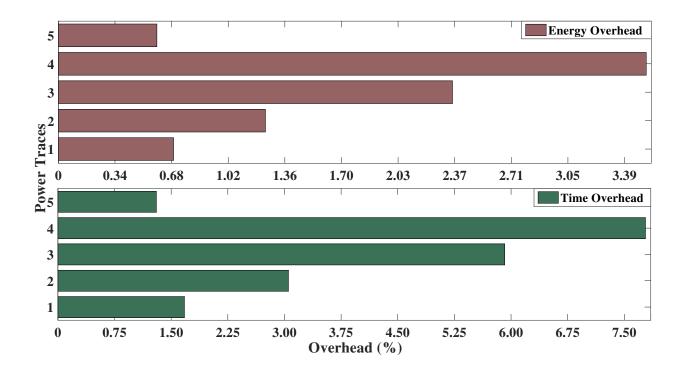

| 18 | Energy and Time Overhead                                                  | 41 |

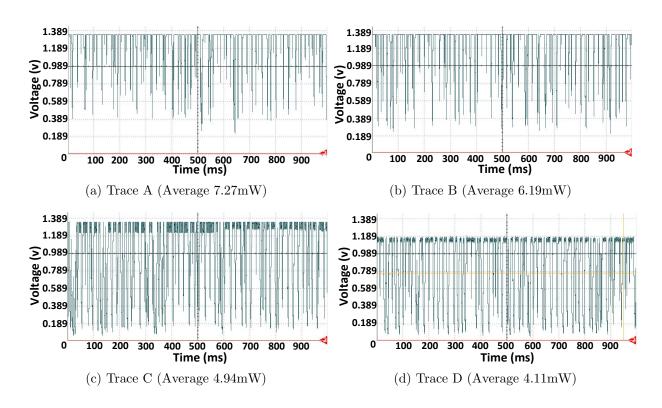

| 19 | Power Traces                                                              | 42 |

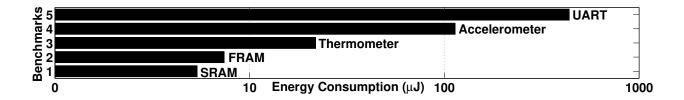

| 20 | Required Energy of Each Benchmark                                         | 42 |

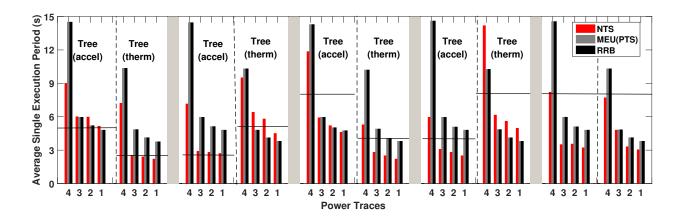

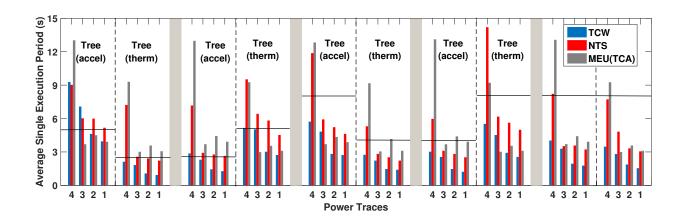

| 21 | Average Single Execution Period with NTS                                  | 44 |

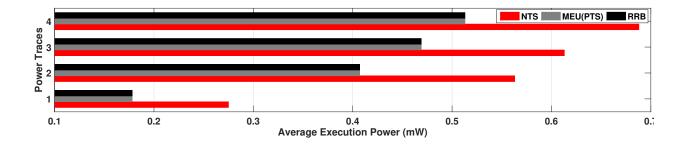

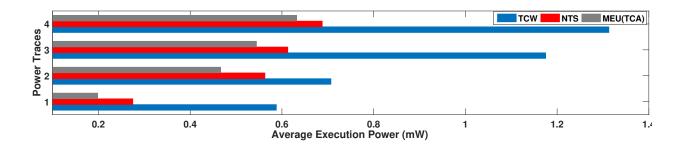

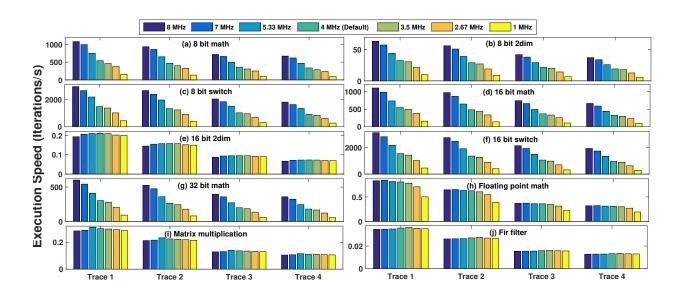

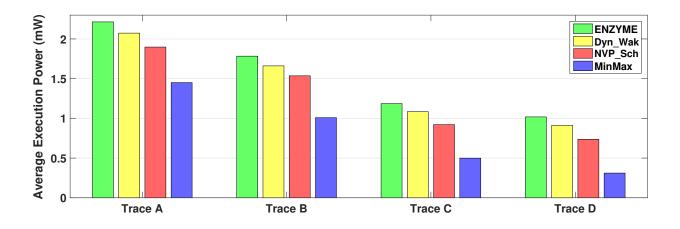

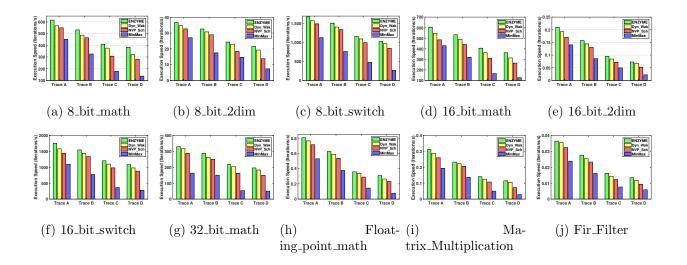

| 22 | Average Execution Power of Benchmarks Under Different Power Traces        | 45 |

| 23 | Four Out of Nine Checkpointings Can Be Avoided without Progress Setback.  | 50 |

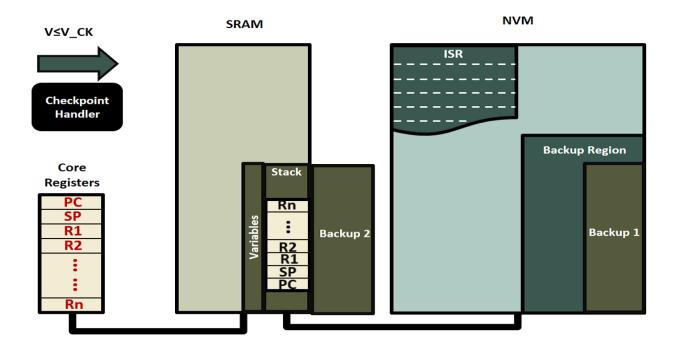

| 24 | Dual-Backup Checkpointing Handler.                                        | 52 |

| 25 | Single Execution Period with TCW                                             | 55 |

|----|------------------------------------------------------------------------------|----|

| 26 | Average Execution Power of Benchmarks Under Different Power Traces           | 55 |

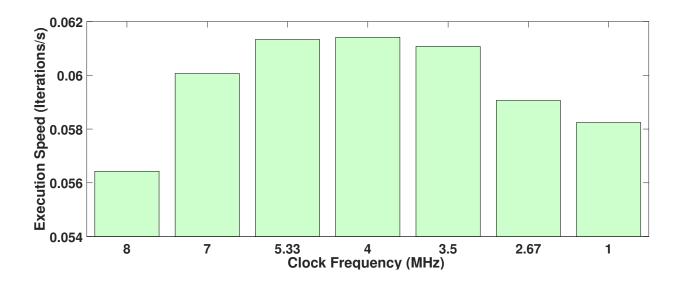

| 27 | Energy efficiency with different clock frequency                             | 58 |

| 28 | Frequency matching based task schedule                                       | 61 |

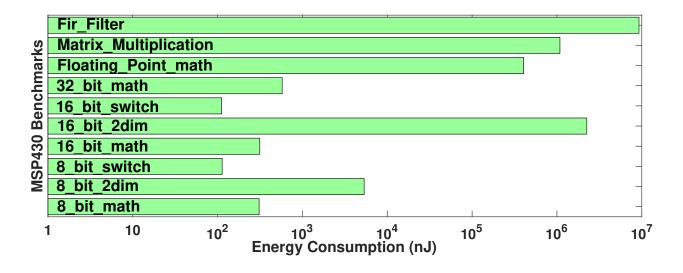

| 29 | Required energy of each benchmark                                            | 62 |

| 30 | Energy Utility under Available Frequencies                                   | 63 |

| 31 | Time and energy overhead                                                     | 64 |

| 32 | Changes of Charging Efficiency and Voltage on the Edge Device with Ultra-low |    |

|    | Harvesting Power                                                             | 68 |

| 33 | Influence of Wake-up Voltage on Charging Cycle and Efficiency of the Edge    |    |

|    | Device with Ultra-low Harvesting Power                                       | 69 |

| 34 | Influence of the Wake-up Voltage on Checkpointing Frequency of the Edge      |    |

|    | Device with Ultra-low Harvesting Power                                       | 70 |

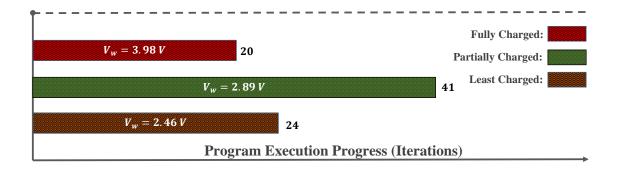

| 35 | Measurements of the Execution Progress with Different Working Voltages       | 71 |

| 36 | Energy efficiency with different voltage combinations                        | 72 |

| 37 | Architecture of self-powered edge device                                     | 75 |

| 38 | Capacitor Charging Circuit                                                   | 76 |

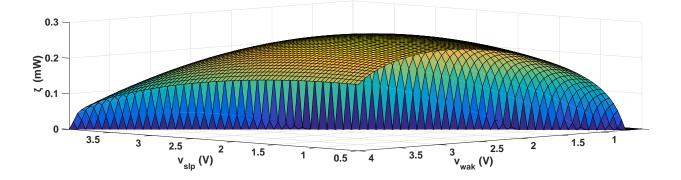

| 39 | Concavity of $\zeta$ in respect of $v_{slp}$ and $v_{wak}$                   | 86 |

| 40 | Optimal $\zeta$ and $v_{wak}$ with given $v_{slp}$                           | 87 |

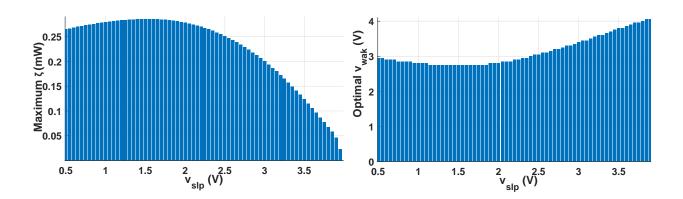

| 41 | Execution speed (theoretical vs experimental)                                | 87 |

| 42 | Maximum Energy Efficiency and Optimal Wakeup Voltages with Different         |    |

|    | Sleep Voltages                                                               | 94 |

| 43 | Average execution power                                                      | 95 |

| 44 | ENZVME vs. Baselines regarding energy efficiency                             | 96 |

#### 1.0 Introduction

In this era of the Internet of Things (IoT), an increasing number of electronics "things" that embedded with software, sensors, and connectivity forms a seamless web to facilitate our daily life. Generally, the majority of these "things", such as wireless sensor nodes, are at the edge of IoT network, which bridges between the physical and cyber world by sensing the real-life information and converting it into the digital representations for IoT applications. It is estimated that IoT will consist of almost 50 billion devices by 2020, which brings a challenge of how to power these vast number of edge devices sustainably and efficiently.

#### 1.1 Research Motivation

While battery power is not a favorable solution in the long run due to size, longevity, safety, and recharging concerns, energy harvesting, out of all possible energy sources, is one of the most promising techniques to meet both the size and power requirements of edge devices. A typical self-powered IoT edge device is usually composed of an energy harvester, a power regulator, a storage capacitor, and an embedded edge device. Energy harvesters can harvest different kinds of ambient energy, such as kinetic, electromagnetic radiation (light and RF), and thermal energy. The harvested energy will be converted into electric energy and flow through the power regulator to provide targeting voltage for charging the storage capacitor or directly powering the edge devices.

Although the future of self-powered IoT edge devices is promising, a critical drawback of most energy harvesters is that the harvesting power is often weak and intermittent, resulting in frequent power interruptions to edge devices. Frequent system turning on and off will jeopardize the data integrity causing significant progress setback if a program's intermediate execution state is not saved. With the help of non-volatile processors (NVP), both the program's execution state and active contents in its stack can be saved into non-volatile memory (NVM), before each power outage. This process is known as checkpointing. The

next time when the harvesting power recovers, the execution state can be restored to volatile RAM and program execution resumes. In this way, edge devices are resilient to power outages and the execution progress can be "intermittently" accumulated.

Nevertheless, even with the help of NVP, the potential of a self-powered IoT edge device is still severely hindered by the intrinsic low energy efficiency and reliability making it challenging to deliver reliable and efficient edge service for satisfying IoT service requests. These drawbacks of self-powered IoT edge devices mainly come from the following four aspects.

- First, although all tasks' runtime execution state can be saved successfully before power outage by NVP, not all tasks can be resumed correctly. Tasks, such as sensing and communication, are susceptible to the time delay. Their execution states, although can be checkpointed successfully, become useless when being resumed after a period of time. Therefore, extra energy and computation resources are required to compensate for their progress loss during the power outage.

- Second, as the checkpointing involves write operation on non-volatile memory, which is both time and energy-consuming, extra time and energy are required to support checkpointing. Considering the limited harvesting power, checkpointing can significantly affect the energy overhead especially when harvesting power becomes extremely small and unstable. What's more, as the endurance of non-volatile memory gradually wears out with each new write operation, checkpointing also threatens the lifetime of edge devices with NVP. Further, if checkpointing is unsuccessful, a significant progress setback would occur.

- Third, each tasks has its own optimal CPU clock frequency for which neither too small nor too large can bring optimal energy efficiency. Therefore, an inappropriate configuration of run-time CPU clock frequency can escalate the already low energy efficiency.

- Finally, under the ultra-low harvesting scenario, the energy harvester and power regulator bundle suffers from severe degradation in energy efficiency making energy efficiency much lower and checkpointing much frequent which further escalates the energy efficiency and QoS of IoT services.

These four challenges need to be addressed before the self-powered IoT edge device can provide a reliable, energy-efficient, and environment-friendly IoT end service.

#### 1.2 Existing Work

In order to solve the aforementioned challenges, existing work mainly focuses on three optimization perspectives including improving power regulator efficiency, reducing check-pointing overhead, and improving runtime execution efficiency.

#### 1.2.1 Optimizing Power Regulator

As the power supply of self-powered IoT edge devices, the energy harvester extracts energy from the ambient environment. Solar [38, 40, 48, 15], wind [38], footsteps [45, 47, 20], breathing [47], blood pressure [47], and body heat [21, 38, 47] are all possible energy harvesting sources. The power harvested from these energy sources has different magnitudes. For example, solar energy can generate a large magnitude of power at a power density of  $15mW/cm^2$ . The footstep is controllable human power, and the amount of harvested power can be as much as 67W [20] during a brisk walk. For ultra-low-power devices, the sources with low power densities, such as breathing (0.42W), and body heat  $(2.4\sim4.8W)$ , can provide sufficient power to drive the devices at low duty cycles [17, 21, 48, 30, 52]. A common drawback of these energy sources is that they are often weak or intermittent, When an edge device is powered directly by an energy harvester, the supply voltage may be too low to drive the edge device. Even if the supply voltage is higher enough such as solar power, the intermittent nature would cause frequent power interruption resulting in data corruption and execution progress setback. Therefore, the power regulator is a key component, which harnesses the harvested energy for supplying targeting voltage to powering IoT edge device.

For a power regulator, upon supplying power to the IoT edge device, it also consumes power rendering lower energy efficiency for powering edge devices. The situation will be even worse when harvesting power is ultra-low and unstable. A considerable amount of research has been conducted for reducing the hardware overhead by improving the regulator efficiency through impedance matching techniques [8, 19, 9, 18, 46, 24]. These work mainly focus on power regulator optimization, for instance [8] proposes effective switching frequency technique for voltage converter to deliver maximum output power. [46] conducts circuit-level

design which enables the regulator to extract power from multiple low-power energy harvesting sources with maximum efficiency. [9] proposes a duty cycle based impedance adjustment technique for the maximum power extraction from a thermoelectric energy source without sacrificing power conversion efficiency. what's more [51, 49, 50] propose through-silicon-via inductors which can be used by energy harvesting circuits with minimum footprint. Further, [63] proposes a run-time simulation framework of both power delivery and architecture and captures their interactions for energy efficiency optimization.

#### 1.2.2 Optimizing Checkpointing

After harvesting power has been delivered to the edge device, a portion will be used to support checkpointing which saves runtime state from volatile memory into the non-volatile region before a power outage happens. Checkpointing involves write operation on nonvolatile memory, which not only is time and energy consuming but also reduces the limited endurance of NVP resulting escalation of reliability. Therefore, many pieces of research work focus on reducing checkpointing overhead through both hardware and software techniques.

Hardware checkpointing stores the system state and data automatically by hardware. For example, Yu et al. [16] propose a non-volatile processor architecture that integrates non-volatile elements into volatile memory at bit granularity. Wang et al. [53] design a FRAM based processor, which attaches an NV-FRAM cell to each volatile standard flip-flop. The flip-flops are accessed for normal execution while the FRAM cells are used to checkpoint the states in flip-flops at power failure. This processor can backup and restore the processor state and data within  $3\mu s$ . Sakimura et al. propose the non-volatile magnetic flip-flops [43] and a 20MHz non-volatile micro-controller with STT-RAM [44]. Recently, Liu et al. propose an enhanced NVP based on ReRAM which has the highest integration level [27]. Also, Li et al. propose the non-volatile I/O enabling automatic reconfiguration of I/O interfaces [23].

Besides hardware checkpointing, there are also software mechanisms that checkpoint the processor's state and other volatile data into non-volatile memories. For example, Mementos [42] is a software mechanism for transiently powered RFID-scale devices. Some trigger points are placed after each call instruction or at each loop latch. At run-time, when these

trigger points are reached, the supply voltage is checked with an ADC. If this voltage is below a threshold, a snapshot of the system state is saved to the flash memory. Quickrecall [14] integrates FeRAM into the main memory to increase the checkpointing efficiency which reduces the backup data size and lowers the failure voltage threshold. Hibernus [6] and Hibernus++ [6] propose interrupt-based checkpointing mechanisms. In these mechanisms, the system stated is checkpointed only once immediately before the power failure, then the system hibernates. This mechanism requires frequent voltage checking and automatic interrupts to checkpoint or restore the system state. MEU [34] proposes prototyping techniques for a joint reduction of software and hardware overhead with software solutions.

#### 1.2.3 Optimizing Run-time Execution

Even though the power regulator and checkpointing operation are optimized, inappropriate runtime clock frequencies can significantly reduce the runtime energy utility. Previous research on DVFS-based techniques [58, 12, 29] mainly focus on how to lower down the execution frequency appropriately so that the power consumption of the embedded system can be reduced. However, low CPU frequency doesn't necessarily guarantee high energy efficiency. In fact, when CPU frequency becomes lower, the reduction of execution power may not be significant. Yet the execution time could become significantly longer. As a result, energy efficiency may become lower. Besides, accessing hardware with a large latency such as non-volatile memory or GPIO can be the bottleneck of the actual execution speed. As such, it is necessary to optimize execution frequency accordingly for each program. Therefore runtime frequency should be adjusted accordingly.

All existing optimization techniques mentioned above that can be used to optimize the energy efficiency of self-powered IoT edge devices can be categorized into hardware and software solutions. Compared with hardware solutions, software solutions have advantages including low cost, full of flexibility, significant reduction of development cost, better adaptability, etc. Besides, what is even more important is that software solutions are able to provide equally competitive performance optimization compared with hardware solutions. Therefore, software solutions become increasingly popular to optimize the performance of

self-powered IoT edge devices. This dissertation is one of such kind that proposed several embedded software approaches to address the aforementioned challenges so that the potential of self-powered IoT edge devices can be fully exerted for better IoT edge services.

#### 1.3 Research Contributions

This dissertation proposes embedded software solutions to address the aforementioned challenges. Compared with the aforementioned research work, this dissertation includes a project that focuses on maximizing execution progress of the atomic task which is subjected to progress loss during the power outage regardless of having NVP equipped. What's more, this dissertation also covers the projects that optimize checkpointing and runtime clock frequency accordingly for low-powered edge devices uniquely through software approaches. Further, this dissertation includes a project which is the first to propose a software paradigm dedicated to self-powered IoT edge devices to thrive in ultra-low harvesting power scenarios. In a nutshell, this dissertation focuses on four different angles to address the aforementioned critical issues challenging self-powered IoT edge devices.

- First, to prevent execution progress loss during the power outage, NVP-aware task schedulers are proposed to maximize the overall task execution progress especially for the atomic tasks which are better to finish execution before the power outage.

- Second, to minimize both the time and energy overhead of checkpointing operation, an intelligent checkpointing scheme is proposed which not only can ensure a successful checkpointing but also can predict the necessity of conducting checkpointing to avoid excessive checkpointing overhead.

- Third, to avoid inappropriate runtime CPU clock frequency, which consumes extra energy while delivering less execution progress, a CPU frequency Modulator is proposed which adjusts the runtime CPU clock frequency accordingly.

- Finally, to thrive in ultra-low harvesting power scenarios, a light-weight software-based paradigm is proposed to help maximize the energy extraction rate of energy harvester

and power regulator bundle. Besides, checkpointing under such an ultra-low scenario is also optimized for more energy-efficient and light-weight operation.

#### 1.4 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 provides the technical background. After that, Chapter 3 proposes an NVP-aware task scheduler to prioritize the atomic task before power outage so that the overall task execution progress can be maximized. To minimize the checkpointing overhead, Chapter 4 proposes an intelligent checkpointing scheme to avoid unnecessary checkpointing. To improve runtime energy efficiency, Chapter 5 proposes a CPU frequency modulator to adjusts the runtime CPU clock frequency accordingly for different tasks. To thrive in ultra-low harvesting power scenarios, Chapter 6 proposes a light-weight software paradigm to optimize energy extraction rate as well as a checkpointing scheme for more energy-efficient and light-weight operation. Finally, Chapter 7 concludes this dissertation.

#### 2.0 Technical Background

This chapter first proposes the targeting system architecture and then introduces the fundamental supporting techniques of this dissertation including checkpointing, voltage monitoring, and sleep/wakeup managing.

#### 2.1 System Architecture

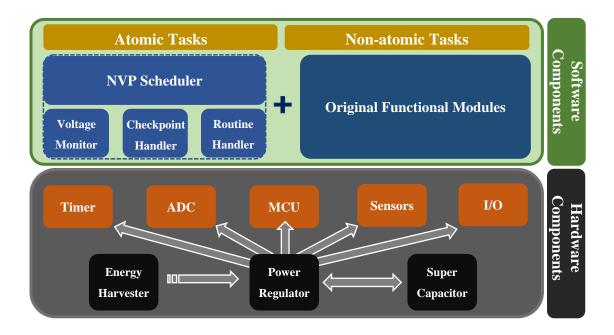

In this section, a general architecture of the self-powered non-volatile IoT edge device is introduced which is shown in Figure 1.

Figure 1: System Architecture of Self-Powered Non-Volatile IoT Edge Device

The targeting self-powered self-powered IoT edge device is equipped with a non-volatile processor and can harvest energy from multiple energy sources in the ambient environment and convert them into electrical energy. Typical energy sources include piezoelectric, thermal (TEG), radio frequency (RF), etc. As most kinds of harvested energy are weak and intermittent, in our target harvesting scenario, the energy harvester cannot power the edge device continuously. Once the program execution has used up the stored energy in the capacitor,

the non-volatile processor conducts checkpointing for maintaining execution progress. After that, the edge device goes to sleep and waits for the storage capacitor to be charged up again by the regulator which harnesses the harvesting power and provides the target supply voltage to the edge device. Once the capacitor has been charged up, the edge device can start or resume the execution until the stored energy is used up again.

#### 2.2 Basic Checkpointing

In this section, the basic checkpointing mechanism will be introduced. The targeting edge device is equipped with NVP. Based on the structure difference of NVP, there are two kinds of checkpointing operations which are software-based checkpointing and hardware-based checkpointing. This dissertation only focuses on software-based checkpointing which is flexible and easy for implementation. Figure 2 shows the targeting NVP architecture for implementing software-based checkpointing.

Figure 2: NVP Architecture

As we can see from Figure 2, for NVP aside from containing traditional on-chip volatile memory, including register file and SRAM, NVP also includes on-chip non-volatile memory. When a power outage occurs, all contents of the processor registers and SRAM should be

checkpointed to on-chip non-volatile memory. Hence, all the computation states can be saved. Once the power comes back on again, the computation can resume with the saved computation states.

Since the targeting NVP only support software-based checkpointing, there is no hardware to automatically save computation states. Hence, the software should take this responsibility. When detecting a low voltage below the preset threshold, the system will enter the checkpoint stage. First, all registers will be pushed onto the stack. Then the whole stack, which includes contents of all registers and all temporary variables, will be checkpointed from SRAM to non-volatile memory. One challenge here is how to save the program counter (PC) since we are not allowed to move PC explicitly. The trick we used is that, whenever a callee is called or interrupt service routine is invoked, the PC will be automatically pushed onto the stack. Then, we can safely save the PC together with other registers to the on-chip NVM

#### 2.3 Voltage Monitoring

In this section, the basic voltage monitoring procedure is introduced. For voltage monitoring, there are mainly two categories which are hardware-based and software-based voltage monitoring. For hardware-based voltage monitoring techniques, there is dedicated hardware, known as voltage monitor, to keep monitoring the voltage of the target. If the voltage reaches the threshold, the voltage monitor will generate an I/O interrupt for preemption on NVP which then will know the power interruption. For the software-based voltage monitoring technique, the voltage detection is initiated by NVP which configures ADC accordingly for different scenarios and even coordinate with timer for voltage monitoring in a timely manner.

Software-based voltage monitoring techniques have significant advantages over hardware-based voltage monitoring mainly due to its flexibility and similar energy consumption. For a hardware-based voltage monitor, it only warns NVP systems about the "poor" quality of the harvesting power through I/O interrupts based on the hardwired voltage threshold. However, this threshold has a large impact on the overall performance of self-powered IoT edge devices. On the one hand, If the threshold is too high the NVP system wastes energy with frequent

checkpointing. On the other hand, if the threshold is too low, the checkpointing may fail. For that matter, after deployment, if the condition of the environment keeps changing, the hardwired threshold will degrade the performance of the edge devices. Therefore, for self-powered IoT edge devices, the software-based voltage monitoring technique is preferable where the NVP system needs to proactively initiate voltage detection. As the ADC detection time is trivial compared with the execution time, this software-based voltage monitoring overhead is negligible.

For the voltage monitoring target, many traditional techniques choose Vcc as the monitoring voltage source. However, Vcc is not suitable for monitoring and this dissertation uses the voltage on the storage capacitor for monitoring. The disadvantages of monitoring Vcc is that Vcc remains stable due to the power regulator unless the stored energy is almost drained out. In this way, once the voltage monitor detects the Vcc drop, NVP may not have enough time to respond for checkpointing, resulting in the progress setback. Therefore, Vcc is ruled out as the voltage detection source. For the voltage on the storage capacitor, it reflects the actual power supply of the energy harvester. Specifically, if the voltage on the storage capacitor drops, the energy harvester generates less power than the edge device consumed. Otherwise, the harvested power is sufficient to drive the edge device.

#### 2.4 Sleep/Wake-up Managing

Once the checkpoint handler saves the run-time states into NVM, the edge device should be in sleep mode other than continue execution or shut down the entire system. There are mainly three reasons that make sleep mode a better option than the other two options.

- 1) After checkpointing, the remaining energy is insufficient to support another checkpointing. Therefore any further execution wastes energy as the state cannot be saved.

- 2) It is much faster for the NVP system to recover from sleep mode than cold reboot after being shut down.

- 3) Once the system is dead, it will automatically restart once the input voltage is beyond the cold start voltage. However, if the power supply is still insufficient, the system will

fail again at the very beginning. However, in sleep mode, ADC and timer are still allowed to monitor the voltage with negligible energy consumption. So the system can wake up when power is sufficient

.

Once the harvesting power comes back on again, the edge device will wake up given a preset wake-up voltage  $V_{wak}$ , which should at least support one checkpointing and a period of execution allowing new progress to be accumulated. Notice that, if the edge device is dead and once the power comes back on again, the edge device will initiate the cold start which requires much higher power than it was in low-power mode. In this case, if the harvesting power is insufficient, the edge device will be stuck at the very beginning as the harvested energy will always be drained out and cannot be preserved. Our solution is that at the very beginning of the startup stage, the NVP system needs to measure  $V_{cap}$ . If  $V_{cap} < V_{wak}$ , the NVP system needs to go back to sleep mode. This can avoid the system from stagnating at the cold starting stage.

#### 3.0 Atomic Task Aware Task Scheduling

This chapter presents the research topic regarding task scheduler design for self-powered IoT edge devices with NVP. The organization of this chapter is as follows. First, research motivation and related work are provided. Then, the targeting system overview is given. After that, the proposed techniques including power prediction, independent task scheduler, and dependent task scheduler will be introduced in detail. Finally, the corresponding experiments and summary are provided.

#### 3.1 Motivation

For self-powered IoT edge devices, before the power outage, programs' runtime execution state needs to be saved from volatile SRAM into on-chip NVM through checkpointing operation. However, not all tasks' execution states need to be pushed into stacks for checkpointing. Tasks, such as sensing and communication, are susceptible to the time delay. Their execution states, although can be checkpointed, become useless when being resumed after a period of time. These tasks should finish before the power outage once scheduled. Otherwise, their execution has to be started over when the power comes back on again. These tasks are defined as atomic tasks. Other tasks that can be checkpointed such as computation and data processing are defined as non-atomic tasks. To reduce the checkpointing overhead, the task scheduler should try its best to finish schedule as many unfinished atomic tasks as possible for completion before the power outage.

The following example will demonstrate how the unfinished atomic tasks affect system performance. The system that we target in this example is checkpointing enabled and equipped with both volatile and non-volatile memories. Assume that successful checkpointing can be ensured. For illustration purposes, task A is a non-atomic task and task B is an atomic task. Initially, tasks are executed concurrently with a round-robin scheduler. Given a harvesting power trace, the execution progress of both tasks are shown in Figure. 3.

Figure 3: Atomic Task B is Unfinished Before The Power Outage Resulting in Progress Setback.

In Figure. 3, the red dash line represents the energy harvesting power trace, the yellow shadow represents the execution progress of task A, and the green bars represent the execution progress of task B. From the beginning, the execution progresses of both tasks are gradually accumulated until the harvesting power drops below  $P_{ck}$ . Since A is non-atomic, its execution status including all the register files and stack can be stored into non-volatile memory when checkpointing is triggered. Therefore, once the power comes back on again the system wakes up and the program execution of A resumes.

However, Since task B is atomic, it loses entire execution status during the power outage. Once the power comes back on again, B has to restart from the very beginning. As we can see, before the power outage, B is almost finished and has the execution progress of 80%, which is a significant setback once this progress is completely lost during the power outage. One simple and intuitive solution to avoid the progress setback is to prioritize B once before the power outage happens. In this way, as A will not suffer from progress setback, if B can finish before the power outage, the overall progress can be maintained. Given the same power trace, figure. 4 shows the execution progress of both A and B with prioritized scheduling.

Figure 4: Prioritizing atomic Task B to Finish Before The Power Outage Results in Progress Maximization.

From Figure. 4, we can see that after detecting the power drop, B has been prioritized immediately and it finishes right before the system conducts checkpointing. In this way, the execution progress of both A and B can be maintained. What is even more appealing is that, compared with Figure. 3, a significant amount of time and energy are saved, which can be further used for other program executions. Overall, the execution progress can be significantly improved.

Although prioritizing B can maximize the overall execution progress, before conducting the priority-based scheduling, it is crucial to know whether B can finish before the power outage. This is because, if B cannot finish, the system will waste even more energy and have a severe progress setback during the power outage. To evaluate whether task B can finish before the power outage, the power analysis should be taken place for evaluation, which is proposed in section 3.4

#### 3.2 Related Work

Energy harvesting extracts power from the ambient environment and is often used to deploy long lifetime battery-less devices. Solar, wind, footsteps, breathing, blood pressure, and body heat [21, 38, 47] are all promising energy harvesting sources. They have different characteristics of predictability, controllability, and magnitude. For example, solar energy is predictable and can generate a large magnitude of power at a power density of  $15mW/cm^2$ . The footstep is a controllable human power and the amount of harvested power can be as much as 67W [20] during a brisk walk. For ultra-low-power devices, the sources with low power densities, such as breathing (0.42W), and body heat  $(2.4\sim4.8W)$ , can provide sufficient power to drive the devices at low duty cycles [48]. With proper configuration and management [17], it is feasible to operate a whole system with purely harvested energy.

In order to make systems power-failure proof, non-volatile memory based processors (NVP) [56] are developed. In these processors, non-volatile memory [35, 32] is attached to the processor, and the volatile execution state is checkpointed into the non-volatile memory upon the power outage. Researchers showed that checkpointing is a feasible method to save the runtime state [41, 42] with nonvolatile memory for energy-harvesting devices. Microcontrollers such as TI's MSP430 series [2] employ FRAM as an on-chip memory. Ransford et al. [42] present a software system, mementos, for transiently powered RFID-scale devices with energy-aware state checkpointing method. This system deploys Flash memory to back up the volatile content. Registers are pushed into the stack and then saved to the Flash memory. Since Flash memory has a limited write endurance and slow write speed, the time and energy overhead is large. Similarly, Wireless Identification and Sensing Platform (WISP) [4] was developed to achieve a similar goal.

Instead of checkpointing the execution state into on-chip or off-chip memory at a low speed, ferroelectric non-volatile register-based processors are proposed for energy-harvesting devices [53, 64]. This kind of processor attaches a nonvolatile memory cell to each volatile element and therefore allows fast local backup of intermediate results and fast recovery. FRAM-based processors [64, 31, 57, 11, 65, 13, 31, 53], present a great potential to be deployed in energy-harvesting devices. For example, Yu et al. [59] propose a non-volatile processor ar-

chitecture that integrates non-volatile elements into volatile memory at bit granularity. To reduce the backup overhead and energy, different technologies have been proposed including instruction scheduling [55], register reduction [62], and instruction selection [54].

Since harvested energy is limited for each power cycle, efficiently utilizing harvested energy is critical. Smart task scheduling techniques can save a significant amount of energy. [60] proposes a long-term deadline-aware scheduling algorithm to reduce energy consumption and deadline miss rates of tasks. [22] proposes a performance-aware task scheduling strategy for energy harvesting nonvolatile processors considering the power switching overhead. This paper will propose a lightweight scheduler that can maximize task progress and thus reduce energy consumption considering all types of tasks.

#### 3.3 System Overview

In this section, the targeting system architecture of self-powered IoT edge devices regarding software and hardware layers is given in Figure 5.

As shown in Figure 5, the architecture of the targeted energy harvesting system includes both hardware and software components from bottom to top. The power supply consists of energy harvesters, a regulator, and a capacitor, which supplies energy for the whole system. The energy harvester converts harvested energy from ambient sources, such as solar energy, thermal energy, and radio frequency (RF) to electrical energy. The converted energy is stored in a small-size storage capacitor, which is used to supply energy for checkpointing upon power outages. The regulator is used to maintain a constant voltage level. The other hardware components consist of MCU, timer, ADC, sensors, and I/O ports. The software layer has full control of the onboard hardware to collect data and make decisions.

The software layer includes the proposed progress maximization scheduler assisted with three auxiliary functional modules: voltage monitor, checkpoint handler, and routine handler. These four functional modules interact with each other to maximize the task execution progress and can be easily integrated into any existing energy harvesting embedded systems. Further, all tasks to be scheduled can be divided into atomic tasks and non-atomic tasks.

Figure 5: System Architecture

#### 3.4 Power Prediction

In this section, a voltage monitor designed to conduct voltage measurement and power analysis will be presented. From Figure 5, we know that detecting the voltage of the storage capacitor requires collaboration between hardware and software. On the hardware side, the output of the storage capacitor needs to connect to an analog to digital converter (ADC) channel of the MCU. On the software side, the ADC needs to periodically sample the storage capacitor's voltage. Here we define  $V_{cap}$  as the voltage on the storage capacitor.

Knowing the voltage of the storage capacitor  $V_{cap}$  is not enough to determine whether the harvesting power can support the NVP system and there are mainly two reasons:

- 1) First, for the storage capacitor, even if  $V_{cap}$  is low, the harvesting power supply can still be sufficient to support the NVP system if it is recovering;

- 2) Second, the power consumption of tasks varies. Therefore, even if the harvesting power can support the current task, it cannot guarantee to support other tasks which consume more power and energy.

These two concerns can be eased by calculating the discharging power of the capacitor. This is because the working status of the system is directly determined by the amount of energy on the capacitor. Also, given the same working power, the changes of the discharging power equal the changes in the harvesting power. So given current ongoing execution of Tsk[cur], the calculation of discharging power on the capacitor can estimate how long  $(T^S)$  the system can be in an execution before the outage happens.

Therefore, with current task Tsk[cur], task information table Tab, and ADC sample period  $T_{ADC}$ , DPA algorithm is able to calculate the discharging power of Tsk[cur]. With the discharging power, DPA can further estimate the duration of  $T^S$  for the system to work before the outage happens. The estimation also comes with the trustiness  $Trust^P$  evaluation.

DPA is called each time by the NVP scheduler to evaluate the discharging power on the capacitor before actually conducting task scheduling. At the beginning, DPA initiates parameters including  $\langle \Delta E_{cap} \rangle_N$ : an array to store N times of energy reductions on the capacitor,  $\langle \Delta E_{cap}^{est} \rangle_N$ : an array to store N times of estimated energy reduction on the capacitor,  $\langle \Delta P_{cap} \rangle_N$ : an array to store N times of discharging power reduction on the capacitor,  $\langle \Psi \rangle_N$ : N times of the correctness of the estimation, and  $P'_{cap}$ : the estimated reduction of the discharging power. The initialization process is shown in line 1 to 5.

After initialization, DPA calls ADC to sample N+1 voltage samples on the capacitor. After each sampling, DPA first calculates the reduction of the energy  $\Delta E_{cap}$  on the storage capacitor which is shown in line 8. Then, in line 9, DPA further calculates the reduction of the discharging power  $\Delta P_{cap}$ . To signal the status of the discharging power, DPA introduces two coefficients v and v (v > v and v + v = 1), If  $\Delta P_{cap} > 0$ , the discharging power is reduced and DPA assigns v to the weight factor K, otherwise,DPA assigns v to v. The rationale behind the weight assignment is to let the system be more aware of the most recent increase of the discharging power, which indicates that the harvesting power is reducing. The comparing process is shown in line 10 - 14.

After calculating  $\Delta P_{cap}$  from the real samples of  $V_{cap}$ , in line 15 to 21, DPA conducts the evaluation procedure. At first, in line 15, DPA estimates the reduction of the discharging power as  $P'_{cap}$ . The estimation uses the weight factor of K. If the real discharging power is reduced (harvesting power recovers), DPA gives more weight to estimation, otherwise, DPA

#### **Algorithm 3.4.1** Discharging Power Analysis (DPA)

```

Input: Tab, and T_{ADC}.

Output: T^{S} and Trust^{P}.

1: \langle \Delta E_{cap} \rangle_N \leftarrow actual reduction of the capacitor energy;

2: \langle \Delta E_{cap}^{est} \rangle_N \leftarrow estimated reduction of the capacitor energy

3: \langle \Delta P_{cap} \rangle_N \leftarrow actual reduction of the discharging power;

4: \langle \Psi \rangle_N \leftarrow correctness of the estimations;

5: P'_{cap} \leftarrow the estimated reduction of the discharging power;

6: for each ADC cycle i from 1 to N+1 do

if i > 1 then

\Delta E_{cap}(i-1) = C[V_{cap}^2(i-1) - V_{cap}^2(i)]/2;

8:

\Delta P_{cap}(i-1) = \Delta E_{cap}(i-1) - \Delta E_{cap}(i);

9:

10:

if \Delta P_{cap}(i) > 0 then

/* discharging power reduced */

K = \nu;

11:

12:

else

/* discharging power increased */

K = v;

13:

end if

14:

\begin{aligned} P'_{cap} &= (1-K)P'_{cap} + K\Delta P_{cap}(i); \\ \Delta E^{est}_{cap}(i-1) &= \Delta E_{cap}(i-2) + P'_{cap}; \end{aligned}

15:

16:

if \Delta E_{cap}^{est}(i-1) < \Delta E_{cap}(i) - 1 then

17:

/* underestimate */

18:

\Psi(i) = 0;

19:

else

\Psi(i) = 1;

/* overestimate */

20:

end if

21:

22:

end if

23: end for

23. End for 24: \ \frac{E_{cap}^{rem} = C[V_{cap}(N+1)^2 - V_{ck}^2]/2}{\Delta E_{cap}^{est} = \sum_{i=1}^{N} \Delta E_{cap}^{est}(i)/N}

26: T^S = T_{ADC} * \frac{E_{cap}^{rem}}{\Delta E_{cap}^{est}}

27: Trust^P = \sum_{i=2}^{N} \Psi(i)/(N-1);

28: return T^S and Trust^P; =0

```

gives more weight to the real discharging power. After the calculation of  $P'_{cap}$ , DPA further estimates the energy reduction  $\Delta E^{est}_{cap}$  on the capacitor, which is shown in line 16. After estimation, in line 17 to 21, DPA compares the estimation  $\Delta E^{est}_{cap}$  with the real energy reduction  $\Delta E_{cap}$ . If DPA underestimates the reduction of the discharging power, the estimation is invalid and DPA assigns  $\Psi = 0$  to indicate the invalidation. If DPA overestimates the reduction, it accepts the estimation and assigns  $\Psi = 1$  to indicate the acceptance. In this way, the estimation can be more aware of the loss of the harvesting power.

After evaluation, DPA calculates the remaining energy  $E_{cap}^{rem}$  in line 24 and the average estimated energy reduction  $\overline{\Delta E_{cap}^{est}}$  in line 25. Then, based on  $E_{cap}^{rem}$  and  $\overline{\Delta E_{cap}^{est}}$ , in line 26, DPA estimates the duration  $T^S$  for system to work before the power outage happens. Accompanied by the estimation of  $T^S$ , DPA also calculates the trustiness  $Trust^P$  of the estimation in line 27. After the calculation, DPA returns  $T^S$  and  $Trust^P$  for NVP scheduler to use as references to conduct task scheduling for progress maximization.

#### 3.5 Independent NVP Task Scheduler

In this section, we will present a lightweight scheduler, which is specifically designed for NVPs. The goal is to maximize system progress under unstable power supply.

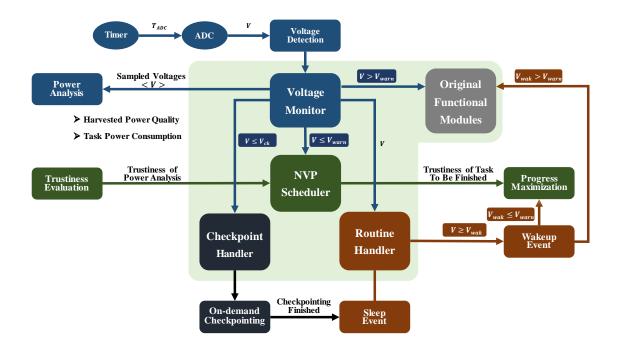

Figure 6 shows the overview. The core component is the NVP scheduler and it is assisted with three functional modules: voltage monitor, checkpoint handler, and routine handler. The NVP scheduler can run on its own or be incorporated into an existing embedded OS. If working with the existing OS, the modules in existing OS remain intact and will be invoked when  $V < V_{warn}$ , where  $V_{warn}$  is the preset voltage threshold. The voltage monitor is active all the time and responsible for voltage detection and analysis of power consumption of the NVP system. Once voltage V drops below  $V_{warn}$ , the NVP scheduler is triggered to maximize task progress. If V continues to drop until it is below threshold  $V_{ck}$ , the checkpoint handler is triggered to ensure a successful checkpointing. After checkpointing, the routine handler will put the system into sleep mode until the power recovers. By then, the routine handler will wake up the entire system. These functional modules interact with each other.

Figure 6: NVP Scheduler Overview

After the voltage monitor detects that the voltage on the storage capacitor drops below  $V_{warn}$ , in anxious of a potential power outage, the NVP Scheduler is triggered to maximize progress with the remaining energy supply. The key idea of the scheduler is to differentiate different tasks and all tasks can be categorized into two groups:

- Atomic tasks: tasks that even can be checkpointed before power outage still have to start

over when the power comes back on again. Typical examples include communication,

sensing, etc.

- Non-atomic tasks: tasks that can be checkpointed and resumed correctly during a power outage without any problem. Typical examples include computation, data fusion, etc.

Several important pieces of information regarding each task also need to be maintained. Of the most important are the task execution power, current progress, progress to time ratio, and atomicity, as shown in Table 1.

For each task, the execution power is measured at offline stage. The execution progress and the progress to time ratio are maintained by the OS and are updated when the task is switched out by the scheduler. When voltage on the storage capacitor drops below  $V_{warn}$ ,

Table 1: Task Information (Tab)

| Tasks  | Execution Power | Current Progress | Progress to Time Ratio | Atomicity  |

|--------|-----------------|------------------|------------------------|------------|

| Tsk[i] | $P_i$           | $Pg_i$           | $Pg_i'$                | Non-atomic |

| Tsk[j] | $P_{j}$         | $Pg_j$           | $Pg_j'$                | Atomic     |

in anxious of a potential power outage, NVP scheduler is triggered to prioritize the atomic tasks. Given the task ready queue Q and the task information table Tab as the inputs, Algorithm 3.5.1 shows details of NVP scheduler.

```

Algorithm 3.5.1 NVP Scheduler

```

```

Input: Q and Tab

Output: schedule tasks for maximum task progress

1: while (V_{ck} < V_{cap} < V_{warn}) do

T^S, Trust^P \Leftarrow DPA(Tab, T_{ADC}); /*Algorithm 3.4.1*/

Trust^{max} = 0;

3:

for each atomic Tsk[i] in ready queue Q do

4:

Trust_i \Leftarrow TCE(T^{\tilde{S}}, Trust^P, Tsk[Cur], Tsk[i], Tab);

/* Algorithm 3.5.2 */

5:

if Trust_i > Trust^{max}; then

6:

Trust^{max} = Trust_i;

7:

Sel = Tsk[i];

8:

9:

end if

end for

10:

if Trust^{max} > Trust^{TH} then

11:

execute Sel

12:

13:

else

14:

break;

15:

end if

16: end while

17: while (V_{ck} < V_{cap} < V_{warn}) do

round-robin scheduling for non-atomic tasks \in Q;

19: end while =0

```

The purpose of NVP Scheduler is to achieve overall task progress maximization by giving more scheduling priority to atomic tasks in the ready queue Q when a potential power outage may happen. The inputs include ready task queue Q and task information table Tab. NVP Scheduler proceeds with a voltage range of  $[V_{ck}, V_{warn}]$ . Once  $V_{cap} < V_{warn}$ , in anxious of a possible power outage, NVP Scheduler starts scheduling. When  $V_{cap} \leq V_{ck}$ , the NVP Scheduler stops and initiates checkpointing procedure.

At first, the NVP scheduler needs to prioritize the scheduling for atomic tasks, which is shown in line 1 to 16. Before conducting scheduling, preparation needs to be made. In line 2, NVP scheduler calls the Discharging Power Analysis (DPA) algorithm to assess the harvesting power and output the estimated execution time  $T^S$  that the system can support to the current ongoing task Tsk[cur], along with which DPA also provides the trustiness value  $Trust^P$  of the estimation. DPA is detailed in Algorithm 3.4.1. After calling DPA, in line 3, NVP scheduler initiates the parameter  $Trust^{max}$  which will be further used to select the best atomic task candidate for scheduling.

After preparation stage, in line 4 to 10, NVP scheduler evaluates the possibility of each task Tsk[i] to finish before the power outage. Given the parameter of  $T^S$  and  $Trust^P$  from DPA, the current task Tsk[cur], targeting task Tsk[i], and the task information table Tab, the Task Completion Evaluation (TCE) algorithm is called by NVP scheduler to evaluate the possibility that Tsk[i] is able to finish before the power outage. This possibility for Tsk[i] is defined as  $Trust_i$ . Details of TCE is given in Algorithm 3.5.2. During the calculation of  $Trust_i$  for each atomic task, NVP scheduler is able to find the best Tsk[i] with the maximum  $Trust_i$ , which will be selected by NVP scheduler for further evaluation. The best Tsk[i] and its  $Trust_i$  are assigned to Sel and  $Trust^{max}$  respectively.

With Sel and  $Trust^{max}$ , in line 11 to 15, NVP scheduler compare  $Trust^{max}$  with  $Trust^{TH}$  which is a threshold to decide whether it is worthwhile to execute Sel. If  $Trust^{max} > Trust^{TH}$ , NVP scheduler believes that Sel can finish before the power outage and proceeds the scheduling for Sel. Otherwise, the NVP scheduler will break out the while loop to schedule for atomic tasks. This is because, if the best atomic candidate Sel is not worthwhile for scheduling, no other atomic tasks will be.

Finally, once there is no suitable atomic candidate for scheduling, NVP will conduct round-robin scheduling for non-atomic tasks in the task ready queue Q until  $V_{cap}$  drops below  $V_{ck}$ , when the checkpointing starts. This is shown in line 17 to 19

During the scheduling, NVP scheduler needs to call its sub-algorithm TCE to conduct task completion evaluation for each atomic task. The evaluation is to find out the trustiness  $Trust_i$  of Tsk[i] to be able to finish before the power outage. Given a targeting task Tsk[i], the current task Tsk[cur], task information table Tab, and the calculated values of  $T^S$  and  $Trust^P$  from DPA, Algorithm 3.5.2 shows the details of the the evaluation.

#### **Algorithm 3.5.2** Task Completion Evaluation (TCE)

```

Input: Tsk[i], Tsk[cur], Tab, T^S, and Trust^P

Output: Trust_i: the trustiness of Tsk[i] to be able to complete;

1: P_{cur}, P_i \leftarrow powers of Tsk[cur] and Tsk[i] from Tab;

2: Pg_i \leftarrow progress of Tsk[i] from Tab;

3: Pg'_i \leftarrow progress to time ration of Tsk[i] from Tab;

4: t_i = (1 - Pg_i)/Pg'_i;

5: T_i^S = Trust^P * T^S * P_{cur}/P_i;

6: Trust_i = T_i^S/t_i;

7: if Trust_i > 1 then

8: Trust_i = 1;

9: end if

10: return Trust_i = 0

```

At the beginning, TCE acquires several pieces of necessary information from Tab. For current task Tsk[cur], TCE needs the execution power  $P_{cur}$ . For the targeting task Tsk[i], TCE needs to access the execution power  $P_i$ , the execution progress  $Pg_i$ , and the progress to time ratio  $Pg'_i$ . The entire information fetching process is given in line 1 - 3.

With these pieces of information, TCE calculates how long that Tsk[i] still needs before completion and how long the system can offer Tsk[i] for execution. Here  $t_i$  is defined as the time required for Tsk[i] to finish which is calculated in line 4 using parameters  $Pg_i$  and  $Pg'_i$ .  $T_i^S$  is defined as the time that the system is able to provide for Tsk[i] before the power outage.  $T_i^S$  is calculated in line 5. Also because  $T_S$  is an estimated value, we need to consider about its trustiness  $Trust^P$ .

Finally, Given  $t_i$  and  $T_i^S$ , TCE is able to calculate  $Trust_i$  in line 6. Then, TCE trims the value of  $Trust_i$  to be between 0 and 1 and delivers  $Trust_i$  to the NVP scheduler to make a final decision.

For auxiliary modules, the NVP scheduler also has a checkpointing handler and a routine handler. For the checkpointing handler, instead of checkpointing run-time data periodically, it is only triggered once the voltage on the storage capacitor  $V_{cap}$  drops below  $V_{ck}$ . After

checkpointing, the routine handler will take over the system for sleep. In the sleep mode, ADC and timer are still allowed to monitor the voltage with negligible energy consumption. If  $V_{cap} < V_{wak}$ , the edge device needs to go back to sleep mode. Otherwise, the edge device can wake up. This can save energy by avoiding the system from stagnating at the cold starting stage.

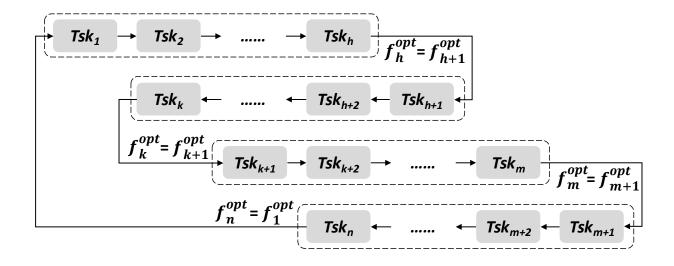

# 3.6 Dependent NVP Task Scheduler

In this section, an NVP-aware task scheduler (NTS) considering data dependence is proposed to maximize the execution progress and reduce the energy consumption on check-pointing. The main goals of NTS are bifold. First, to maximize the chance for tasks to meet their deadlines, the earliest deadline first (EDF) based list scheduling is used to schedule NVP tasks. Then, NTS differentiates tasks' atomicity based on their IO characteristics and schedules a task whose execution state can be stored and recovered successfully before the power outage. In this way, the harvested energy can be fully used for execution and the progress of the unfinished task can be maintained successfully without wasting energy to start over the execution.

Besides, NTS also considers the fact that tasks on the self-powered IoT edge device are usually iterative. For instance, the temperature sensing task on a self-powered IoT edge sensor node will keep collecting data periodically after the node has been deployed. This is true as the use of an energy harvesting system as the power source is mainly for devices to have long-term autonomous operations. Therefore, the type of tasks on these devices and their goals tends to be unchanged.

Aside from considering atomicity and task iteration, NTS also considers the data dependency, all father tasks should also be scheduled before their children. All tasks and the dependencies among these tasks are represented with Directed Acyclic Graph (DAG) where a parent task always requires data from its child tasks. Each task also has its own time constraint and energy consumption. Having all these concerns addressed, with the task set  $\{tsk\}$  which contains the data dependency and energy requirements of each task. The task

ready queue Q, wake-up voltage  $v_{wak}$ , and current delay set  $\{d\}$  as inputs, algorithm 3.6.1 provides details for task grouping and scheduling (NTS).

Given a DAG, scheduled task list sch, wake-up voltage  $v_{wak}$ , time constraint set  $\langle t \rangle$ , and energy consumption set  $\langle e \rangle$  of each task's energy requirement as inputs, Algorithm 3.6.1 provides the details of the NVP-aware Task Scheduling (NTS) algorithm. NTS is executed when the edge device is temporarily awake to monitor the capacitor voltage. The purpose of the NTS algorithm is to schedule tasks for the next execution cycle such that the size of checkpointing data can be as small as possible. Initially, NTS searches for all subtrees in DAG and removes the scheduled tasks in sch from subtrees which are then stored into task tree set  $\langle tree \rangle$  as shown in line 1. Then, in line 2, NTS calculates the amount of energy E that can be stored in a capacitor-based on the wake-up voltage  $v_{wak}$ . E will first be used to finish the previous checkpointed task  $tsk_p$ , if any. This is shown in line 4. Next, NTS initiates parameter  $\Psi$  which is used to indicate whether the scheduling is finished. After that, the deadline of each tree is calculated by adding its time constraint and the current time, which is shown in line 7 to 9. In line 10, NTS sorts all trees in ascending order of their deadlines. With the sorted tree sequence, in line 11, NTS starts picking up tasks for scheduling from the tree with the most imminent deadline.

For tasks on the selected tree, NTS keeps scheduling tasks as long as the stored energy E is beyond the required energy of all scheduled tasks. Because of data dependencies, leaf tasks need to be scheduled first. When a leaf task  $tsk_i^j$  on  $tree_i$  has been chosen, NTS adds  $tsk_i^j$  into both  $tsk_{nx}$  and sch. After that, NTS removes  $tsk_i^j$  from the current task tree and subtracts the required energy  $e_i^j$  from E so that the following scheduling has updated information. These steps are shown in line 13 to 16. Once the energy in the capacitor is not enough to support a new task, in line 18 to 27, NTS adds an existing non-atomic leaf task, if any, to the end of the scheduling list and marks  $\Psi = 1$  to indicate the completion of scheduling process.

Before breaking out the scheduling process, NTS checks whether all tasks in  $tree_i$  have been scheduled. If so, NTS will release them from sch. In this way, these tasks can continue their next iteration in the coming execution cycle. In the end, NTS returns the schedule list  $tsk_{nx}$ . These steps are shown in line 30 to 37.

# Algorithm 3.6.1 NVP-aware Task Scheduling (NTS)

```

Input: DAG, sch, v_{wak}, \langle t \rangle, and \langle e \rangle

Output: The task schedule list for the next execution cycle, tsk_{nx}

1: Build up unscheduled task tree set \langle tree \rangle based on DAG and sch;

2: Calculate energy storage E based on v_{wak};

3: if previous task tsk_p has been checkpointed then

E = E - e_p;

5: end if

6: \Psi = 0

/* indicator of completing scheduling */

7: for each tree_i do

/* deadline of tree_i */

d_i = t^{cur} + t_i;

9: end for

10: Sort trees in ascending order of d_i;

11: for each tree_i do

for each leaf task tsk_i^j in tree_i do

12:

if E > e_i^j then

13:

Add tsk_i^j to tsk_{nx} and sch;

14:

Remove tsk_i^j from tree_i;

15:

Update E = E - e_i^j;

16:

17:

for each leaf task tsk_i^k in tree_i do

18:

if tsk_i^k is a non-atomic task then

19:

Add tsk_i^k to tsk_{nx} and sch;

20:

Remove tsk_i^k from tree_i;

21:

Update E = E - e_i^k;

22:

23:

Break;

24:

end if

end for

25:

\Psi=1;

26:

Break;

27:

end if

28:

29:

end for

if tree_i is empty then

30:

Release all tasks of tree_i from sch;

31:

32:

end if

if \Psi = 1 then

33:

34:

Break;

end if

35:

36: end for

37: return tsk_{nx}; =0

```

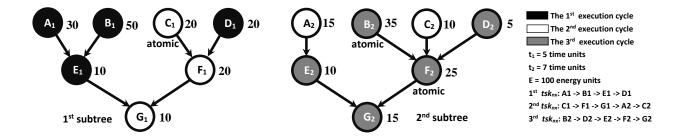

Figure 7: Example DAG

The example DAG in Fig. 7 will be used for better understanding of how NTS works. As we can see, this DAG has two subtrees. The first tree is on the left with the time constraint of 5 time units. The second tree is on the right with the time constraint of 7 time units. Both trees have seven nodes representing tasks. The atomic tasks are labeled at the bottom of each node and the unlabeled tasks are non-atomic. Each task's energy consumption is given on the right of each node. The energy in the capacitor is 100 energy units.

For the first execution cycle, NTS selects the  $1^{st}$  tree for scheduling because of its earlier deadline. Then, NTS starts to schedule leaf task  $A_1$  and  $B_1$ , which leaves  $E_1$ ,  $C_1$ , and  $D_1$  as the leaf tasks. After that, NTS selects  $E_1$  for scheduling. The energy left in the capacitor after the execution of  $E_1$  becomes 100-90=10. When NTS selects  $C_1$  for scheduling, it finds out that energy consumption of  $C_1$  is more than the energy available in the capacitor. At this point, NTS starts searching for unscheduled non-atomic leaf tasks, if any, in the  $1^{st}$  tree and selects  $D_1$  for scheduling. The scheduled tasks in the first execution cycle are in black.

For the second execution cycle,  $D_1$  needs to be resumed at the beginning. NTS assumes that  $D_1$  has to be started over which will consume all its required energy. Therefore, the energy left for the rest of the tasks is 100-20=80. Then, NTS schedules  $C_1$ ,  $F_1$ , and  $G_1$ , which completes the scheduling of the 1<sup>st</sup> tree and leaves 80-50=30 energy units for scheduling tasks on the 2<sup>nd</sup> tree. For this subtree, NTS first schedules  $A_2$ , which leaves 15 energy units in the capacitor. When NTS selects  $B_2$  for scheduling, it finds out that the energy consumption of

$B_2$  is more than the energy available in the capacitor. At this point, NTS starts searching for unscheduled non-atomic leaf tasks in the  $2^{nd}$  tree and selects  $C_2$  for scheduling. The scheduled tasks in the second execution cycle are in white.

For the third execution cycle,  $C_2$  needs to be resumed at the beginning, which leaves 100-10=90 energy units for the rest of the unscheduled tasks. Since the total amount of required energy of the remaining unscheduled tasks on the  $2^{nd}$  tree is also 90 energy units, all tasks on the  $2^{nd}$  tree can be scheduled. The scheduled tasks in the third execution cycle are in grey.

NTS has the time complexity of O(n) where n is the number of tasks. Due to the limited number of runtime programs on an edge device, the energy consumption of NTS is trivial compared with that of task execution. Experiments will show the performance and overhead of the NTS algorithm.

# 3.7 Experiments

In this section, the experiments are conducted to evaluate the performance of both the NVP scheduler and the NTS scheduler.

#### 3.7.1 Evaluation of NVP Scheduler

3.7.1.1 Hardware Platform The experiment platform of the NVP embedded system is TI's MSP430FR5739 ultra-low-power evaluation board, which consists of a 16-bit MCU, a 10-bit ADC module, a 1kB volatile SRAM, a 16KB nonvolatile FRAM memory, and different peripherals for sensing and wireless sensing applications. The Bq25570 ultra-low-power regulator is used to supply a stable voltage, which can work with a minimum of the 120mV input voltage and a maximum of 4.2V boost voltage. The only hardware overhead of our design is that there should be an extra wire to connect between the storage capacitor and the ADC channel so that the voltage on the capacitor can be constantly monitored.

**3.7.1.2** Power Traces To evaluate the performance of the NVP scheduler, five different power traces are generated as shown in Figure 8.

|      | Trace 1   | Trace 2 | Trace 3 | Trace 4 |  |

|------|-----------|---------|---------|---------|--|

| High | 9.1 s 3 s |         | 1 s     | always  |  |

| Low  | 0.9 s     | 2 s     | 4 s     | 0 s     |  |

Figure 8: Power Trace Used for Experiments

The source power is provided by the MSP430FR5969 evaluation board which is programmed to generate different power traces through a GPIO pin which can provide a 3.6V output once the pin is set to be high, otherwise the output is 0. Then, power will be harnessed by the power regulator Bq25570 to power the MSP430FR5739. Power source 1 is for the output pin to set low for 0.9 seconds in every 10 seconds period; Power source 2 is for the output pin to set low for 2 seconds in every 5 seconds period; Power source 3 is for the output pin to set low for 4 seconds in every 5 seconds period; Power source 4 is for the output pin to set low for 1 second in every 1.3 seconds period; Power source 5 is for the output pin to set high all the time.

3.7.1.3 Software Setup Experimental software includes a lightweight NVP scheduler and the proposed three functional modules of Voltage Monitor, Checkpoint Handler, and Routine Handler. The original scheduler of the system is a round-robin scheduler. For the NVP scheduler, the Voltage Monitor keeps monitoring the voltage of the capacitor. Specifically, for every  $T_{ADC}$  period, the timer will wake up the ADC module for a short period during which  $V_{cap}$  will be sampled and analyzed, and the progress to time ratio of the executing task will be updated. If  $V_{cap} > V_{warn}$ , the original round-robin scheduler is in charge. Otherwise, the NVP scheduler will take over task scheduling for progress maximization. Before presenting experimental results, parameters are listed in Table 2.

Table 2: Task Information

| С          | $T_{ADC}$ | $V_{warn}$ | $V_{ck}$ | $V_{safe}$ | ν   | v   | $\varphi$ | $\psi$ |

|------------|-----------|------------|----------|------------|-----|-----|-----------|--------|

| $470\mu F$ | 37.5ms    | 2.5V       | 1.2V     | 0.5V       | 0.2 | 0.8 | 0.9       | 0.1    |

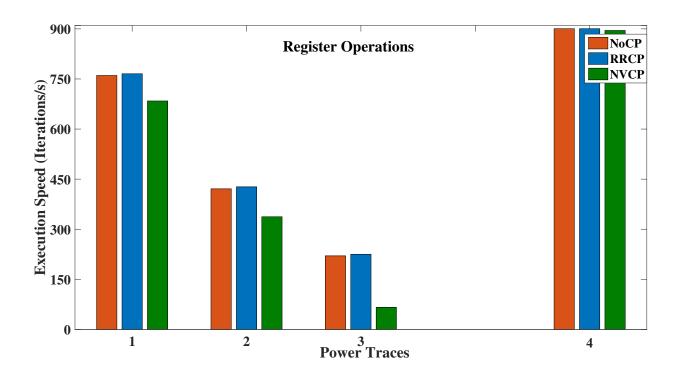

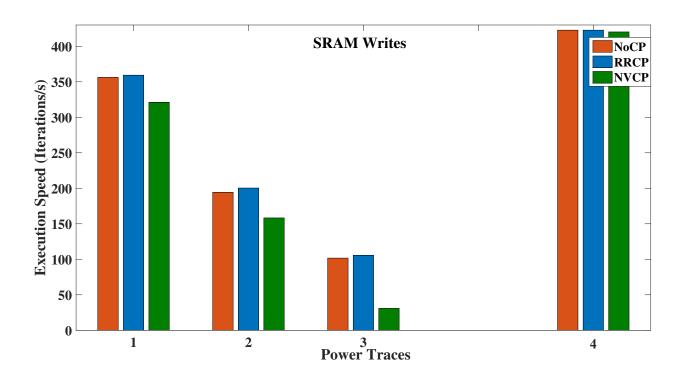

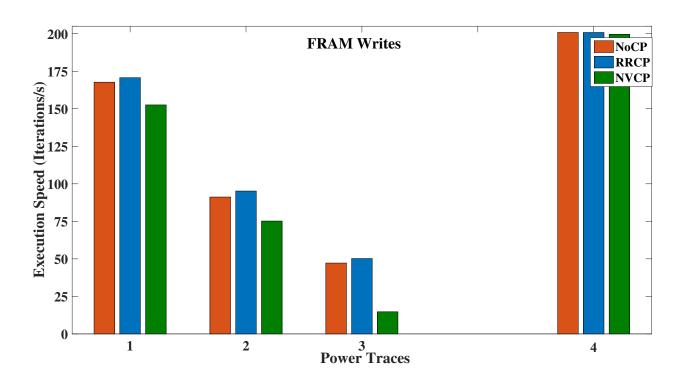

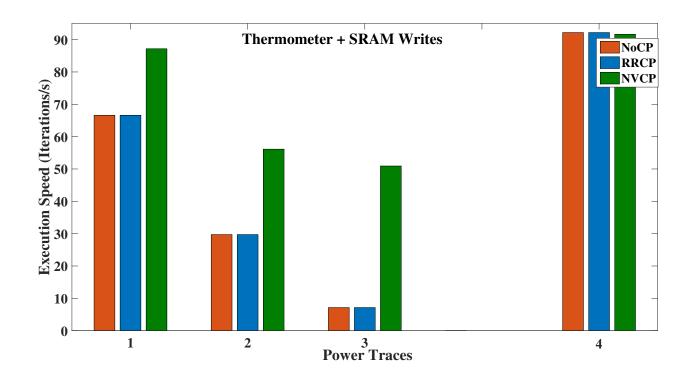

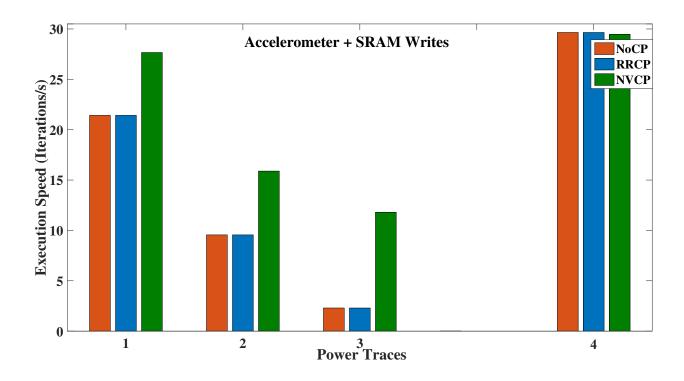

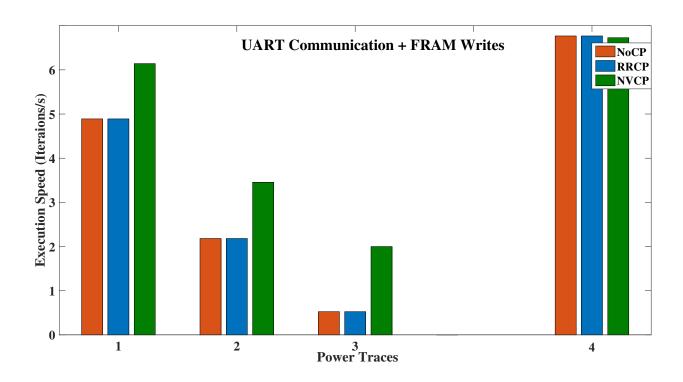

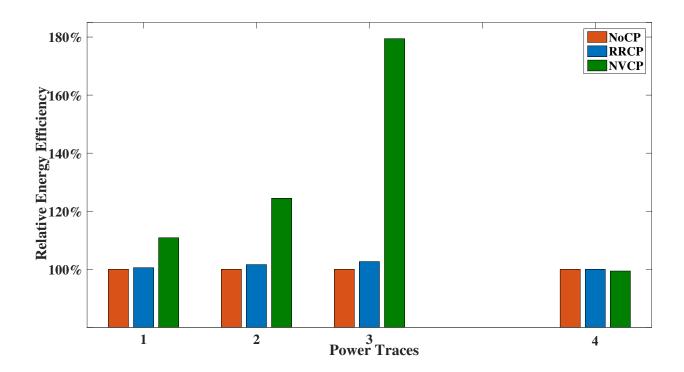

The benchmarks include three atomic tasks of acceleration measurement (the results are written in SRAM), temperature sensing (the results are written in SRAM), and UART communication (the data are written in FRAM). There are also three non-atomic tasks including register operations, SRAM writes, and FRAM writes. These six benchmarks are iterative and independent of each other.

With power traces, the experiments start with the power measurements of these six benchmarks. The baselines of this experiment are NoCP and RRCP. NoCP represents a round-robin scheduler without a checkpoint handler. The RRCP represents the round-robin scheduler with checkpointing ability. The proposed NVP scheduler which is incorporated into the baseline RRCP is defined as NVCP. For NVCP, the voltage monitor is always active to sample the voltage V on the capacitor. Once  $V < V_{warn}$ , NVP scheduler is activated and takes over the task scheduling, otherwise, it remains inactive.

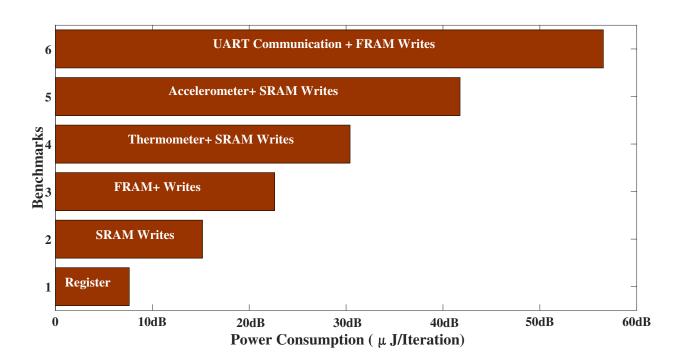

3.7.1.4 Energy Consumption Analysis The power consumption of the six benchmarks is measured with a stable power supply. Figure 9 shows the measurements. All benchmarks are iterative and the duration of each iteration is trivial. For instance, the benchmark 6 has the largest iteration period of 24ms and benchmark 1 has the lowest period of 0.18ms. During these periods, the changes in voltage on the capacitor are negligible. So it is reasonable to use  $\mu J/Iteration$  representing the power consumption of each task.

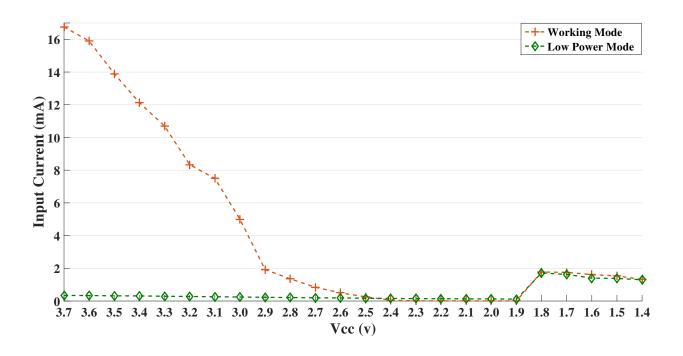

**3.7.1.5** Sleep Mode vs. Working Mode The first experiment is to show the power consumption of NVP system in sleep mode. In Figure 10, we adjust the Vcc from 3.7 to 1.4 gradually and measure the input current.

Figure 9: Power Consumption of Benchmarks

Figure 10: Power Consumption of Low Power Mode vs Working Mode