### New Architectures and Nonlinear Control Strategy of Dual Active Bridge Converter

by

### Zachary T. Smith

Bachelor of Science in Electrical Engineering, University of Pittsburgh, 2014 Master of Science in Electrical Engineering, University of Pittsburgh, 2021

## Submitted to the Graduate Faculty of

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2022

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

#### Zachary T. Smith

It was defended on

July 14, 2022

and approved by

Brandon Grainger, PhD., Assistant Professor, Department of Electrical and Computer Engineering

Alexis Kwasinski, PhD., Associate Professor, Department of Electrical and Computer Engineering

Robert Kerestes, PhD., Assistant Professor, Department of Electrical and Computer Engineering

Paul Ohodnicki, PhD., Assistant Professor, Department of Electrical and Computer Engineering

Michael McIntyre, PhD., Associate Professor, Department of Electrical and Computer Engineering, University of Louisville

Richard Beddingfield, PhD., Postdoctoral Research Scholar, Department of Electrical and Computer Engineering, North Carolina State University

Dissertation Director: Brandon M. Grainger, PhD., Assistant Professor, Department of Electrical and Computer Engineering Copyright © by Zachary T. Smith

2022

#### New Architectures and Nonlinear Control Strategy of Dual Active Bridge Converter

Zachary T. Smith, Ph.D.

University of Pittsburgh, 2022

This dissertation contains 3 distinct research projects that focus on architectures and control strategies for dual active bridge converters and triple active bridge converters. Objective #1 presents design considerations, performance analysis, and control strategy for a current-fed, triple active bridge converter. This project was verified using a digital signal processor to implement a new control method within both 1) a real time digital simulator, and 2) a triple active bridge prototype. Objective #2 evaluates operational performance improvements to a dual active bridge converter through the use of observers and parameter estimators. The observer tracks the converter current without the need for a current sensor. The quick nature of the presented current observer (less than 1ms) allows the converter controller to compensate quickly to a dc bias current, which should reduce stress on the transformer and extend the lifetime of converter components. The proposed parameter estimator is shown to be suited for use with tunable inductors, allowing the controller to maintain design requirements even with dynamically changing magnetics. Objective #3 presents a finite element analysis of a 3-winding, concentric wound, 50kW, 10kHz ferrite ribbon transformer. This study models the performance of the transformer within a triple active bridge experimental test bed. When possible, these projects have been submitted and/or published within IEEE conferences and journals to further the field of study of dual active bridge converters for use in multiport and medium voltage applications.

# **Table of Contents**

| Nomenclature xiv                                                                  |

|-----------------------------------------------------------------------------------|

| 1.0 Background 1                                                                  |

| 2.0 Research Plan: Objective #1 - Design Considerations, Decoupled Control, and   |

| Grid Implementation of a CFTAB Converter5                                         |

| 2.1 Literature Review                                                             |

| 2.2 Description of Converter7                                                     |

| 2.2.1 Converter Topology7                                                         |

| 2.2.2 Converter Operation9                                                        |

| 2.3 Power Flow Analysis10                                                         |

| 2.3.1 Decoupling Mutual Inductor Characteristic Equations                         |

| 2.3.2 State Space Matrix14                                                        |

| 2.3.3 Computation of Steady-State Current Waveforms                               |

| 2.3.4 Computation of Average Power Flow18                                         |

| 2.3.5 Average Power Flow Equations Across All Modes                               |

| 2.4 Design Considerations for Mutual Inductors and Transformer Leakage Inductance |

|                                                                                   |

| 2.4.1 Discussions                                                                 |

| 2.5 Decoupled Control                                                             |

| 2.5.1 Average Power Flow Control Case Study                                       |

| 2.5.2 Control Hardware-in-the-Loop Experiment                                     |

| 2.5.2.1 Typhoon HIL Schematic and SCADA Panel                                     |

| 2.5.2.2 Texas Instruments Controller                                                                             | 38                                           |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.5.2.3 Performance of Real Time Digital Simulation                                                              | 41                                           |

| 2.6 Experimental Prototype                                                                                       | 42                                           |

| 2.6.1 Control Card Setup                                                                                         | 42                                           |

| 2.6.2 Test Bed Parameters                                                                                        | 45                                           |

| 2.6.3 Experimental Setup                                                                                         | 47                                           |

| 2.6.4 Experimental Results                                                                                       | 50                                           |

| 2.7 Ring Bus implementation of Back-to-Back 3-Port Converters                                                    | 55                                           |

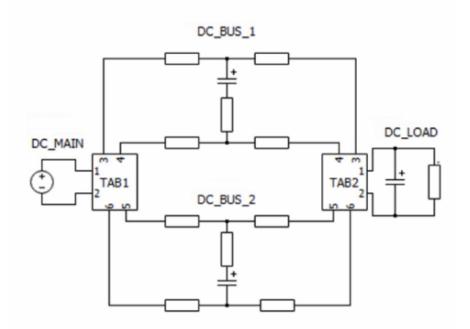

| 2.7.1 Validation of Network Control Using PLECS                                                                  | 56                                           |

| 2.7.2 PLECS Simulation of Back-to-Back Converters                                                                | 58                                           |

| 2.8 Conclusions and Discussions                                                                                  | 60                                           |

|                                                                                                                  |                                              |

| 3.0 Research Plan: Objective #2 - Nonlinear Observer and Parameter Estimator for                                 |                                              |

| 3.0 Research Plan: Objective #2 - Nonlinear Observer and Parameter Estimator for<br>Dual Active Bridge Converter | 62                                           |

|                                                                                                                  |                                              |

| Dual Active Bridge Converter                                                                                     | 62                                           |

| Dual Active Bridge Converter         3.1 Literature Review                                                       | 62<br>62                                     |

| Dual Active Bridge Converter         3.1 Literature Review         3.1.1 Current Observer                        | 62<br>62<br>64                               |

| Dual Active Bridge Converter                                                                                     | 62<br>62<br>64<br>66                         |

| Dual Active Bridge Converter                                                                                     | 62<br>62<br>64<br>66<br>67                   |

| Dual Active Bridge Converter                                                                                     | 62<br>62<br>64<br>66<br>67<br>68             |

| Dual Active Bridge Converter                                                                                     | 62<br>62<br>64<br>66<br>67<br>68<br>69       |

| Dual Active Bridge Converter                                                                                     | 62<br>62<br>64<br>66<br>67<br>68<br>69<br>71 |

| 3.4 Parameter Estimator for Inductance within a Dual Active Bridge Converter 75    |

|------------------------------------------------------------------------------------|

| 3.4.1 Background76                                                                 |

| 3.4.2 Dual Active Bridge Model77                                                   |

| 3.4.3 Dual Active Bridge Controller Structure78                                    |

| 3.4.4 Parameter Estimator 80                                                       |

| 3.4.5 PLECS Simulation of Control Strategy                                         |

| 3.4.6 Control Hardware-in-the-Loop Experiment                                      |

| 3.5 Conclusions and Discussions                                                    |

| 4.0 Research Plan: Objective #3 – Finite Element Analysis of 3-Winding Transformer |

| within a Triple Active Bridge Converter                                            |

| 4.1 Literature Review                                                              |

| 4.2 TAB Circuit Topology                                                           |

| 4.2.1 Circuit Control                                                              |

| 4.3 Finite Element Model                                                           |

| 4.4 Finite Element Analysis Results97                                              |

| 4.5 Conclusions 101                                                                |

| Bibliography 103                                                                   |

# List of Tables

| Table 1: CFTAB Converter Circuit Parameters                                 | 16  |

|-----------------------------------------------------------------------------|-----|

| Table 2: CFTAB Converter Circuit Parameters for Leakage Inductance Analysis |     |

| Table 3: Parameters for 3 Port Converter Prototype                          | 46  |

| Table 4: Operating Parameters for 3 Port DAB Converter Experiment           |     |

| Table 5: System Parameters and Design Requirements                          | 85  |

| Table 6: Finite Element Analysis Scenarios                                  |     |

| Table 7: Finite Element Analysis Scenarios and Self-Inductance              | 102 |

# List of Figures

| Figure 1: Monodirectional AC Grid (left) and Bidirectional DC Grid (right)                                  |

|-------------------------------------------------------------------------------------------------------------|

| Figure 2: Example dc distribution ring bus network using bidirectional multi-port converters 3              |

| Figure 3: Current-fed triple active bridge topology for the example application of a LV-MV-MV               |

| converter                                                                                                   |

| Figure 4: Switching voltage waveforms for each port: $v1$ (black), $varm2$ (blue), and $varm3$              |

| (red)10                                                                                                     |

| Figure 5: State Space A matrix using the parameters in Table I                                              |

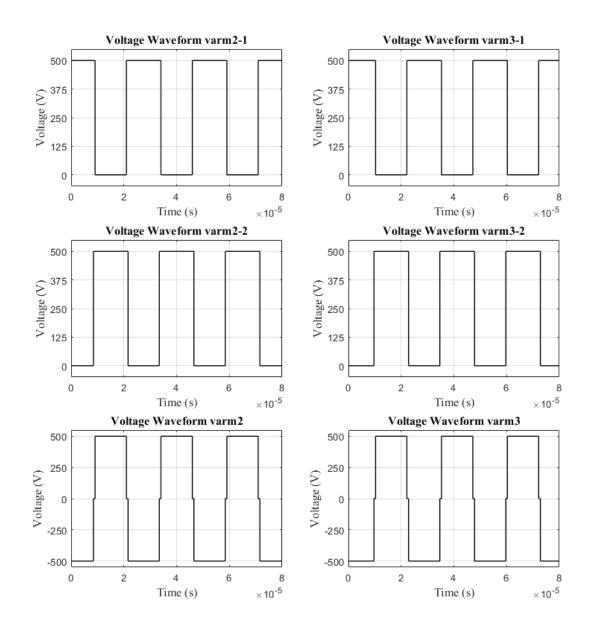

| Figure 6. Individual arm voltages for each current-fed port and each port's voltage difference              |

| waveform                                                                                                    |

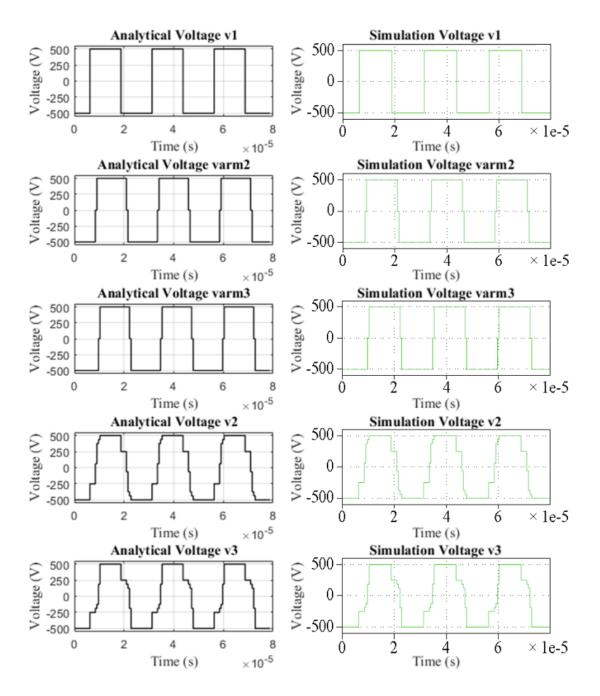

| Figure 7. Analytical vs simulation waveforms for port voltages and switching waveforms 27                   |

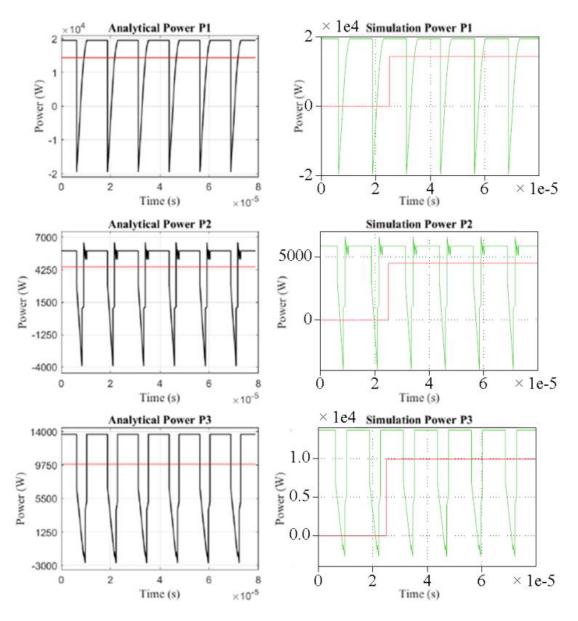

| Figure 8. Analytical vs PLECS simulation waveforms for power flow at each port                              |

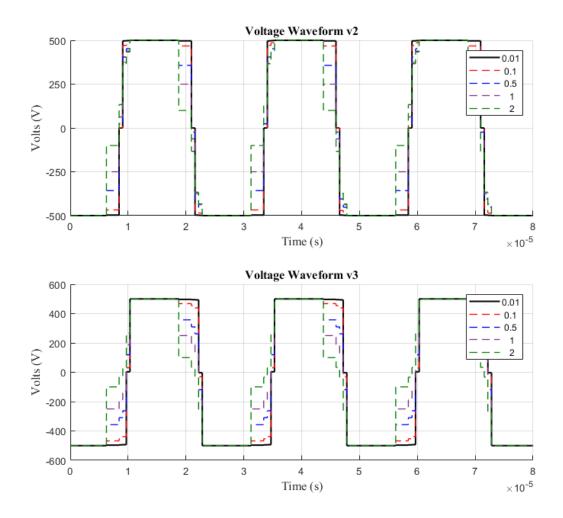

| Figure 9: Current-fed port voltage waveforms $v2$ and $v3$ with inductance ratios $Ldc - M/Lx$              |

| between 1% and 200% (from simulation)                                                                       |

| Figure 10: Power transfer at current-fed ports with respect to the inductance ratios $Ldc - M/Lx$           |

| (from simulation)                                                                                           |

| Figure 11: Power output at port 2 across the entire operating range $(-0.5 \le \phi^2 \le 0.5 \text{ and})$ |

| $-0.5 \le \phi_3 \le 0.5$ ) (top) and Power output at port 3 across the entire operating range (bottom).    |

|                                                                                                             |

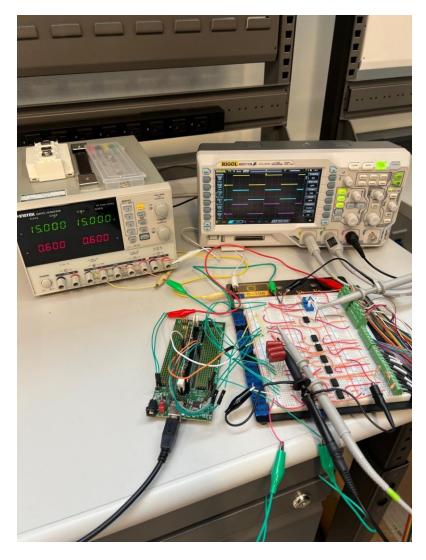

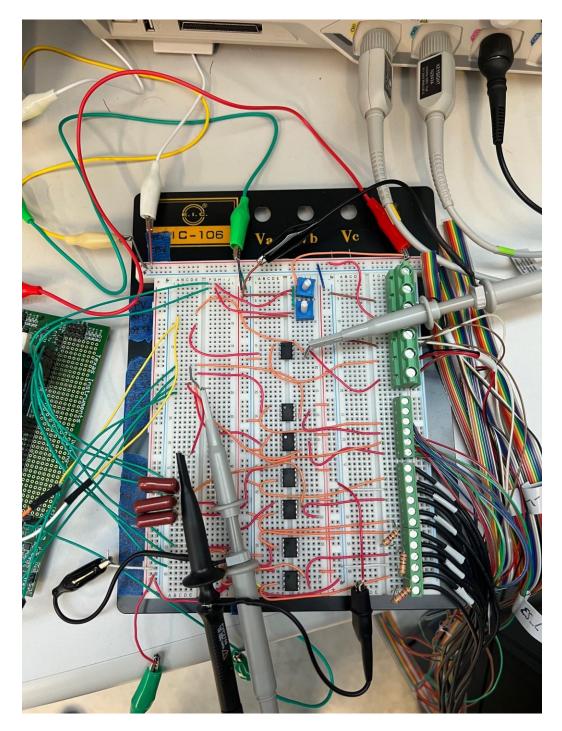

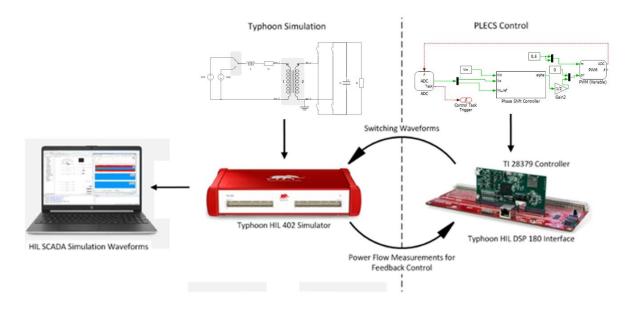

| Figure 12: Typhoon HIL Control Hardware-in-the-Loop Experimental Setup                                      |

| Figure 13: Typhoon HIL model of a 3-bus network (LV-MV-MV) with 3-port interfacing                          |

| converter                                                                                                   |

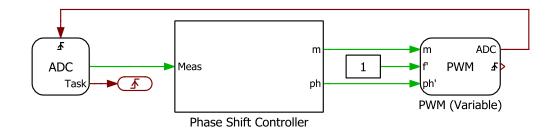

| Figure 14: PLECS phase-shift controller using TI C2000 target blocks                              |

|---------------------------------------------------------------------------------------------------|

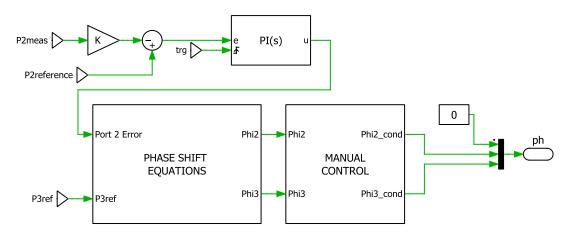

| Figure 15: Control logic for phase-shift control                                                  |

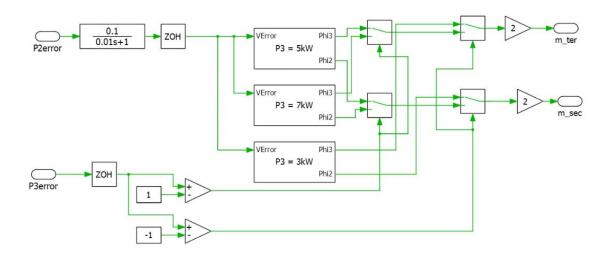

| Figure 16: Control blocks for selecting the power output at port 3                                |

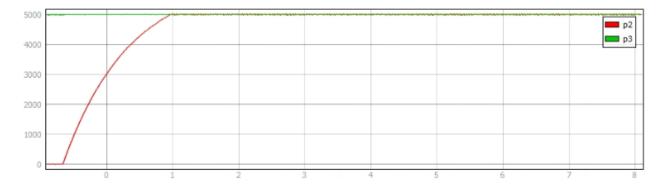

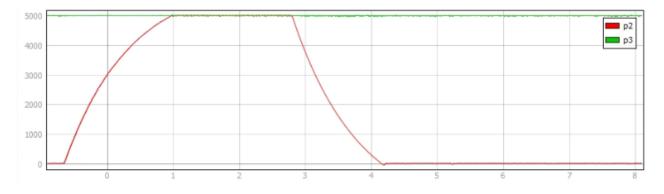

| Figure 17: Simulated CFTAB power output waveforms at ports 2 and 3 as the load for port 2         |

| changes from 0kW to 5kW                                                                           |

| Figure 18: Quick turn-on then turn-off of the load at port 2                                      |

| Figure 19: Control Card Launchpad and Buffer Board Circuit43                                      |

| Figure 20: Buffer Board Circuit                                                                   |

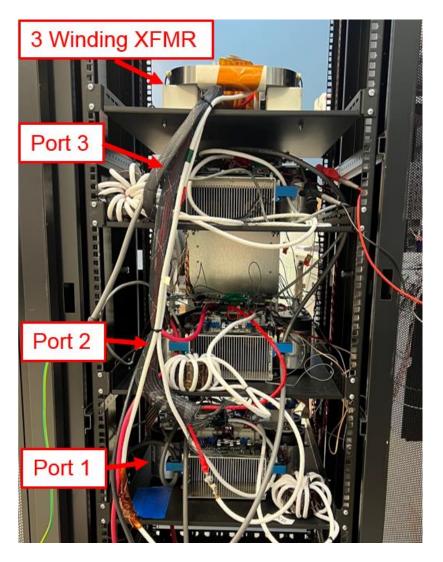

| Figure 21: 50kW 3 Port Dual Active Bridge Converter 46                                            |

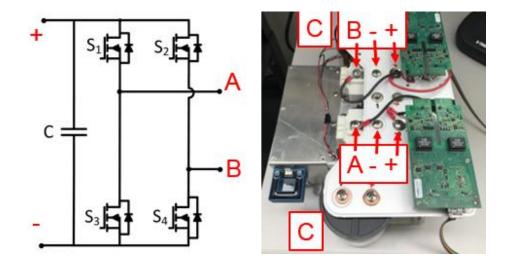

| Figure 22: Single H-Bridge Schematic (Left) and Physical Layout with SiC Modules and Mountee      |

| Gate Driver Boards (Right)                                                                        |

| Figure 23:Resistive Load Setup for TAB Test Bed 49                                                |

| Figure 24: TAB Test Bed Power Supply 50                                                           |

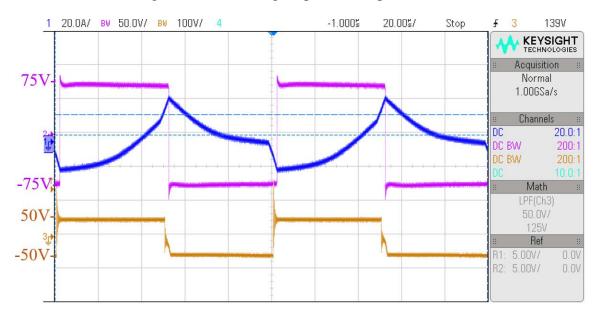

| Figure 25: AC switching waveforms. Port 2 Voltage (Purple), Port 2 Current (Blue), and Port 3     |

| Voltage (Orange). Port 1 Voltage, which is $\pm 150V$ , is not shown                              |

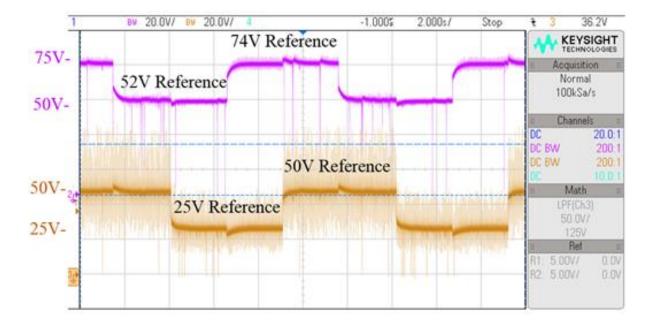

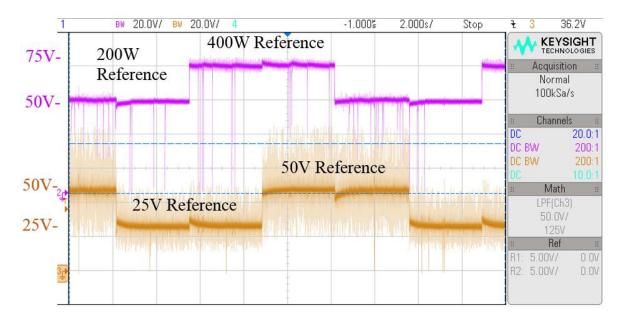

| Figure 26: Voltage reference changes for port 2 dc bus voltage (purple) and port 3 dc bus voltage |

| (orange) with PI controller on both ports 2 and 3 (reference case)                                |

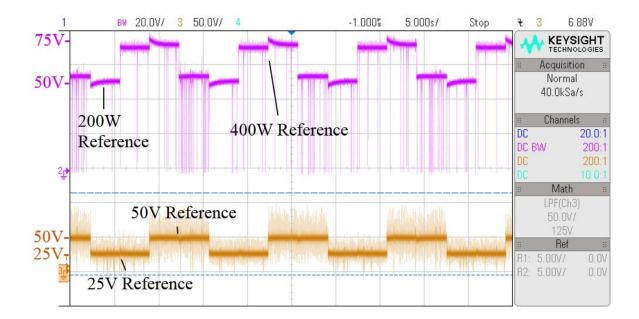

| Figure 27: Port 2 power flow control before tuning (a) and after tuning (b)                       |

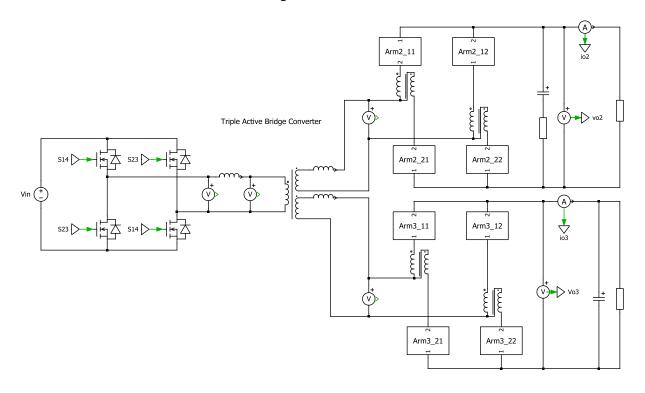

| Figure 28: PLECS Simulation Model of CF3P-DAB Converter                                           |

| Figure 29: Output waveforms at (a) the secondary port during a load change from 0W to 5kW and     |

| (b) the tertiary port maintaining a constant 5kW load                                             |

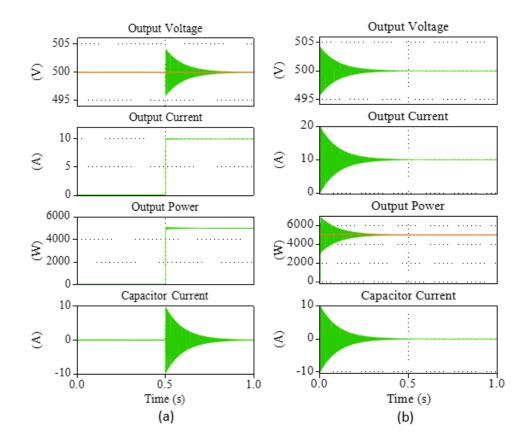

| Figure 30: PLECS Simulation Model of Back-to-Back CFMP-DAB Converters                             |

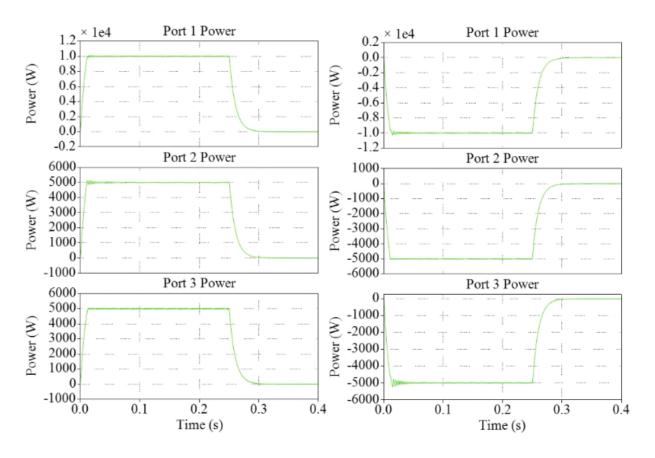

| Figure 31: Output waveforms for (a) the first CFMP-DAB converter splitting 10kW delivery                                                                                               |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| across two buses and (b) the second CFMP-DAB converter absorbing 5kW from each bus to feed                                                                                             |  |  |  |  |  |  |

| a constant 10kW load 59                                                                                                                                                                |  |  |  |  |  |  |

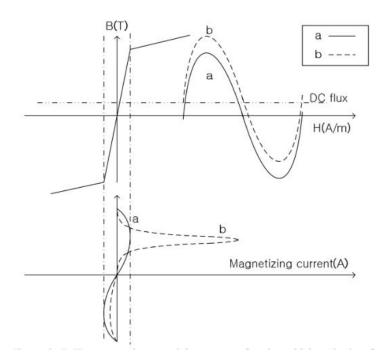

| Figure 32: B-H curve and magnetizing current for sinusoidal excitation for (a) average flux = $0$ ,                                                                                    |  |  |  |  |  |  |

| and (b) average flux $\neq 0$ [38]                                                                                                                                                     |  |  |  |  |  |  |

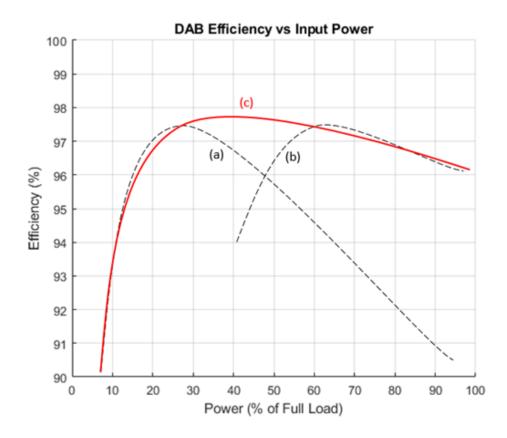

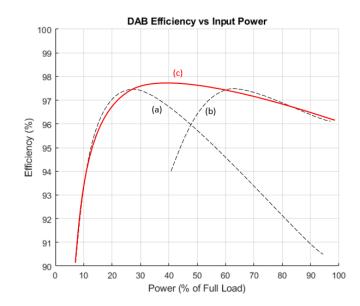

| Figure 34: Conceptual DAB efficiency curves with (a) wide operating range and high leakage                                                                                             |  |  |  |  |  |  |

| inductance $L= 2.5L0$ {where $L0$ is an arbitrary inductance value}, (b) high efficiency at max                                                                                        |  |  |  |  |  |  |

| load and low leakage inductance $L = L0/2.5$ , and (c) both high efficiency and wide operating                                                                                         |  |  |  |  |  |  |

| range using a tunable inductor $L0/2.5 \le L \le 2.5L0$                                                                                                                                |  |  |  |  |  |  |

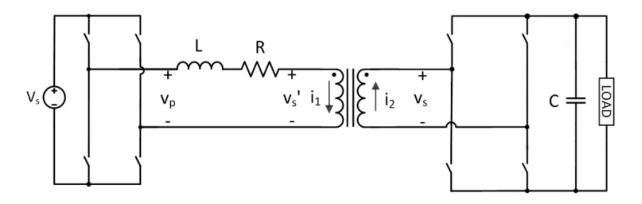

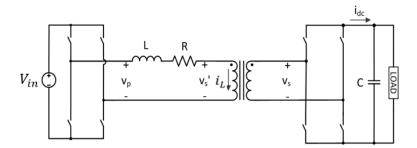

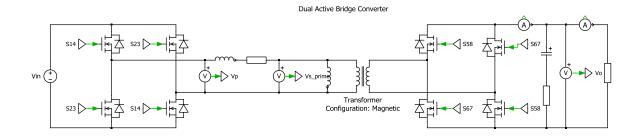

| Figure 35: Dual Active Bridge Converter Circuit Model                                                                                                                                  |  |  |  |  |  |  |

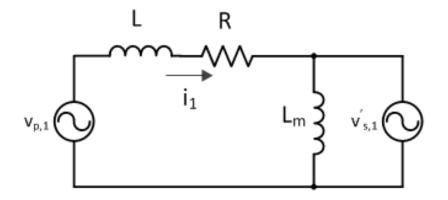

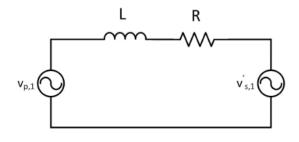

| Figure 36: Fundamental Harmonic Model of DAB Converter                                                                                                                                 |  |  |  |  |  |  |

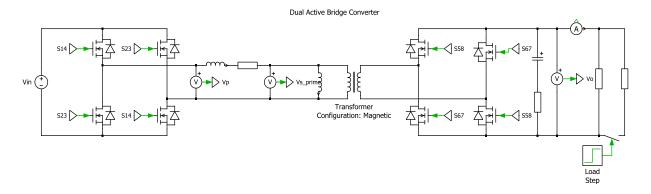

| Figure 37: DAB Converter Model within PLECS for Current Observer                                                                                                                       |  |  |  |  |  |  |

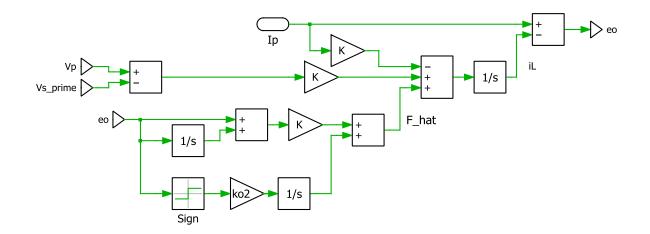

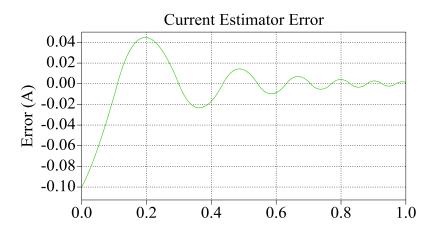

| Figure 38: Inductor Current Estimator for <i>iL</i> with the High Frequency Voltages as Inputs 70                                                                                      |  |  |  |  |  |  |

| Figure 39: Current Estimator Error71                                                                                                                                                   |  |  |  |  |  |  |

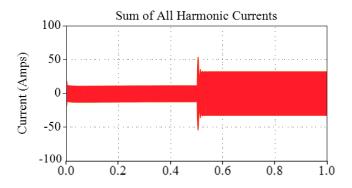

| Figure 40: AC Current of DAB with Load Step at 0.5s                                                                                                                                    |  |  |  |  |  |  |

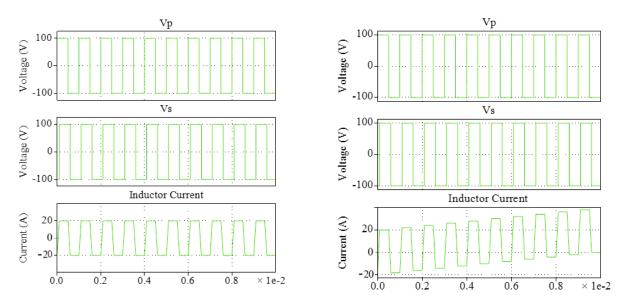

| Figure 41: AC Voltages and Currents for Symmetrical Switching, $Vp = 0.5$ ; , $Vs = 0.5$ (Left)                                                                                        |  |  |  |  |  |  |

| and Asymmetrical Switching, $Vp = 0.5$ ; $Vs = 0.495$ (Right)                                                                                                                          |  |  |  |  |  |  |

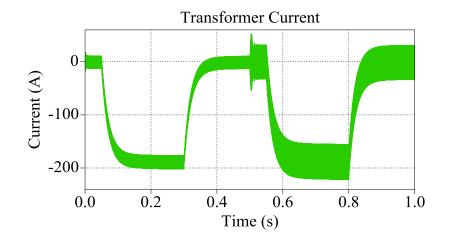

| Figure 42: DC Current Bias is Applied to Transformer at <b>0</b> . <b>05</b> <i>s</i> < <i>t</i> < <b>0</b> . <b>3</b> <i>s</i> and again at <b>0</b> . <b>55</b> <i>s</i> <           |  |  |  |  |  |  |

| <i>t</i> < 0.8 <i>s</i>                                                                                                                                                                |  |  |  |  |  |  |

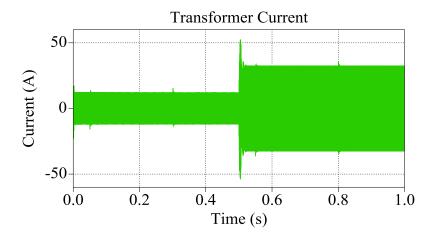

| Figure 43: Transformer Current with Compensation Strategy Implemented. DC Current Bias is                                                                                              |  |  |  |  |  |  |

| Applied to Transformer at <b>0</b> . <b>05</b> <i>s</i> < <i>t</i> < <b>0</b> . <b>3</b> <i>s</i> and again at <b>0</b> . <b>55</b> <i>s</i> < <i>t</i> < <b>0</b> . <b>8</b> <i>s</i> |  |  |  |  |  |  |

| Figure 44: Conceptual DAB efficiency curves with (a) wide operating range and high leakage                                                                                             |  |  |  |  |  |  |

| inductance $L= 2.5L0$ {where $L0$ is an arbitrary inductance value}, (b) high efficiency at max                                                                                        |  |  |  |  |  |  |

| load and low leakage inductance $L = L0/2.5$ , and (c) both high efficiency and wide operating |

|------------------------------------------------------------------------------------------------|

| range using a tunable inductor $L0/2.5 \le L \le 2.5L0$                                        |

| Figure 45: Dual Active Bridge Converter Model                                                  |

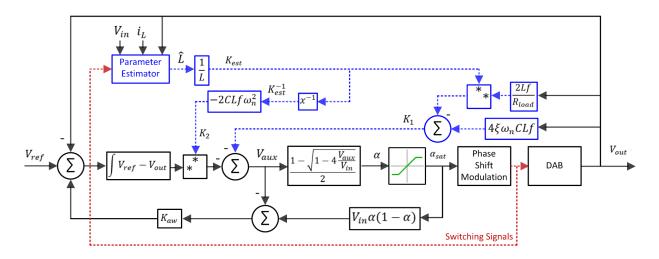

| Figure 46: Augmented Control Block DIagram Architecture with Parameter Estimator               |

| Figure 47: DAB Converter Fundamental Harmonic Model 80                                         |

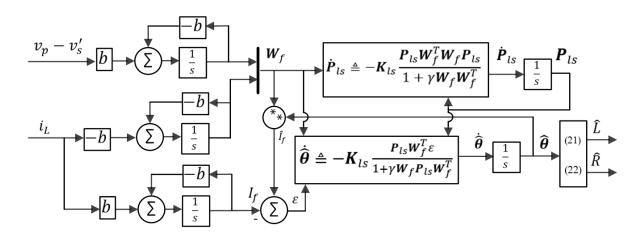

| Figure 48: Parameter Estimator Block Diagram                                                   |

| Figure 49: PLECS DAB Converter Model                                                           |

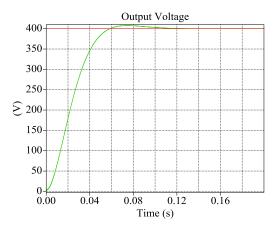

| Figure 50: Load Bus Voltage Large Signal Transient                                             |

| Figure 51: Typhoon HIL Experimental Setup                                                      |

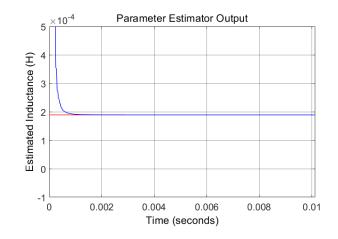

| Figure 52: Estimated Inductance (blue) vs Modeled Inductance (red)                             |

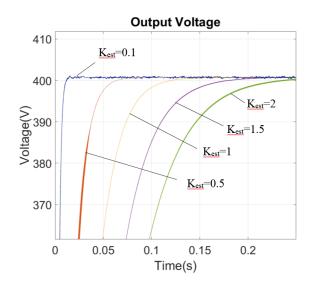

| Figure 53: Large Signal Transient without Parameter Estimator                                  |

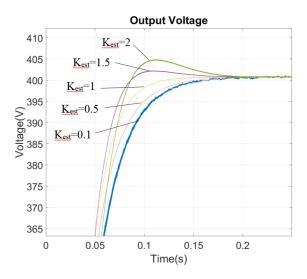

| Figure 54: Large Signal Transient with Parameter Estimator and compensation for values of      |

| Kest = LL                                                                                      |

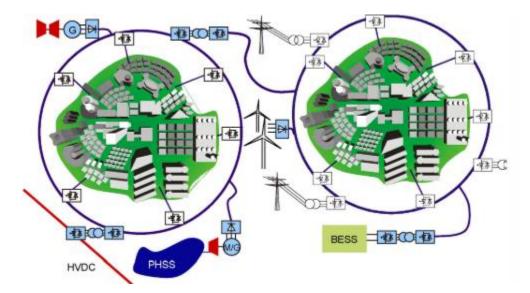

| Figure 55: Proposed multi-terminal DC network [11]. Note that 3-port converters could be used  |

| to decouple parts of the DC network in case maintanence or an outage occurs                    |

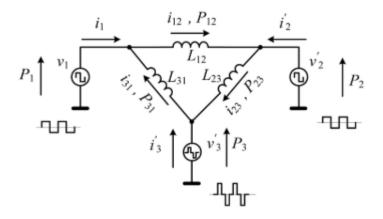

| Figure 56: Triple active bridge converter topology                                             |

| Figure 57: Delta model of triple active bridge converter [18]                                  |

| Figure 58: 3-Winding Transformer for Triple Active Bridge Converter                            |

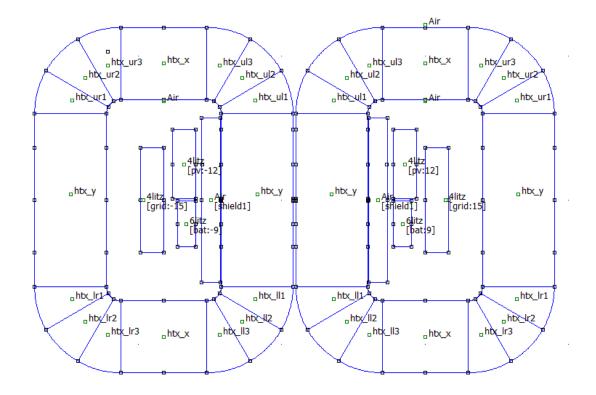

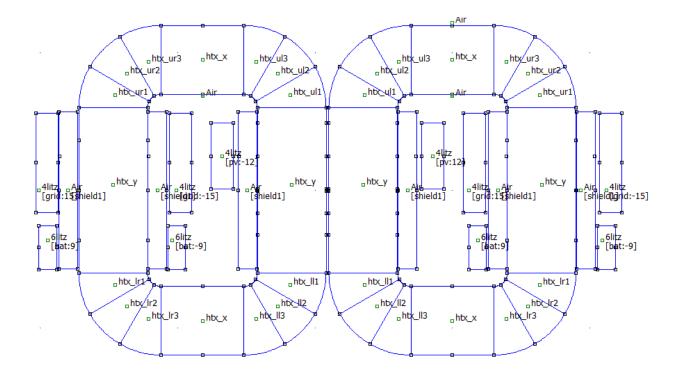

| Figure 59: FEMM Model of 3-Winding Transformer                                                 |

| Figure 60: FEMM Model of Split-Winding Configuration for 3-Winding Transformer                 |

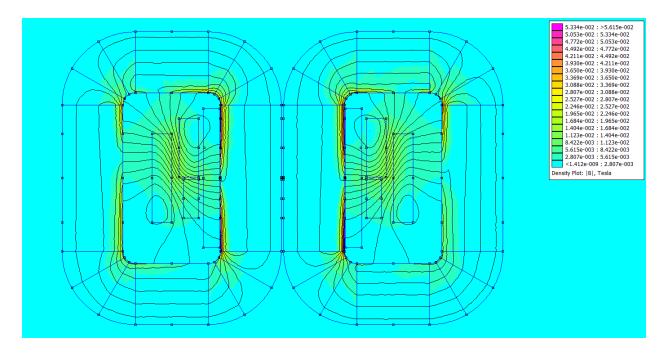

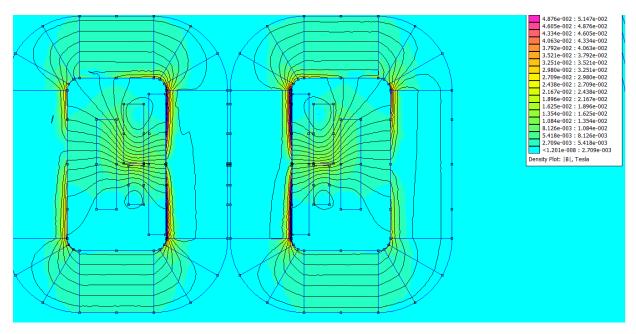

| Figure 61: FEMM Simulation Results – Scenario #1, Concentric Wound Configuration               |

| Figure 62: FEMM Simulation Results – Scenario #1, Split-Winding Configuration                  |

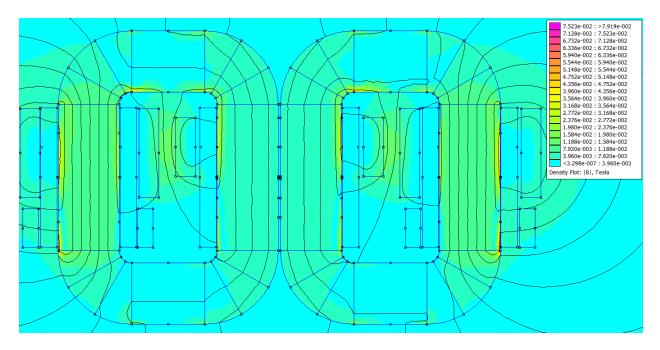

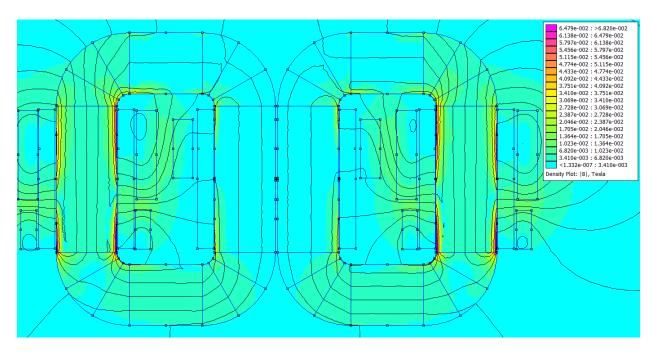

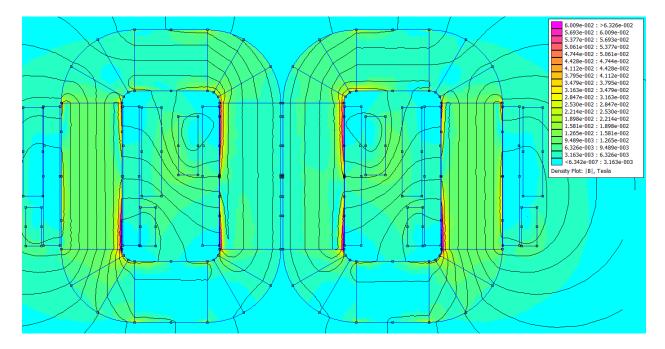

| Figure 63: FEMM Simulation Results – Scenario #2, Concentric Wound Configuration               |

| Figure 64: FEMM Simulation Results – Scenario #2, Split-Winding Configuration    | 100 |

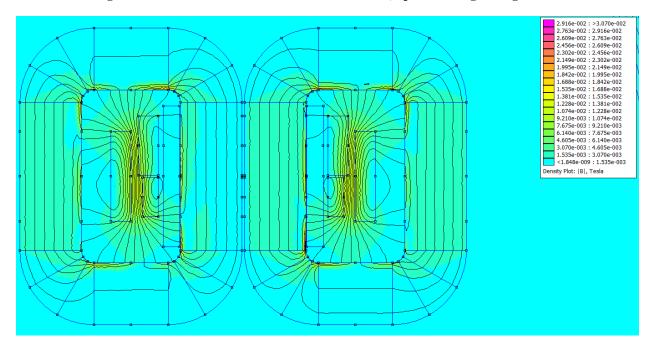

|----------------------------------------------------------------------------------|-----|

| Figure 65: FEMM Simulation Results – Scenario #3, Concentric Wound Configuration | 100 |

| Figure 66: FEMM Simulation Results – Scenario #3, Split-Winding Configuration    | 101 |

# Nomenclature

| DAB                     | Dual active bridge                                               |

|-------------------------|------------------------------------------------------------------|

| DC                      | Direct current                                                   |

| MMF                     | Magneto motive force                                             |

| MV                      | Medium voltage                                                   |

| MVDC                    | Medium voltage direct current                                    |

| ZCS                     | Zero current switching                                           |

| ZVS                     | Zero voltage switching                                           |

| $\phi_x$                | Switching phase shift angle at port $x$ with respect to port 1   |

| $D_x$                   | Duty cycle of switching voltage waveform at port $x$             |

| $f_s$                   | Switching frequency                                              |

| $n_x$                   | Transformer turns ratio at port $x$                              |

| L <sub>dc</sub>         | Self-inductance of mutual inductor                               |

| L <sub>M</sub>          | Mutual inductance of mutual inductor                             |

| $V_{xDC}$               | DC bus voltage at port $x$                                       |

| $v_x$                   | Port voltage at port <i>x</i>                                    |

| $i_x$                   | Port current at port <i>x</i>                                    |

| $v_{Lx}$                | Transformer leakage inductance voltage at port $x$               |

| V <sub>armx</sub>       | Square wave peak voltage for arm voltage at current-fed port $x$ |

| v <sub>armx-y</sub>     | Square wave voltage for arm $y$ voltage at current-fed port $x$  |

| <i>v<sub>armx</sub></i> | Switching voltage waveform for current-fed port $x$              |

- $v_{Tx}$  Voltage across transformer winding at port *x*

- $v_{xDCh1}$  Voltage across high-side mutual inductor 1 at current-fed port x

- $v_{xDCh2}$  Voltage across high-side mutual inductor 2 at current-fed port x

- $v_{xDCl1}$  Voltage across low-side mutual inductor 1 at current-fed port x

- $v_{xDCl2}$  Voltage across low-side mutual inductor 2 at current-fed port x

#### **1.0 Background**

The widespread adoption of dc systems for low-voltage applications at the distribution level has spurred further research into even higher power dc networks, including increased system voltages into the medium voltage (MV) range. At this point, many benefits of distributed energy resources (DERs) such as: increased system resilience, reduced transmission and generation capacity costs, and lowered environmental effects, are common knowledge in the industry.

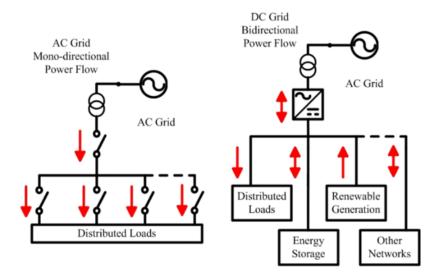

Unfortunately, without proper control, the increasingly dynamic distribution system is more likely to face voltage instability and protection coordination challenges [1]. One possible method of addressing these challenges is to place the DERs on a dc network instead of an ac network. Dc networks have been highly effective in the past at providing continuous, high-quality power to sensitive loads at the LV level by utilizing energy storage and advanced control to quickly respond to system transient events [2]. With the development of wide bandgap semiconductor devices, it is becoming viable to operate at the kilovolt level using solid-state switches [3]. In addition to switching device technology improvements, the increased levels of renewable energy resources entering the grid at the distribution level or naval grid architecture is creating a demand for increased control and safety measures at those levels. Figure 1 shows the key differences between a unidirectional ac network and a bidirectional dc network. Note that shipboard grids typically contain multiple electrical grid zones such as these, which only further increases the complexity of the network [4].

Figure 1: Monodirectional AC Grid (left) and Bidirectional DC Grid (right)

However, as the capacity of dc networks is increased, certain concerns arise. Namely, DERs themselves typically increase the control burden of the network [1], [5], [6]. In addition, the intermittent nature of renewable energy resources usually requires the system designer to include energy storage devices to reduce transient power fluctuation within the network [7]. On top of it all, traditional ac circuit breakers cannot be used within MVDC networks, making fault protection of these networks difficult.

A key component within dc networks that can address many of these issues is the converters that interface with the network. Modern solid-state switches and stacked topologies have recently enabled the possibility of operating at the kilovolt level for connection to the utility grid [8]–[10]. Power electronics can be used to increase flexibility of the dc network and also to respond to DERs [11]–[14].

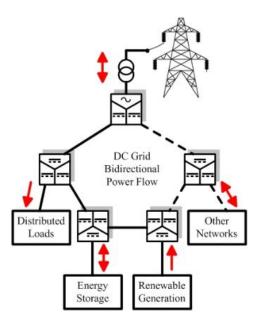

Figure 2: Example dc distribution ring bus network using bidirectional multi-port converters. Note that the distributed loads can receive power at the distribution level without experiencing long transmission losses.

A centralized converter with multiple ports can be used within a dc network to incorporate DERs, storage, and other networks into a grid with minimal conversion steps [15]–[18]. Also, by adding inductance to a converter, fault tolerant operation can be achieved [19]. If these features are combined, the result is a current-fed, multi-port converter that can interconnect multiple MVDC buses within a dc network [20]. The current-fed triple active bridge (CFTAB) converter design containing both of these features will be the basis for the research performed in this article [20]. See Figure 2 for an example of a dc network that makes use of such multi-port converters to create a ring network.

In addition, multi-port converters provide a method to tie in energy storage into the network using centralized control [16], [21]–[23]. At present, there are also at least 6 different categories of fault current limiting power converters available to protect the network from fault events [24].

This rise in microgrid research has opened the possibility of integrating battery energy storage and distributed generation within a shipboard power network. Energy storage has already proven a reliable method for increasing shipboard power system resilience as well as dispatching energy to pulsed power loads [25]. By leveraging the controllability of power electronics, it is possible to quickly dispatch power to desired electrical zones within the network [25]. This flexibility allows the reduction in size of the on-board generators, which are typically oversized to supply pulsed power loads [25].

A key technology gap within MVDC networks is the lack of a commercially available circuit breaker to interconnect buses and interrupt fault currents. Recently, there have been promising initiatives to develop dc circuit breakers, including a dc breaker for shipboard dc systems [26]. In the absence of a mature product, power electronics can instead be used to control power flow and limit the transient current surge during a fault [24]. Ultimately, in the future it should be possible to improve system resiliency by combining these redundant methods of fault protection for dc systems.

Triple active bridge-based (TAB) converters have been demonstrated to integrate photovoltaics, local dc generation, energy storage, and dc loads within the same system with minimal conversion steps [15], [16]. The addition of inductive components has been shown to provide fault-ride through capability during an extreme voltage collapse or sag event [19]. By incorporating the features of fault tolerance within a TAB converter, the resulting current-fed TAB (CFTAB) converter can interconnect multiple MVDC buses within a dc network [20].

# 2.0 Research Plan: Objective #1 - Design Considerations, Decoupled Control, and Grid Implementation of a CFTAB Converter

Objective #1 consists of a few distinct projects that focus on a current-fed triple active bridge (CFTAB) converter. The power flow study explores the relationship between the parameters of the magnetic components and the performance of the converter. From the analysis, a controller is proposed which decouples the 2 load ports from one another. The decoupled performance prevents load changes at one port from affecting the performance of the other load port. The controller was implemented within a control hardware-in-the-loop experiment as well as using a prototype 3-port converter. A PLECS model was used to demonstrate two CFTAB converters interconnected and operating in a ring bus configuration.

#### **2.1 Literature Review**

The widespread adoption of dc systems for low-voltage applications at the distribution level has spurred further research into even higher power dc networks, including increased system voltages into the medium voltage (MV) range. At this point, many benefits of distributed energy resources (DERs) such as: increased system resilience, reduced transmission and generation capacity costs, and lowered environmental effects, are common knowledge in the industry.

However, as the capacity of dc networks is increased, certain concerns arise. Namely, DERs themselves typically increase the control burden of the network [1], [5], [6]. In addition, the intermittent nature of renewable energy resources usually requires the system designer to

include energy storage devices to reduce transient power fluctuation within the network [7]. On top of it all, traditional AC circuit breakers cannot be used within MVDC networks, making fault protection of these networks difficult.

A key component within dc networks that can address many of these issues is the converters that interface with the network. Modern solid-state switches and stacked topologies have recently enabled the possibility of operating at the kilovolt level for connection to the utility grid [8]–[10]. Power electronics can be used to increase flexibility of the dc network and also to respond to DERs [11]–[14].

In addition, multi-port converters provide a method to tie in energy storage into the network using centralized control [16], [21]–[23]. At present, there are also at least 6 different categories of fault current limiting power converters available to protect the network from fault events [24].

A centralized converter with multiple ports can be used within a dc network to incorporate DERs, storage, and other networks into a grid with minimal conversion steps [15]–[18]. Also, by adding inductance to a converter, fault tolerant operation can be achieved [19]. If these features are combined, the result is a current-fed, multi-port converter that can interconnect multiple MVDC buses within a DC network [20]. The current-fed triple active bridge (CFTAB) converter design containing both of these features will be the basis for the research performed in this article [20]. See Figure 2 for an example dc network that makes use of such multi-port converters to create a ring network.

#### 2.2 Description of Converter

#### 2.2.1 Converter Topology

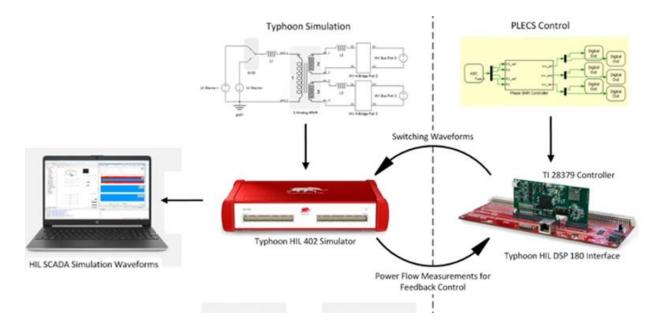

Traditionally, a dual active bridge (DAB) converter is comprised of a high frequency transformer with both the primary and secondary windings each having a full H-bridge interface to the primary and secondary dc buses [5], [27]–[29]. The primary-side H-bridge will generate a square waveform from the primary dc bus and apply it to the primary windings of the high frequency transformer. Likewise, the secondary-side H-bridge will generate a square waveform from the secondary DC bus and apply that voltage waveform to the secondary windings of the high frequency transformer. This traditional DAB topology can be controlled by adjusting the phase angle delay of the secondary side square wave with respect to the primary. Triple active bridge (TAB) converters are similar, with the addition of a tertiary H-bridge port and a 3-winding high frequency transformer [21], [30].

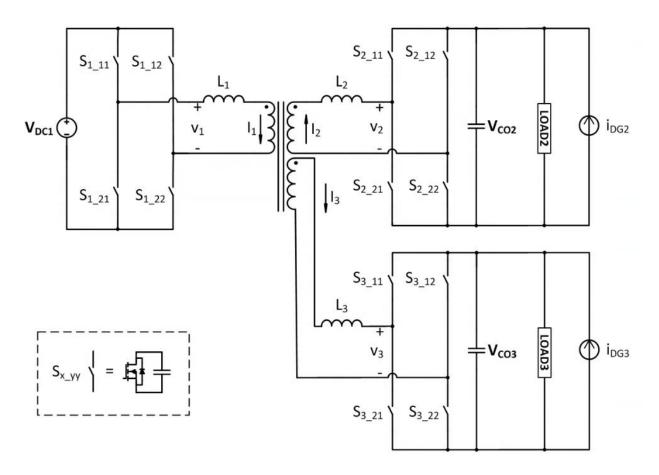

The current-fed triple active bridge (CFTAB) converter developed in this paper takes a similar design to a TAB converter, with mutual inductor pairs and MMC style arms added to the medium voltage windings of the 3-winding transformer [20]. The topology of the converter is shown in Figure 3. The secondary and tertiary ports are both connected to their respective MV dc buses. The application for the MV dc buses could be a redundant connection to a critical load, or to two separate dc buses altogether with independent load and generation profiles. To operate at MV levels, the secondary and tertiary sides will require switching submodules to be placed in arm configurations as shown in Figure 3. A simplification is made by in this paper by approximating each stacked arm submodule as a single ideal voltage source. This eliminates the need for a

complex and sensitive capacitor balancing scheme when modeling and evaluating the performance of the CFTAB converter.

The winding leakage inductance of the primary, secondary, and tertiary windings are  $L_1$ ,  $L_2$ , and  $L_3$ , respectively. The MV ports have mutual inductor pairs, and the naming convention is based on the pattern  $L_{xDCyz}$ , where x is the port number, y is either 'h' for high-voltage side (or closer to the positive dc voltage) or 'l' for low-voltage side (or closer to the negative dc voltage), and z is either 1 or 2 which identifies which inductor within the mutual inductor pair.

Figure 3: Current-fed triple active bridge topology for the example application of a LV-MV-MV converter. The MV arms consist of stacked submodules. Each MV port also contains 2 pairs of mutual inductors.

The converter power flow is determined by the voltages  $v_1$ ,  $v_2$ , and  $v_3$  and currents  $i_1$ ,  $i_2$ , and  $i_3$  which correspond to the primary, secondary, and tertiary transformer windings, respectively. The power flow at any port x can be computed as:

$$p_x = v_x i_x \tag{2-1}$$

Since MMF is shared within an ideal transformer, the overall power flow of the converter can be defined as:

$$p_1 = p_2 + p_3 \tag{2-2}$$

#### 2.2.2 Converter Operation

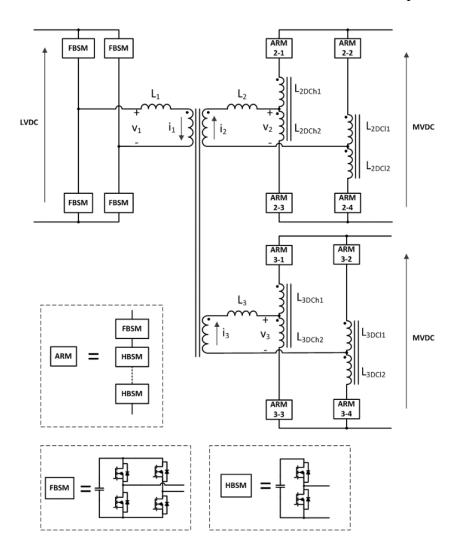

Traditional single phase shift control is used to regulate the power flow of the converter. As typical for DAB based converters, the average current through the transformer is assumed to be zero under stable operation. The proposed control is phase shift-based and uses average power output as the control reference. Shown in Figure 4 are the square voltage waveforms that are applied at each port of the converter. Note that while the voltage  $v_1$  is directly applied to the primary windings of the transformer, the arm voltage waveforms  $v_{arm2}$  and  $v_{arm3}$  are not directly applied to the secondary and tertiary MV transformer windings due to the mutual inductors. The voltages across the secondary and tertiary windings of the transformer ( $v_2$  and  $v_3$ ) can nevertheless be computed from the 3 controlled switched voltage waveforms ( $v_1$ ,  $v_{arm2}$ , and  $v_{arm3}$ ) The primary voltage waveform  $v_1$  is used as the reference, and the two controllable parameters are the phase shifts of the secondary ( $\phi_2$ ) and tertiary ( $\phi_3$ ). In addition to controlling phase shift, it is possible to additionally regulate the duty cycles of each square wave. However, the duty cycles at the ports with mutual inductors are bound by the relationship in (2-3) [31].

$$V_{busDC} = 2DV_{arm} \tag{2-3}$$

In (3), D = 0.5 represents an ideal square wave. If this condition is not met, the mutual inductor pairs will experience a dc voltage bias, and a dc bias in the current will result. Therefore, the duty cycles at the secondary and tertiary ports in this application are not freely available to be used as control variables, since they are limited by the voltage ratio of the bus voltages and arm capacitor voltages.

Figure 4: Switching voltage waveforms for each port:  $v_1$  (black),  $v_{arm2}$  (blue), and  $v_{arm3}$  (red). For this study, the port voltages will all be assumed to be 500V. The phase angles  $\phi_2$  and  $\phi_3$  are the control variables and use the primary waveform  $v_1$  as the reference.

#### 2.3 Power Flow Analysis

The average power flow was computed by using a switched circuit model for all 8 possible states. There are potentially more states, but in this application a duty cycle of D = 0.5 was

maintained on the secondary and tertiary ports for stability purposes (which reduces the number of possible switched states). To reduce possible states even further to simplify the analysis, the duty cycle of the primary was maintained at 0.5 as well.

A single switching cycle of this converter is expected to be within the kilohertz range (around 1 to 25kHz). This makes it intuitive to assume that the dc bus voltages and submodule voltages will remain constant within a switching cycle. Under this assumption, the current slopes become linear under a constant applied voltage, and a state space representation of the circuit can be constructed.

#### 2.3.1 Decoupling Mutual Inductor Characteristic Equations

One key challenge in the circuit analysis is mathematically decoupling the currents within the mutual inductor pairs. The standard equation for the voltage applied across an inductor with mutual coupling is:

$$v_{\alpha} = L_{\alpha} \frac{di_{\alpha}}{dt} - M \frac{di_{\beta}}{dt}$$

(2-4)

Where  $\alpha$  denotes the first inductor within the coupled pair and  $\beta$  denotes the second inductor. This equation is unfortunately not a linear state equation due to the two inductor current derivatives. However, it is possible to perform a circuit analysis to substitute for one of the inductor current derivatives. Reducing the equation into a linear form will permit the creation of a state-space model for the circuit for each switch configuration.

Reflecting on the topology in Figure 3, there are 2 mutual inductor pairs on each of the two MV ports. This equates to a total of 8 inductors that have non-linear state equations. Performing

the substitution to a linear form will require 21 equations. The equations can be derived from the circuit diagram in Figure 3 as follows:

Mutual inductor equations from Kirchhoff's voltage loop within one MV port:

$$v_{2dch2} - v_{2dch1} = v_{2dcl1} - v_{2dcl2} \tag{2-5}$$

$$v_{3dch2} - v_{3dch1} = v_{3dcl1} - v_{3dcl2} \tag{2-6}$$

Kirchhoff's voltage loops within each MV port:

$$v_{Co2} - v_{Carm2-11} - v_{2dch1} - v_{2dch2} - v_{Carm2-21}$$

=  $v_{Co2} - v_{Carm2-12} - v_{2dcl1} - v_{2dcl2} - v_{Carm2-22}$  (2-7)

$$v_{Co3} - v_{Carm3-11} - v_{3dch1} - v_{3dch2} - v_{Carm3-21}$$

=  $v_{Co3} - v_{Carm3-12} - v_{3dcl1} - v_{3dcl2} - v_{Carm3-22}$  (2-8)

$$v_{Co2} = v_{Carm2-12} + v_{2dcl1} - v_2 + v_{2dch2} + v_{Carm2-21}$$

(2-9)

$$v_{Co3} = v_{Carm3-12} + v_{3dcl1} - v_3 + v_{3dch2} + v_{Carm3-21}$$

(2-10)

$$v_{co2} = v_{Carm2-11} + v_{2dch1} + v_2 + v_{2dcl2} + v_{Carm2-22}$$

(2-11)

$$v_{Co3} = v_{Carm3-11} + v_{3dch1} + v_3 + v_{3dcl2} + v_{Carm3-22}$$

(2-12)

Kirchoff's current law at ports 2 and 3:

$$\frac{v_{L2}}{L_2} = -\frac{di_{2dch1}}{dt} + \frac{di_{2dch2}}{dt}$$

(2-13)

$$\frac{v_{L3}}{L_3} = -\frac{di_{3dch1}}{dt} + \frac{di_{3dch2}}{dt}$$

(2-14)

Faraday's law for mutual inductors in ports 2 and 3:

$$v_{2dch1} = L_{dc} \frac{di_{2dch1}}{dt} + M \frac{di_{2dch2}}{dt}$$

(2-15)

$$v_{2dch2} = L_{dc} \frac{di_{2dch2}}{dt} + M \frac{di_{2dch1}}{dt}$$

(2-16)

$$v_{2dcl1} = L_{dc} \frac{di_{2dcl1}}{dt} + M \frac{di_{2dcl2}}{dt}$$

(2-17)

$$v_{2dcl2} = L_{dc} \frac{di_{2dcl2}}{dt} + M \frac{di_{2dcl1}}{dt}$$

(2-18)

$$v_{3dch1} = L_{dc} \frac{di_{3dch1}}{dt} + M \frac{di_{3dch2}}{dt}$$

(2-19)

$$v_{3dch2} = L_{dc} \frac{di_{3dch2}}{dt} + M \frac{di_{3dch1}}{dt}$$

(2-20)

$$v_{3dcl1} = L_{dc} \frac{di_{3dcl1}}{dt} + M \frac{di_{3dcl2}}{dt}$$

(2-21)

$$v_{3dcl2} = L_{dc} \frac{di_{3dcl2}}{dt} + M \frac{di_{3dcl1}}{dt}$$

(2-22)

Note that the second current slope term is added instead of subtracted as in (2-4). This is simply due to the current direction defined in the other direction in the circuit schematic in Figure 3.

Three-winding transformer turns ratio and current balance equations:

$$\frac{v_1 - v_{L1}}{n_1} = \frac{v_2 + v_{L2}}{n_2} \tag{2-23}$$

$$\frac{v_1 - v_{L1}}{n_1} = \frac{v_3 + v_{L3}}{n_3} \tag{2-24}$$

$$n_1 i_{L1} = n_2 i_{L2} + n_3 i_{L3} \tag{2-25}$$

The final step in preparation to solve the equation is to establish which variables are states within the system and which are controllable inputs. After decoupling the mutual inductor currents, the system can then easily be rewritten into state space form. The state space equation is of the form  $\dot{x} = Ax + Bu$  where the arrays x and u are:

$$\boldsymbol{x} = [i_{L1} \ i_{L2} \ i_{L3} \ v_{Co2} \ v_{Co3} \ v_{Carm2-11} \ v_{Carm2-12} \ v_{Carm2-21} \ v_{Carm2-22} \ \dots$$

$$\dots \ i_{2dch1} \ i_{2dcl1} \ i_{2dcl2} \ i_{2dcl2} \ v_{Carm3-11} \ v_{Carm3-12} \ \dots$$

$$(2-26)$$

$v_{Carm3-21} v_{Carm3-22} l_{3dch1} l_{3dcl1} l_{3dch2} l_{3dcl2}]^{\prime}$

$$\boldsymbol{u} = [V_1 \ I_{DC2} \ I_{DC3}]^T \tag{2-27}$$

Solving for each state variable is done through MATLAB's symbolic solver toolkit. This solver was used to solve the system of 21 equations to mathematically decouple the mutual inductor currents from their respective pair. The result of the analysis provided a linear equation for the current derivatives for each mutual inductor, which allowed the system to be put into state space form.

#### 2.3.2 State Space Matrix

This section describes the process for computing the average power flow output of the converter. The switching frequency is assumed to be much faster than the time constant of the

capacitors within the dc buses and MV arms. Under this assumption, the inductor currents are the only state variable to change appreciably within one switching cycle, and the currents can be assumed to be linear.

The *A* and *B* matrices were constructed by using the inductor current derivatives solved in (2-5)-(2-25). The capacitor voltage derivatives were easily computed from Kirchhoff's nodal analysis. Unfortunately, the symbolic representation of the 21-state system has too many terms to fit within this paper, thus the symbolic matrices themselves are not included. Instead, the numeric *A* matrix is solved for using the parameters listed in Table I. The switching state that generates positive voltages for  $v_1$ ,  $v_{arm2}$ , and  $v_{arm3}$  is used. The resulting *A* matrix is provided in Figure 5.

| 0 | 0 | 0 | 0  | 0  | 0 | -156 | -156 | 0 | 0 | 0     | 0     | 0     | 0 | -156 | -156 | 0 | 0 | 0     | 0     | 0     |

|---|---|---|----|----|---|------|------|---|---|-------|-------|-------|---|------|------|---|---|-------|-------|-------|

| 0 | 0 | 0 | 0  | 0  | 0 | -234 | -234 | 0 | 0 | 0     | 0     | 0     | 0 | 78   | 78   | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 78   | 78   | 0 | 0 | 0     | 0     | 0     | 0 | -234 | -234 | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | -1000 | 0     | -1000 | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | -1000 | 0     | -1000 |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 10000 | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 10000 | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 69 | 0  | 0 | 117  | 48   | 0 | 0 | 0     | 0     | 0     | 0 | -39  | -39  | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 69 | 0  | 0 | -117 | -187 | 0 | 0 | 0     | 0     | 0     | 0 | 39   | 39   | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 69 | 0  | 0 | -187 | -117 | 0 | 0 | 0     | 0     | 0     | 0 | 39   | 39   | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 69 | 0  | 0 | 48   | 117  | 0 | 0 | 0     | 0     | 0     | 0 | -39  | -39  | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 10000 | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 10000 | 0     | 0     |

| 0 | 0 | 0 | 0  | 0  | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     | 0 | 0    | 0    | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 69 | 0 | -39  | -39  | 0 | 0 | 0     | 0     | 0     | 0 | 117  | 48   | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 69 | 0 | 39   | 39   | 0 | 0 | 0     | 0     | 0     | 0 | -117 | -187 | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 69 | 0 | 39   | 39   | 0 | 0 | 0     | 0     | 0     | 0 | -187 | -117 | 0 | 0 | 0     | 0     | 0     |

| 0 | 0 | 0 | 0  | 69 | 0 | -39  | -39  | 0 | 0 | 0     | 0     | 0     | 0 | 48   | 117  | 0 | 0 | 0     | 0     | 0     |

Figure 5: State Space *A* matrix using the parameters in Table I. Note that this matrix changes with the switched states. This analytical solution for the *A* matrix matches the results from the PLECS 'get'

'topology' function.

Table 1 provides the circuit design parameters for the CFTAB converter. These parameters are based on the design parameters of a previous analysis and are similar to analyses on other multi-port structures [16], [20]. One key feature to note is that the switching frequency of the design has been slowed down from 40kHz to 1kHz to account for performance restrictions within the TI controller and real-time digital simulator (discussed in Section V). To achieve similar output power of the converter, the inductance values are increased by a factor of 40 from the reference design. Note that this limitation of the experimental setup is not in itself a limitation of the speed of the proposed control or converter.

| Variable          | Parameter                    | Value  |

|-------------------|------------------------------|--------|

| $n_1$             | Primary Turns Ratio          | 1      |

| $n_2$             | Secondary Turns Ratio        | 1      |

| $n_3$             | Tertiary Turns Ratio         | 1      |

| $L_1$             | Primary Winding Inductance   | 800µH  |

| $L_2$             | Secondary Winding Inductance | 800µH  |

| $L_3$             | Tertiary Winding Inductance  | 800µH  |

| $L_{dc}$          | Coupled Inductor Inductance  | 4.0mH  |

| $L_M$             | Mutual Inductance            | 3.2mH  |

| $f_s$             | Switching Frequency          | 1.0kHz |

| $D_1$             | Primary Duty Cycle           | 0.5    |

| $D_2$             | Secondary Duty Cycle         | 0.5    |

| $D_3$             | Tertiary Duty Cycle          | 0.5    |

| $V_{1DC}$         | Primary DC Voltage           | 500V   |

| $V_{2DC}$         | Secondary DC Voltage         | 500V   |

| V <sub>3DC</sub>  | Tertiary DC Voltage          | 500V   |

| V <sub>arm2</sub> | Secondary Arm Voltage        | 500V   |

| V <sub>arm3</sub> | Tertiary Arm Voltage         | 500V   |

| T <sub>s</sub>    | Switching Period             | 1.0ms  |

**Table 1: CFTAB Converter Circuit Parameters**

One thing to note is that the matrices A and B will change with each switch configuration. For simplicity, the duty cycle of all ports is assumed to be 50%. This means that the voltage is positive for half the cycle and negative for the remainder of the cycle. This limits the number of possible states for each port to 2. With 3 ports, the number of possible states is  $2^3$ , or 8. The matrices A and B were computed for each switch configuration.

To confirm the accuracy of the state space matrices, a PLECS circuit schematic of the converter was developed. The results of the PLECS circuit analysis confirmed the accuracy of the state space matrices. The converter model used the circuit parameters in Table 1 match the analytically derived state-space matrices and match the results in Figure 5.

#### 2.3.3 Computation of Steady-State Current Waveforms

Before computing the average power flow, the average current through the transformer inductors must equal zero. Typically, this means that at steady-state, the current values at the start of a switching cycle are non-zero. To determine the correct initial current values, begin with zero initial current within all inductors, and then compute the final current values after the 3<sup>rd</sup> switched state (halfway through the switching cycle). The initial current is equal to:  $i(0) = -\frac{1}{2}i\left(\frac{T_s}{2}\right)$ .

As the system is in state-space form, the linear derivatives of currents are known. The change in current during a state is equal to the following equation where  $\varphi$  is the fraction of the total switching cycle that the state is active:

$$\Delta i = \frac{di}{dt}\varphi T_s \tag{2-28}$$

Since all switching signals have a 50% duty cycle, the converter should be exactly halfway through the switching cycle after 3 states.

Once the steady-state initial current values are known, the current waveform for an entire cycle can be computed by applying (2-28) for each of the 6 states. Since there are 6 states, there will be 6 intervals to compute the change in current. The current value at the end of each state can be computed with (29):

$$i_{Lx}(t_{fn}) = \Delta i_{Lx} + i_{Lx}(t_{in})$$

(2-29)

Where *x* represents the port number,  $t_{fn}$  is the final time at the end of state *n*, and  $i_{Lx}(0)$  is the initial current at the beginning of state *n*.

#### 2.3.4 Computation of Average Power Flow

The voltage during a state is assumed to remain constant. The current changes in a linear trajectory. Therefore, the average power flow at a port during a single state is equal to

$$P_{xn} = v_x \frac{\left(i_x(0) + i_x(t_{fn})\right)}{2}$$

(2-30)

Where *x* represents the port number and  $t_{fn}$  is the final time at the end of state *n*. Recall that the current  $i_x$  is equivalent to the current flowing through the transformer winding at that port  $i_{Lx}$ . The MV voltages can be computed from (2-9) and (2-10), and the primary port voltage is already known. Since the transformer leakage inductor currents are states, the initial and final current at each state can easily be computed using the state space matrices using the method described in (2-28). The average power flow through the converter during an entire switching cycle can be computed by:

$$P_{xavg} = \sum_{n=1}^{6} P_{xn}\varphi_{xn} \tag{2-31}$$

Where  $P_{xn}$  is the average power at port x during state n, and  $\varphi_{xn}$  is the fraction of the total switching cycle that state n occurs. The phase shift  $\varphi$  can be converted to radians by multiplying by  $2\pi$ .

#### 2.3.5 Average Power Flow Equations Across All Modes

The average power flow was computed for the entire operating range of the converter  $(-0.5 < \varphi_2 \le 0.5 \text{ and } -0.5 < \varphi_3 \le 0.5)$ . A key feature to note is that the power flow equations are unique to the sequence of the switches. There are 8 possible switching sequences, and each sequence will be called a 'mode' of the converter. See Table 2 for the list of possible operating modes of the converter. The resulting power flow equations for each mode are as follows:

### <u>MODE 1:</u> $0 < \phi_2 < \phi_3$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (-2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (-2 \phi_{3}^{2} + \phi_{3})]\}$$

$$(2-32)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [-2(L_{3\alpha} n_{1} V_{1} - L_{3} n_{3} V_{Carm3-0}) \phi_{2}^{2} + (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) \phi_{2} + L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} - \phi_{3}) - 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} ] \}$$

$$(2-33)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (-2\phi_{2}^{2} - \phi_{2}) + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) (-2\phi_{3}^{2} + \phi_{3}) + 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-34)$$

Where,

$$L_{\alpha} = (L_{dc} - M)^2 n_1^2 + L_2 L_3 (n_1^2 + n_2^2 + n_3^2) + (L_{dc} - M) (L_2 n_1^2 + L_2 n_2^2 + L_3 n_1^2 + L_3 n_3^2)$$

(2-35)

$\underline{\text{MODE 2:}} \quad 0 < \phi_3 < \phi_2$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (-2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (-2 \phi_{3}^{2} + \phi_{3})]\}$$

$$(2-36)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [ (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) (-2\phi_{2}^{2} + \phi_{2}) - L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} + \phi_{3}) + 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} ] \}$$

$$(2-37)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (2\phi_{2}^{2} - \phi_{2}) - 2(L_{2\alpha} n_{1} V_{1} - L_{2} n_{2} v_{Carm2-0}) \phi_{3}^{2} + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) \phi_{3} - 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-38)$$

$\underline{\text{MODE 3:}} \quad \phi_3 < \phi_2 < 0$

$$P_{1} \approx L_{1}^{-1}L_{\alpha}^{-1}\{T_{s}n_{1}V_{1}[L_{2}L_{3\alpha}n_{2}V_{Carm2-0}(2\phi_{2}^{2}+\phi_{2}) + L_{2\alpha}L_{3}n_{3}V_{Carm3-0}(2\phi_{3}^{2}+\phi_{3})]\}$$

(2-39)

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [2(L_{3\alpha} n_{1} V_{1} - L_{3} n_{3} V_{Carm3-0}) \phi_{2}^{2} + (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) \phi_{2} + L_{3} n_{3} V_{Carm3-0} (-2\phi_{3}^{2} - \phi_{3}) + 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} ] \}$$

$$(2-40)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [ L_{2} n_{2} V_{Carm2-0} (2\phi_{2}^{2} - \phi_{2}) + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) (2\phi_{3}^{2} + \phi_{3}) - 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-41)$$

$\underline{\text{MODE 4:}} \quad \phi_2 < \phi_3 < 0$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (2 \phi_{3}^{2} + \phi_{3})]\}$$

$$(2-42)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [ (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) (2\phi_{2}^{2} + \phi_{2}) + L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} - \phi_{3}) - 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} ] \}$$

$$(2-43)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (-2\phi_{2}^{2} - \phi_{2}) + 2(L_{2\alpha} n_{1} V_{1} - L_{2} n_{2} v_{Carm2-0}) \phi_{3}^{2} + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) \phi_{3} + 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-44)$$

**<u>MODE 5:</u>**  $\phi_2 < 0 < \phi_3; \quad \phi_3 - \phi_2 < 0.5$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (-2\phi_{3}^{2} + \phi_{3})]\}$$

$$(2-45)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [ (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) (2\phi_{2}^{2} + \phi_{2}) + L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} - \phi_{3}) - 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3}] \}$$

$$(2-46)$$

$$P_{3} \approx L_{a}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (-2\phi_{2}^{2} - \phi_{2}) + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) (-2\phi_{3}^{2} + \phi_{3}) + 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-47)$$

**<u>MODE 6:</u>**  $\phi_2 < 0 < \phi_3; \ \phi_3 - \phi_2 > 0.5$

$$P_{1} \approx L_{1}^{-1}L_{\alpha}^{-1}\{T_{s}n_{1}V_{1}[L_{2}L_{3\alpha}n_{2}V_{Carm2-0}(2\phi_{2}^{2}+\phi_{2}) + L_{2\alpha}L_{3}n_{3}V_{Carm3-0}(-2\phi_{3}^{2}+\phi_{3})]\}$$

(2-48)

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [2(L_{3\alpha} n_{1} V_{1} - L_{3} n_{3} V_{Carm3-0}) \phi_{2}^{2} + (L_{3\alpha} n_{1} V_{1} - 3L_{3} n_{3} V_{Carm3-0}) \phi_{2} + L_{3} n_{3} V_{Carm3-0} (-2\phi_{3}^{2} + 3\phi_{3}) + 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} - L_{3} n_{2} V_{Carm2-0} ] \}$$

$$(2-49)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (2\phi_{2}^{2} + 3\phi_{2}) - 2(L_{2\alpha} n_{1} V_{1} - L_{2} n_{2} v_{Carm2-0}) \phi_{3}^{2} + (L_{2\alpha} n_{1} V_{1} - 3L_{2} n_{2} v_{Carm2-0}) \phi_{3} - 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} + L_{2} n_{2} V_{carm2-0} ] \}$$

$$(2-50)$$

**<u>MODE 7:</u>**  $\phi_3 < 0 < \phi_2; \ \phi_2 - \phi_3 < 0.5$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (-2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (2 \phi_{3}^{2} + \phi_{3})]\}$$

$$(2-51)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [ (L_{3\alpha} n_{1} V_{1} + L_{3} n_{3} V_{Carm3-0}) (-2\phi_{2}^{2} + \phi_{2}) + L_{3} n_{3} V_{Carm3-0} (-2\phi_{3}^{2} - \phi_{3}) + 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} ] \}$$

$$(2-52)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (2\phi_{2}^{2} - \phi_{2}) + (L_{2\alpha} n_{1} V_{1} + L_{2} n_{2} v_{Carm2-0}) (2\phi_{3}^{2} + \phi_{3}) - 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} ] \}$$

$$(2-53)$$

**<u>MODE 8:</u>**  $\phi_3 < 0 < \phi_2; \phi_2 - \phi_3 > 0.5$

$$P_{1} \approx L_{1}^{-1} L_{\alpha}^{-1} \{T_{s} n_{1} V_{1} [L_{2} L_{3\alpha} n_{2} V_{Carm2-0} (-2 \phi_{2}^{2} + \phi_{2}) + L_{2\alpha} L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} + \phi_{3})]\}$$

$$(2-54)$$

$$P_{2} \approx L_{\alpha}^{-1} \{ T_{s} n_{2} V_{Carm2-0} [-2(L_{3\alpha} n_{1} V_{1} - L_{3} n_{3} V_{Carm3-0}) \phi_{2}^{2} + (L_{3\alpha} n_{1} V_{1} - 3L_{3} n_{3} V_{Carm3-0}) \phi_{2} + L_{3} n_{3} V_{Carm3-0} (2\phi_{3}^{2} + 3\phi_{3}) - 4L_{3} n_{3} V_{Carm3-0} \phi_{2} \phi_{3} + L_{3} n_{2} V_{Carm2-0} ] \}$$

$$(2-55)$$

$$P_{3} \approx L_{\alpha}^{-1} \{ T_{s} n_{3} V_{Carm3-0} [L_{2} n_{2} V_{Carm2-0} (-2\phi_{2}^{2} + 3\phi_{2}) + 2(L_{2\alpha} n_{1} V_{1} - L_{2} n_{2} v_{Carm2-0}) \phi_{3}^{2} + (L_{2\alpha} n_{1} V_{1} - 3L_{2} n_{2} v_{Carm2-0}) \phi_{3} + 4L_{2} n_{2} V_{Carm2-0} \phi_{2} \phi_{3} - L_{2} n_{2} V_{Carm2-0} ] \}$$

$$(2-56)$$

# 2.4 Design Considerations for Mutual Inductors and Transformer Leakage Inductance

To confirm the accuracy of the characteristic equations, a PLECS simulation was developed. Circuit component values were chosen based upon the values from a reference experiment of a current-fed DAB [32]. Table 2 includes the parameters that were used for both the

calculations and the simulation. Note that these parameters are for an application at a higher switching frequency than the parameters found in Table 1.

| Variable          | Parameter                        | Value |

|-------------------|----------------------------------|-------|

| $n_1$             | Primary Turns Ratio              | 1     |

| $n_2$             | Secondary Turns Ratio            | 1     |

| $n_3$             | Tertiary Turns Ratio             | 1     |

| $L_1$             | Primary Winding Inductance       | 20µH  |

| $L_2$             | Secondary Winding Inductance     | 20μΗ  |

| $L_3$             | Tertiary Winding Inductance      | 20µH  |

| $L_{dc}$          | Coupled Inductor Inductance      | 100µH |

| М                 | Mutual Inductance                | 80µH  |

| $f_s$             | Switching Frequency              | 40kHz |

| $D_1$             | Primary Duty Cycle               | 0.5   |

| $D_2$             | Secondary Duty Cycle             | 0.525 |

| $D_3$             | Tertiary Duty Cycle              | 0.525 |

| $\phi_2$          | Secondary Switching Delay (p.u.) | 0.1   |

| $\phi_3$          | Tertiary Switching Delay (p.u.)  | 0.15  |

| $V_{1DC}$         | Primary DC Voltage               | 500V  |

| $V_{2DC}$         | Secondary DC Voltage             | 525V  |

| $V_{3DC}$         | Tertiary DC Voltage              | 525V  |

| V <sub>arm2</sub> | Secondary Arm Voltage            | 500V  |

| V <sub>arm3</sub> | Tertiary Arm Voltage             | 500V  |

| T <sub>s</sub>    | Switching Period                 | 25µs  |

Table 2: CFTAB Converter Circuit Parameters for Leakage Inductance Analysis

-

For the analysis, each arm was treated as a square wave voltage source. Note that  $arm_{2-1}$  and  $arm_{2-4}$  switch as a pair; likewise,  $arm_{2-2}$  and  $arm_{2-3}$  switch as a pair. Also, as the duty cycle of the arms extend beyond 0.5, the voltage difference waveform  $v_{arm_2}$  will have zero states as if it were operating with a duty cycle below 0.5.

Additional assumptions are made for some of the parameters. For instance, an 80% mutual coupling coefficient M was selected to determine the mutual inductance  $L_M$ . If a different value of M is chosen, port voltages  $v_2$  and  $v_3$  will be affected because ports 2 and 3 contain mutual inductors. An analysis of converter performance with respect to varying values of M has not been performed in this study.

For simplification of the analysis and to match the parameters with the reference experiment, the turns ratio of the transformer is kept at 1:1:1. Note that in order to maintain stable operation at an arbitrary current fed port x, the arm voltage is related to the DC voltage with

$$V_{xDC} = 2D_x V_{armx}.$$

(2-57)

This relationship exists to maintain the coupled inductor Volt-second balance. Deviating from this relationship will impose a DC current bias on the coupled inductors and could possibly lead to instability. In practice, this means the capacitors within the arm submodules will require cell voltage balancing to enforce a constant overall arm voltage.

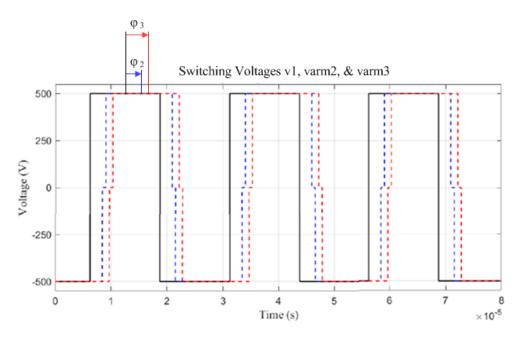

The switching phase angle delays  $\phi_x$  for the secondary and tertiary ports are selected to be different to conveniently isolate the effects of switching at each port. As shown in Figure 7, a key feature of the converter voltages  $v_2$  and  $v_3$  is that the voltages deviate further from an ideal square wave as the phase angle delays  $\phi_x$  increase. Therefore, the phase angle delays were kept at relatively small values (0.1 and 0.15). This is typically acceptable in applications where the converter has been optimized for high efficiency at full load with a narrower operating range.

Figure 7. Analytical vs simulation waveforms for port voltages and switching waveforms.

Figure 8. Analytical vs PLECS simulation waveforms for power flow at each port.

Figure 7 shows that the equations from the analyses accurately predict the behavior of the converter. By using the selected parameters, the current-fed port voltages  $v_2$  and  $v_3$  cannot be assumed to be square waveforms when the transformer leakage inductance value is close in magnitude to the mutual inductance values. It is also apparent that port voltages  $v_2$  and  $v_3$  are affected any time switching occurs at another port. Calculation of power flow through the

converter is done by applying the formula in (2-27). The resulting analytical power flow waveforms are shown in Figure 8 and confirmed with the power flow results from the simulation.

#### 2.4.1 **Discussions**

Looking at the comparison between analytical and simulation voltage waveforms in Figure 7, it is confirmed that the port voltage equations accurately describe the performance of the converter. Similarly, the equations for power flow at each port are confirmed with the simulation results in Figure 8. The peak power values as well as average power (shown in red) are equivalent between the analysis and the simulation. Note that it takes one switching period for the simulation to calculate average power (half a period in this instance, due to symmetry) thus in the case of the simulation, the average power is initially zero before a switching period elapses.

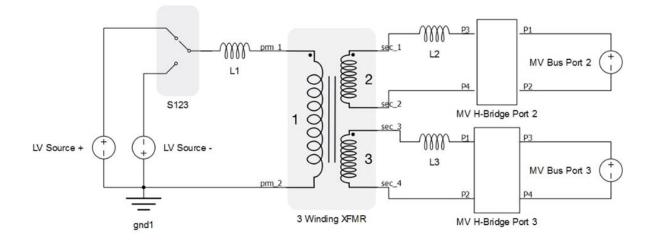

A key result of these analyses is that the current-fed port voltages  $v_2$  and  $v_3$  deviate from an ideal square wave as the mutual inductance values ( $L_{dc} - M$ ) are increased to values similar in magnitude to the transformer leakage inductances  $L_2$  and  $L_3$ . To explore this phenomenon further, the mutual inductance values ( $L_{dc} - M$ ) were varied between 1% and 200% of the transformer leakage inductance values  $L_2$  and  $L_3$ . Figure 9 shows how the selection of inductor values affects the port voltage waveforms and ultimately the performance of the converter.

Figure 9: Current-fed port voltage waveforms  $v_2$  and  $v_3$  with inductance ratios  $(L_{dc} - M)/L_x$  between 1% and 200% (from simulation).

When the mutual inductance values are 1% of the transformer leakage inductance values, the port voltage waveform is approximately a square wave (with zero states in accordance with the switching duty cycle). Due to the relatively short period of the zero states, each port voltage waveform can be approximated as an ideal square wave when computing power flow.

Therefore, when mutual inductance values are much lower than transformer leakage inductance values, the traditional power flow equations for voltage-fed multi-port converters as listed in [21] can be used. With the parameters listed in Table 2, power flow at the current-fed ports was computed and compared to the expected power flow from the voltage-fed power flow

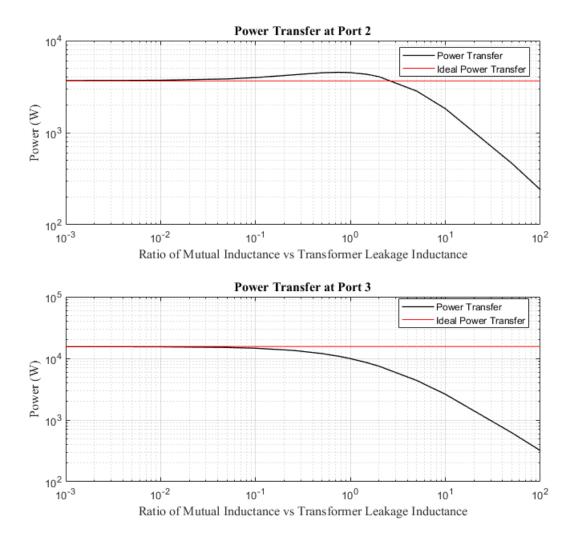

equations in [21]. The results shown in Figure 10 demonstrate that as the mutual inductance  $(L_{dc} - M)$  increases, the current-fed ports deliver less power than the "ideal power transfer" computed from the voltage-fed power flow equations.

Figure 10: Power transfer at current-fed ports with respect to the inductance ratios  $(L_{dc} - M)/L_x$  (from simulation).

The analyses establish characteristic equations for voltage, current, and power flow within a current-fed, multi-port converter. Waveforms were generated from the characteristic equations and confirmed with a PLECS simulation using circuit parameters from a reference experiment. Additionally, the validity of traditional power flow equations for a voltage-fed multi-port converter were tested against the performance of the current-fed, multi-port DAB converter. The results demonstrate that under certain conditions, a current-fed port's power flow can be controlled in the same manner as a voltage-fed port.

#### **2.5 Decoupled Control**

An operational concern with converters containing multi-winding transformers is that the shared flux within the transformer will cause a change in power flow for all 3 ports when the phase shift of a single port is changed. In an IEEE multiport converter seminar in 2021, Dr. Marco Liserre stated that a load change at a first load port creates unintended power fluctuations at a second load port. The aim of this section is to propose a control method that accounts for the coupled port behavior to maintain a constant power output while another port experiences a load change.

The contribution of this section is to harness the results of the power flow analysis to propose a control strategy based on the resulting power flow equations. Since a controller for the CFTAB converter has never been proposed before, this will be a novel controller. The critical feature of the proposed control is that transient power flow conditions at one of the load ports do not affect the power flow performance at the second load port. This is because the coupled flux effects within the multi-winding transformer are predicted from the power flow analysis and compensation is incorporated within the controller. This control compensation is useful when significant load changes can create voltage disturbances at the other 2 dc ports, particularly in the case of weak grid systems like an islanded microgrid [33]. In electric vehicle applications as well, it is an important controller design metric to shield the battery port from transient disturbances [34]. Traditionally, a decoupling matrix is used to prevent transient disturbances. However, this method requires linearization around an operating point to derive the decoupling gain matrices. The proposed control strategy will be able to achieve decoupled performance without the need to re-calculate the control laws as the operating point changes.

## 2.5.1 Average Power Flow Control Case Study

Deriving the power flow equations makes it possible to compute the valid operating points of  $(\phi_2, \phi_3)$  that will deliver a constant power output at one of the ports. Then, a trajectory of these operating points can be discovered to allow the other port to adjust power flow while maintaining constant power at the original port. To demonstrate this concept, a case study will be explored using the parameters in Table 1 for a constant 5kW load at port 3.

The circuit component values in Table 1 were substituted into (2-32)-(2-56) and the resulting power output waveforms at each port are plotted in Figure 11 for the full switching range for  $-0.5 \le \phi_2 \le 0.5$  and  $-0.5 \le \phi_3 \le 0.5$ . The eight different modes are colored separately in the graphs to clearly show each mode. A key feature to note is that the power output at a port x trends from negative to positive for the range  $-0.25 \le \phi_x \le 0.25$ , regardless of the phase shift at the other port. This is to be expected as a typical control strategy is to independently control each port by increasing its phase shift to increase power flow to that port, and vice versa. A key result of any change in phase shift, however, is a clear change in power output at both ports. For example, if an increase at port 2 power flow is desired and  $\phi_2$  is increased accordingly, the power output at port 3 will certainly change as a result. The following section of this paper will describe a method of adjusting the power output at one port without affecting the power output at the other

port. As a reminder, the power output at port 1 is simply equal to the sum of the power flow to ports 2 and 3 as described in (2-2). Therefore, the power output at port 1 is also controlled by manipulating  $\phi_2$  and  $\phi_3$ .

Note that in Figure 11, the highlighted operating points (dark black) are in a flat plane at 5kW for port 3 output power while the trajectory of port 2 output power can range from approximately -10kW to 10kW. It can also be noted that the control strategy can be simplified further by restricting the operating points to  $-0.25 \le \phi_2 \le 0.25$  and  $-0.25 \le \phi_3 \le 0.25$  to force proportional control. This means the power output at port 2 increases as the phase angle  $\phi_2$  is increased (and vice versa), which makes standard feedback control well-suited to regulating the power output at Port 2 by regulating  $\phi_2$ . The phase shift  $\phi_3$  can then be computed from  $\phi_2$  to achieve a constant 5kW power output at port 3.

Figure 11: Power output at port 2 across the entire operating range (−0.5 ≤ φ<sub>2</sub> ≤ 0.5 and −0.5 ≤ φ<sub>3</sub> ≤ 0.5) (top) and Power output at port 3 across the entire operating range (bottom). Each distinct color corresponds to one of the eight operating modes as described in Table II. Port 2 and port 3 power output with 5kW power reference at port 3. Valid operating points that output 5kW at port 3 are highlighted in dark black. Note that at port 2, the power output can equal zero near the origin with power output increasing or

decreasing according to the phase angle  $\phi_2$ .

# Solving for $\phi_3$ :

A relationship between the phase shifts  $\phi_2$  and  $\phi_3$  can be computed by substituting 5kW into (2-38) for Mode 2 and is given in (2-57).

$$5000 = 78125 \left( -\phi_2^2 - \frac{1}{2}\phi_2 - 3\phi_3^2 + \frac{3}{2}\phi_3 + 2\phi_2\phi_3 \right)$$

(2-58)

Then, solving for  $\phi_3$ :

$$\phi_3 = -\phi_2 \pm \frac{1}{250} \sqrt{125000\phi_2^2 - 125000\phi_2 + \frac{124625}{4} + \frac{3}{4}}$$

(2-59)

From (2-58), a constant power output of 5kW is produced at port 3 regardless of the value of  $\phi_2$ . As  $\phi_2$  changes,  $\phi_3$  will be computed accordingly to maintain the desired output of  $P_3$

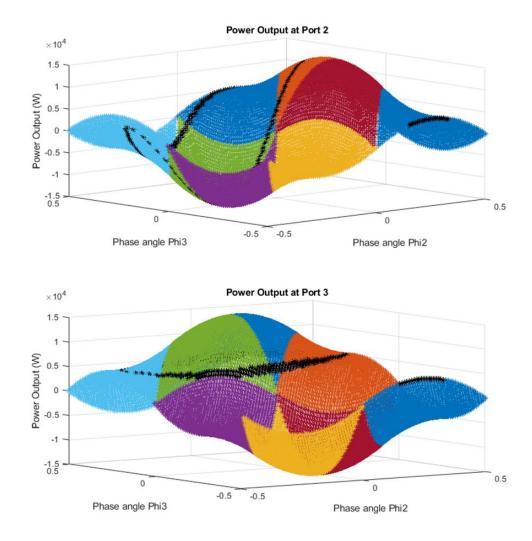

## 2.5.2 Control Hardware-in-the-Loop Experiment