Dynamic Performance Improvement of Non-Isolated DC-DC converters and PV Energy Harvesting Systems using One Step Finite Control Set Model Predictive Control coupled with geometrical domain analysis

### **Thibaut Harzig**

B.S. in Electrical Engineering, National Institute of Applied Sciences, 2016

M.S. in Electrical Engineering, University of Pittsburgh, 2019

Submitted to the Graduate Faculty of the

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2022

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

#### **Thibaut Harzig**

It was defended on

June 21, 2022

and approved by

Nikhil Bajaj, PhD, Assistant Professor, Department of Mechanical Engineering and Materials Science

Robert Kerestes, PhD, Assistant Professor, Department of Electrical and Computer Engineering

Zhi-Hong Mao, PhD, Professor, Department of Electrical and Computer Engineering

Alexis Kwasinski, PhD, Associate Professor, Department of Electrical and Computer Engineering

Dissertation Director: Brandon Grainger, PhD, Assistant Professor, Department of Electrical and Computer Engineering Copyright © by Thibaut Harzig

2022

#### Dynamic Performance Improvement of Non-Isolated DC-DC converters and PV Energy Harvesting Systems using One Step Finite Control Set Model Predictive Control coupled with geometrical domain analysis Thibaut Harzig, PhD

University of Pittsburgh, 2022

The proposed research project uses the well-documented Model Predictive Control (MPC) framework to improve the dynamic performance of power converters and differential power processing (DPP) architecture with the help of geometrical domain analysis. The first research task is to implement a One Step Finite Control Set MPC (FCS-MPC) for a DC-DC boost converter. In the proposed control scheme, the cost function is built using time-optimal trajectories of the boost converter to solve the convergence issue brought by the non-minimum phase behavior of this system. The constraint of the proposed FCS-MPC limits important voltage deviations when using time-optimal trajectories. The second research task aims at proposing a generalized One Step FCS-MPC for the most common Non-Isolated DC-DC converters (buck boost and buck-boost). The proposed control scheme uses a unified switching model of nonisolated DC-DC converters and adapts the existing time-optimal boundary controllers to the FCS-MPC framework. The contributions are the avoidance of non-minimum phase issues, the limitation of voltage deviation and current spikes, and the possibility to target a specific steady state switching frequency. The third research task involves the implementation of FCS-MPC control schemes for the Differential Power Processing (DPP) PV-bus direct architecture. In this architecture a bidirectional Flyback is connected in parallel with each PV panel to operate a maximum power point tracking (MPPT). This system incorporates a string converter controlling the PV string current minimizing the power processed by bidirectional Flyback converters with a Least Power Point Tracking (LPPT) algorithm. In this research task the classical direct duty cycle control MPPT is replaced by a FCS-MPC MPPT using geometrical domain analysis. The classical LPPT implemented with PI controllers is replaced by a FCS-MPC where the cost function is the power processed by the bidirectional flyback converters. The benefit is to avoid interactions between LPPT and MPPTs with an increase in the control dynamic performance. Overall, the proposed set of control schemes improves the minimization of power stress on bidirectional Flyback converters.

# **Table of Contents**

| Dynamic Performance Improvement of Non-Isolated DC-DC converters and PV                |

|----------------------------------------------------------------------------------------|

| Energy Harvesting Systems using One Step Finite Control Set Model Predictive           |

| Control coupled with geometrical domain analysisi                                      |

| Nomenclature xix                                                                       |

| Acknowledgement xxi                                                                    |

| 1.0 Introduction1                                                                      |

| 1.1 Background1                                                                        |

| 1.1.1 Emergence of Model Predictive Control in Power Electronics and Power             |

| Systems1                                                                               |

| 1.1.2 Existing Predictive Controllers applied to Power Converters and Drives2          |

| 1.2 Classification of Model Predictive Controls used in Power Electronics and Drives 3 |

| 1.3 Basic Principles of FCS-MPC7                                                       |

| 1.3.1 Internal dynamic model8                                                          |

| 1.3.2 Minimization of the Cost Function and Receding horizon policy9                   |

| 1.3.3 FCS-MPC Constraints10                                                            |

| 1.4 Contribution11                                                                     |

| 1.5 Thesis Organization12                                                              |

| 2.0 Research Task #1-FCS-MPC for a DC-DC Boost Converter Ensuring Time                 |

| Optimal regulation and Controlled Output Voltage Deviation                             |

| 2.1 Literature Review and Motivation13                                                 |

| 2.2 Boost Converter Normalization and Discrete Relationships15                         |

| 2.3 Dynamic Performance indices for boost converter                             | 18 |

|---------------------------------------------------------------------------------|----|

| 2.3.1 Voltage Deviation Performance Indices                                     | 19 |

| 2.3.2 Recovery Time Performance Indices                                         | 20 |

| 2.4 Time Optimal Boundary Control using NSS                                     | 21 |

| 2.5 Proposed Finite Control Set Model Predictive Control based on NSS tracking  | 23 |

| 2.5.1 NSS Tracking Cost Function for Time Optimal Control                       | 24 |

| 2.5.2 Constraints of the proposed FCS-MPC                                       | 27 |

| 2.6 Simulation Results                                                          | 29 |

| 2.7 Limitations                                                                 | 33 |

| 3.0 Research Task #2-Unified FCS-MPC for non-isolated Synchronous DC-DC         |    |

| converter ensuring Time Optimal regulation, controlled output voltage deviation |    |

| and inductor current overshoot                                                  | 35 |

| 3.1 Literature Review and Motivation                                            | 35 |

| 3.2 Generalized Predictive Model and Natural Switching Surfaces                 | 35 |

| 3.3 Dynamic Performance indices for Voltage Regulation of Non-Isolated DC-D     | )C |

| Converters                                                                      | 39 |

| 3.3.1 Buck Converter                                                            | 39 |

| 3.3.1.1 Voltage Deviation Performance Indices                                   | 40 |

| 3.3.1.2 Recovery Time Performance Indices                                       | 41 |

| 3.3.2 Boost Converter                                                           | 43 |

| 3.3.2.1 Voltage Deviation Performance Indices                                   | 43 |

| 3.3.2.2 Recovery Time Performance Indices                                       | 44 |

| 3.3.3 Buck-boost Converter                                                      | 46 |

| 3.3.3.1 Voltage Deviation Performance Indices                             |

|---------------------------------------------------------------------------|

| 3.3.3.2 Recovery Time Performance Indices 48                              |

| 3.4 Generalized Formulation of Time Optimal Boundary Control using NSS 50 |

| 3.4.1 Generalized Control Laws51                                          |

| 3.4.2 Steady-State Characteristics with linear ON Natural Trajectory52    |

| 3.4.3 Steady-State Characteristics with circular ON Natural Trajectory53  |

| 3.5 Proposed Generalized Finite Control Set Model Predictive Control 55   |

| 3.5.1 Cost Function for time optimal regulation with linear ON Natural    |

| Trajectory55                                                              |

| 3.5.2 Cost Function for time optimal regulation with circular ON Natural  |

| Trajectory56                                                              |

| 3.5.3 Current Constraint57                                                |

| 3.5.4 Voltage Constraint57                                                |

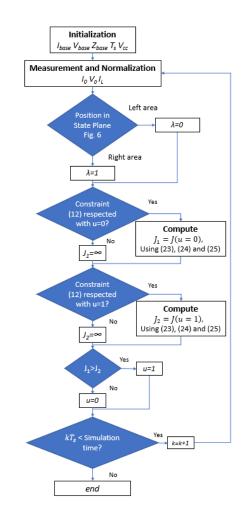

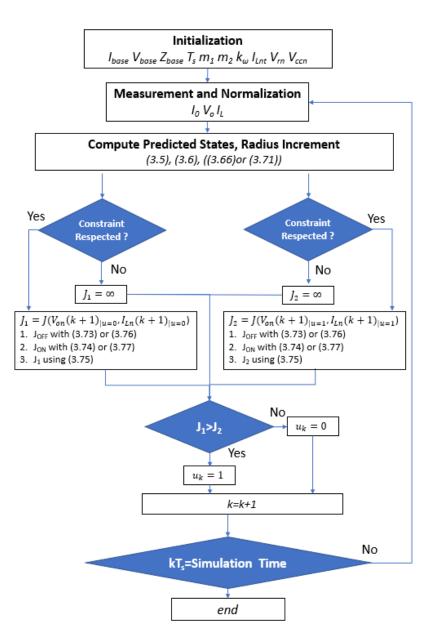

| 3.5.5 Steps of the Proposed FCS-MPC58                                     |

| 3.6 Simulation Results 60                                                 |

| 3.6.1 DC-DC Buck Converter60                                              |

| 3.6.2 DC-DC Boost Converter                                               |

| 3.6.3 DC-DC Buck-Boost Converter68                                        |

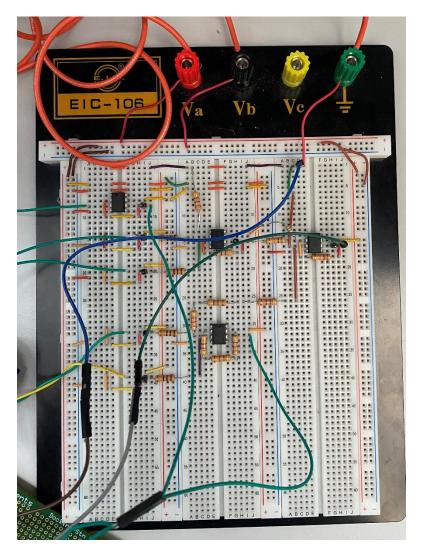

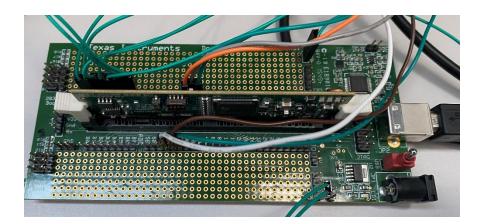

| 3.7 Control Hardware in-the-Loop Experiment Results                       |

| 3.7.1 Buck Converter74                                                    |

| 3.7.2 Boost Converter79                                                   |

| 3.7.3 Buck-Boost Converter83                                              |

| 3.8 Sensitivity of Converter and Proposed FCS-MPC parameters              |

| <b>3.8.1</b> Sensitivity of the inductance L on control performance                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.8.2 Sensitivity of the Capacitance C on control performance                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                     |

| 3.8.3 Impact of input voltage V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90                                     |

| 3.8.4 Impact of sampling Period T <sub>s</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                     |

| 3.8.5 Maximum Target Switching Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92                                     |

| 3.8.6 Impact of delay on control decision application                                                                                                                                                                                                                                                                                                                                                                                                                                | 92                                     |

| 3.9 Experiment on Synchronous Buck Converter                                                                                                                                                                                                                                                                                                                                                                                                                                         | <del>)</del> 3                         |

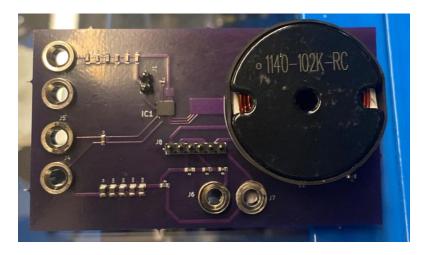

| 3.9.1 PCB Layout of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                               | 93                                     |

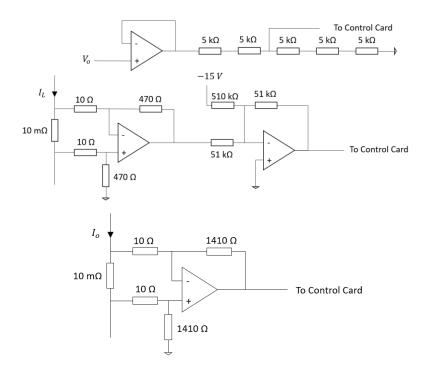

| 3.9.2 I/O Interface of the control card                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96                                     |

| 3.9.3 Experiment Results                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98                                     |

| 4.0 Research Task #3-Improvement of Maximum Power Point Tracking(MPPT)                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| and Least Power Point Tracking (LPPT) dynamic performances in DPP                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| and Least Power Point Tracking (LPPT) dynamic performances in DPP architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                         | )2                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| architecture using FCS-MPC10                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                     |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02                               |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02<br>05                         |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02<br>05<br>05                   |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02<br>05<br>05                   |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02<br>05<br>05<br>07<br>09       |

| architecture using FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 02<br>02<br>05<br>05<br>07<br>09       |

| architecture using FCS-MPC       10         4.1 Literature Review and Motivation       10         4.1.1 Benefits of PV Differential Power Processing       10         4.1.2 Comparison of series DPP architectures       10         4.1.2.1 Series PV-PV DPP       10         4.1.2.2 Series PV-bus and PV-bus direct architecture       10         4.1.2.3 Serie PV-Isolated Port architecture       10         4.1.2.4 Discussion on the choice of serie DPP architecture       11 | D2<br>D2<br>D5<br>D5<br>D7<br>D9<br>10 |

| 4.2.2 String Converter achieving LPPT                        | 114 |

|--------------------------------------------------------------|-----|

| 4.2.3 Interactions between MPPT and LPPT                     | 116 |

| 4.3 One Step FCS-MPC MPPT of bidirectional Flyback Converter | 117 |

| 4.3.1 Flyback Converter Normalization                        | 117 |

| 4.3.2 Proposed Cost Function for Natural Trajectory Tracking | 120 |

| 4.3.3 Proposed FCS-MPC Maximum Power Point Tracking          | 121 |

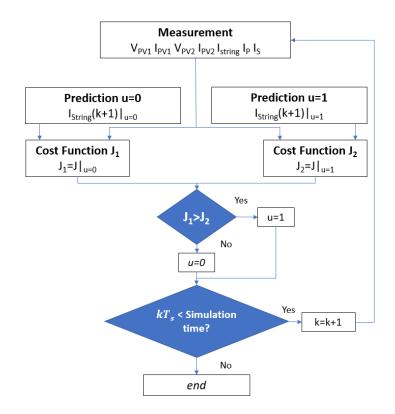

| 4.4 One Step FCS-MPC of Boost Converter                      | 123 |

| 4.5 Simulation Results                                       |     |

| 5.0 Conclusion and Future Work                               | 130 |

| Bibliography                                                 |     |

## List of Tables

| Table 1: Parameters of the unified predictive model            | 36 |

|----------------------------------------------------------------|----|

| Table 2: Simulation Parameters of DPP Architecture under Study | 25 |

# List of Figures

| Figure 1: Evolution of Digital Hardware Processing Power in Million of Instruction Per         |

|------------------------------------------------------------------------------------------------|

| Seconds (MIPS) [1]                                                                             |

| Figure 2: Evolution of annual MPC-related peer reviewed publications appearing in IEEE         |

| Xplore since 2000 (related to power electronic systems)                                        |

| Figure 3: Classification of most common control schemes for power converters and drives        |

| [1], [6]                                                                                       |

| Figure 4: Classification of Model Predictive Controllers                                       |

| Figure 5: Indirect Control Scheme                                                              |

| Figure 6: Direct Control Scheme                                                                |

| Figure 7: DC-DC boost converter 16                                                             |

| Figure 8:ON and OFF natural switching surfaces of the boost converter                          |

| Figure 9: Time optimal trajectories for start-up (a), loading (b) and unloading (c) transient. |

|                                                                                                |

| Figure 10: State plane representation of control laws from [14]                                |

| Figure 11: Ideal trajectories for MTC in state-plane domain for (a) start-up transient, (b)    |

| loading transient and (c) unloading transient                                                  |

| Figure 12: Lambda mapping when Io increases (a) or decreases (b) at t=026                      |

| Figure 13: Proposed FCS-MPC Flowchart                                                          |

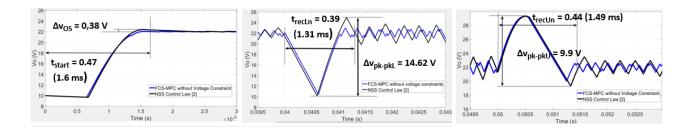

| Figure 14: Simulation Results of the converter start-up transient (left) loading transient     |

| (center) and unloading transient (right) in the time domain using NSS control Laws             |

| of [6] (black) and proposed FCS-MPC without voltage constraint (blue))                         |

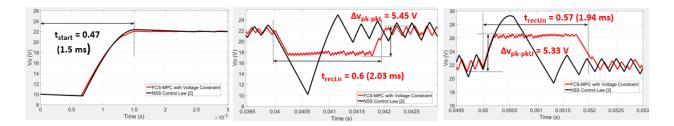

| Figure 15: Simulation Results of the converter start-up transient (left) loading transient |

|--------------------------------------------------------------------------------------------|

| (center) and unloading transient (right) in the time domain using NSS control laws         |

| of [6] (black) and proposed FCS-MPC with voltage constraint (red)                          |

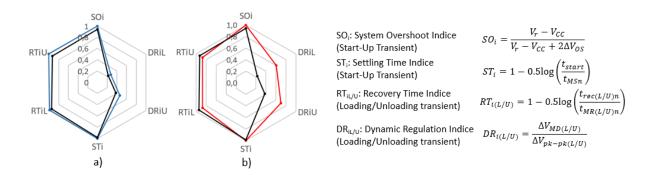

| Figure 16: Benchmarking indices of (a) NSS control laws (black) compared with proposed     |

| FCS-MPC without voltage constraint (blue) and (b) NSS control laws (black)                 |

| compared with proposed FCS-MPC with Voltage Constraint (red)                               |

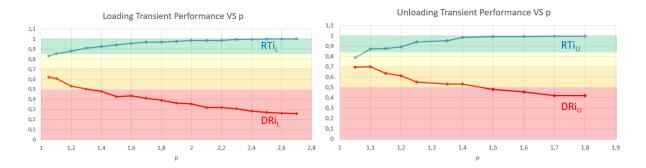

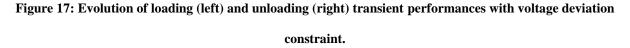

| Figure 17: Evolution of loading (left) and unloading (right) transient performances with   |

| voltage deviation constraint                                                               |

| Figure 18: Evolution of loading (left) and unloading (right) transient performances with   |

| sampling period (p=1.05)                                                                   |

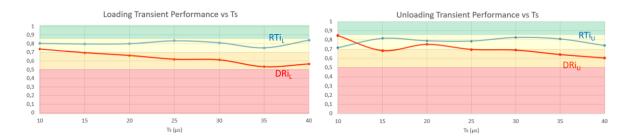

| Figure 19: Impact of Vccn on the Settling Time Performance Index                           |

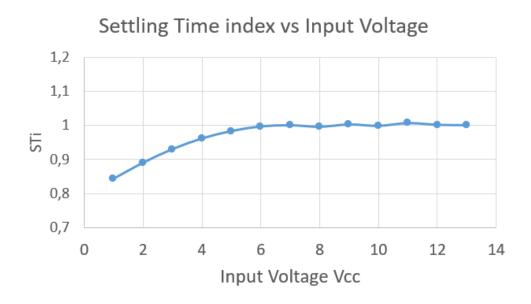

| Figure 20: DC-DC buck (a), boost (b) and buck-boost (c) converter                          |

| Figure 21: Load Line (Black), OFF (red) and ON (blue) Natural trajectory for buck (a),     |

| boost (b) and buck-boost (c)                                                               |

| Figure 22:Buck Converter time optimal trajectories for start-up (a), loading (b) and       |

| Figure 22. Duck Converter time optimal trajectories for start-up (a), loading (b) and      |

| unloading (c) transient                                                                    |

|                                                                                            |

| unloading (c) transient                                                                    |

| unloading (c) transient                                                                    |

| unloading (c) transient                                                                    |

| <ul> <li>unloading (c) transient</li></ul>                                                 |

| unloading (c) transient                                                                    |

| Figure 27: Evolution of Buck converter States and control actions when Time Optimal   |

|---------------------------------------------------------------------------------------|

| Boundary Control of [18]-[19] is applied61                                            |

| Figure 28: Evolution of Buck converter States and control actions when proposed FCS-  |

| MPC without Voltage Constraint is applied61                                           |

| Figure 29: Evolution of Buck converter States and control actions when proposed FCS-  |

| MPC with current Constraint is applied                                                |

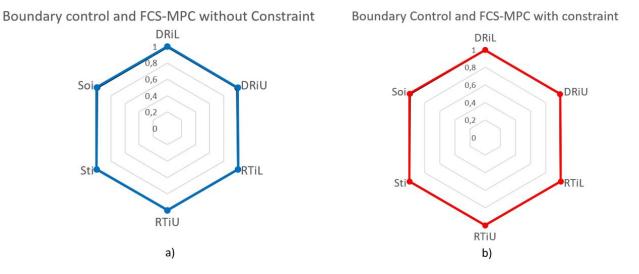

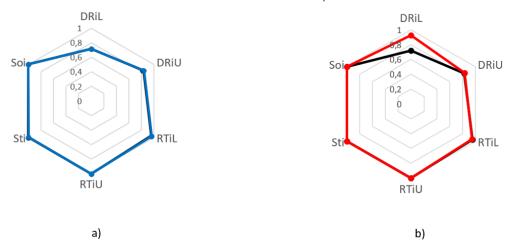

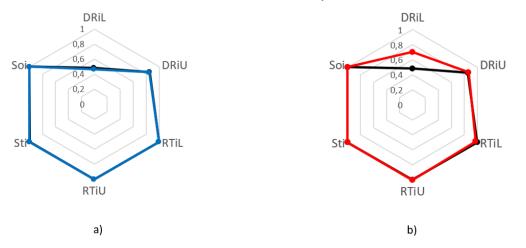

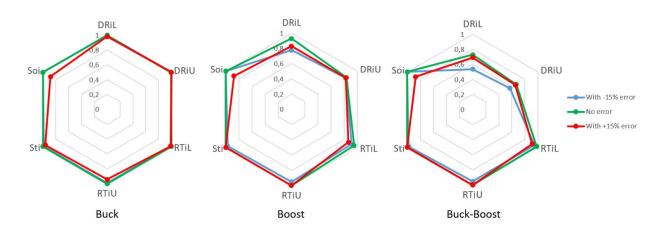

| Figure 30: Benchmarking indices of (a) Time Optimal Boundary control laws (black)     |

| compared with proposed FCS-MPC without current constraint (blue) and (b) Time         |

| Optimal Boundary control laws (black) compared with proposed FCS-MPC with             |

| current Constraint (red)63                                                            |

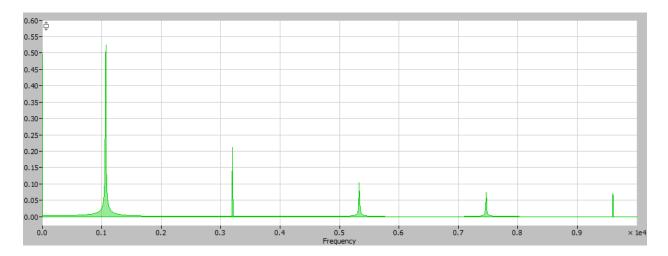

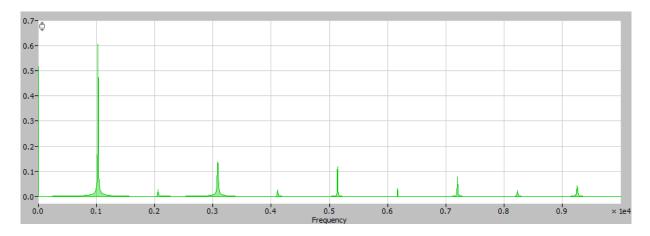

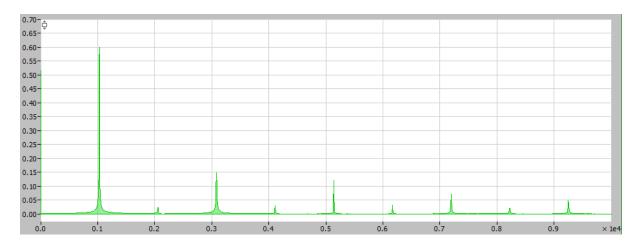

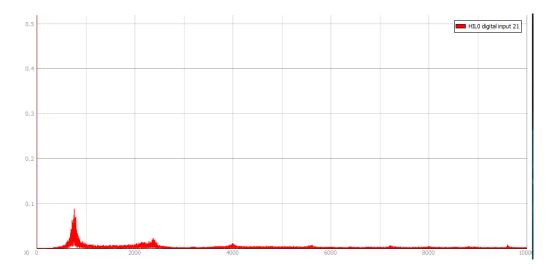

| Figure 31: Fourier Analysis of the Gate signal for Buck Converter                     |

| Figure 32: Evolution of Boost converter States and control actions when Time Optimal  |

| Boundary Control of [14] is applied65                                                 |

| Figure 33: Evolution of Boost converter States and control actions when proposed FCS- |

| MPC without voltage constraint is applied65                                           |

| Figure 34: Evolution of Boost converter States and control actions when proposed FCS- |

| MPC with voltage constraint is applied                                                |

| Figure 35:Benchmarking indices of (a) Time Optimal Boundary control laws (black)      |

| compared with proposed FCS-MPC without voltage constraint (blue) and (b) Time         |

| Optimal Boundary control laws (black) compared with proposed FCS-MPC with             |

| Voltage Constraint (red)67                                                            |

| Figure 36: Fourier Analysis of the Gate signal for Boost Converter                    |

| Figure 37:Evolution of Buck-Boost converter States and control actions when Time          |

|-------------------------------------------------------------------------------------------|

| Optimal Boundary Control of [20] is applied69                                             |

| Figure 38: Evolution of Buck-Boost converter States and control actions when proposed     |

| FCS-MPC without voltage constraint is applied                                             |

| Figure 39: Evolution of Buck-Boost converter States and control actions when proposed     |

| FCS-MPC with voltage constraint is applied70                                              |

| Figure 40: Benchmarking indices of (a) Time Optimal Boundary control laws (black)         |

| compared with proposed FCS-MPC without voltage constraint (blue) and (b) Time             |

| Optimal Boundary control laws (black) compared with proposed FCS-MPC with                 |

| Voltage Constraint (red)71                                                                |

| Figure 41: Fourier Analysis of the Gate signal for Buck-Boost Converter                   |

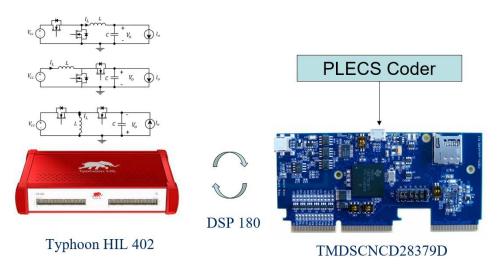

| Figure 42: Hardware-in-the-Loop (HIL) simulation of a non-isolated dc-dc converter with   |

| the proposed FCS-MPC73                                                                    |

| Figure 43: Experimental setup for the Control Hardware-in-the-Loop simulation             |

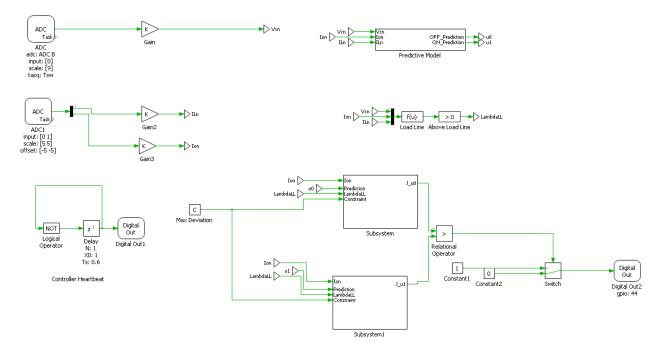

| Figure 44: Proposed FCS-MPC for the boost converter on PLECS CODER                        |

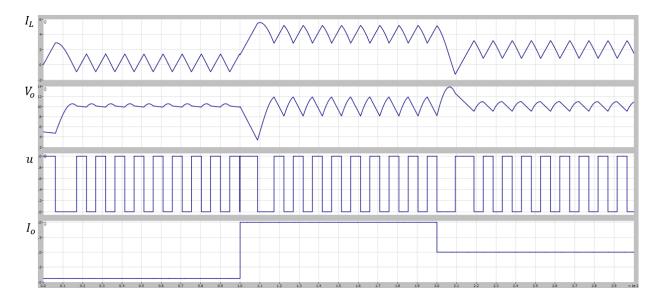

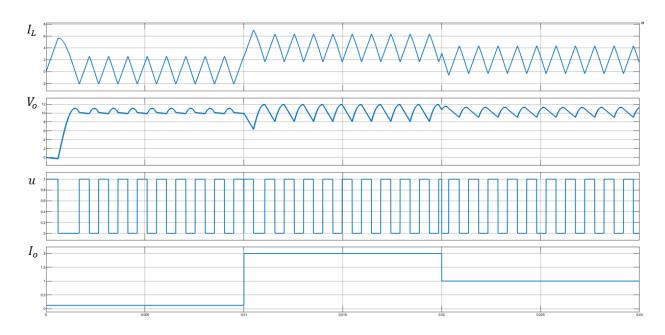

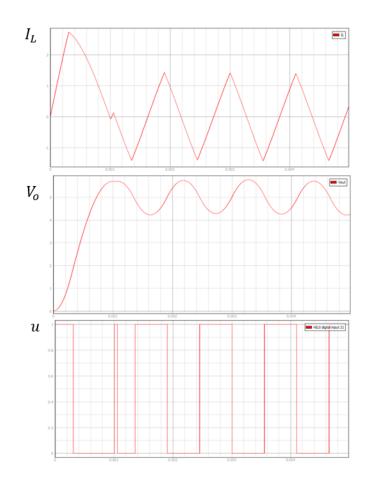

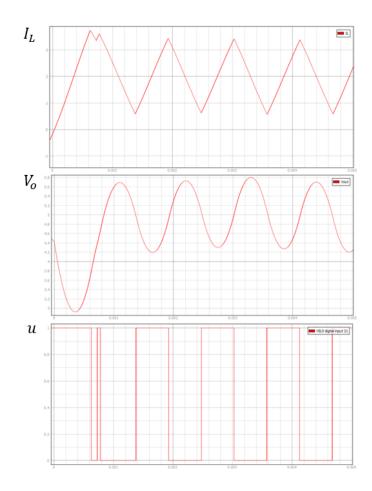

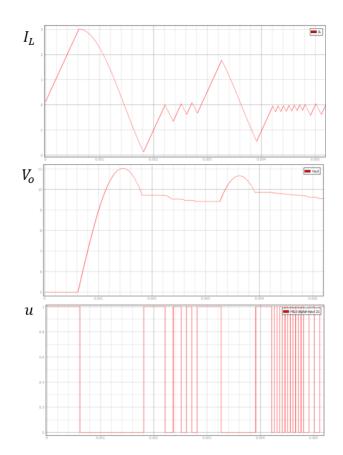

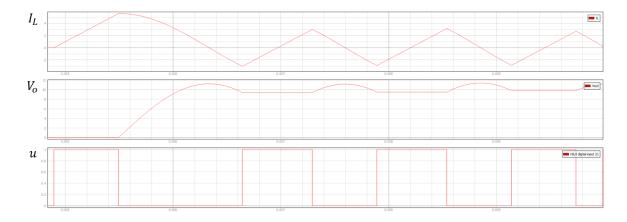

| Figure 45: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the buck |

| converter under start-up transient75                                                      |

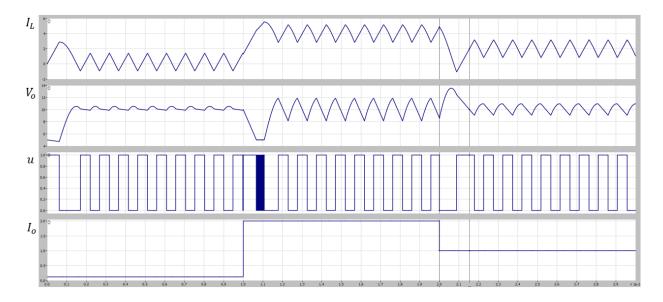

| Figure 46: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the buck |

| converter under loading transient                                                         |

| Figure 47: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the buck |

| converter under unloading transient77                                                     |

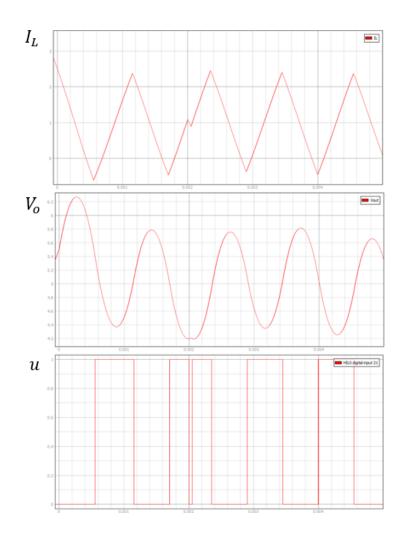

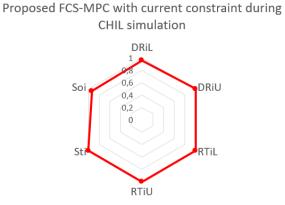

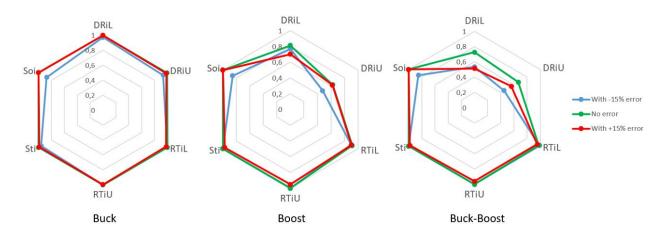

| Figure 48: Benchmarking indices of proposed FCS-MPC with Current Constraint for Buck      |

|                                                                                           |

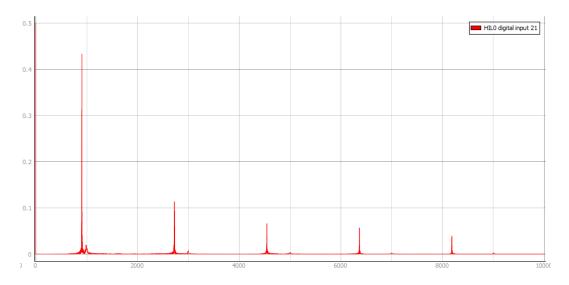

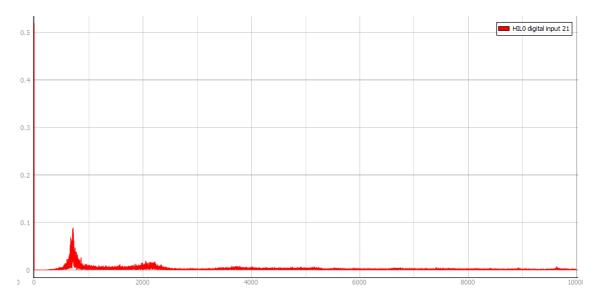

| Figure 49: Fourier Analysis of the Gate signal for Buck Converter                                              |

|----------------------------------------------------------------------------------------------------------------|

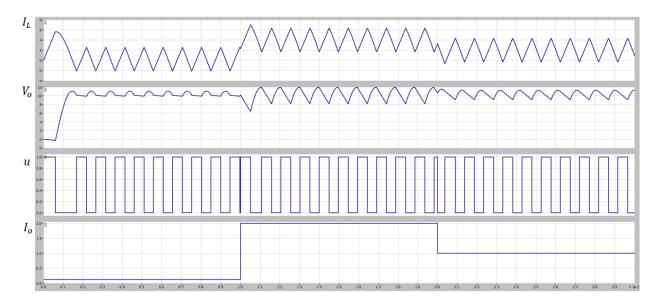

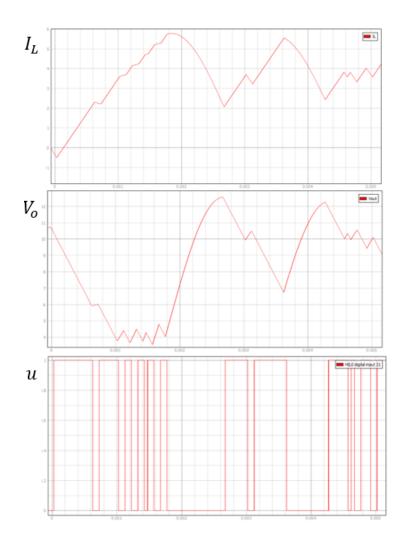

| Figure 50: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the boost                     |

| converter under start-up transient79                                                                           |

| Figure 51: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the boost                     |

| converter under loading transient 80                                                                           |

| Figure 52: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the boost                     |

| converter under unloading transient                                                                            |

| Figure 53: Benchmarking indices of proposed FCS-MPC with Voltage Constraint for Boost                          |

|                                                                                                                |

| Figure 54: Fourier Analysis of the Gate signal for Boost Converter                                             |

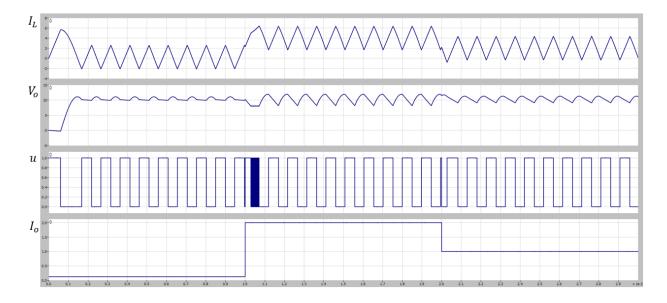

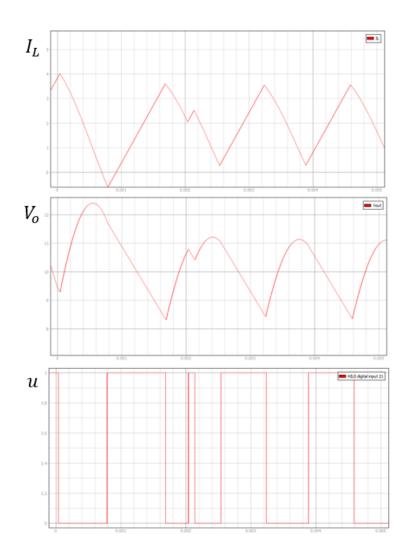

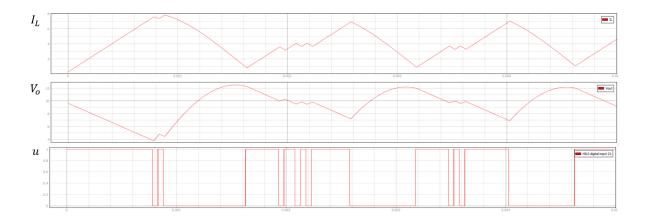

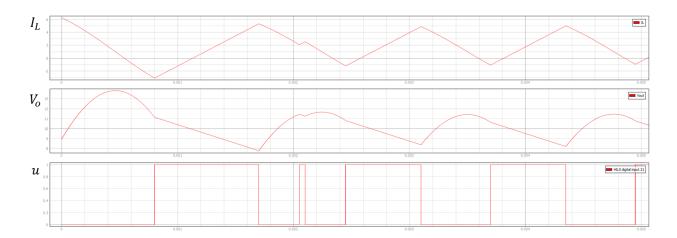

| Figure 55: CHIL simulation result of $IL$ (top), $Vo$ (middle) and $u$ (left) of the buck                      |

| converter under start-up transient                                                                             |

| Figure 56: CHIL simulation result of <i>IL</i> (top), <i>Vo</i> (middle) and <i>u</i> (left) of the buck-boost |

| converter under loading transient                                                                              |

| Figure 57: CHIL simulation result of <i>IL</i> (top), <i>Vo</i> (middle) and <i>u</i> (left) of the buck-boost |

| converter under unloading transient                                                                            |

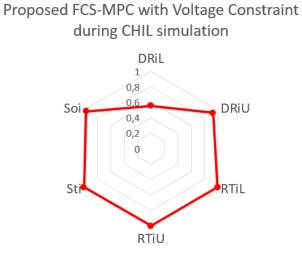

| Figure 58: Benchmarking indices of proposed FCS-MPC with Voltage Constraint for                                |

| Buck-Boost                                                                                                     |

| Figure 59: Fourier Analysis of the Gate signal for Buck-Boost Converter                                        |

| Figure 60: Dynamic Performance indices of DC-DC converters with variations in L                                |

| Figure 61: Dynamic Performance indices of DC-DC converters with variations in C 89                             |

|                                                                                                                |

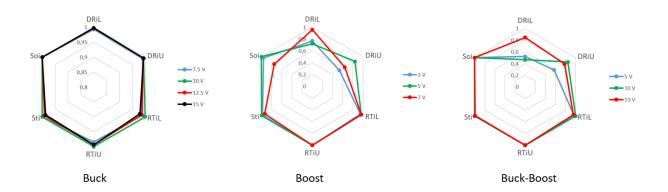

| Figure 62: Dynamic Performance indices of DC-DC converters with different values of                            |

| Figure 63: Dynamic Performance indices of DC-DC converters with different values of    |

|----------------------------------------------------------------------------------------|

| sampling period91                                                                      |

| Figure 64: Dynamic Performance indices of DC-DC converters with different values of    |

| sampling period92                                                                      |

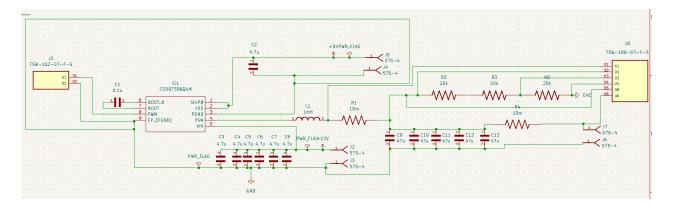

| Figure 65: Schematic of the experimental buck converter developed in KiCad             |

| Figure 66: BOM used for the assembly of buck converter                                 |

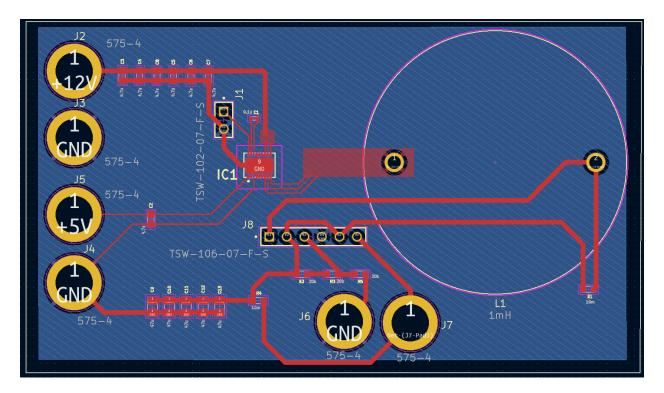

| Figure 67: Buck converter Layout in KiCad95                                            |

| Figure 68: Buck Converter design                                                       |

| Figure 69: Schematic of the scaling and offset of buck converter measurements          |

| Figure 70:Implementation of measurement scaling and offset                             |

| Figure 71: Docking Station USB-EMU R3                                                  |

| Figure 72: Proposed FCS-MPC of the buck converter                                      |

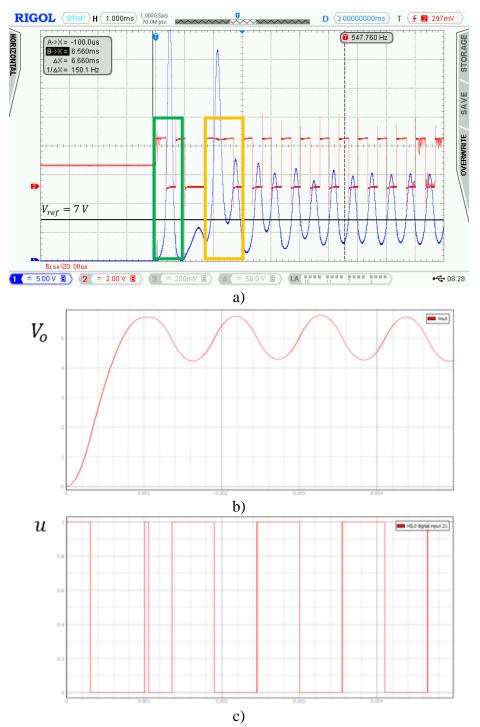

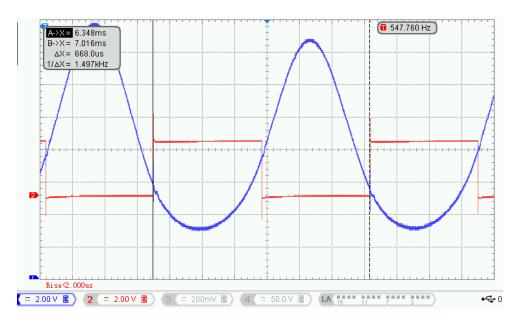

| Figure 73: Output voltage and gate signal comparison between hardware (a) and CHIL     |

| platform (b and c)                                                                     |

| Figure 74: Steady-state behavior of gating signals (red) and Output Voltage (blue) 101 |

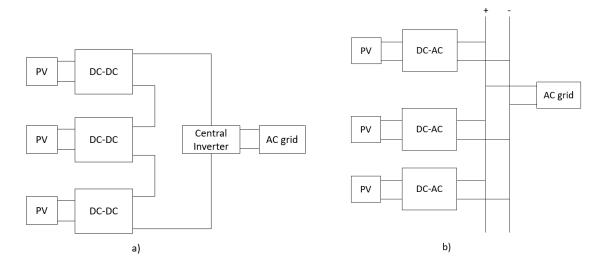

| Figure 75: series PV connected with a central inverter                                 |

| Figure 76:FPP DC optimizers (a) and module integrated inverters (or microinverter) 103 |

| Figure 77: Conceptual idea of Parallel DPP architecture 104                            |

| Figure 78: Conceptual idea of series DPP architectures 105                             |

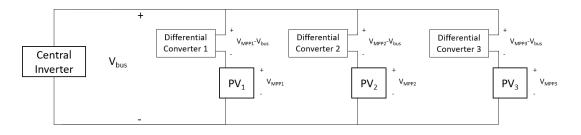

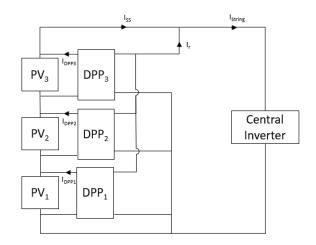

| Figure 79: Series PV-PV DPP architecture 106                                           |

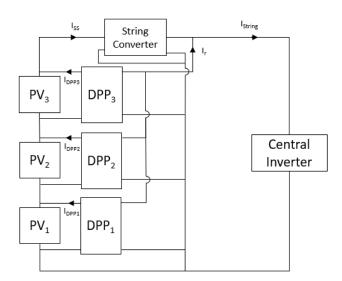

| Figure 80: Series PV-bus DPP architecture 107                                          |

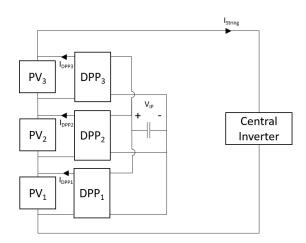

| Figure 81: Series PV-bus direct DPP architecture 108                                   |

| Figure 82: Series PV-IP DPP architecture                                               |

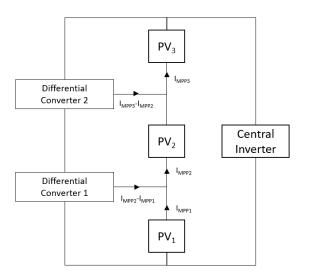

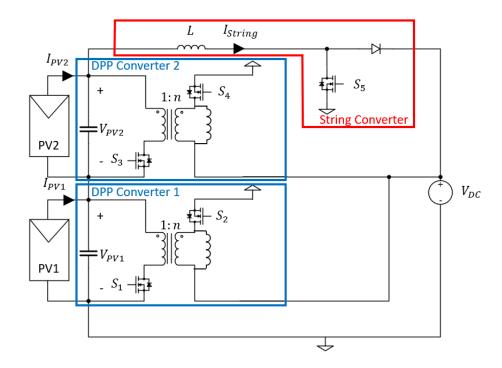

| Figure 83: Detailed Schematic of the DPP PV-bus direct architecture under study 111     |

|-----------------------------------------------------------------------------------------|

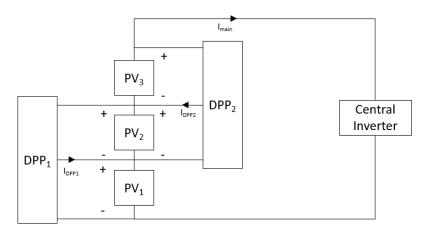

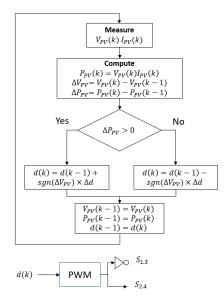

| Figure 84:Direct Duty Cycle Control Maximum Power Point Tracking (MPPT) using           |

| Perturb and Observe (P&O)113                                                            |

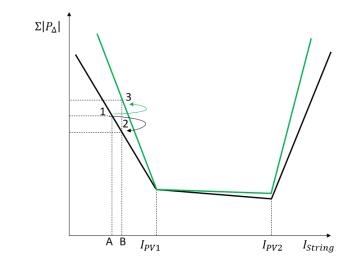

| Figure 85: Evolution of Power Processed by DPP converters Waveform when VPV1 is         |

| increased115                                                                            |

| Figure 86: Perturb and Observe (P&O) Least Power Point Tracking (LPPT) 115              |

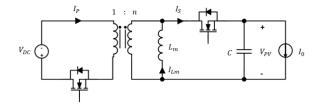

| Figure 87: Bidirectional Flyback Converter 117                                          |

| Figure 88: ON and OFF natural switching surfaces of the bidirectional Flyback converter |

|                                                                                         |

| Figure 89:Target ON (blue) and OFF (red) Natural trajectories and lambda mapping in     |

| the state-plane for a given $V_{\rm ref}$                                               |

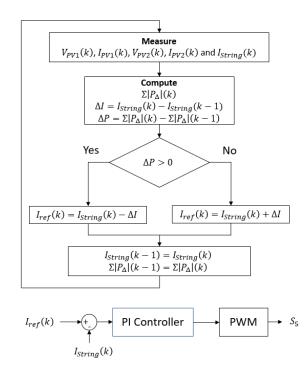

| Figure 90: Proposed FCS-MPC MPPT Flowchart 122                                          |

| Figure 91: Proposed Boost FCS-MPC Flowchart124                                          |

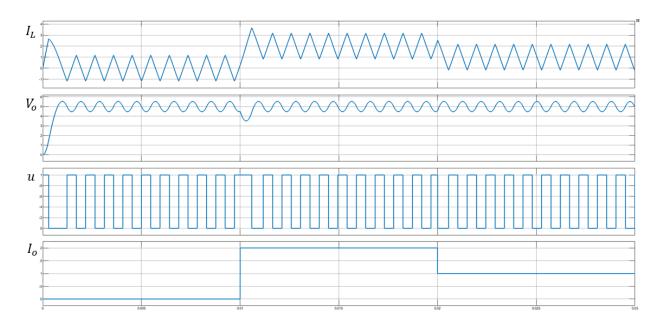

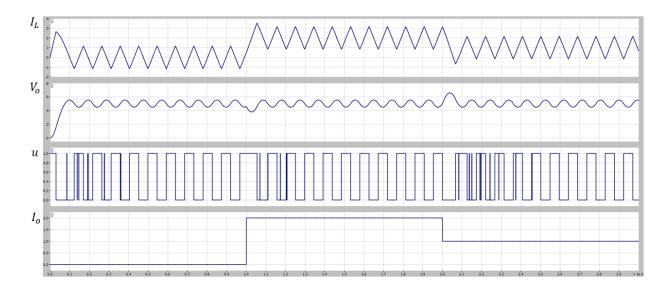

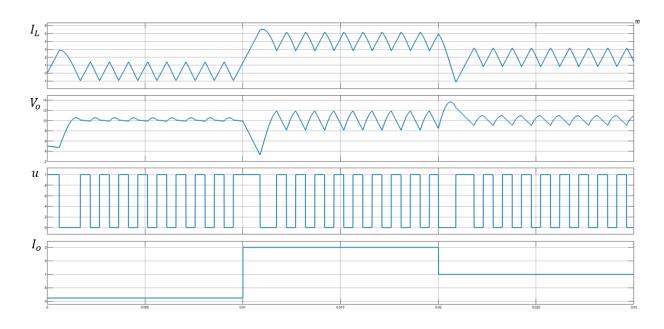

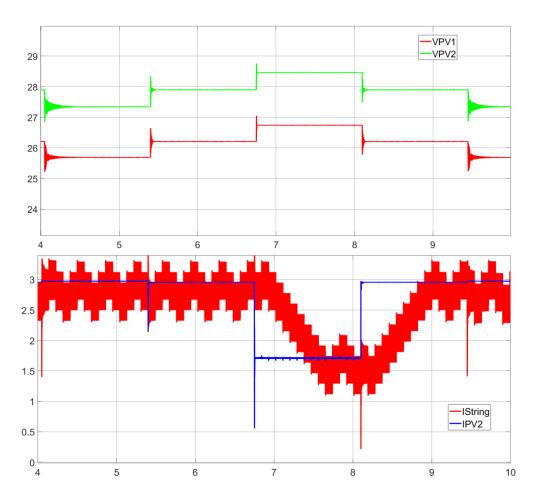

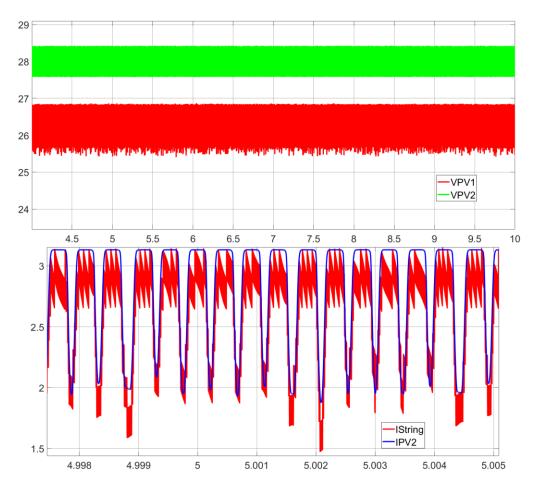

| Figure 92: Steady State Operation of Classical MPPT (top) and LPPT (bottom) 126         |

| Figure 93: Steady State Operation of proposed FCS-MPC MPPT (top) and boost converter    |

| FCS-MPC (bottom)127                                                                     |

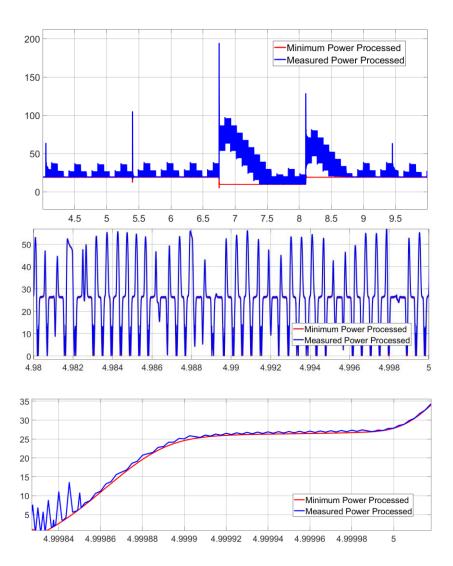

| Figure 94: Comparison of Measured and Minimum Processed Power by DPP converters         |

| using classical control schemes (top) and control schemes (middle) (zoomed-in           |

| (bottom))                                                                               |

# Nomenclature

| CCS-MPC           | Continuous Control Step Model Predictive Control    |

|-------------------|-----------------------------------------------------|

| DPP               | Differential Power Processing                       |

| DPC               | Direct Power Control                                |

| DTC               | Direct Torque Control                               |

| EMPC              | Explicit Model Predictive Control                   |

| FCS-MPC           | Finite Control Set Model Predictive Control         |

| FOC               | Field Oriented Control                              |

| GPC               | Generalized Predictive Control                      |

| HIL               | Hardware-in-the-Loop                                |

| LPPT              | Least Power Point Tracking                          |

| MILP              | Mixed Integer Linear Programming                    |

| MIPS              | Million of Instructions Per Second                  |

| MO-MPC            | Multiobjective Model Predictive Control             |

| MPPT              | Maximum Power Point Tracking                        |

| MPC               | Model Predictive Control                            |

| M <sup>2</sup> PC | Modulated Model Predictive Control                  |

| MPP               | Maximum Power Point                                 |

| MP <sup>3</sup> C | Model Pulse Pattern Predictive Control              |

| NSS               | Natural Switching Surface                           |

| OSS-MPC           | Optimal Switching Sequence Model Predictive Control |

# OSV-MPCOptimal Switching Vector Model Predictive ControlPWMPulse width ModulationRHPZRight Half plane Zero

- SVM Space Vector Modulation

- VOC Voltage Oriented Control

#### Acknowledgement

First, I would like to thank the Hillman Foundation for their financial support throughout my doctorate studies.

I would also like to thank Dr. Gregory Reed for his contribution to the Electric Power System Laboratory. This contribution led to a very inspirational work environment where I had the occasion to develop many skills.

I would like to thank Dr. Robert Kerestes and Alexis Kwasinski for their teaching and their class materials in the field of power electronics and electric machines that largely contributed to the technical aspects of this dissertation.

I would like to thank Dr. Zhi-Hong Mao and Nikhil Bajaj for their excellent class materials about control theory. Their teaching gave me the solid knowledge basis for the study of more complex control technics such as model predictive control.

Then, I would like to thank my supervisor Dr. Brandon Grainger for his guidance and availability throughout this doctorate. Each one of our research meetings gave me a better insight on where to focus my research guiding me to well-referenced and high-quality research papers.

I would like to thank Tom Cook, Zachary Smith and Santino Graziani for their support. Each one of them helped me in the realization of this project. I would like to specifically thank Zachary Smith and Ali Smith for their kindness and their patience with me, they also largely contributed to my integration in the U.S.

I would like to thank other colleagues in my lab who largely contributed to a friendly and motivating work environment: Ryan Brody, Adam Emes, Christian Perenyi, Corey Weinmann,

xxi

Jenna Delozier, Aryana Nakhai, Nate Carnovale, Nolan Scanlon, Erick Bittenbender, John Kieffer, Michael Sullivan, Sabrina Nguyen and Sabrina Helbig,

I would like to specifically thank Alvaro Cardoza for the emotional support that each of our conversation brought me. I would also to thank him for introducing me to ECE-Graduate Student Association.

I would also like to thank Busra Tugce Susam, Deniz Kocanaogullari, Mahmoud ElKhadrawy and Sébastien Ollivier. They are my second family in U.S and supported me during the most difficult of my days.

Finally, I would like to thank my entire family for their support during this rough period of COVID-19. Both my parents, Maurice and Françoise were always present to listen and talk even if we are miles away. My brother David always inspires me to never give up, always see the brighter days to come and stay positive in life and with my work. Our discussions helped me at every step in the realization of this project and in life in general.

#### **1.0 Introduction**

#### **1.1 Background**

#### 1.1.1 Emergence of Model Predictive Control in Power Electronics and Power Systems

The primary concepts of model predictive control (MPC) emerged in the 1960s as an application of optimal control theory [1] before finding industry applications in the 1970s [1]-[2]. In the late 1990, more than 4500 publications existed in the field of linear MPC in a diverse range of domains such as refining, petrochemicals, chemicals, food processing, aerospace and defense, mining and metallurgy as well as the automotive industry. [2]-[3]. In the meantime, power electronics and power systems field lately adopted MPC theory because of the limited processing power available. The reason is that MPC implementation requires to solve a control problem in real time which implies an important processing power when systems, such as power electronics systems, requires a small sampling period due to very short time constant. In fact, the first application of MPC theory in power electronics was related to high power systems with low switching frequency in the 1980s [4].

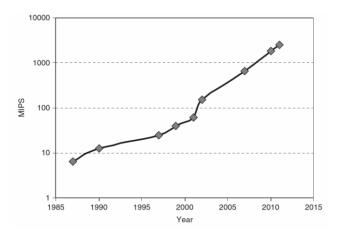

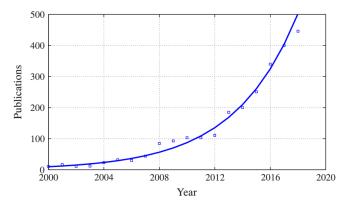

With the important increase in processing power illustrated in figure 1 and the advent of microprocessors, an increasing number of control schemes tied to MPC theory were created for power electronics systems as illustrated in figure 2 [5].

Figure 1: Evolution of Digital Hardware Processing Power in Million of Instruction Per Seconds (MIPS) [1]

Figure 2: Evolution of annual MPC-related peer reviewed publications appearing in IEEE Xplore since 2000 (related to power electronic systems)

#### 1.1.2 Existing Predictive Controllers applied to Power Converters and Drives

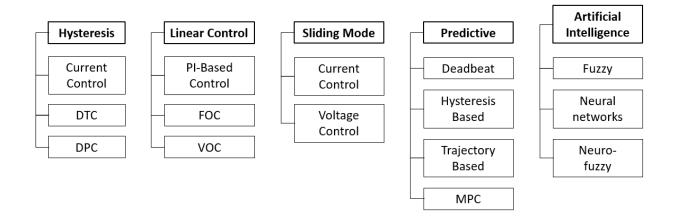

As illustrated by figure 3, MPC belongs to a larger family controller called predictive controllers. This type of controller uses a system model to predict the future behavior of the system to choose the best control decision.

Figure 3: Classification of most common control schemes for power converters and drives [1], [6]

The difference between each type of predictive controller is the optimization criterion applied to generate the control signal. For deadbeat control schemes the optimization criterion is to reach the target output value or set the error to zero after a finite number of sampling instants [7]-[8]. While for hysteresis-based and trajectory-based predictive controller, the optimization intent is to maintain the system states inside a specific area and along a precalculated trajectory respectively [9]. For MPC, the optimization is tied to the minimization of a cost function symbolizing the control objectives set by the control designer.

#### 1.2 Classification of Model Predictive Controls used in Power Electronics and Drives

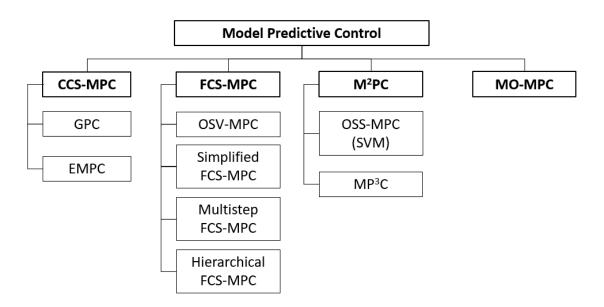

As a starting point, let us consider a general power electronic system where  $u \in R^{n_u}$  is the input vector (also called manipulated variables) and  $y \in R^{n_y}$  the output vector (also called controlled variables) of the system. Both vectors **u** and **y** can contain real values as well as integer values. In figure 4 presenting the different families of MPC, Continuous Control Set Model Predictive Control (CCS-MPC) refers to a type of MPC where the system is assumed be of continuous nature and the input vector u, resulting from the optimization, is composed of real valued components [11].

Figure 4: Classification of Model Predictive Controllers

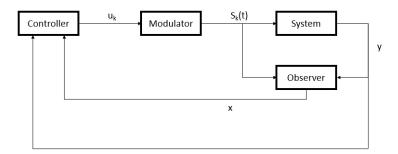

In the context of power converters and drives, the presence of a continuous control signal is associated to the use of a modulator (e.g Space Vector Modulation (SVM) or Pulse Width Modulation (PWM)) that translates the control signal into gating signals driving semiconductor switches of the system. Because of the modulator, such control schemes in figure 5 are considered to be indirect control problem.

**Figure 5: Indirect Control Scheme**

The modulator also sets a fixed switching frequency for the system switches. To estimate the future behavior of the controlled system, the control stage requires the state vector  $x \in \mathbb{R}^{n_x}$  of the system. An observer is used to reconstruct the missing elements of the state vector using a model of the system fed with the control variable u. Observer estimation of state vector is specifically designed to converge to the real state vector by feeding back the difference between the response of this model and the actual output of the system to the controller.

The most common examples of CCS-MPC are the Generalized Predictive Control (GPC) and the Explicit MPC (EMPC). GPC is particularly suited for linear and unconstrained optimization problems [12]-[13]. EMPC solves the optimization problem offline to obtain an explicit control law stored in the form of a look up table. Therefore, the remaining online calculation effort is limited to a search algorithm applying the control law from the offline optimization [14]-[15].

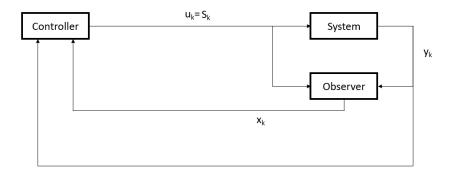

The second family of Model Predictive Control presented in figure 4 is Finite Set Model Predictive Control (FCS-MPC) where the finite number of system states is considered in the MPC framework. This type of MPC is said to be a direct control problem since no modulator is required as in figure 6 and the output of the Model Predictive Controller is a specific switching state with a correponding input vector u.

**Figure 6: Direct Control Scheme**

The first type of FCS-MPC is the optimal switching vector MPC (OSV-MPC) where each possible input vector u is evaluated thanks to a cost function symbolizing the control objectives [16]. The vector u associated with the minimum cost function is applied until the next sampling instant. This type of FCS-MPC is the most widely used in the FCS-MPC family because of its implementation and formulation simplicity. In the literature OSV-MPC is often referred as FCS-MPC since it was the first type of FCS-MPC to emerge in power systems application. The first drawback of OSV-MPC is the high computional cost required to solve optimization problem. The computation cost requirement can be mitigated with the use of simplified FCS-MPC [17]-[18], Multistep FCS-MPC [19]-[21] and Hierarchical FCS-MPC [22]-[25]. The second drawback is is the variable switching frequency since the same input vector can be used in two consecutives sampling instant for OSV-MPC.

This problem is solved by the Modulated MPC or MP<sup>2</sup>C presented in figure 4 since this type of model predictive control includes a modulation scheme in the cost function. In the case of Optimal switching sequence MPC (OSS-MPC) only specific sequences of input vectors are considered in the optimization problem [26]-[27]. The SVM scheme determines which input

vectors and their application time to obtain a set of possible switching sequences. The switching sequence with the minimum cost function is applied until the next sampling instant. As the application times are associated with switching sequence, the switching frequency can be made constant. A different kind of modulation is explored combining the optimized pulse paterns concepts and Model Predictive Control framework to obtain the Model Predictive Pulse Pattern Control (MP<sup>3</sup>C) [28].

The Multi-Objective MPC (MO-MPC) presented in figure 4 uses the multi-objective formulation to avoid the adjustment of the weighting factors composing the cost function [29]. The notion of weighting factor and its use in Model Predictive Control are explained in the next section. The scope of this work is focused in the application of OSV-MPC, named FCS-MPC throughout

this document, since this type of MPC is the most intuitive and easy to implement.

#### **1.3 Basic Principles of FCS-MPC**

This section presents the key design aspects of FCS-MPC to build a generalized MPC framework for the rest of this document. Five key attributes common to all MPC variations and formulations are defined in [2]:

- The internal dynamic model

- Cost Function (with weighting factors)

- Optimization Stage

- Receding horizon policy

- Constraints

The next subsections describe the key attributes defined above and the specificities brought by the FCS-MPC formulation. The first subsection describes the internal dynamic model while the second subsection describes the optimization stage along with the cost function and the receding horizon policy. Finally the last subsection describes the constraints of Model Predictive Control.

#### **1.3.1 Internal dynamic model**

The MPC formulation requires an internal dynamic model of the system to predict its future states and outputs and input the best control decision. This internal dynamic model is the state-space representation of the system in (1) for linear systems such as power electronic systems and drives where x, y and u are the same state, output and input vectors defined in section 1.2. F, G and C are the system, input, and output matrix, respectively.

$$\dot{x} = Fx + Gu$$

$$y = Cx + Du$$

(1-1)

In the context of FCS-MPC, the system is controlled in the discrete domain with discrete variables x(k), y(k) and u(k). The system of equations (1-1) can be discretized using the Forward Euler discretization of (1-2) to obtain (3) where  $T_s$  is the sampling period,  $A = I + FT_s$  and  $B = GT_s$ .

$$\dot{x} = \frac{x(k+1) - x(k)}{T_s}$$

(1-2)

$$\begin{aligned} x(k+1) &= Ax(k) + Bu(k) \\ y(k) &= Cx(k) + Du(k) \end{aligned} \tag{1-3}$$

The purpose of system of equations in (1-3) is to predict the system states at next sampling instant x(k + 1) for each specific control decision u(k), knowing the current system state x(k).

#### **1.3.2 Minimization of the Cost Function and Receding horizon policy**

The control objectives set by the Model Predictive Control is expressed by the mean of the cost function, evaluating a specific control decision. A generalized formulation of the cost function is

expressed in (1-4) mapping a set of input vectors  $\boldsymbol{U}(k) = \begin{bmatrix} \boldsymbol{u}^T(k) \\ \boldsymbol{u}^T(k+1) \\ \vdots \\ \boldsymbol{u}^T(k+N_p-1) \end{bmatrix}$  to a real scalar

value over a finite *horizon* of  $N_P$  time steps.

$$J(x(k), \boldsymbol{U}(k)) = \sum_{l=k}^{k+N_p-1} \Lambda(x(l), u(l))$$

(1-4)

(4) is the sum of stage costs  $\Lambda(.,.)$  over  $N_P$  time steps ahead, each computed using the current state vector x(k), as a starting point, cost and the elements of U(k) along with discrete-time dynamic model introduced in (1-3) to calculate each x(l).[2] introduces the notion of *receding horizon policy* where only the first element of U(k) is applied and U(k) is recalculated at the next sampling instant. In the literature MPC are referred to be long horizon prediction as  $N_P$  gets higher providing better closed-loop performances than short horizon prediction where Np gets small or equals 1. However, increasing the length of horizon prediction worsen the computational cost required to implement the control scheme. A common usage is to express each stage cost as a linear expression of control objectives  $J_i(x(l), u(l))$  in (1-5) for the time step *l*.

$$\Lambda(x(l), u(l)) = \sum_{i=1}^{n} \lambda_i J_i(x(l), u(l))$$

(1-5)

Each  $\lambda_i$  is called a weighting factor and is a key design feature since it adjusts the trade-off between control objectives. A high weighting factor  $\lambda_i$  prioritizes the associated control objective  $J_i$ .

The minimization of the cost problem subject to the discrete time internal dynamic system and constraints on input, state and output vectors (detailed in the next section) can be formulated as mixed-integer linear programming (MILP) problem in (1-6).

$$U_{opt}(k) = \arg\min_{\substack{Uk\\Uk}} I(x(k), U(k))$$

$$x(l+1) = Ax(l) + Bu(l)$$

$$subject to \qquad y(l) = Cx(l) + Du(l)$$

$$\forall l = k, ..., k + N_p - 1$$

(1-6)

In the case of FCS-MPC (OSV-MPC), the input vector can only take a discrete number of values and the MILP problem is solved by calculating the cost function associated to each possible input vector and select the input vector with the minimum cost function.

#### **1.3.3 FCS-MPC Constraints**

In all MPC formulations and variations, state, output and input vectors can be restricted by the general constraints defined in (1-7) using bounded continuous set X, Y and U where  $n_X$ ,  $n_Y$  and  $n_U$  are the dimensions of the state, output and input vectors respectively.

$$\begin{aligned} x \in \mathbf{X} \subseteq \mathbb{R}^{n_X} \\ y \in \mathbf{Y} \subseteq \mathbb{R}^{n_Y} \\ u \in \mathbf{U} \subseteq \mathbb{Z}^{n_U} \end{aligned}$$

(1-7)

The constraints on state and output vectors are used to evaluate the state predictions from the internal dynamic model. In fact, if a predicted state or output is estimated to not respect the constraint, the associated cost function is set to infinity (hard constraint). Since the control decision is taken based on the minimization of cost function, setting the cost function to infinity is equivalent to ignore the possibility to apply the associated control decision.

In the context of the FCS-MPC, only a discrete number of possible input vectors (corresponding to the number of switching states of a power electronic system) is considered. Therefore, in the case of FCS-MPC, the input vector constraint in (1-7) should be replaced by  $U \subseteq Z^{n_u}$ .

#### **1.4 Contribution**

The first contribution of this work, mentioned as research task 1, is to apply geometrical domain analysis to design a Time Optimal One Step FCS-MPC for boost converter. The purpose in the use of geometrical domain analysis is to avoid the non-minimum phase behavior disturbing FCS-MPC schemes. The second purpose is to mitigate the large load transients when time optimal boundary control is used.

The second contribution, mentioned as research task 2, is to extend the previous FCS-MPC to non-isolated dc-dc converters using the unified switching model in geometrical domain.

The third contribution, referred as research task 3, aims at applying FCS-MPC to series PV-bus direct Bidirectional Flyback Differential Power Processing to improve the control dynamic performance and power stress minimization. The proposed control scheme is solving the interaction issue between Maximum Power Point (MPPT) Tracking and Least Power Point Tracking (LPPT) algorithm.

#### **1.5 Thesis Organization**

Section II develops the construction of cost function using natural trajectories, and constraint for the time optimal One Step FCS-MPC of DC-DC boost converter, also referred as research task 1. Section III generalizes the concepts of section II to common Non-Isolated DC-DC converters using a unified switching model. Section III is dedicated to research task 2 and formulates the cost function leading to a time optimal regulation and targeting a specific switching frequency. In this section, the proposed control scheme is validated using a Control Hardware-in-The Loop simulation. Section IV presents the proposed set of FCS-MPC of research task 3 for the series PV bus direct flyback bidirectional DPP. Section VI concludes this work with potential future research tasks.

# 2.0 Research Task #1-FCS-MPC for a DC-DC Boost Converter Ensuring Time Optimal regulation and Controlled Output Voltage Deviation

#### 2.1 Literature Review and Motivation

Traditional linear controllers used for basic DC-DC topologies such as buck, boost and buck-boost converter use the small signal representation to obtain a linear representation of the system [1]. With this representation, useful analysis tools in the frequency domain were developed such as pole placement, root locus and bode plot [8]. However, for the boost converter, the input to output (output voltage) transfer function from small signal analysis contains a right half plane zero (RHPZ), limiting the dynamic performance of linear controllers. If a system's transfer function contains a RHPZ, the system is said to have a non-minimum phase behavior characterized by an initial undershoot in response to a step change [2] This behavior disturbs another type of control: the one step finite control set (FCS)-Model Predictive control (MPC) [2]-[5] In fact, a one-step FCS-MPC uses a mathematical model (predictive model) to estimate the converter states for the next sampling period for each control action. Because of the initial undershoot, the non-minimum phase behavior can mislead the one step FCS-MPC. To anticipate this behavior, the prediction horizon of the FCS-MPC can be extended [4], [6]. However, extending the prediction horizon increases the computational burden. Algorithms such as [7] aim at reducing this computational burden but increases the complexity of the FCS-MPC.

In response to the dynamic performance limitation of linear controllers mentioned earlier, geometrical domain analysis was developed as an alternative to the small signal analysis. Using the state plane where the x-axis represents the capacitor voltage and the y-axis the inductor

current, a geometrical point of view of the converter behavior is adopted. A typical geometrical based control uses a switching surface (SS) as a boundary to divide the state plane into areas that will condition the control action [8]. Such controllers are called boundary controllers because their development relies on a boundary in the state plane. A good example of boundary control is sliding mode control (SMC) using a first order SS to create a simple and robust control algorithm [9]-[12]. Because the transition along the first order SS is slow, other boundary controls using curved switching surfaces such as Second Order Switching Surfaces are used [13]. The dynamic response is improved when using this type of switching surface when compared to SMC but exhibits overshoots during start-up and large load transient. To solve the overshoot problem, boundary controllers using natural state plane trajectories of the boost converter as switching surfaces, also called Natural Switching Surfaces (NSS), are developed in [14] (boundary boost converter). The use of these switching surfaces ensures the converter to reach steady state in one switching action which represents a time optimal regulation [15], and a constant switching frequency. However, the proposed boundary control in [14] shows time optimal performances without considering an important dynamic performance factor-the output voltage deviation [16]. Those downsides are reduced in [17] merging geometrical domain analysis and averaging to create average natural trajectories. However, this strategy increases the control complexity compared to time optimal boundary control of [14].

As mentioned in section 1.1, MPC can include non-linear expressions and system constraints through the design of a cost function. The motivation behind this work is to use the geometrical analysis developed in [14] to formulate a cost function that will track specific time optimal trajectories within the proposed one step FCS-MPC. The proposed control scheme is designed to have the same dynamic performances as [14] while offering the possibility to limit

the voltage deviation setting a constraint on the FCS-MPC. Two main contributions can be listed since boundary controllers are improved by FCS-MPC as much as FCS-MPC benefits from the geometrical domain analysis. On one hand, geometrical analysis offers a solution to avoid the non-minimum phase behavior that perturbs the one step FCS-MPC. On the other hand, large voltage deviation from [16] can be limited with FCS-MPC constraints.

In Section 2.2, the normalization process of the boost converter to obtain a predictive model and Natural Trajectories of the converter is reviewed. Section 2.3 presents the dynamic performance indices from [16], specific to boost converter output voltage regulation. Section 2.4 recalls key aspects of time optimal boundary control using NSS from [14]. Section 2.5 of the paper describes the key aspects of the proposed One-Step FCS-MPC such as the predictive model, the cost function using Natural Trajectories tracking expressions, and input parameter constraint. Section 2.6 presents the results of the MATLAB simulation of the boost converter with the proposed control to validate the FCS-MPC design and compares its dynamic performance with the boundary controller in [14] using the dynamic performance indices of [16]. Section 2.7 presents the limitations of the proposed FCS-MPC from this section.

### 2.2 Boost Converter Normalization and Discrete Relationships

The behavior of the boost converter illustrated in figure 7 can be described with differential equations (2-1) and (2-2) where u = 0 when the MOSFET is OFF and u = 1 when the MOSFET is ON.

$$C\frac{dV_o}{dt} = (1-u)I_L - I_o$$

(2-1)

$$L\frac{dI_L}{dt} = V_{cc} - (1-u)V_0$$

$$(2-2)$$

$$V_{cc} + V_0 = I_0$$

Figure 7: DC-DC boost converter

Continuous Conduction Mode is assumed in this work. The following base values were utilized to normalize the system of differential equations to obtain (2-3) and (2-4) where  $V_r$  is the desired output voltage setpoint.

$$V_{base} = V_r T_{base} = 2\pi\sqrt{LC}$$

$$Z_{base} = \sqrt{L/C} I_{base} = V_{base}/Z_{base}$$

$$\frac{1}{2\pi} \frac{dV_{on}}{dt_n} = (1-u)I_{Ln} - I_{on}$$

(2-3)

$$\frac{1}{2\pi} \frac{dI_{Ln}}{dt_n} = V_{ccn} - (1-u)V_{on}$$

(2-4)

From (2-3) and (2-4), the discretized relationships, listed as (2-5) and (2-6), are obtained to create a predictive model.  $T_{sn}$  represents the normalized sampling period of the inductor current and capacitor voltage.

$$V_{on}(k+1) = 2\pi T_{sn}((1-u)I_{Ln}(k) - I_{on}(k)) + V_{on}(k)$$

(2-5)

$$I_{Ln}(k+1) = 2\pi T_{sn}(V_{ccn} - (1-u)V_{on}(k)) + I_{Ln}(k)$$

(2-6)

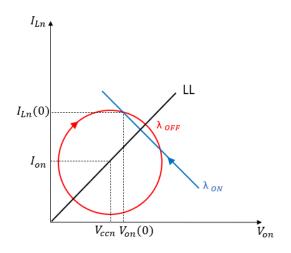

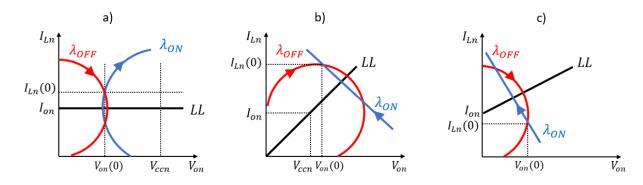

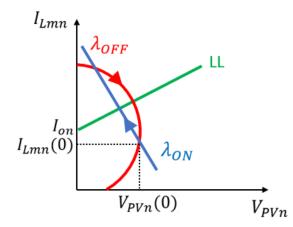

Time Optimal Control framed by geometrical analysis relies on building time optimal trajectories in the state plane using natural trajectories of converter states in both switching modes (MOSFET ON or OFF). As shown in figure 8, a state plane analysis of the converter behavior gives a visual representation of the states trajectory when *u* is maintained at 0 ( $\lambda_{OFF}$ ) or at 1 ( $\lambda_{ON}$ ), corresponding to the OFF NSS and ON NSS of the converter, respectively.

Figure 8:ON and OFF natural switching surfaces of the boost converter

Equations (2-7) and (2-8) are the analytical expression of the ON NSS and OFF NSS respectively, obtained by transformation of the time-domain solution of (2-3) and (2-4) as presented in [14].

$$\lambda_{ON}: I_{Ln} = -\frac{V_{ccn}}{I_{on}} V_{on} + I_{Ln}(0) + \frac{V_{ccn}}{I_{on}} V_{on}(0)$$

(2-7)

$$\lambda_{OFF} : (I_{Ln} - I_{on})^2 + (V_{on} - V_{ccn})^2 = (I_{Ln}(0) - I_{on})^2 + (V_{on}(0) - V_{ccn})^2$$

(2-8)

With (2-5) and (2-6), it is possible to explain the orientation taken by the converter as each NSS represents 1 of 2 states in figure 2. The OFF NSS is a circle whose center is defined by the DC operating point ( $V_{ccn}$ ,  $I_{on}$ ) and whose radius is the distance between the DC operating point and

the point defined by the initial conditions (V<sub>on</sub> (0), I<sub>Ln</sub> (0)). The ON NSS is a line with a slope equal to  $-\frac{V_{CCn}}{I_{on}}$  and intersects the initial condition coordinate.

The load line (LL) presented in figure 8 and in the equation below corresponds to the set of equilibrium points of the converter where the OFF NSS tangent and the ON NSS are identical.

$$LL: I_{Ln} = \frac{I_{on}}{V_{ccn}} V_{on}$$

### 2.3 Dynamic Performance indices for boost converter

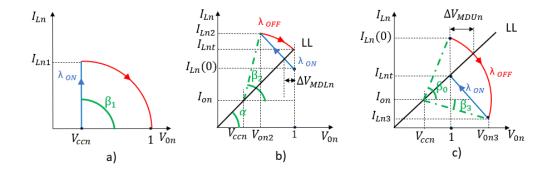

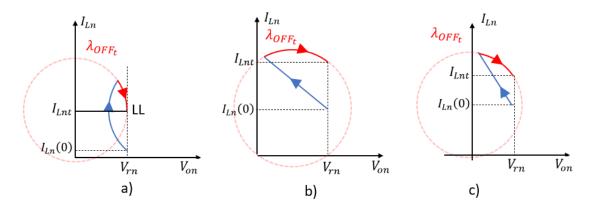

Figure 9 illustrates the desired time optimal trajectory for different transient types to ensure MTC. All these trajectories are time optimal since each one of them is composed of only one ON NSS and one OFF NSS. This is equivalent to regulating within one switching action [15],[16].

Figure 9: Time optimal trajectories for start-up (a), loading (b) and unloading (c) transient.

Three types of transients are considered in this figure: loading transient, unloading transient and start-up transient. The start-up refers to controlling the output voltage from a value equal to the

DC input voltage,  $V_{ccn}$ , to the desired output voltage equal to 1 when normalized. Loading and unloading transient scenarios refer to the converter response to an increase and a decrease in the load current  $I_0$ , respectively. In the two last transient cases, the voltage needs to be regulated to its reference value with a different target inductor current  $I_{Lnt} = \frac{i_{on}}{V_{ccn}}$  resulting from the change in load current  $I_0$ .

In [16], theoretical performance limits of boost converters are developed to provide objective dynamic performance indices ranging from 0 to 1. Section 2.3.1 and 2.3.2 review the dynamic performance indices related to recovery time and voltage deviation for the three transient types mentioned above, respectively.

### **2.3.1 Voltage Deviation Performance Indices**

Figure 9a shows that the minimum start-up voltage overshoot  $\Delta v_{OS}$  is zero. The difference between the desired output voltage and the initial output voltage,  $V_r - V_{cc}$ , is used as a reference in the voltage deviation index related to start-up transient *SOi* in (2-9).

$$SOi = \frac{V_r - V_{cc}}{V_r - V_{cc} + 2\Delta v_{OS}}$$

(2-9)

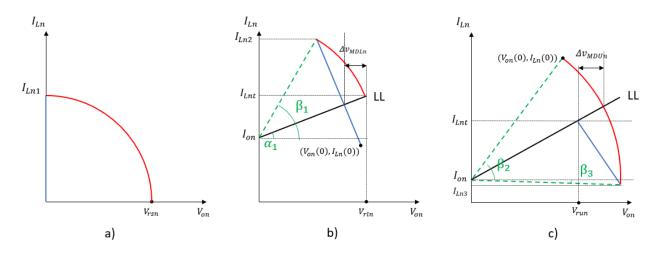

Figure 9b and 9c illustrate the minimum voltage deviation during a loading transient  $\Delta v_{MDLn}$  and an unloading transient  $\Delta v_{MDUn}$ , respectively. In both cases, the minimum deviation is achieved once the load line has been reached. Thanks to this observation,  $\Delta v_{MDLn}$  in (2-10) and  $\Delta v_{MDUn}$  in (2-11) are geometrically calculated.

$$\Delta v_{MDLn} = \frac{(i_{Lnt} - i_{Ln}(0))i_{Lnt}}{1 + i_{Lnt}^2}$$

(2-10)

$$\Delta v_{MDUn} = V_{ccn} - 1 + \sqrt{\frac{(i_{Ln}(0) - I_{on})^2 + (1 - V_{ccn})^2}{1 + i_{Lnt}^2}}$$

(2-11)

In (2-12), the minimum voltage deviation is used as a reference to objectively analyze the peakto-peak voltage excursion  $\Delta v_{pk-pk(L/U)}$  from the voltage regulation during a loading transient (subscript L) or an unloading transient (subscript U).

$$DR_{(L/U)} = \frac{\Delta v_{MD(L/U)}}{\Delta v_{pk-pk(L/U)}}$$

(2-12)

### 2.3.2 Recovery Time Performance Indices

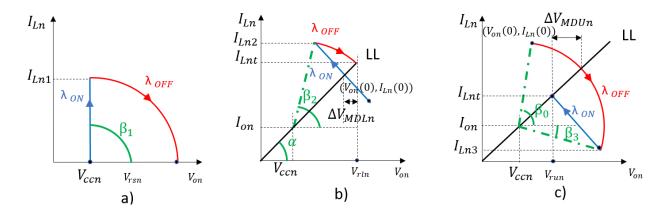

The normalized minimum settling time during start-up transient (2-13) is calculated using the geometrical values from figure 9a ( $\beta_1$  and  $I_{L1}$ ) and (2-2), [16].

$$t_{MS_n} = \frac{i_{Ln1}}{2\pi V_{ccn}} + \frac{\beta_1}{2\pi} = \frac{1}{2\pi} \left( \frac{1}{V_{ccn}} - 1 \right) + \frac{1}{4}$$

(2-13)

This minimum is used as a reference to objectively analyze the settling time,  $t_{start}$ , in (2-14).

$$ST_i = 1 - 0.5 \log\left(\frac{t_{start}}{t_{MS}}\right) \tag{2-14}$$

The minimum recovery time for a loading transient scenario requires determining the intersection point  $(i_{Ln2}, V_{on2})$  (figure 9b) between the initial ON NSS and the target OFF NSS. With this point,  $\beta_2$  and  $\alpha$  can be calculated [16]. Using (2-2), the theoretical minimum normalized recovery time for a loading transient  $t_{MRL_n}$  is given in (2-15).

$$t_{MRL_n} = \frac{i_{Ln2} - i_{Ln}(0)}{2\pi V_{ccn}} + \frac{\beta_2 - \alpha}{2\pi}$$

(2-15)

A similar calculation is possible for the unloading transient to obtain the intersection point between the initial OFF NSS and the target ON NSS. ( $i_{Ln3}$ ,  $V_{on3}$ ) (figure 9c). After that,  $\beta_0$  and  $\beta_3$  are computed to estimate the minimum recovery time for a given unloading transient in (2-16).

$$t_{MRU_n} = \frac{i_{Lnt} - i_{Ln3}}{2\pi V_{ccn}} + \frac{\beta_0 + \beta_3}{2\pi}$$

(2-16)

Equation (2-15) and (2-16) are used as a reference to inspect the loading  $(t_{recL})$  and unloading transient  $(t_{recU})$  recovery time, respectively, in (2-17).

$$RTi_{(L/U)} = 1 - 0.5\log\left(\frac{t_{rec(L/U)}}{t_{MR(L/U)}}\right)$$

(2-17)

# 2.4 Time Optimal Boundary Control using NSS

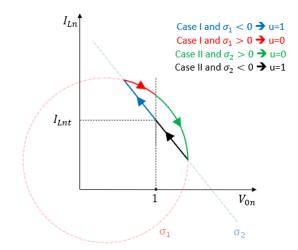

The boundary control presented in [14] aims at ensuring a MTC during start-up and when the output voltage undergoes large load changes. The control scheme from [14], presented below, distinguishes two cases based on the capacitor voltage  $V_{on}$ . Each case has its own control law.

<u>Case I</u>:  $V_{on} < 1$ If  $\sigma_1 > 0$ , then u = 0, else u = 1<u>Case II</u>:  $V_{on} > 1$ If  $\sigma_2 > 0$ , then u = 1

Where,

$$\sigma_1 = (i_{Ln} - I_{on})^2 + (v_{on} - V_{ccn})^2 - (1 - V_{ccn})^2 - \left(\frac{I_{on}}{V_{ccn}} - I_{on}\right)^2 - \Delta r^2$$

(2-18)

$$\sigma_2 = i_{Ln} + \left(\frac{V_{ccn}}{I_{on}}\right) v_{on} - \left(\frac{I_{on}}{V_{ccn}} + \frac{V_{ccn}}{I_{on}}\right)$$

(2-19)

Control laws  $\sigma_1$  and  $\sigma_2$  are created replacing  $V_{on}(0)$  by 1 and  $I_{Ln}(0)$  by  $I_{Lnt} = \frac{i_{on}}{V_{ccn}}$  in (2-8) and (2-7), respectively. Equation (2-18) is the relationship of the OFF NSS circle including the target point  $(1, I_{Lnt})$  with an increment  $\Delta r^2$  in its radius. Equation (2-19) is the relationship of the ON NSS containing the target point. Figure 10 illustrates control laws  $\sigma_1$  and  $\sigma_2$  in the state plane domain.

Figure 10: State plane representation of control laws from [14].

If the normalized capacitor voltage is inferior to 1 (case I), the MOSFET is kept ON if the converter states are inside the OFF NSS containing the point  $(1, \frac{I_{on}}{V_{ccn}})$ . Once the converter states reach the target OFF NSS, the MOSFET is turned OFF and the system evolves along the target OFF NSS. Then, once the normalized capacitor voltage is superior to 1 (case II), the MOSFET is turned ON when it reaches the ON NSS containing the point  $(1, \frac{I_{on}}{V_{ccn}})$ , putting the converter states back in case I.

The purpose of the increment  $\Delta r^2$  is to have a control on the output voltage ripple in (2-20), inductor current ripple in (2-21) and switching frequency (2-22).

$$\Delta V_{on} = \frac{2\sqrt{\Delta r^2}}{\sqrt{1 + \left(\frac{V_{ccn}}{I_{on}}\right)^2}}$$

(2-20)

$$\Delta I_{Ln} = \frac{V_{ccn}}{I_{on}} \Delta V_{on} \tag{2-21}$$

$$f_{sw} = \frac{2\pi}{T_{base}\Delta V_{on}} I_{on}(1 - V_{ccn})$$

(2-22)

The MOSFET is kept ON until reaching the target OFF NSS under start-up and loading transient as in figure. 9a and 9b. The MOSFET is kept OFF until reaching the target ON NSS under an unloading transient like in figure 9c. From these statements, the boundary control scheme ensures the MTC for start-up and large load changes.

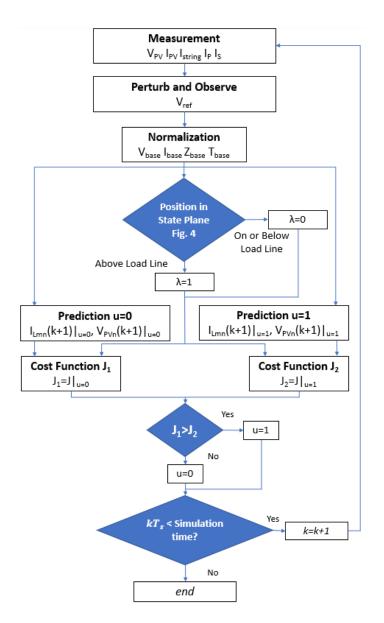

### 2.5 Proposed Finite Control Set Model Predictive Control based on NSS tracking

The design of the FCS-MPC relies on three key features: the predictive model, a cost function representing the feature to be minimized and constraints on input variables used for the control. Equations (2-5) and (2-6) are used as the predictive model in the proposed FCS-MPC. Section 2.5.1 describes the cost function designed for time optimal control while section 2.5.2 presents the constraint on the output voltage deviation.

### 2.5.1 NSS Tracking Cost Function for Time Optimal Control

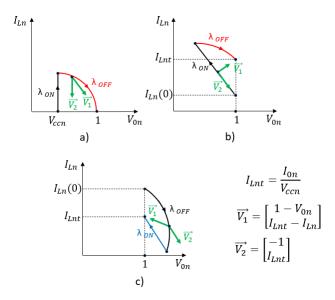

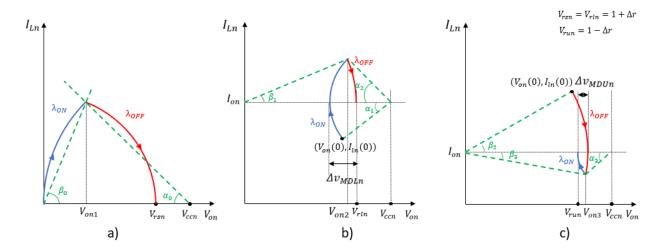

Figure 11 introduces vectors  $V_1$  and  $V_2$ , useful for the cost function design, along with the expected time optimal trajectories.

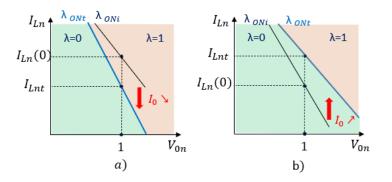

Figure 11: Ideal trajectories for MTC in state-plane domain for (a) start-up transient, (b) loading transient and (c) unloading transient

From this figure, two situations are considered. One scenario is illustrated in (a) and (b) where the state trajectory ends with an OFF NSS in red whereas the other scenario is illustrated by (c) where the state trajectory ends with an ON NSS in blue. Since the system offers only two possible switching positions, the first situation can be translated into tracking the OFF NSS containing the target point (1,  $I_{Lnt}$ ) while the other situation is equivalent to tracking the ON NSS including the target point (1,  $I_{Lnt}$ ).

The OFF NSS tracking is translated into a cost function term in (2-23), decreasing when the converter states evolve along the ideal trajectory of (a) under start-up conditions or (b) for a

loading transient, where  $R^2 = (I_{Lnt}(k) - I_{on}(k))^2 + (1 - V_{ccn})^2$  and can be verified from the diagrams in figure. 11.

$$J_{ref_{OFF}}(I_{Ln}(k+1), V_{on}(k+1)) = |||\overrightarrow{V_1}||||\overrightarrow{V_2}|| - \overrightarrow{V_1}, \overrightarrow{V_2}| + |(I_{Ln}(k+1) - I_{on}(k))^2 + (V_{on}(k+1) - V_{ccn})^2 - R^2|$$

(2-23)

Similarly, the ON NSS tracking is expressed in (2-24) as a decreasing term when the converter states evolve along the trajectory in (c) for an unloading transient.

$$J_{refon}(I_{Ln}(k+1), V_{on}(k+1))$$

$$= |||\overrightarrow{V_1}|| ||\overrightarrow{V_2}|| + \overrightarrow{V_1}. \overrightarrow{V_2}|$$

$$+ |1 + I_{Lnt}(k)^2 - I_{Ln}(k+1)I_{Lnt}(k) - V_{on}(k+1)|$$

(2-24)

The first term of the addition in (2-23) and (2-24) uses a scalar product between a vector representing the orientation and direction taken by the tracked NSS at the target point  $(-\overrightarrow{V_2})$  for ON NSS and  $\overrightarrow{V_2}$  for OFF NSS) and a vector  $\overrightarrow{V_1}$  going from the current position to the target point. In (2-23), this term will be minimized if  $\overrightarrow{V_1}$  shares the same direction and orientation as  $\overrightarrow{V_2}$ . Similarly, the first term of (2-24) is minimized if  $\overrightarrow{V_1}$  shares the same direction and orientation as  $-\overrightarrow{V_2}$ .

The second term of the addition in (2-23) compares the square of the distance from the DC operating point and the current position with the distance from the DC operating point and the target point. Similarly, the second term in (2-24) refers to the distance between the x-intercept of the ON NSS tied to the current position and the x-intercept of the ON NSS tied to the target point.

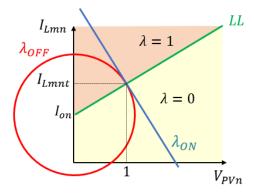

To create the cost function (2-25), (2-23) and (2-24) are combined using a factor  $\lambda$  equal to 1 if the ON NSS tracking is enabled and 0 if OFF NSS tracking is enabled.

$$J = \lambda J_{refor} + (1 - \lambda) J_{refor}$$

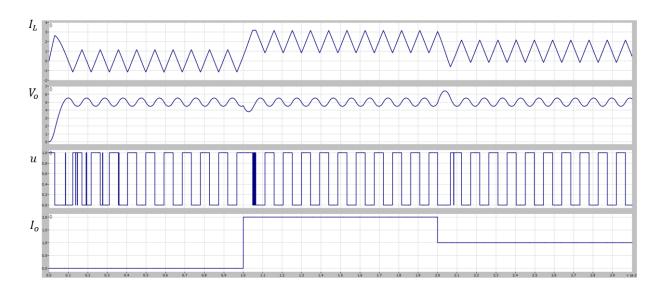

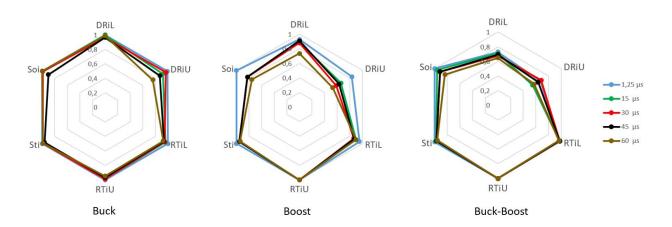

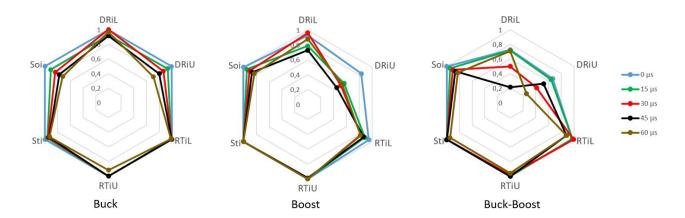

(2-25)