## A PHYSICAL IMPLEMENTATION WITH CUSTOM LOW POWER EXTENSIONS OF A RECONFIGURABLE HARDWARE FABRIC

by

## Gerold Joseph Dhanabalan

B.E.(Hons.), Birla Institute of Technology and Science, Pilani, 2002

Submitted to the Graduate Faculty of Swanson School of Engineering in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

University of Pittsburgh

2008

## UNIVERSITY OF PITTSBURGH

## SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

Gerold Joseph Dhanabalan

It was defended on

March 05, 2008

and approved by

Dr.Alex K. Jones, Assistant Professor, Electrical and Computer Engineering Department

Dr. Steven P. Levitan, John A. Jurenko Professor, Electrical and Computer Engineering

Department

Dr.Jun Yang, Assistant Professor, Electrical and Computer Engineering Department

Thesis Advisor: Dr.Alex K. Jones, Assistant Professor, Electrical and Computer Engineering

Department

# A PHYSICAL IMPLEMENTATION WITH CUSTOM LOW POWER EXTENSIONS OF A RECONFIGURABLE HARDWARE FABRIC

Gerold Joseph Dhanabalan, M.S.

University of Pittsburgh, 2008

The primary focus of this thesis is on the physical implementation of the SuperCISC Reconfigurable Hardware Fabric (RHF). The SuperCISC RHF provides a fast time to market solution that approximates the benefits of an ASIC (Application Specific Integrated Circuit) while retaining the design flow of an embedded software system. The fabric which consists of computational ALU stripes and configurable multiplexer based interconnect stripes has been implemented in the IBM 0.13um CMOS process using Cadence SoC Encounter.

As the entire hardware fabric utilizes a combinational flow, glitching power consumption is a potential problem inherent to the fabric. A CMOS thyristor based programmable delay element has been designed in the IBM 0.13um CMOS process, to minimize the glitch power consumed in the hardware fabric. The delay element was characterized for use in the IBM standard cell library to synthesize standard cell ASIC designs requiring this capability such as the SuperCISC fabric. The thesis also introduces a power-gated memory solution, which can be used to increase the size of an EEPROM memory for use in SoC style applications. A macromodel of the EEPROM has been used to model the erase, program and read characteristics of the EEPROM. This memory is designed for use in the fabric for storing encryption keys, etc.

## TABLE OF CONTENTS

| AC  | KNO | WLED  | GEMENTS xvii                                              |

|-----|-----|-------|-----------------------------------------------------------|

| 1.0 |     | INTR  | ODUCTION1                                                 |

|     | 1.1 | S     | STATEMENT OF THE PROBLEM 6                                |

| 2.0 |     | SUPE  | RCISC RECONFIGURABLE HARDWARE FABRIC                      |

|     | 2.1 | A     | ARCHITECTURE OF THE SUPERCISC RHF                         |

|     | 2.2 | A     | ARITHMETIC AND LOGIC UNIT (ALU)                           |

|     | 2.3 | Ι     | NTERCONNECT MULTIPLEXER STRUCTURE (MUX) 10                |

|     | 2.4 | F     | FINAL MULTIPLEXER STRUCTURE (FINALMUX) 11                 |

| 3.0 |     | POW   | ER ESTIMATION 13                                          |

|     | 3.1 | F     | POWER DISSIPATION TERMINOLOGIES 13                        |

|     |     | 3.1.1 | Static Power Consumption15                                |

|     |     | 3.1.2 | Dynamic Power Consumption16                               |

|     | 3.2 | F     | PRIMEPOWER POWER ESTIMATION FLOW 17                       |

|     |     | 3.2.1 | Prime Power's Event Based Power Estimation Flow           |

|     |     | 3.2.2 | Calculation of Static Power Dissipated using Prime Power  |

|     |     | 3.2.3 | Calculation of Dynamic Power Dissipated using Prime Power |

|     | 3.3 | ł     | POWER ESTIMATION USING HSPICE                             |

|     |     | 3.3.1 | Calculation of Rise Power                                 |

|     |     | 3.3.2 | Calculation of Fall Power                                 |

|     |     | 3.3.3 | Calculation of On-State Leakage                           |

|     |     | 3.3.4 | Calculation of Off-State Leakage                          |

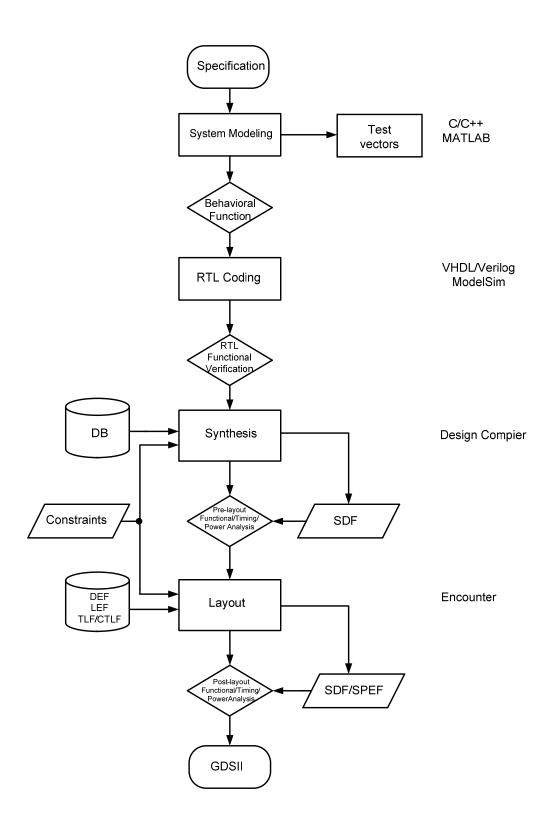

| 4.0 |     | ASIC DESIGN FLOW |                                           |    |

|-----|-----|------------------|-------------------------------------------|----|

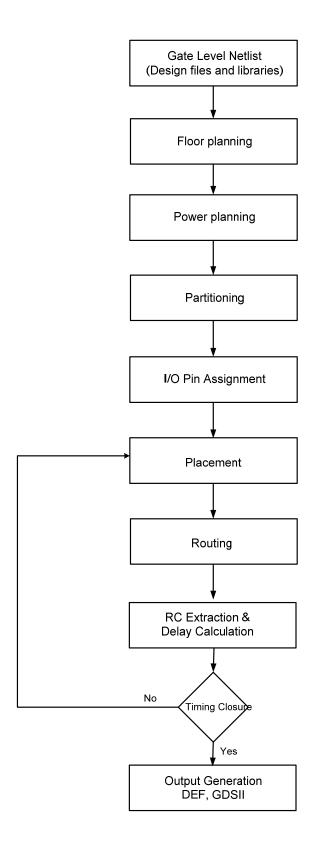

|     | 4.1 | P                | PHYSICAL DESIGN FLOW                      | 30 |

|     |     | 4.1.1            | Floorplanning                             | 30 |

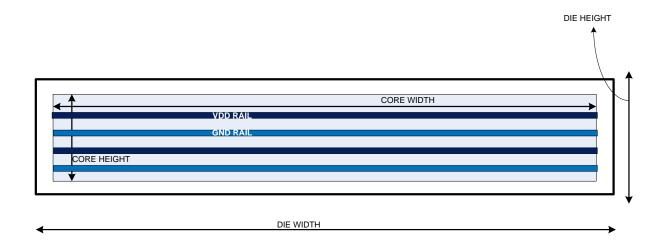

|     |     | 4.1.2            | Powerplanning                             | 33 |

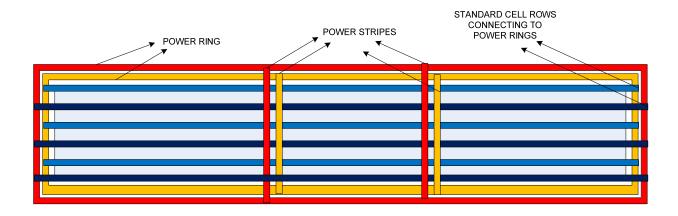

|     |     | 4.1.3            | Partitioning a design                     | 34 |

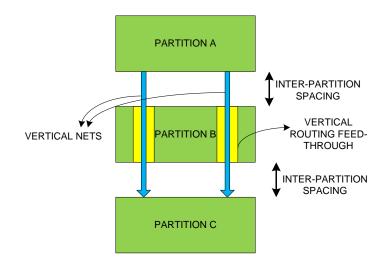

|     |     | 4.1.4            | Routing Feedthrough                       | 34 |

|     |     | 4.1.5            | Pin Assignment                            | 36 |

|     |     | 4.1.6            | Placement                                 | 36 |

|     |     | 4.1.7            | Routing                                   | 37 |

| 5.0 |     | PHYS             | SICAL IMPLEMENTATION OF THE SUPERCISC RHF | 38 |

|     | 5.1 | Ι                | DESIGN OF THE ALU STRIPE                  | 38 |

|     |     | 5.1.1            | ALU Module Specifications                 | 38 |

|     |     | 5.1.2            | ALU Stripe Specifications                 | 40 |

|     |     | 5.1.3            | ALU Stripe Automation Scripts             | 42 |

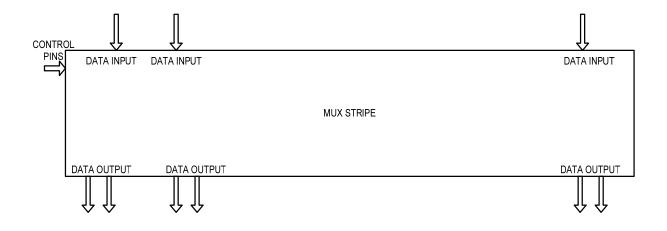

|     | 5.2 | Γ                | DESIGN OF THE MULTIPLEXER STRIPE          | 48 |

|     |     | 5.2.1            | MUX Module Specifications                 | 49 |

|     |     | 5.2.2            | MUX Stripe Specifications                 | 50 |

|     |     | 5.2.3            | MUX Stripe Automation Scripts             | 52 |

|     | 5.3 | Γ                | DESIGN OF THE FINALMUX STRIPE             | 56 |

|     |     | 5.3.1            | FINALMUX Module Specifications            | 56 |

|     |     | 5.3.2            | FINALMUX Stripe Specifications            | 58 |

|     |     | 5.3.3            | FINALMUX Stripe Automation Scripts        | 59 |

|     | 5.4 | Ι                | DESIGN OF THE BIGFABRIC                   | 61 |

|     | 5.4.1                                         | BIGFABRIC Chip Specifications                                                                                                                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.4.2                                         | BIGFABRIC Automation Scripts                                                                                                                                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.5 | P                                             | OWER ANALYSIS OF THE CHIP                                                                                                                                                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.1                                         | Power Results for ADPCM Encoder Bench Mark                                                                                                                                               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.2                                         | Power Results for ADPCM Decoder Bench Mark                                                                                                                                               | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.3                                         | Power Results for IDCT Row Bench Mark                                                                                                                                                    | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.4                                         | Power Results for IDCT Column Bench Mark                                                                                                                                                 | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.5                                         | Power Results for Sobel Bench Mark                                                                                                                                                       | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.5.6                                         | Power Results for Laplace Bench Mark                                                                                                                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | DELA                                          | Y ELEMENTS FOR LOW POWER FABRIC                                                                                                                                                          | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

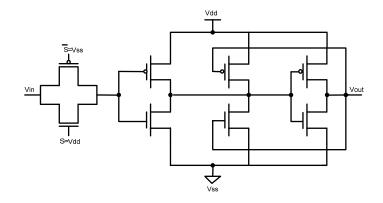

| 6.1 | Ľ                                             | DELAY ELEMENT TOPOLOGIES                                                                                                                                                                 | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.2 | I                                             | OW POWER FABRIC USING DELAY ELEMENTS                                                                                                                                                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

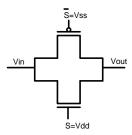

| 6.3 | Т                                             | HYRISTOR BASED DELAY ELEMENT                                                                                                                                                             | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

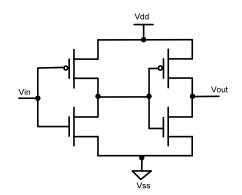

|     | 6.3.1                                         | CMOS Thyristor Concept                                                                                                                                                                   | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

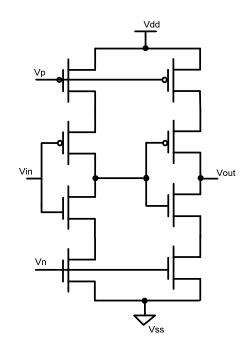

|     | 6.3.2                                         | Dynamic Triggering Scheme                                                                                                                                                                | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 6.3.3                                         | Static Triggering Scheme                                                                                                                                                                 | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 6.3.4                                         | Delay Analysis of the Thyristor Based Delay Element                                                                                                                                      | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

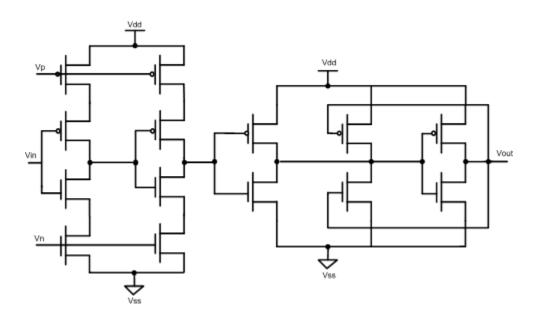

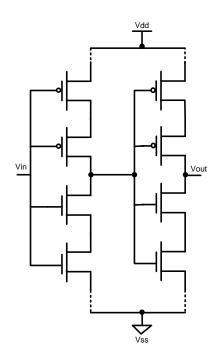

| 6.4 | N                                             | IODIFIED CMOS THYRISTOR DELAY ELEMENT                                                                                                                                                    | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.5 | (                                             | CUSTOM CMOS THYRISTOR DELAY ELEMENT FOR FABRIC                                                                                                                                           | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 6.5.1                                         | Programmability                                                                                                                                                                          | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

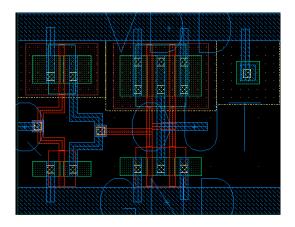

|     | 6.5.2                                         | Layout of the Programmable Delay Element                                                                                                                                                 | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 6.5.3                                         | Parasitic Extraction of the Delay Element                                                                                                                                                | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 6.5.4                                         | Cell Characterization and HSPICE Post-Processing                                                                                                                                         | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | 5.4.2<br>5.5 P<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.5.5<br>5.5.6<br>DELA<br>6.1 C<br>6.2 L<br>6.3 T<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4 N<br>6.5 C<br>6.5.1<br>6.5.2<br>6.5.3 | <ul> <li>5.4.2 BIGFABRIC Automation Scripts</li> <li>5.5 POWER ANALYSIS OF THE CHIP</li> <li>5.5.1 Power Results for ADPCM Encoder Bench Mark</li> <li>5.5.2 Power Results for IDCT Row Bench Mark</li> <li>5.5.3 Power Results for IDCT Column Bench Mark</li> <li>5.5.4 Power Results for IDCT Column Bench Mark</li> <li>5.5.5 Power Results for Sobel Bench Mark</li> <li>5.5.6 Power Results for Laplace Bench Mark</li> <li>6.1 DELAY ELEMENTS FOR LOW POWER FABRIC</li> <li>6.2 LOW POWER FABRIC USING DELAY ELEMENTS</li> <li>6.3 THYRISTOR BASED DELAY ELEMENT</li> <li>6.3.1 CMOS Thyristor Concept</li> <li>6.3.2 Dynamic Triggering Scheme</li> <li>6.3.4 Delay Analysis of the Thyristor Based Delay Element</li> <li>6.5 CUSTOM CMOS THYRISTOR DELAY ELEMENT FOR FABRIC</li> <li>6.5 CUSTOM CMOS THYRISTOR DELAY ELEMENT FOR FABRIC</li> <li>6.5.1 Programmability</li> <li>6.5.2 Layout of the Programmable Delay Element</li> <li>6.5.3 Parasitic Extraction of the Delay Element</li> </ul> |

|     |     | 6.5.5 | Characterization Results for a 4ns delay element 114 |

|-----|-----|-------|------------------------------------------------------|

|     |     | 6.5.6 | Characterization Results for a 5ns delay element 115 |

|     |     | 6.5.7 | Characterization Results for a 7ns delay element 116 |

| 7.0 |     | EEPR  | OM CIRCUIT DESIGN 117                                |

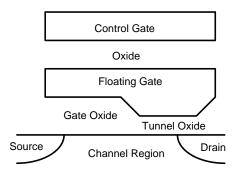

|     | 7.1 | F     | CEPROM CELL 117                                      |

|     |     | 7.1.1 | Erase Operation119                                   |

|     |     | 7.1.2 | Write Operation121                                   |

|     | 7.2 | E     | CEPROM MEMORY ARCHITECTURE 123                       |

|     |     | 7.2.1 | Ramp Generator 129                                   |

|     |     | 7.2.2 | High Voltage Generation Using Charge Pump130         |

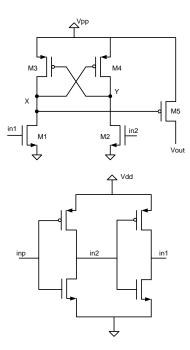

|     |     | 7.2.3 | Word Line Level Shifter                              |

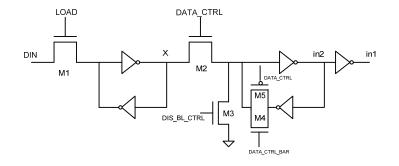

|     |     | 7.2.4 | Column Latch for Bitlines131                         |

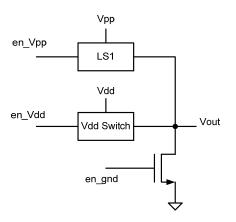

|     |     | 7.2.5 | Power Multiplexer 133                                |

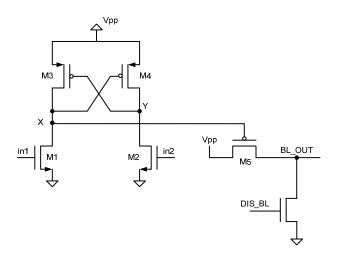

|     |     | 7.2.6 | Sense Amplifier 134                                  |

|     |     | 7.2.7 | Memory Bank Architecture137                          |

|     |     | 7.2.8 | Memory Bank Simulation139                            |

| 8.0 |     | POW   | ER GATED EEPROM DESIGN140                            |

|     | 8.1 | A     | ARCHITECTURE OF THE POWER GATED MEMORY 140           |

|     |     | 8.1.1 | Memory Block with Power Gate142                      |

|     |     | 8.1.2 | Dynamic Decoder143                                   |

|     | 8.2 | N     | MEMORY BLOCK POWER CONSUMPTION 143                   |

|     | 8.3 | P     | POWER-ON RESET145                                    |

|     | 8.4 | F     | RESULTS                                              |

| 9.0    | CONCLUSION |  |

|--------|------------|--|

| APPEND | IX A       |  |

| APPEND | IX B       |  |

| APPEND | IX C       |  |

| APPEND | IX D       |  |

| BIBLIO | GRAPHY     |  |

## LIST OF TABLES

| Table 5-1: ALU Module Specifications                           | 39 |

|----------------------------------------------------------------|----|

| Table 5-2: Specification of the ALU Stripe                     | 41 |

| Table 5-3: ALU Initialization Parameters.                      | 43 |

| Table 5-4: ALU Module Pin Placement Parameters                 | 45 |

| Table 5-5: ALU Horizontal Routing Feedthrough Specification    | 47 |

| Table 5-6: MUX Module Specification                            | 50 |

| Table 5-7: MUX Stripe Specifications                           | 52 |

| Table 5-8: MUX Module Pin Placement Parameters                 | 53 |

| Table 5-9: MUX Stripe Feedthrough Specifications               | 54 |

| Table 5-10: MUX Stripe Pin Placement Parameters                | 55 |

| Table 5-11: FINALMUX Module Specification                      | 56 |

| Table 5-12: Final MUX Stripe Specifications                    | 59 |

| Table 5-13: BIGFABRIC Module Specifications                    | 62 |

| Table 5-14: Reconfigurable Hardware Fabric Chip Specifications | 63 |

| Table 5-15: BIGFABRIC VRF for FINALMUX stripe                  | 68 |

| Table 5-16: BIGFABRIC VRF for ALU and MUX stripe               | 68 |

| Table 5-17: ADPCM Encoder Post Layout Power Simulation         | 73 |

| Table 5-18: ADPCM Decoder Post Layout Power Simulation         | 74 |

| Table 5-19: IDCT Row Post Layout Power Simulation              | 75 |

| Table 5-20: IDCT Col Post Layout Power Simulation              | 76 |

| Table 5-21: Sobel Post Layout Power Simulation                 | 77 |

| Table 5-22: Laplace Post Layout Power Simulation                            | 78  |

|-----------------------------------------------------------------------------|-----|

| Table 8-1: Power Gated Memory Simulation Results                            | 148 |

| Table D 1: Characterization data for 4ns delay element using 160fF buffer   | 184 |

| Table D 2: Characterization data for 4ns delay element using 640fF buffer   | 185 |

| Table D 3: Characterization data for 4ns delay element using 80fF buffer    | 186 |

| Table D 4: Characterization data for a 5ns delay element using 160fF buffer | 187 |

| Table D 5: Characterization data for a 5ns delay element using 640fF buffer | 188 |

| Table D 6: Characterization data for a 5ns delay element using 80fF buffer  | 190 |

| Table D 7: Characterization data for a 7ns delay element using 160fF buffer | 191 |

| Table D 8: Characterization data for a 7ns delay element using 640fF buffer | 192 |

| Table D 9: Characterization data for a 7ns delay element using 80fF buffer  | 193 |

## LIST OF FIGURES

| Figure 1-1: SuperCISC Reconfigurable Hardware Fabric Triangle        | 2  |

|----------------------------------------------------------------------|----|

| Figure 1-2: SuperCISC RHF System Integration Diagram                 | 5  |

| Figure 2-1: Architecture of SuperCISC Reconfigurable Hardware Fabric | 8  |

| Figure 2-2: ALU Logical Diagram                                      |    |

| Figure 2-3: 5:1 MUX Interconnect Structure                           |    |

| Figure 2-4: FINALMUX Stripe Logical Diagram                          |    |

| Figure 3-1: Power Dissipation Terminology Tree                       | 14 |

| Figure 3-2: Schematic of an Inverter                                 |    |

| Figure 3-3: Prime Power Event Based Simulation Flow                  |    |

| Figure 3-4: Leakage Power definition of a NAND Standard Cell         |    |

| Figure 3-5: NLPM definition of Internal Power                        |    |

| Figure 3-6: Rise Power Measurement window                            |    |

| Figure 3-7: HSPICE Rise Power Calculation command                    |    |

| Figure 3-8: Fall Power Measurement window                            |    |

| Figure 3-9: On-state leakage Power Measurement window                |    |

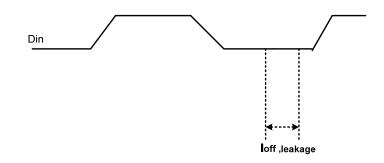

| Figure 3-10: Off-state leakage Power Measurement window              |    |

| Figure 4-1 : Typical ASIC Design Flow                                |    |

| Figure 4-2: ASIC Physical Design Flow                                |    |

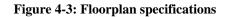

| Figure 4-3: Floorplan specifications                                 |    |

| Figure 4-4: ALU Stripe Floor plan                                    |    |

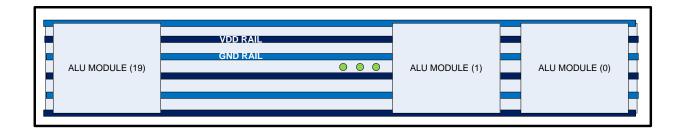

| Figure 4-5: Power Planning                                           |    |

| Figure 4-6: Routing in the absence of Routing Feedthroughs  |    |

|-------------------------------------------------------------|----|

| Figure 4-7: Routing in the presence of Routing Feedthroughs |    |

| Figure 4-8: Placed ALU Module                               |    |

| Figure 4-9: Routed ALU Module                               |    |

| Figure 5-1: Placed and Routed ALU Module                    | 39 |

| Figure 5-2: Logical ALU Stripe                              | 40 |

| Figure 5-3: Floorplan of ALU Stripe                         | 40 |

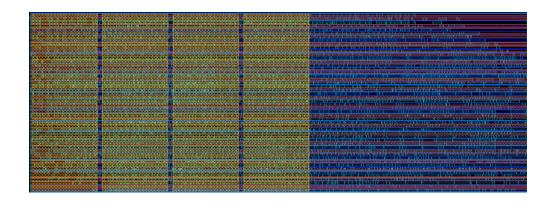

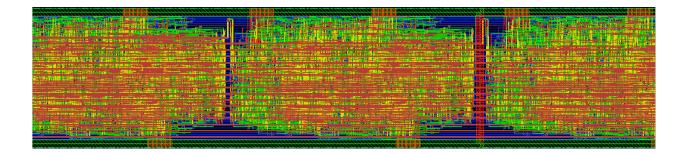

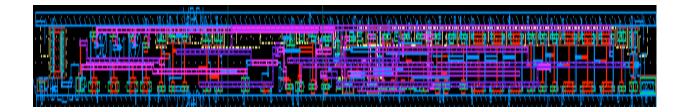

| Figure 5-4: Placed and Routed ALU Stripe                    | 41 |

| Figure 5-5: Zoomed-in view of Placed and Routed ALU Stripe  | 42 |

| Figure 5-6: Default ALU Module Pin alignment                |    |

| Figure 5-7: Early Exit ALU Module Pin alignment             |    |

| Figure 5-8: Normal ALU Stripe Pin assignment                |    |

| Figure 5-9: Specialized ALU Stripe Pin assignment           |    |

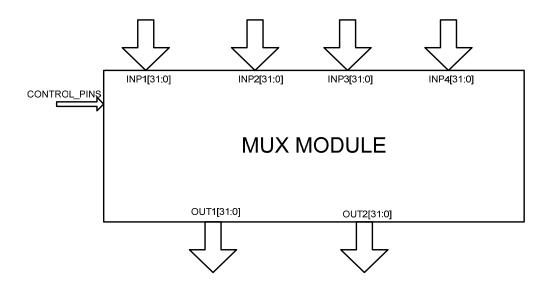

| Figure 5-10: MUX Module Logical Diagram                     | 49 |

| Figure 5-11: Placed and Routed MUX Module                   | 50 |

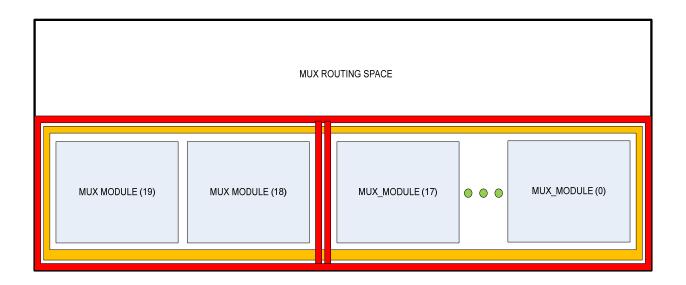

| Figure 5-12: MUX Stripe Logical Diagram                     | 51 |

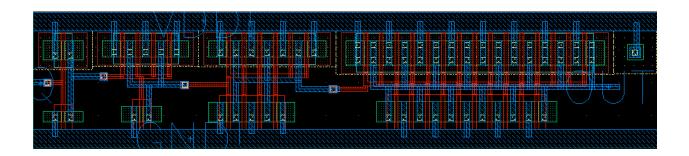

| Figure 5-13: MUX Stripe Floorplan                           | 51 |

| Figure 5-14: Placed and Routed MUX Stripe                   | 52 |

| Figure 5-15: FINALMUX Module Logical Diagram                | 57 |

| Figure 5-16: Placed and Routed FINALMUX Module              | 57 |

| Figure 5-17: Final MUX Stripe Logical Diagram               | 58 |

| Figure 5-18: Final MUX Stripe Floorplan                     | 58 |

| Figure 5-19: Placed and Routed FINALMUX Stripe              | 59 |

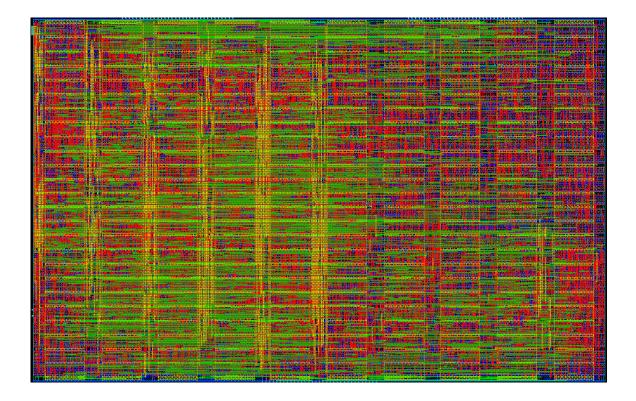

| Figure 5-20: BIGFABRIC Logical Diagram                                      | 65 |

|-----------------------------------------------------------------------------|----|

| Figure 5-21: Top-level routing of the BIGFABRIC                             | 66 |

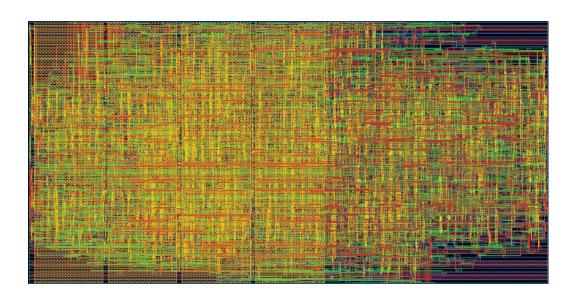

| Figure 5-22: Place and Routed BIGFABRIC in OKI 0.16um                       | 67 |

| Figure 5-23: Modelsim Command for SDF back annotation                       | 70 |

| Figure 5-24: SPEF Annotation in Prime Power                                 | 72 |

| Figure 5-25: Summary of Power Analysis Flow                                 | 72 |

| Figure 6-1: Transmission gate based delay element                           |    |

| Figure 6-2: Transmission Gate with Schmitt Trigger                          |    |

| Figure 6-3 Cascaded inverter based delay element                            | 82 |

| Figure 6-4: NP-Voltage Controlled delay element                             |    |

| Figure 6-5: NP-Voltage Controlled delay element with Schmitt Trigger        |    |

| Figure 6-6: N-Voltage Controlled delay element                              |    |

| Figure 6-7: P-Voltage Controlled delay element                              |    |

| Figure 6-8: Current Starved Cascaded Inverter                               |    |

| Figure 6-9: m-Transistor Cascaded Inverter                                  | 87 |

| Figure 6-10: Staged Cascaded Inverter                                       | 88 |

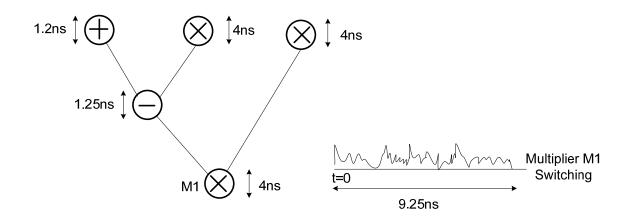

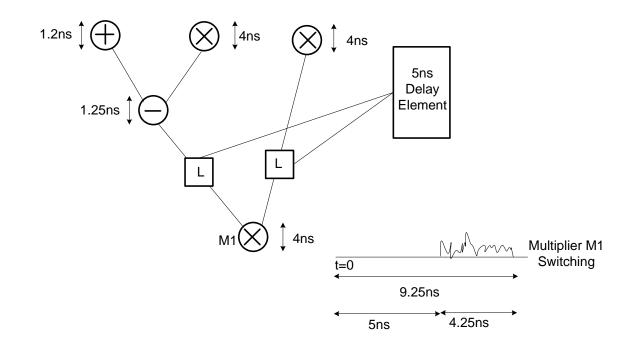

| Figure 6-11: Combinational switching without delay elements                 |    |

| Figure 6-12: Combinational switching with delay elements                    |    |

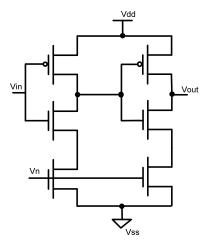

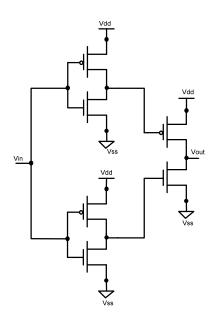

| Figure 6-13: CMOS Thyristor structure                                       |    |

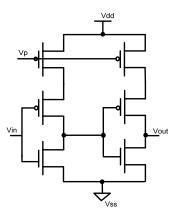

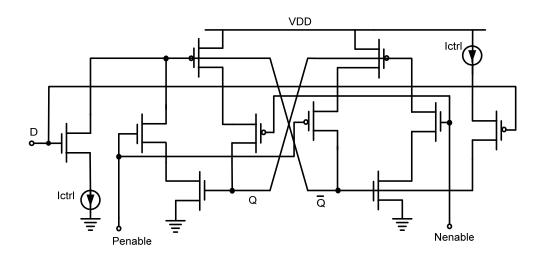

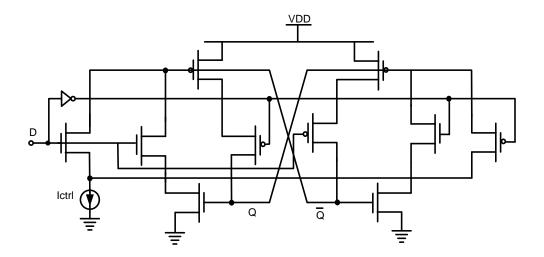

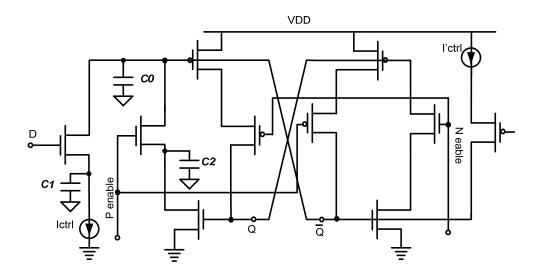

| Figure 6-14: CMOS Thyristor Dynamic Triggering Scheme                       |    |

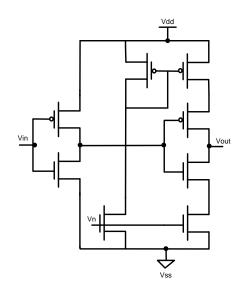

| Figure 6-15: CMOS Thyristor Static Triggering Scheme                        |    |

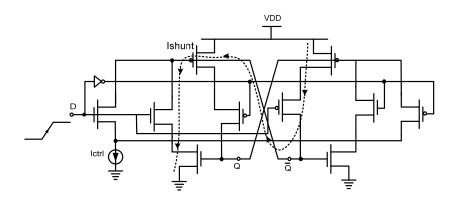

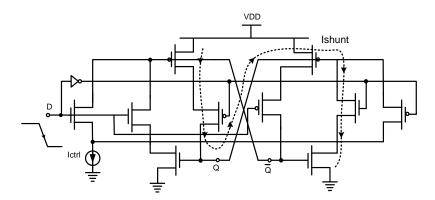

| Figure 6-16: CMOS Thyristor Shunt current when D transitions to a high      |    |

| Figure 6-17: CMOS Thyristor shunt current when D transitions to a logic low |    |

| Figure 6-18: CMOS Thyristor showing Parasitic Capacitances       | 100 |

|------------------------------------------------------------------|-----|

| Figure 6-19: CMOS Modified Thyristor Delay Element               | 101 |

| Figure 6-20: Timing diagram of the modified CMOS delay element   | 102 |

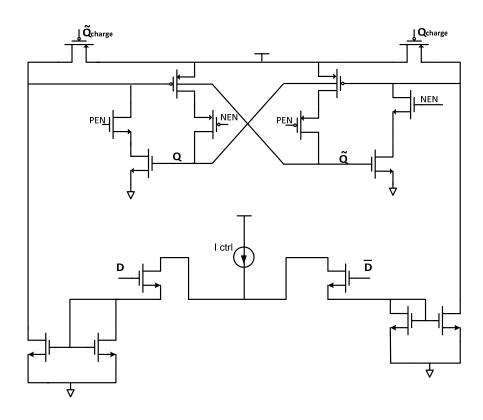

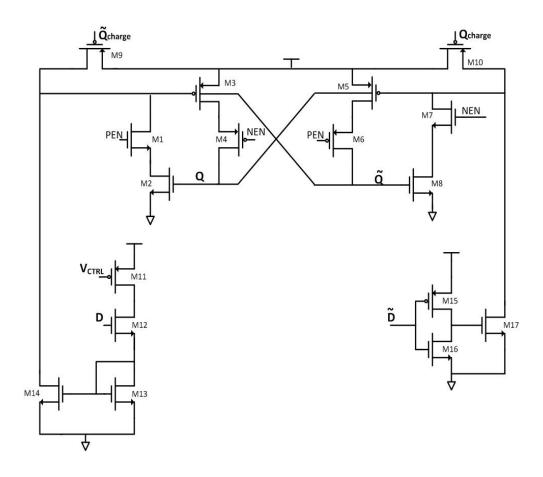

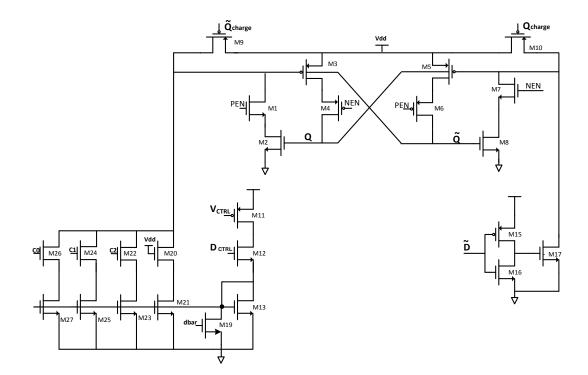

| Figure 6-21: Custom CMOS Thyristor based Delay Element           | 103 |

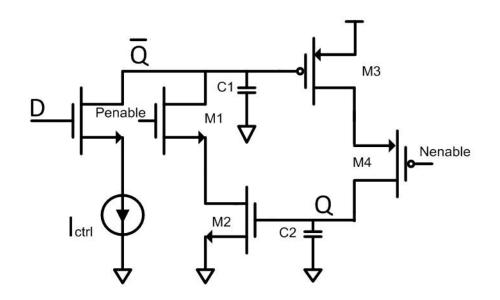

| Figure 6-22: Programmable delay element                          |     |

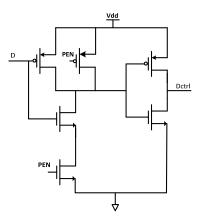

| Figure 6-23: AND gate to generate Dctrl                          | 107 |

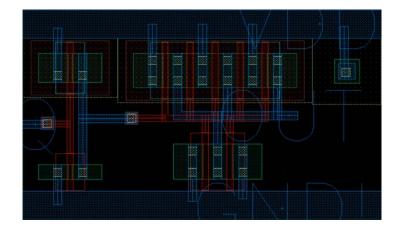

| Figure 6-24: Layout of the Programmable Delay Element            | 107 |

| Figure 6-25: Layout of a 640fF drive Buffer                      | 109 |

| Figure 6-26: Layout of a 160fF drive buffer                      | 109 |

| Figure 6-27: Layout of a 80fF drive buffer                       | 110 |

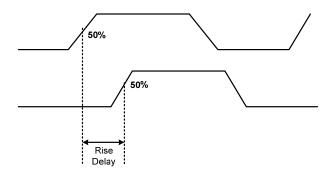

| Figure 6-28: Cell Rise Delay Measurement                         |     |

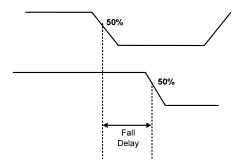

| Figure 6-29: Cell Fall Delay Measurement                         |     |

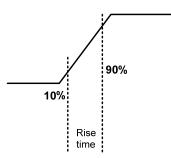

| Figure 6-30: Rise Time Measurement Waveform                      |     |

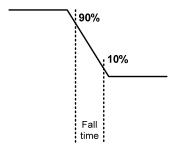

| Figure 6-31: Fall Time Measurement Waveform                      | 113 |

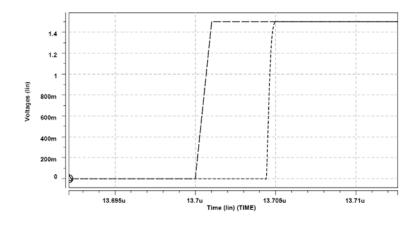

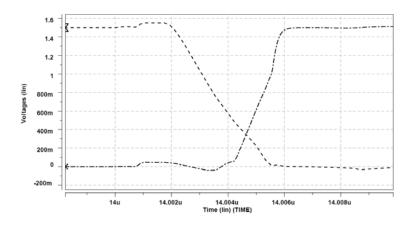

| Figure 6-32: Input and Delayed waveforms for 4ns delay element   | 114 |

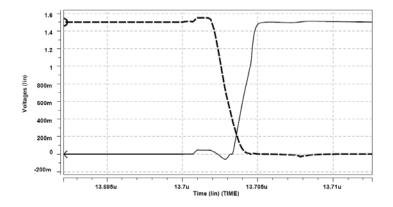

| Figure 6-33: Q and Q~ discharge waveforms for 4ns delay element  |     |

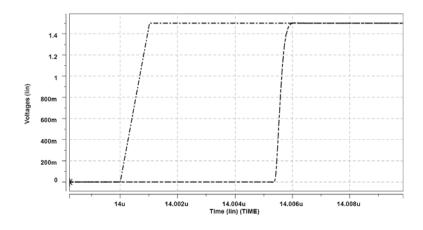

| Figure 6-34: Input and delayed waveforms for a 5ns delay element | 115 |

| Figure 6-35: Q and Q~ discharge waveforms of a 5ns delay element | 115 |

| Figure 6-36: Input and delayed waveforms of a 7ns delay element  |     |

| Figure 6-37: Q and Q~ waveforms of a 7ns delay element           |     |

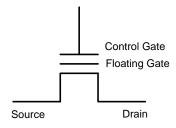

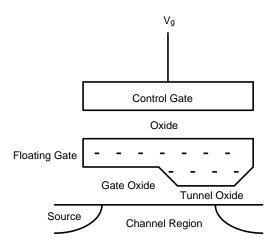

| Figure 7-1: Structure of the FLOTOX Transistor                   |     |

| Figure 7-2: Symbol of a FLOTOX transistor                        |     |

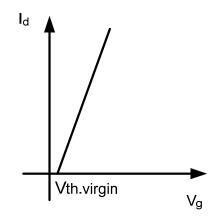

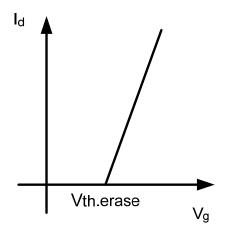

| Figure 7-3: IV Characteristics of a virgin FLOTOX transistor     | 119 |

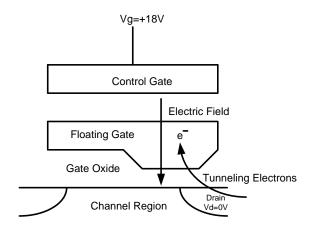

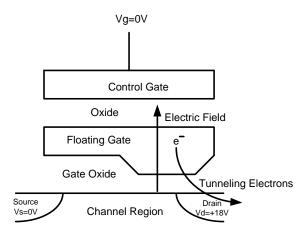

| Figure 7-4: EEPROM Erase Physical Operation                     | 120 |

|-----------------------------------------------------------------|-----|

| Figure 7-5: Charge on Floating Gate after erase operation       | 120 |

| Figure 7-6: IV Characteristics of an erased FLOTOX transistor   | 121 |

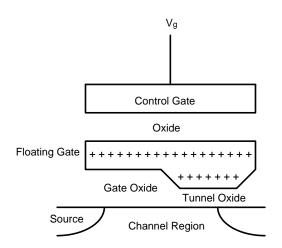

| Figure 7-7: EEPROM Write Physical Operation                     | 122 |

| Figure 7-8: Charge on floating gate after write operation       | 122 |

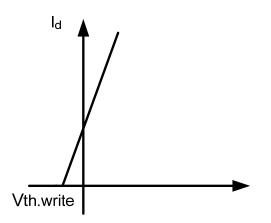

| Figure 7-9: IV Characteristics of a written FLOTOX transistor   | 123 |

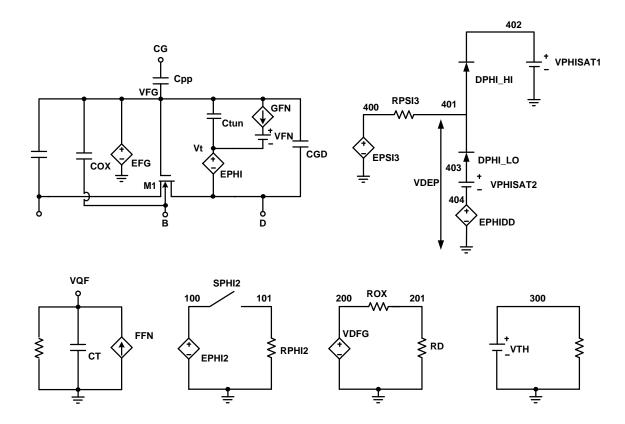

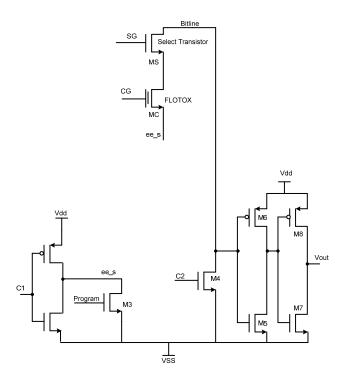

| Figure 7-10: FLOTOX EEPROM Macromodel Schematic                 | 126 |

| Figure 7-11: HSPICE Description of the FLOTOX EEPROM Macromodel | 127 |

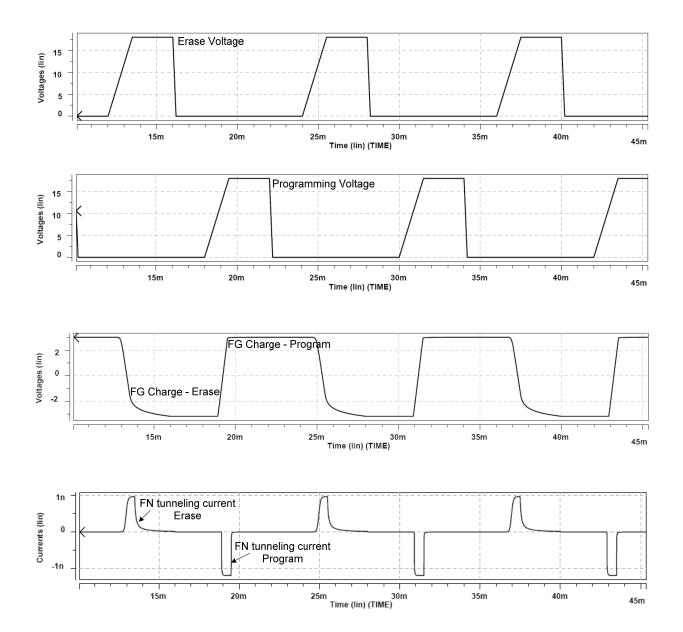

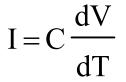

| Figure 7-12: FLOTOX EEPROM Cell HSPICE Simulation               | 128 |

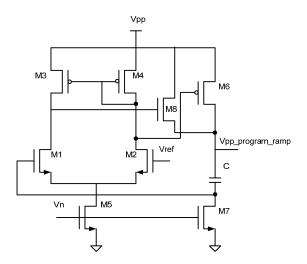

| Figure 7-13: Ramp Generator Schematic                           | 130 |

| Figure 7-14: Schematic of Voltage Level Shifter                 | 131 |

| Figure 7-15: Data Latch Schematic of Column Latch               |     |

| Figure 7-16: Level Shifter and Pass Transistor for Column Latch | 133 |

| Figure 7-17: Power Multiplexer Schematic                        |     |

| Figure 7-18: Sense Amplifier Schematic                          | 135 |

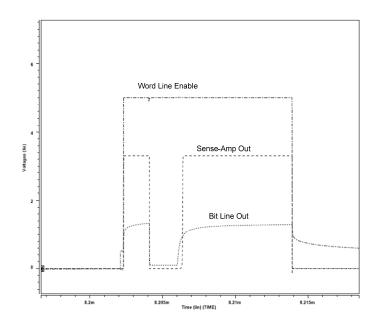

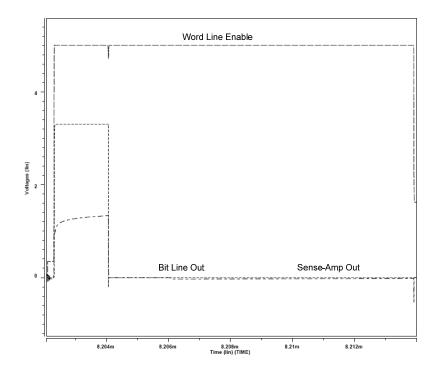

| Figure 7-19: Sense Amplifier Reading a Logic '1'                |     |

| Figure 7-20: Sense Amplifier Reading a Logic '0'                |     |

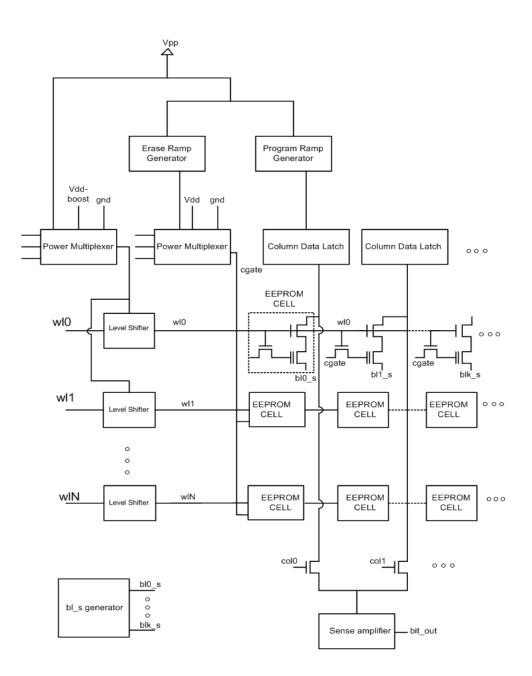

| Figure 7-21: Memory Bank Architecture                           |     |

| Figure 7-22: EEPROM Bank Simulation                             | 139 |

| Figure 8-1: Memory Block with power gate                        | 141 |

| Figure 8-2: Power Gated Memory Design                           |     |

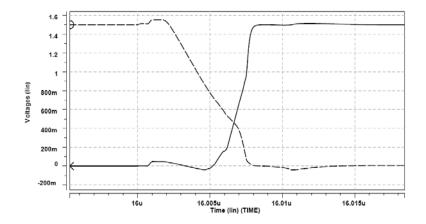

| Figure 8-3: Simulation of Power on condition                    |     |

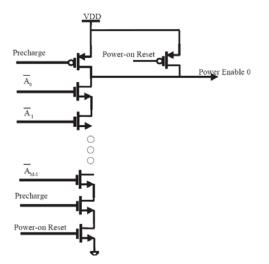

| Figure 8-4: Dynamic Decoder with power-on reset                 |     |

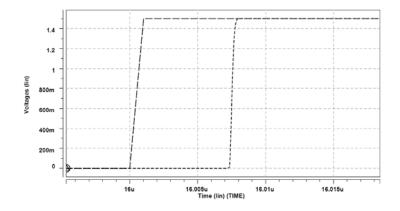

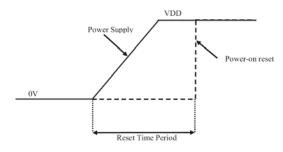

| Figure 8-5: Power-on reset timing diagram   | 147 |

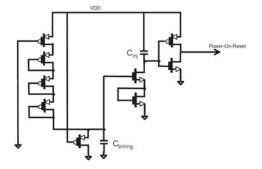

|---------------------------------------------|-----|

| Figure 8-6: Power-on reset circuit          | 147 |

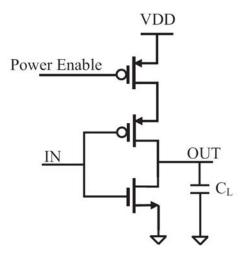

| Figure 8-7: Inverter with power gate.       | 149 |

| Figure 8-8: Power Enable Ramp-up simulation | 150 |

### ACKNOWLEDGEMENTS

"Many, O Jehovah my God, are the wonderful works which You have done, and Your thoughts toward us; There is none to compare with You. If I would declare and speak of them, they would be too numerous to count"

#### Psalm 40:5

As I pen this down, I think of all the great works God has done in my life. As a Father cares for his child, so has He protected and cared for me. All glory and honor be to God who has blessed every work of my hand and has made this education possible. I dedicate this thesis to Lord Jesus Christ who has been my strength throughout my life.

I like to express my sincere gratitude to Dr.Alex K. Jones for giving me an opportunity to work with him on my thesis. He has been a constant source of encouragement throughout the course of the research and has constantly supported my interests in analog circuit design. My sincere thanks for all the help and support he has given throughout the course of my study.

I like to express my thanks to Dr. Steven P. Levitan who has given me a strong foundation for a career in VLSI. The design basics that he has given have taken me a long way. I like to express my thanks to Dr.Jun Yang for being a part of my thesis defense committee and helping me out in my courses. I consider it a great previlege to be a student in many of her classes. I like to express my sincere thanks to my parents Dhanabalan, Alphonse Mary and my wife Pio Clara who have shared my burden and have always encouraged me in my difficult times. Apart from her motivation, I also thank Pio for her valuable technical suggestions. I also like to thank my brothers Charles Daniel and Richard Carol, who have always helped me keep up with the stresses of graduate studies. I also like to thank my uncle Gnanasekar and aunt Anthuvan Grace for their constant support.

I also like to thank Dr.J.T. (Tom) Cain and Sandy Weisberg for their help with all my academic related issues. My special thanks to Sam Dickerson for his help with all HSPICE simulations. I like to thank Bill McGahey who has been the key person to contact customer support to get many CAD tool related issues solved. I also like to thank Gayatri Mehta for her help with the Prime Power simulations and Hariram for his help with the documentation.

I like to thank my friends Suresh and Gopinath who have helped me in my studies. I also like to thank Ajay Ogirala who has always been my "academic yellow pages". I also like to thank my friends Anish, Gladys, Anand, Christy, Joshua, Manoj, Jasmine, Ben, Mekha, Ratnakar, Sabrina, Pastor Dave, Laura, Pastor Prabhu Isaac and family who have always prayed for me.

## **1.0 INTRODUCTION**

Technological advances in multimedia have increased the demand on high performance systems. Hardware acceleration has become a necessity to cope with the challenges in processing speed especially for signal processing applications. On the other hand, market trends have shown that the economic success of a product is primarily determined by its time to market. Design of ASICs (Application Specific Integrated Circuits) based on a standard ASIC flow has always shown better performance and power characteristics at the expense of increased time-to-market.

ASICs are the choice when huge design times can be tolerated [1]. However, with the market for many applications, especially the consumer electronic products being very volatile, it is necessary that these products reach the market faster for a huge return on investment. Such a market driven by design time has led to the increased use of reconfigurable devices. FPGAs (Field Programmable Gate Arrays) are the most commonly used reconfigurable devices. Although FPGAs reduce the design time tremendously, the power consumed by the FPGAs prevents them from being used for battery-powered applications, which demand low power.

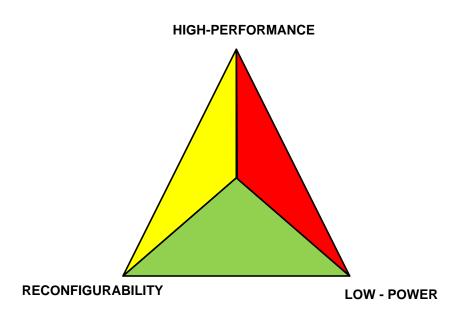

The wireless and mobile market has made the highest impact on the low-power design space. With consumer demands increasing at an exponential rate for low-power electronic gadgets, the research community has interesting opportunities to explore high performance lowpower designs. This interest in developing a high-performance, low-power, reconfigurable hardware device led to the birth of an energy efficient SuperCISC Reconfigurable Hardware fabric. The objective of the SuperCISC RHF research is to develop a hardware design that has a reconfigurable architecture, high performance and low power [2] [3]. The RHF triangle as shown in Figure 1-1 below illustrates the three key design parameters that have been optimized by the design of the SuperCISC RHF.

Figure 1-1: SuperCISC Reconfigurable Hardware Fabric Triangle

The work described in the document is about the physical implementation of the SuperCISC reconfigurable hardware fabric of a specific instance called 20X18. However, automation scripts have been developed to implement other instances of the hardware fabric. The physical implementation of the design is the final stage in the SuperCISC reconfigurable hardware design flow and is one of the most crucial stages in the design flow. The physical design of the SuperCISC RHF is essential to fabricate and commercialize the IP (Intellectual

Property) block. The physical design flow actually transforms the synthesized design into the layout that gets fabricated. Proper design considerations at the layout level are of utmost importance for the commercial success of the IP block.

The pre-layout power characteristics of the IP block, estimated after synthesizing the Verilog/VHDL netlist can use wireload models to model the interconnect parasitics. Such a model could be pessimistic or optimisitic dependent on the vendor library. For an accurate power estimation it is necessary to calculate the power consumed by the chip after placement and routing of the chip has been completed. Also, as the RHF has interconnects which are reconfigurable, it is necessary to understand the power consumed by the interconnects. Hence it is of prime importance to do a post-layout power analysis.

As the objective of the SuperCISC reconfigurable hardware fabric (RHF) is to achieve a low power reconfigurable solution, it is necessary to use custom circuit design techniques to reduce any source of wasteful power consumption in the fabric. As the SuperCISC RHF uses a complete combinational flow, glitching power is inherent to the fabric. The key design technique that has been adopted is to freeze the inputs to the computational units using latches until all the inputs to the computational unit have arrived. The latches are transparent (allow data to pass through) when enabled and hold the previous value when disabled. The 'enable' input to these latches is controlled by a delay element, which times the enabling of the latches. The value of the delay element to be used is determined using STA (Static Timing Analysis) at the mapping stage in the reconfigurable hardware fabric design flow. Hence, delay elements can be used to selftime the design. However, conventional delay elements, like the inverter chain, transmission gate, n or p-voltage controlled delay elements have a limitation on the range of delay that can be obtained. Also the signal integrity of these delay elements is significantly degraded because of the RC characteristics of the delay elements. More importantly, the power consumed by these delay elements is significant because of the short circuit power consumed by the degraded signal integrity or because of the large number of delay elements that are needed to obtain the delay.

Hence it is necessary to use a delay element that can suite the delay range requirements as well as have a low power characteristic. The CMOS thyristor based delay element is such a circuit that possesses good signal integrity properties with a wide delay range and low power. Circuit level changes to minimize the on-state and sub-threshold leakage power consumed by the CMOS thyristor based delay element have been suggested. Also, design techniques to minimize the number of delay elements used in the SuperCISC RHF are essential. So the design has been improved to make the delay element programmable for a specific range of delays.

EEPROMs have become an integral part of modern SoCs to store non-volatile information such as cryptographic keys etc. EEPROMs can be integrated with the SuperCISC reconfigurable hardware fabric to store such non-volatile information. However, the EEPROM needs to have a low power characteristic to save the power gained by the SuperCISC RHF. This thesis proposes a power gated EEPROM architecture level optimization which enables an increase in the size of the EEPROM with a minimum power overhead. A FLOTOX EEPROM macromodel described in HSPICE has been used to simulate the AC and DC characteristics of the EEPROM. Power simulations were then performed on a 2, 4, 8 bank EEPROM architecture to show the minimum power overhead in using the power-gated design.

Thus the objective of this thesis is to do a physical implementation of the SuperCISC reconfigurable hardware fabric and estimate its power characteristics after placement and routing. The thesis also shows the implementation of a CMOS thyristor based delay element that can be programmed for specific delay values to be used in the SuperCISC RHF. The final part of

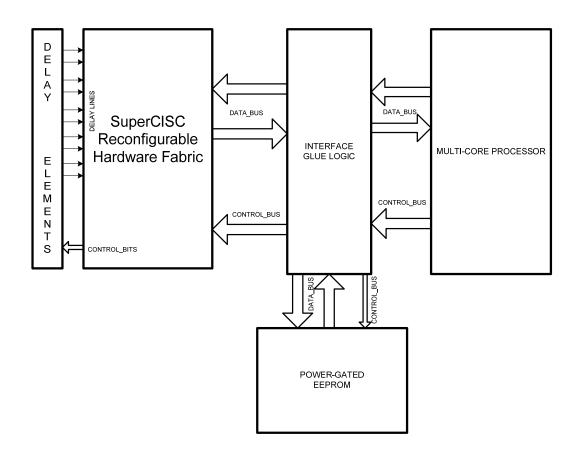

the thesis proposes a power gated memory architectural solution for use with non-volatile memories such as EEPROMs. Figure 1-2 shows the system-level diagram where the SuperCISC RHF, the delay elements and the EEPROM are integrated as part of the SuperCISC architecture. The glue logic interface shown in the figure is used to interface the processor core with the SuperCISC RHF and the power gated EEPROM. The control bits for programming the delay elements are a part of the control bus input to the RHF. Chapters 2, 6 and 8 contain the details of the SuperCISC RHF, delay elements and the power-gated EEPROM respectively.

Figure 1-2: SuperCISC RHF System Integration Diagram

#### **1.1 STATEMENT OF THE PROBLEM**

The physical implementation of the SuperCISC Reconfigurable Hardware Fabric is important for the RHF design to be fabricated and commercialized. Also for an accurate power estimation of the IP block, post layout power analysis needs to be performed. As the objective of the SuperCISC RHF is to consume minimum power, it is necessary that any source of unwanted power consumption be eliminated. As the SuperCISC RHF uses a combinational flow, glitching power is inherent to the fabric. So, specialized circuits like the delay element are needed to time the design to minimize the glitching power. Also for SoCs that use an EEPROM integrated with the SuperCISC RHF, increasing the size of the EEPROM while keeping the active power low is essential. The work described in this thesis shows the methodology used for the physical implementation of the fabric. Also, the design of the CMOS delay element has been described along with the power gating technique used to increase the size of the EEPROM.

My contributions to the thesis have been on the physical implementation of the SuperCISC RHF in the IBM 0.13um CMOS technology. The parasitics extracted from the layout have been annotated to the design to estimate the post layout power consumption. I have also implemented a programmable delay element with delays of 4ns, 5ns and 7ns to be used as a standard cell in the IBM cell library. The standard cell has been characterized for various loads and transition times. To increase the size of the EEPROM while keeping the active power consumption low, a power gated memory solution has been proposed. Power measurements were conducted to show that the power-gated memory solution enables an increase in the size of the memory with a minimum power overhead.

#### 2.0 SUPERCISC RECONFIGURABLE HARDWARE FABRIC

The SuperCISC Reconfigurable Hardware Fabric is a hardware acceleration unit, which can be embedded into the SuperCISC processor architecture [2]. The fundamental idea behind the SuperCISC architecture is to use a processor core to handle the control-intensive part of the code, while the SuperCISC RHF handles the computation intensive parts of the code, called kernels [2]. The kernels are converted into an entirely combinational hardware function generated automatically from C using a design automation flow. Using hardware predication, a Control Data Flow Graph (CDFG) can be converted into a Super Data Flow Graph (SDFG) [3] [4]. SDFG based hardware functions are asynchronous with respect to the processor core. The hardware functions generated by the SDFG get mapped onto the hardware fabric using a mapper. The entire SuperCISC RHF is a purely combinational data flow unit. Removing the sequential logic simplifies the implementation of the SDFG on the hardware fabric. Removal of sequential logic also saves operating power by avoiding clock trees and local storage elements [2]. The objective of the SuperCISC RHF is to provide a reconfigurable device which consumes low energy. The low energy consumed by the device partly comes from the limited programmability available.

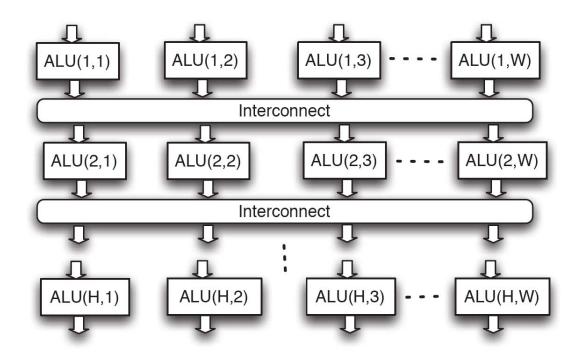

## 2.1 ARCHITECTURE OF THE SUPERCISC RHF

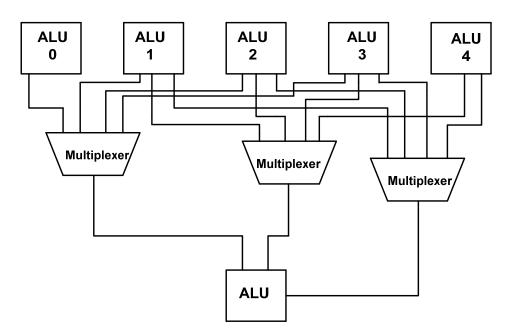

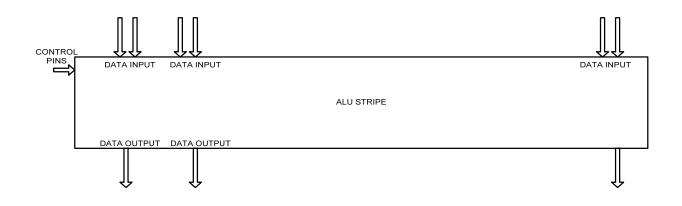

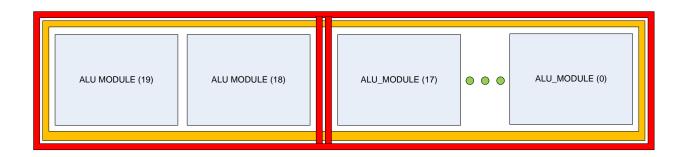

The architecture of the SuperCISC RHF comprises an array of ALUs with interconnects between the rows of the ALU array. Each row in the reconfigurable fabric is called a stripe. The stripe of ALUs is called the *Computational Stripe* and the stripe of multiplexers which form the interconnect logic is called the *Interconnect Stripe*. The multiplexers in the *Interconnect Stripe* can be configured to select the appropriate operands to the ALU [3]. Figure 2-1 shows the architecture of the reconfigurable hardware fabric with computational and interconnect stripes alternating.

Figure 2-1: Architecture of SuperCISC Reconfigurable Hardware Fabric

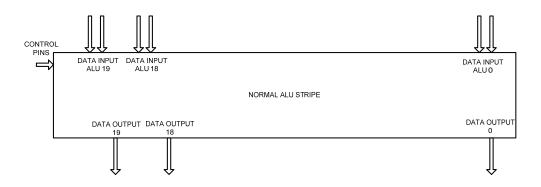

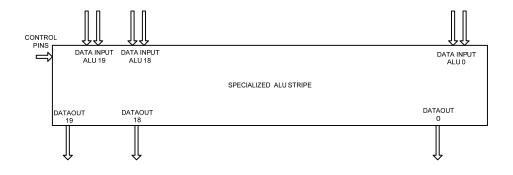

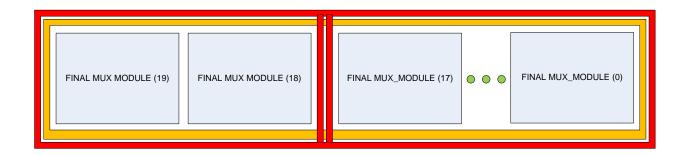

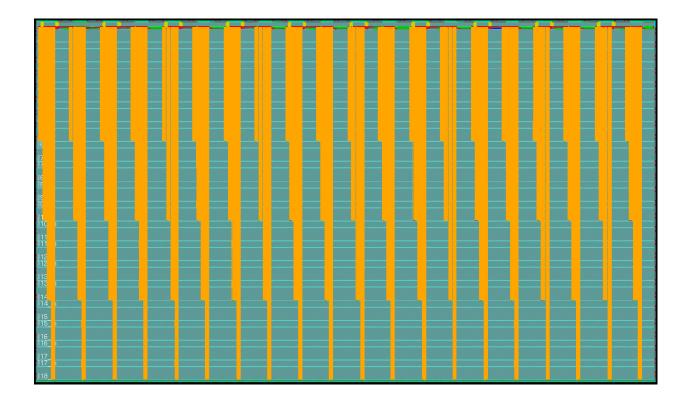

The specifications of the hardware fabric are the number of ALUs per stripe and the number of *Computational (ALU)* stripes. A 20X18 configuration represents a RHF with 20 ALUs per stripe and 18 ALU stripes. The number of multiplexer stripes is one less than the number of the ALU stripes, as the ALU and MUX stripes alternate each other. The final ALU stripe in the design is followed by a special interconnect stripe called the FINALMUX stripe. The FINALMUX stripe has its inputs from the last ALU stripe and from specialized ALU stripes called "early exit" ALU stripes. The FINALMUX stripe multiplexes these inputs to the get the final output of the hardware fabric.

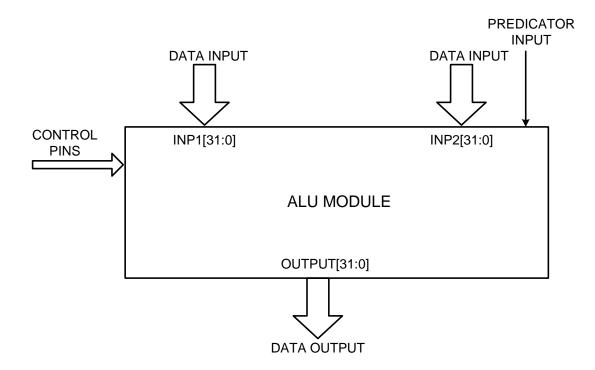

## **2.2** ARITHMETIC AND LOGIC UNIT (ALU)

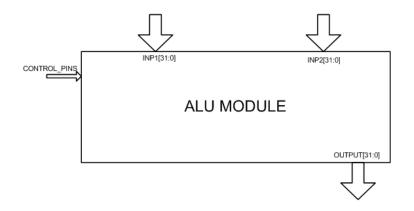

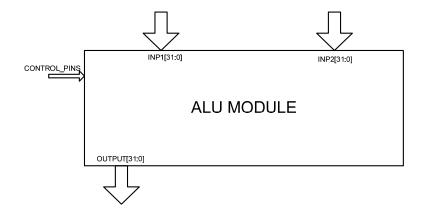

The ALU performs conventional arithmetic and logical operations. In addition to the normal operations, a specialized hardware predication function is implemented within the ALU for implementing SDFGs [3] [4]. This operation requires a third single-bit operand called *predicator input* to be included in the ALU. The predicator input acts as a selector to choose one of the two operands INP1 and INP2 [3]. Figure 2-2 below shows the logical diagram of the ALU used in the hardware fabric. The control pins of the ALU select the logical operation performed by the ALU.

Figure 2-2: ALU Logical Diagram

## 2.3 INTERCONNECT MULTIPLEXER STRUCTURE (MUX)

The multiplexer implements the interconnect structure used to connect the computational stripes. One possible interconnect structure called 5:1 is shown in Figure 2-3. The 5:1 interconnect structure is basically a 5:1 multiplexer that is emulated using 4:1 multiplexers. The 5:1 multiplexer is undesirable from a power and performance perspective. Hence it is good to emulate the behavior using 4:1 multiplexers. The ALU has three operands, INP1, INP2 and the predicator input. Each operand of the ALU has a multiplexer associated with it. The multiplexer for operand INP1 selects from ALU0, ALU1, ALU2 or ALU3. The multiplexer for operand

INP2 selects from ALU1, ALU2, ALU3 or ALU4. The multiplexer for the predicator input is similar to the one for operand INP2.

Figure 2-3: 5:1 MUX Interconnect Structure

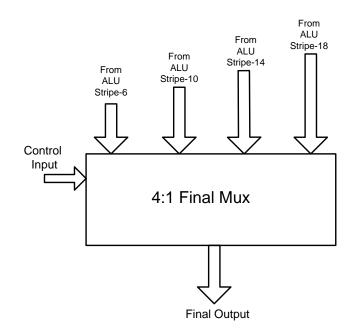

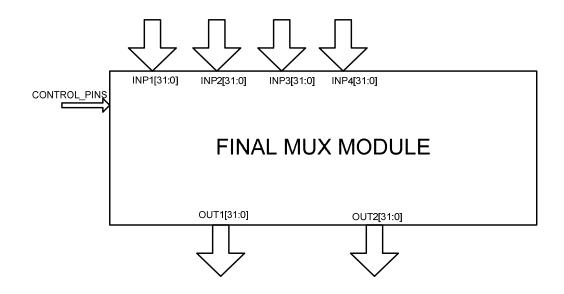

#### 2.4 FINAL MULTIPLEXER STRUCTURE (FINALMUX)

The third component of the hardware fabric is the FINALMUX stripe which is again a multiplexer stripe. The output of the fabric is physically connected to the output of the FINAL MUX stripe. A 4:1 FINALMUX stripe selects one out of four outputs. Let us consider a 20X18 RHF configuration with a 4:1 FINALMUX stripe and an ALU Stripe spacing of 4 as an example. For a 20X18 configuration having 18 computational stripes, the outputs can actually be derived from ALU stripe 6, ALU stripe 10, ALU stripe 14 and ALU stripe 18 for an ALU stripe spacing

of 4. These connections are termed "early exits" and are a hardware provision to bypass the remaining computational stripes, for applications that need not use the remaining computational stripes. The ALU Stripe spacing determines the spacing between the "early exits" in the fabric. Figure 2-4 below shows the logical functionality of the FINALMUX stripe with inputs connected to the outputs of the respective early exits.

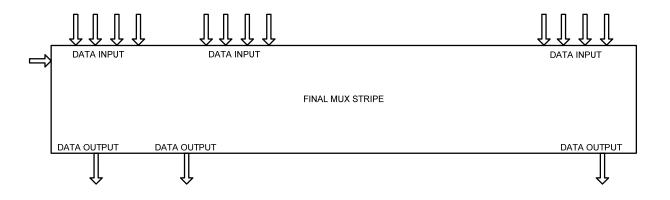

Figure 2-4: FINALMUX Stripe Logical Diagram

## **3.0 POWER ESTIMATION**

The need for electronic gadgets to be mobile has driven the electronics industry for low-power design techniques, starting all the way from architecture level improvements down to transistor layout optimization. As the goal of the SuperCISC reconfigurable hardware fabric is to achieve high performance and low-power, it is necessary to estimate the power consumed by the fabric after synthesis at the pre-layout level as well as after the physical design at the post-layout level stage. This section of the document discusses the power consumption terminologies, the power estimation flow using Synopsys Prime Power and transistor level power estimation techniques for the delay element used in the fabric.

## 3.1 POWER DISSIPATION TERMINOLOGIES

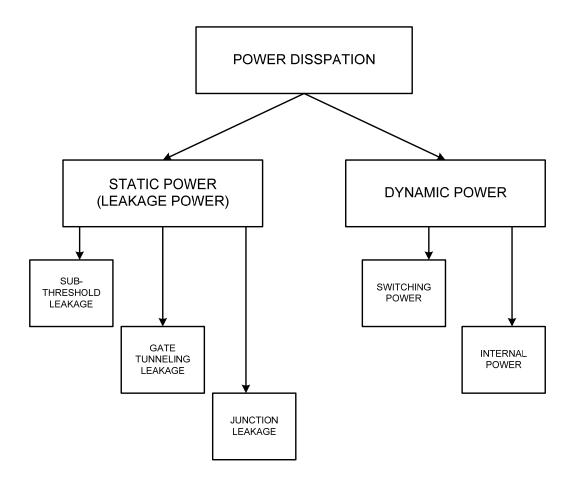

The power consumed by a circuit can be broadly classified into two categories [5]:

- (i) Static Power Consumption

- (ii) Dynamic Power Consumption

Static Power Consumption in a CMOS circuit can be due to variety of sources, sub-threshold leakage, gate tunneling leakage and junction leakage. Dynamic power consumption can be classified into switching power and internal power. The power dissipation terminology tree

shown in Figure 3-1 shows the various components of power that gets dissipated in a CMOS circuit [5]. The subsections discuss in detail about the various terminologies used in the design.

Figure 3-1: Power Dissipation Terminology Tree

#### 3.1.1 Static Power Consumption

Static power is the power dissipated when the gate or circuit is not switching. In other words, the power consumed when the device is static or inactive can be called static power. The primary source of static power comes from the leakage of current from the supply rail to ground through various paths within the circuit. Hence, it has become conventional to refer static power as leakage power.

Sub-threshold leakage has been one of the main sources of leakage in nanometer CMOS technologies. Consider an NMOS transistor as an example. The sub-threshold leakage is due to the current flow from the drain to source of the transistor, even when the gate voltage is set below the threshold voltage of the transistor. This is because of the weak inversion layer that exists in the channel at voltages close to the threshold voltage of the transistor. Sub-threshold leakage has been shown to be the major leakage source in nanometer CMOS technologies. The other sources of leakage include gate tunneling leakage and junction tunneling leakage. Gate tunneling leakage has become an issue with nanometer CMOS technologies because of the reduced gate oxide thickness. Junction leakage is the current flow from the drain or source diffusion region to the body (substrate) terminal of a MOSFET. This leakage current is because of the reverse biased junctions between the source/drain diffusion region and the substrate or the well [6].

## 3.1.2 Dynamic Power Consumption

Dynamic Power is the power dissipated when the circuit is active and switches. Dynamic power can be visualized to be the sum of two components:

- (i) Switching Power

- (ii) Internal Power

## Switching Power

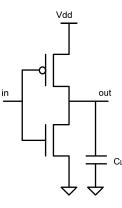

*Switching power* is the power dissipated by the charging and discharging of the load capacitance of the circuit. The switching power of an inverter shown in Figure 3-2 driving a load  $C_L$  is given by Equation 3-1 where *f* is the frequency of operation in Hz,  $C_L$  is the load capacitance in F, and  $V_{dd}$  is the supply voltage in V [7].

Figure 3-2: Schematic of an Inverter

Power (W) =

$$f * C_L * V_{dd}^2$$

#### **Equation 3-1: Dynamic Power of an Inverter**

## **Internal Power**

Internal Power is the power dissipated by the cell because of the charging and discharging of the nodes internal to the cell. In addition to that, short-circuit current that results when both the PMOS and NMOS transistors are ON (as in the case of an inverter) dissipates short-circuit power. This power is also accounted in the internal power consumption. Short-circuit power is a function of the input transition time. For slow transition times, the short circuit power is high as compared with fast transition times because the NMOS and PMOS transistors are simultaneously ON for a longer duration of time. Short circuit power is also influenced by the sizes of the transistors.

## 3.2 PRIMEPOWER POWER ESTIMATION FLOW

Prime power is gate-level power analysis tool for analyzing the power dissipation of standardcell based designs [5]. Prime power supports event-based and statistical activity based power analysis at the gate level.

Event based power analysis uses event driven simulation to calculate the power consumed at every event. Event based power analysis is actually dependent on the input vector and when averaged over a large number of input vectors can give a very accurate estimate of the power consumed by the chip.

Statistical Activity based power analysis uses a probabilistic and statistical estimation algorithm to calculate the average power. It is mostly vector free or has weak vector dependence [5].

17

As event based power analysis was adopted as the design flow for the power estimation of the SuperCISC reconfigurable hardware fabric as it provides accurate time based information [5].

## 3.2.1 Prime Power's Event Based Power Estimation Flow

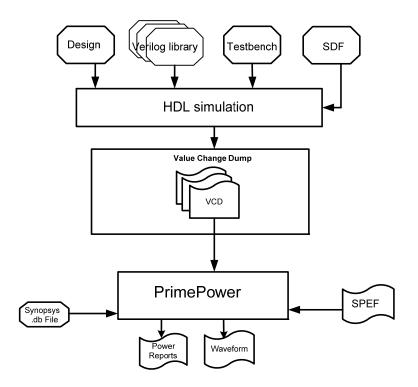

Figure 3-3 shows the event-based simulation flow used by Synopsys Prime Power. PrimePower's simulation flow is comprised of two distinct phases [5]:

- (i) Switching activity Generation

- (ii) Power Profile Generation.

Figure 3-3: Prime Power Event Based Simulation Flow

#### Switching activity Generation

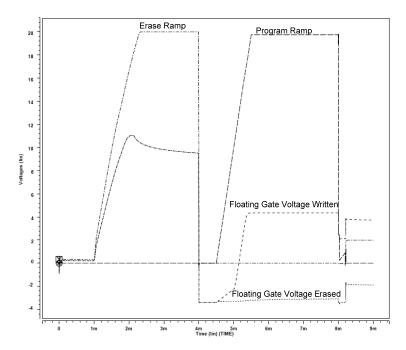

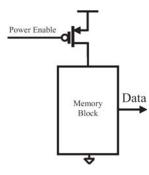

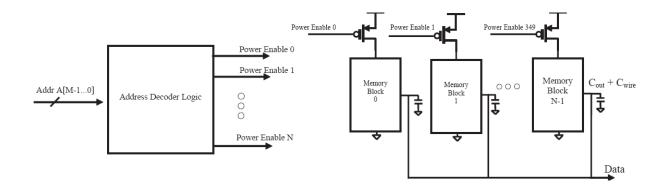

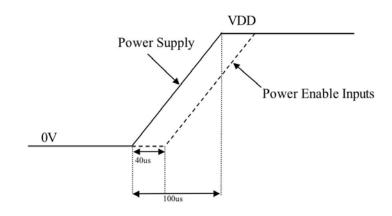

Switching activity generation is an important step in event based power estimation. Switching activity of the circuit is estimated by running a Modelsim simulation of the design using predetermined input vectors. The toggling of nets in the design is captured by the VCD (Value Change Dump) file. While generating the VCD file, the delays after place and route of the design can be annotated using the SDF (Standard Delay Format) file. The SDF file contains the delays of all the cells and interconnects in the design. The SDF file can be generated by the place and route tool like SoC Encounter using the command 'delayCal'.