# AN IMPLEMENTATION OF A THREE DIMENSIONAL COMPUTATIONAL PIPELINE WITH MINIMAL LATENCY AND MAXIMUM THROUGHPUT FOR LU FACTORIZATION USING FIELD PROGRAMMABLE GATE ARRAYS

by

**Edward Thomas Henciak**

B.S.E.E, University of Pittsburgh, 1998

Submitted to the Graduate Faculty of

The Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

University of Pittsburgh

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

**Edward Thomas Henciak**

It was defended on

April 4, 2008

and approved by

Dr. Ronald G. Hoelzeman, Associate Professor, Department of Electrical and Computer

Engineering

Dr. J. Robert Boston, Professor, Department of Electrical and Computer Engineering

Thesis Co-advisor: Dr. James T. Cain, Professor, Department of Electrical and Computer

Engineering

Thesis Co-advisor: Dr. Marlin Mickle, Professor, Department of Electrical and Computer

Engineering

Copyright © by Edward Thomas Henciak

2008

# AN IMPLEMENTATION OF A THREE DIMENSIONAL COMPUTATIONAL PIPELINE WITH MINIMAL LATENCY AND MAXIMUM THROUGHPUT FOR LU

FACTORIZATION USING FIELD PROGRAMMABLE GATE ARRAYS

Edward Thomas Henciak, M.S.

University of Pittsburgh, 2008

Traditionally, computationally intense algebraic functions such as LU factorization are solved using complex systems such as supercomputers, parallel processing systems, and non-dedicated computing clusters. While these solutions are adequate for some problems, they typically suffer from classic parallel processing issues such as communication overhead, complex scheduling algorithms, and cost. Moreover, they are not feasible for embedded applications.

Extremely high performance solutions are sometimes implemented using costly, custom hardware such as Application Specific Integrated Circuits (ASICs). Unfortunately, the design, implementation, and verification of ASICs has become cost prohibitive and such solutions are only feasible if the end design is to be manufactured in very high volumes. As a result, many proposed architectures to solve specific problems lie dormant because they are simply too expensive to realize.

In recent years, advancements in Field Programmable Gate Array (FPGA) technology allow engineers to map complex algorithms to logic gates while achieving performance similar to ASIC technology. This thesis demonstrates the feasibility of the implementation of a three dimensional pipeline designed to solve LU factorization using FPGAs based on an architecture

iv

proposed nearly 10 years ago when a technology to implement such an architecture either did not exist or was too costly to implement.

# TABLE OF CONTENTS

| 1.0 |     | INTRODUCTION1                                              |

|-----|-----|------------------------------------------------------------|

|     | 1.1 | OVERVIEW OF THE PROBLEM1                                   |

|     | 1.2 | THESIS OBJECTIVE 3                                         |

|     | 1.3 | OUTLINE OF THE THESIS6                                     |

| 2.0 |     | THE LU FACTORIZATION PROBLEM ON COMPUTING PLATFORMS 7      |

|     | 2.1 | PARALLEL PROCESSING SYSTEM WITH SHARED MEMORY9             |

|     | 2.2 | PARALLEL PROCESSING WITH DISTRIBUTED MEMORY 12             |

|     | 2.3 | NETWORK DISTRIBUTED CLUSTER PROCESSING 15                  |

|     | 2.4 | PARALLEL PROCESSING SYSTEM-ON-A-CHIP 18                    |

|     | 2.5 | DEDICATED PROCESSING LOGIC21                               |

| 3.0 |     | THE THREE DIMENSIONAL LU FACTORIZATION PIPELINE24          |

|     | 3.1 | THREE DIMENSIONAL ARCHITECTURE OVERVIEW25                  |

|     |     | 3.1.1 3D Pipeline Example                                  |

|     | 3.2 | HARDWARE SELECTION33                                       |

|     | 3.3 | DESIGN FLOW OVERVIEW 35                                    |

| 4.0 |     | DESIGN, IMPLEMENTATION AND VERIFICATION OF THE PIPELINE 37 |

|     | 4.1 | IEEE 754 FLOATING POINT PRIMITIVES 37                      |

|     |     | 4.1.1 Floating Point Logic Creation                        |

|      |      | 4.1.2 | Floating Point Logic Utilization                       | 44 |

|------|------|-------|--------------------------------------------------------|----|

|      | 4.2  | P     | IPELINE AND TEST CIRCUITRY DEVELOPMENT                 | 46 |

|      |      | 4.2.1 | Multiply-Subtract Component                            | 46 |

|      |      | 4.2.2 | Crout Matrix Stage Component                           | 48 |

|      |      | 4.2.3 | Complete Crout Pipeline and Associated Test Circuitry  | 52 |

|      | 4.3  | P     | IPELINE AND TEST CIRCUITRY SIMULATION                  | 56 |

|      | 4.4  | S     | YSTEM SYNTHESIS                                        | 62 |

|      |      | 4.4.1 | Pipeline "Test Synthesis"                              | 62 |

|      |      | 4.4.2 | Xilinx EDK and Microblaze                              | 64 |

|      |      | 4.4.3 | Full System Synthesis                                  | 66 |

|      | 4.5  | Н     | ARDWARE VERIFICATION                                   | 67 |

|      |      | 4.5.1 | Software testing                                       | 68 |

|      |      | 4.5.2 | Internal hardware probing                              | 70 |

|      | 4.6  | II    | MPLEMENTATION AND VERIFICATION EPILOGUE                | 73 |

| 5.0  |      | FUTU  | RE WORK AND CONLUSIONS                                 | 74 |

|      | 5.1  | F     | UTURE WORK                                             | 74 |

|      |      | 5.1.1 | Floating Point Core Limitations and Exception Handling | 75 |

|      |      | 5.1.2 | Fully Systolic Operation                               | 76 |

|      |      | 5.1.3 | Resource Utilization                                   | 78 |

|      |      | 5.1.4 | Design Partitioning                                    | 82 |

|      |      | 5.1.5 | FPGA Based Distributed Computing Clusters              | 84 |

|      | 5.2  | C     | ONCLUSION                                              | 87 |

| A PI | PENI | )IX A |                                                        | 88 |

| BIBLIOGRAPHY | . 99 |

|--------------|------|

|--------------|------|

# LIST OF TABLES

| Table 1 : Resor | arce Estimation | <br> | . 45 |

|-----------------|-----------------|------|------|

# LIST OF FIGURES

| Figure 1: Mathematical Representation of LU Factorization as detailed in [1]                |

|---------------------------------------------------------------------------------------------|

| Figure 2: LU Factorization (Crout Elimination) pseudocode                                   |

| Figure 3: Example matrix from the Chen-Hu architecture and resulting data structure         |

| Figure 4: Task model and resulting task graph that is mapped to processors in the system 11 |

| Figure 5: Rectangular processing array                                                      |

| Figure 6: Tree example                                                                      |

| Figure 7: Distributed Computing Cluster [5]                                                 |

| Figure 8: Binary tree of processors from [11]                                               |

| Figure 9: Linear array solution presented in [12]                                           |

| Figure 10: Dataflow of architecture presented in [12]                                       |

| Figure 11: Crout loop unrolled for the 4x4 case26                                           |

| Figure 12: Crout 3D pipeline                                                                |

| Figure 13: Overview of the 3x3 example                                                      |

| Figure 14: Dataflow for matrix stage 1                                                      |

| Figure 15: Second matrix stage of the 3x3 example                                           |

| Figure 16: The Xilinx ML506 development kit                                                 |

| Figure 17: Xilinx Coregen Floating Point Selection Menu                                     |

| Figure 18: Floating point precision menu                                                   | 41 |

|--------------------------------------------------------------------------------------------|----|

| Figure 19: Floating point performance vs. area tradeoffs                                   | 42 |

| Figure 20: Single stage of 3D pipeline                                                     | 47 |

| Figure 21: Conditional component instantiation for Crout pipeline (divide).                | 49 |

| Figure 22: Conditional component instantiation for Crout pipeline (multiply-subtract)      | 50 |

| Figure 23: Conditional component instantiation for Crout pipeline (pass current element)   | 51 |

| Figure 24: 5x5 Crout Pipeline Instantiation                                                | 53 |

| Figure 25: Block Diagram of Crout Pipeline Test Circuit                                    | 55 |

| Figure 26: Testbench block diagram                                                         | 57 |

| Figure 27: Pipeline simulation results                                                     | 59 |

| Figure 28: Close up of stage to stage sequencing                                           | 60 |

| Figure 29: Simulation console as results are read from memory                              | 61 |

| Figure 30: Pre "full system" synthesis results                                             | 63 |

| Figure 31: EDK session showing a simple processor system                                   | 64 |

| Figure 32: Complete synthesis hierarchy with Microblaze System                             | 65 |

| Figure 33: Final system synthesis results                                                  | 67 |

| Figure 34: Output to console from system                                                   | 69 |

| Figure 35: Chipscope node probing                                                          | 71 |

| Figure 36: Results of Chipscope Session                                                    | 72 |

| Figure 37: Function to compute flip flops required for the divide function                 | 79 |

| Figure 38: Function to compute LUTs required for the divide function                       | 79 |

| Figure 39: Function to compute flip flops required for the multiply-then-subtract function | 80 |

| Figure 40: Function to compute LUTs required for the multiply-then-subtract function       | 80 |

| Figure 41: Function to compute DSP48 slices required for the multiply function  | . 80 |

|---------------------------------------------------------------------------------|------|

| Figure 42: Function to compute LUTs required for the FWD function               | . 81 |

| Figure 43: Total number of flip flops required for "non-systolic" FWD functions | . 82 |

| Figure 44: The SGI Reconfigurable Application Specific Computing (RASC) RC100   | . 85 |

#### 1.0 INTRODUCTION

#### 1.1 OVERVIEW OF THE PROBLEM

As demand for computational performance increases, new technologies and data processing architectures are required. While traditional, programmable CPUs obviously work extremely well for many real world applications, some problems are only "realistically" solved using custom hardware solutions.

A programmable CPU is not designed to be the optimal solution for *application specific* problems but rather flexibility. Programmable CPUs, at best, can only emulate what an application specific solution could provide without the resulting performance gains. As a result, engineers develop custom hardware solutions for these application specific problems when warranted.

Unfortunately, custom hardware solutions tend to have problems of their own. A countless number of custom computing architectures have been proposed over the years. However, the underlying technologies required to implement these computing architectures are either too primitive, cost prohibitive or simply do not exist at the time they are devised. As a result, most of these architectures lie dormant simply waiting to be realized so that their full potential can be unleashed.

Fortunately, the past ten years has seen explosive growth in Field Programmable Gate Array (FPGA) technology. In the past, the need for high speed digital circuits typically translated into a requirement for an Application Specific Integrated Circuit (ASIC). Not only do ASICs have significant costs in terms of manufacturing, they also require a significant amount of manpower for realization of the device. Modern ASICs require teams of engineers to design, implement, and verify a complex digital system.

FPGAs lighten this manpower requirement in that they are reconfigurable computing platforms: they do not require the verification efforts ASICs require nor do they require the up front costs involved with ASIC manufacturing. If a problem is discovered in an FPGA design, the problem can be fixed without having to remanufacture the device.

More importantly, FPGAs have achieved a level of performance on par with ASICs. For example, the Xilinx Virtex 5 SXT device provides the end user with DSP MAC functions capable of running up to 550MHz as well as high speed serial transceivers running at 3.2Gbps [1]. Similar performance is available by competing products from other FPGA vendors such as Altera and Lattice Semiconductor. The end result is that many custom, high performance computing platforms can now be realized with little risk and lower cost.

Despite this technology providing vast, new computing resources, skeptics may still question the overall feasibility of such a technology. As a result, this thesis aims to demonstrate the application of FPGAs on an architecture proposed almost ten years ago [1] when a technology for implementing the proposed architecture either did not exist, or existed but was far too cost prohibitive to implement at the time. More importantly, this particular application and architecture has significant potential for use in modern, real time, embedded systems.

#### 1.2 THESIS OBJECTIVE

Solutions to complex mathematical problems have always been a driving force behind the explosive growth in computing platforms. Obviously, as more computation power is available to end users, more complex problems can be solved. However, not all of these problems are best solved on traditional, programmable CPUs. Some problems, especially those that require solutions in real time, are best solved using other means.

This thesis examines the problem of a complex mathematical problem, LU factorization, as well computational solutions that exist for this problem. Subsequently, this thesis also demonstrates the implementation of a proposed, high performance architecture that solves the LU factorization problem using a 3D systolic array in a modern FPGA device.

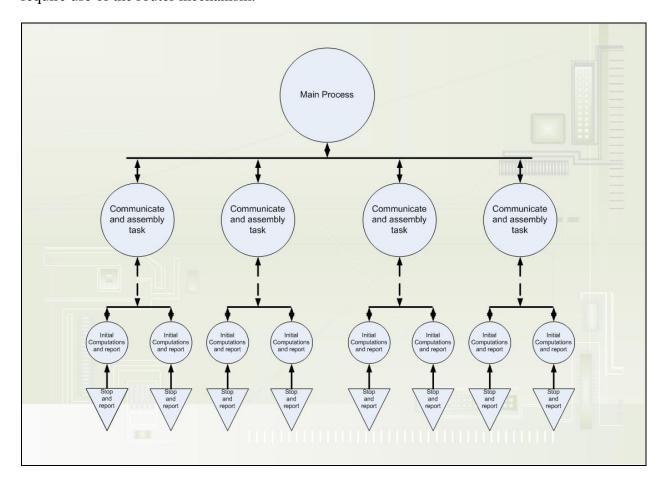

In the past, solutions that previously relied on parallel, Von Neumann processing systems were typically implemented on distributed computing platforms where a mathematical problem is decomposed into several smaller tasks. These smaller tasks are subsequently assigned to various processing elements available in the system. Once the processing elements have completed their task, the results are reported back to a host. Once the host assembles the results, a final solution is reported and the system is free to work on the next problem.

Problems exist with distributed computing methodology with the first being communication bottlenecks. Typically, distributed systems of the past tend to use slower communications protocols relative to their potential computing power. For example, a modern CPU might appear to have more than enough processing bandwidth to solve the partial solutions

of any given parallel processing problem. However, the communications bandwidth available to the system might restrict the usefulness of the CPU.

Next, distributed systems tend to suffer from communication overhead. For example, a typical Ethernet packet contains several bytes of header information and requires several bus transactions with the Ethernet peripheral interface on the system bus. The end result is degraded performance due to the communication link since the Ethernet peripheral is typically running at a speed far less than the processing power of the CPU. Moreover, the bus where the peripheral resides is typically shared with other peripherals thus reducing overall system bandwidth.

Finally, the linear CPUs in the distributed systems typically execute some kind of operating system. Some of the processor's time is interrupted to service other tasks required to maintain CPU operation. While most of these tasks are taken into account when evaluating communication performance, some potential performance is lost simply due to the operating system requirement.

Overall, the objective of this thesis is to demonstrate that a radically different solution to the LU factorization problem can be implemented using modern, custom hardware technology. Instead of mapping the LU factorization algorithm to a distributed, linear computing system, it is now possible to create a custom hardware pipeline using FPGA technology. Not only can this architecture be implemented, an LU factorization problem can be solved in an optimal number of cycles.

In the past, this solution was not feasible given the low gate densities of FPGAs, but modern FPGA devices are well suited for the computationally intense task of LU factorization. This thesis demonstrates the implementation of an algorithm proposed by Dr. Joann Paul and Dr. Marlin Mickle of the University of Pittsburgh [1] that is virtually impossible to implement with

significant performance gains on linear CPUs, but is straightforward to implement on a modern FPGA, and discusses performance compared to distributed, linear CPUs as well as other LU factorization solutions.

#### 1.3 OUTLINE OF THE THESIS

Chapter 2 of this thesis reviews literature leading to the support of FPGA technology as a viable candidate for implementing the massively parallel processing solution the 3D Pipeline for LU factorization requires. It is intended to give the reader an idea of various solutions that have been explored over the past 20 years. Chapter 3 defines the problem and details the approach used to solve the problem using FPGA technology. Chapter 4 details the results of the work described and outlined in Chapter 3. Finally, Chapter 5 presents conclusions and details potential future work.

#### 2.0 THE LU FACTORIZATION PROBLEM ON COMPUTING PLATFORMS

LU factorization of matrices is computationally intense. The process is highly iterative in nature when implemented on a traditional, Von Neumann central processing unit. Consider the following mathematical representation of LU factorization.

$$t_{ij} = \frac{1}{s_{ii}} \left( a_{ij} - \sum_{k=1}^{i-1} s_{ik} * t_{kj} \right)$$

$$s_{ij} = a_{ij} - \sum_{k=1}^{j-1} s_{ik} * t_{kj}.$$

Figure 1: Mathematical Representation of LU Factorization as detailed in [1]

Overall, the following mathematical function can be represented in computer wording using the following pseudo code. The variable N is equal to the size of the matrix (i.e. if N=4, then the matrix is 4x4).

```

for i in 1 to (N-1)

for j in (i+1) to N

A(i,j) = A(i,j)/A(i,i);

end

for k in (i+1) to N

for j in (i+1) to N

A(j,k) = A(j,k) - A(j,i)*A(i,k);

end

end

end

```

Figure 2: LU Factorization (Crout Elimination) pseudocode

The end result of this procedure is a square matrix with the resulting s and t matrices both above and below the diagonal. The s and t matrices are subsequently used to solve sets of linear simultaneous equations through back substitution. Unfortunately, the above algorithm requires a substantial number of cycles to process matrices on traditional CPUs. Each multiply, subtract, and divide requires time. The amount of time is variable depending on the precision of the data being processed. The loops also introduce conditionals which require the CPU to execute many compare operations to determine if branching is required.

However, the potential for parallelism exists in the algorithm and researchers have exploited this parallelism in various projects. This chapter aims to review the work that has been

done with implementing parallel solutions to address the LU factorization problem. Moreover, this chapter demonstrates how this parallelism has migrated from banks of CPUs to single, programmable logic devices over the past two decades.

#### 2.1 PARALLEL PROCESSING SYSTEM WITH SHARED MEMORY

One potential application for LU factorization algorithms is circuit simulation. Back in 1988, researchers at the Southern Methodist University as well as the University of Wisconsin examined the use of a Sequent Balance 21000 computing cluster for circuit simulation [2]. This particular system uses up to 10 processors running Unix with a single, shared memory. Overall, various circuits are used to evaluate the performance of the system.

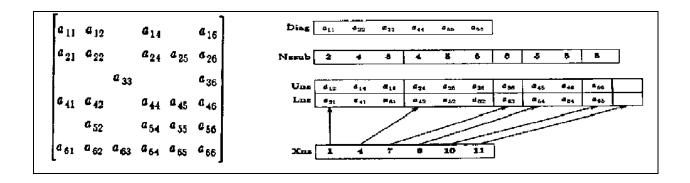

The system is responsible for assembling a solution matrix based on the circuit that requires simulation. LU Factorization is used to solve this solution matrix. Once the solution matrix is created, a data structure (see Figure 3) is created in memory that represents the diagonal entries vector (DIAG), nonzero off-diagonal entries subscripts (NZSUB), the nonzero upper triangular entries vector row by row (UNZ), the nonzero lower triangular entries vector column by column (LNZ), and the index of the start of nonzero values in each column/row of LNZ/UNZ and NZSUB.

Figure 3: Example matrix from the Chen-Hu architecture and resulting data structure

Once the data structure is assembled, the CPU must now label the tasks required to solve the matrix and map these tasks to various processors in the system. It is important to note that, even at this point, the solution of the matrix has not commenced! The data structure described in Figure 3 only facilitates scheduling of tasks that are candidates for parallel execution. After the graph of these tasks is created, the scheduler can now instruct the processors to begin computing the final solution.

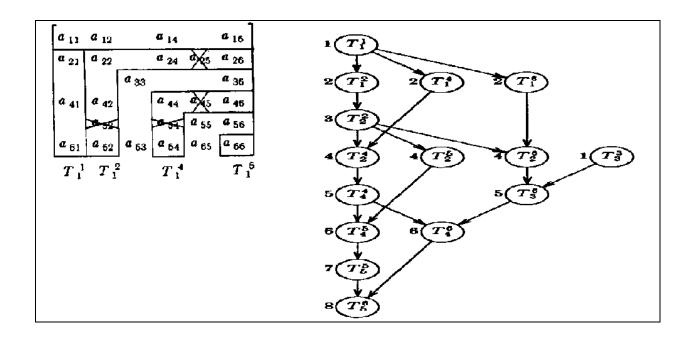

Figure 4: Task model and resulting task graph that is mapped to processors in the system.

Overall, the researchers found significant performance increase when mapping the LU factorization algorithm to parallel processing elements. For example, in the case of a 150 node simulation, performance was increased by a factor of 6.5 when using a 10 processor system when compared to a sequentially executing algorithm. The same algorithm running on a five processor configuration yielded an improvement factor of 4.16.

While a performance increase is observed, it is important to consider all the tasks involved to solve the matrix. To recap, the system must assemble the data structure based on the matrix, assign task clusters to processors, label each task in the task graph, and form a task queue. This is a significant amount of overhead. Moreover, the researchers admit that "the critical path scheduling, in this case, will require a large amount of synchronizing semaphores and hence result in large overhead." [2] The system suffers from other communication overhead

such as interrupts, memory contention, and indirect accesses to nonzero entries. Finally, given the shared memory architecture of the system, it is virtually impossible to pipeline seeing that a new solution cannot commence until the previous solution has been solved. Throughput is rather low in such a system for these reasons.

#### 2.2 PARALLEL PROCESSING WITH DISTRIBUTED MEMORY

The solution described in the previous section suffered from a serious bottleneck: memory contention and communication issues. Of course, alleviating these problems will yield better system performance. In 1992, researchers at the Supercomputing Research Center in Bowie, MD created a system to solve LU factorization on a MasPar MP-1 parallel processing system [3]. Using this system, a new way of mapping data and computations to processors is used, and reasonable processor utilization is obtained even for "unstructured" sparse matrices. The sparse problem is decomposed into many smaller, dense sub-problems, with low overhead for communications and memory access.

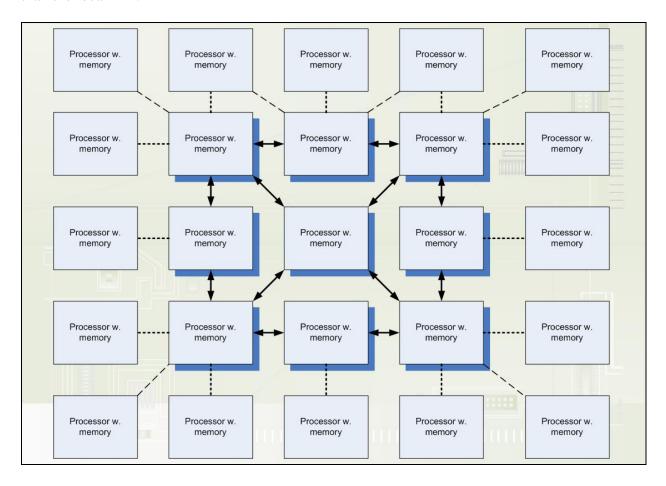

The MP-1 is a distributed memory system. Overall, this system alleviates one of the bottlenecks seen in the previous chapter: shared memory. Instead of multiple CPUs competing for memory access, each CPU uses its own memory space. Of course, some communication bandwidth is required to load each processor's shared memory; however, this bandwidth is virtually negligible when compared with the daunting task of LU factorization.

The processor array in the MP-1 is a rectangular array. Each processor has a low latency link to communicate with its eight nearest neighbors as well as a broadcast function to send specified row (column) elements across the entire row (column) [3]. This "mesh based"

communication is available to drastically reduce any inter-processor communication. Obviously, so long as a processor is communicating with a nearest neighbor processor, communication overhead is kept to a minimum. In the event a processor needs to communicate with a non-neighbor, a router is available, but the communication cost associated with the router is higher than the local link.

Figure 5: Rectangular processing array

Similar to the architecture discussed in the previous section, the system requires the LU Factorization problem to be broken down into a graph. In the case of this research, the tasks are mapped to an elimination tree. Moreover, tasks are mapped such that all inter-processor

communication requirements are constrained to the high speed nearest neighbor and do not require use of the router mechanism.

Figure 6: Tree example

In the tree example seen in Figure 6, one processor is responsible for decomposing the matrix into subtasks. Navigating down the tree, these tasks are assigned to processors in the rectangular processing array. In LU factorization, some results are required from other tasks before computation can commence. These required computations as well as matrix elements are forwarded down the tree. Eventually, the tasks are decomposed such that a processor is able to perform computations that are not dependent on previous solutions being available. As a result,

these child tasks stop processing and begin reporting their results back to their parent tasks. As the solutions begin navigating up the tree, the intermediate calculations are performed until all results are communicated to the main process. At this point, the main task has the solution to the factorization.

The researchers indicate that their method was tested on a 64x64 processor array. Overall, they indicate that the decomposition function requires very little overhead and that most of the CPU cycles are spent on LU Factorization and not communication requirements thanks to the local link feature of the grid architecture. However, similar to the architecture in the previous section, a major problem is throughput. Again, despite the distributed nature of this system, a new matrix cannot be processed until the previous matrix is complete. Moreover, this architecture requires a rather large number of general purpose processors, 4096 to be exact. As a result, this approach would require extensive cost to develop.

#### 2.3 NETWORK DISTRIBUTED CLUSTER PROCESSING

The previous research discussed involved solutions to LU factorization using static sized processing arrays. In 2004, research in parallel processing performed by researchers at the University of Tokyo yielded high performance solutions to LU factorization on non-dedicated computing clusters where the number of available computing resources may be arbitrary and even dynamically changing. The researchers observed 130Gflops with 128 processes running on a 70-node, dual 2.4GHz Intel Xeon cluster with a matrix size of 46,080 by 46,080 [4]. However, all 70 nodes are not available at all times.

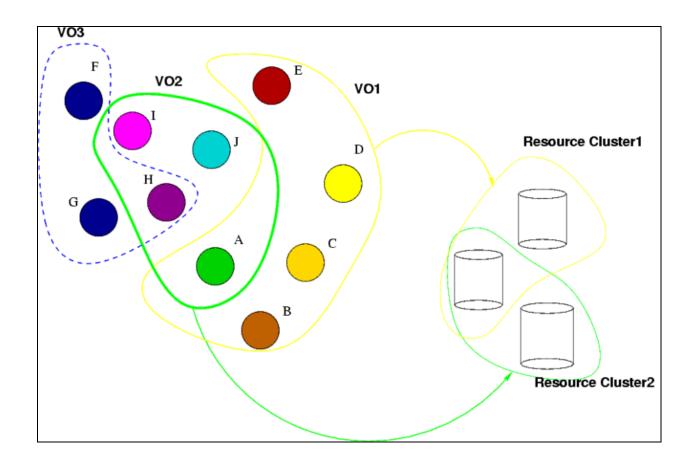

Figure 7: Distributed Computing Cluster [5]

Overall, distributed cluster computing (also known as "Grid Computing" or "Cloud Computing today) takes advantage of networked computers in an effort to create a "virtual supercomputer" to perform parallel operations via network links such as Ethernet as opposed to traditional parallel processing systems interconnected by a high speed computer bus [5]. Overall, a topology is created that breaks all available systems down into various resource clusters known as Virtual Organizations (VOs). Tasks are distributed among these VOs and results are communicated as needed.

Solutions using distributed clusters are rather attractive in that numerous, networked processors exist that sit idle during down times. With the advent of the Internet, literally millions

of computers are now globally networked. In a report examining the use of broadband connectivity in the world, over 180 million active DSL lines, 60 million active cable lines, and 23 million active fiber lines connecting as many or more computers worldwide are in place [6]. This clearly indicates a substantial number of computing resources with broadband connections available at any given time on the Internet.

As a result, researchers are looking to exploit this untapped power that exists. Researchers at Stanford University, under the Folding@home project, utilize idle, networked Sony Playstation 3 gaming consoles, as well as other powerful computers, to perform complex, mathematical functions in an effort to understand protein folding, mis-folding, and related diseases [7]. Researchers at Berkeley are using the same distributed cluster approach to distribute the analysis of radio telescope data in an effort to locate intelligent radio signals under the SETI@home project [8].

The research performed at the University of Tokyo is similar to the projects mentioned above only this project focuses on LU factorization. The 70 node system is partitioned into various virtual organizations. A programming model known as "Phoenix" is developed to facilitate communications between VOs as well as construct an algorithm for task scheduling and load balancing. Also, methods are created to handle the communication protocol, the dynamic nature of nodes in the system, as well as the nondeterministic time involved with inter-processor communication. Keep in mind that parallel processing systems discussed in the other research have deterministic interconnect.

Overall, this system yields amazing results given the number of mathematical calculations required. However, this system requires very complex algorithms to schedule, distribute, and collect results. Moreover, the number of computing resources required is very

large. A solution such as distributed computing clusters, while interesting, is not feasible for a straightforward solution to the LU factorization problem to say nothing of embedded system applications. Also, the system cannot perform a subsequent solution until the current solution is computed. Still, it is a glimpse at the future of parallel processing and how it pertains to the resources required for solving complex mathematical functions such as LU factorization. Some of the aspects of this architecture that may be used in the future pertaining to the 3D LU factorization pipeline are discussed in Section 5.1.5.

#### 2.4 PARALLEL PROCESSING SYSTEM-ON-A-CHIP

While most research involved with solving LU factorization has been performed using large computer systems, some research has been performed at implementing a solution to LU factorization on a chip level as opposed to a large scale, discrete processor system. The benefits of using chips as opposed to large workstations are cost, reduced power consumption, and the potential to use these solutions in embedded systems. Researchers at the New Jersey Institute of Technology successfully implemented LU factorization at the chip level using FPGA technology [9].

The researchers employed a solution that is not unlike the shared memory solution discussed in Section 2.1. To create a computational platform, six, 32-bit RISC processors are instantiated in an Altera FPGA. These processors are connected to a shared memory using a customized block of logic on the FPGA fabric. The soft core IP processor from Altera, Nios, is used. The Nios RISC processor is a fully configurable soft IP that offers over 125MHz in an

Altera Stratix FPGA. Since floating point operations are desired for LU factorization, a single precision, IEEE754 floating point unit is used so that floating point operations are handled in hardware as opposed to software thus improving performance.

An algorithm is developed to partition the solution among five processors. The sixth processor acts as a "local controller" governing the operation of the entire process. These processors post results via the shared memory and the local controller broadcasts results to other processors as needed. These algorithms are not unlike those examined in Section 2.1. After one matrix is processed, the system is free to begin processing another matrix.

The researchers demonstrate that performance for non-trivial matrix sizes is rather impressive. In the case of a 5x5 LU factorization, a software solution takes 45,168 system clock cycles on a single CPU. When their parallel processing solution is implemented, the performance increases significantly as only 4,583 clock cycles are required [9]. Therefore, this research proves that application acceleration similar to that seen in similar architectures using workstations is possible on FPGAs.

The same researchers took this concept a step farther and implemented another system designed to solve LU factorization not unlike the system seen in Section 2.2. The system is implemented on an Altera FPGA. The algorithms to partition data in [9] are modified to handle load balancing. The feasibility of scaling the architecture is also presented. Also, distributed memory using on-chip SRAM is used as opposed to a single shared memory among all processors.

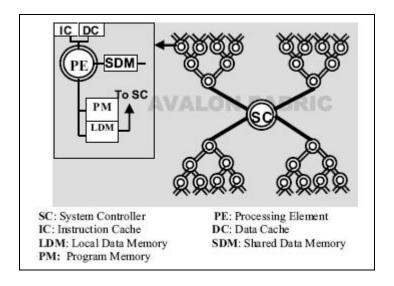

Figure 8: Binary tree of processors from [11]

One processor is assigned "system controller" to provide a mechanism for both partitioning tasks taking into account the load balancing of both processing communications. Each node of the tree consists of both instruction and data caches, both data and program memory for the Harvard Architecture Nios processor, and a shared data memory for communicating results to children in the tree. Each node also has a path to communicate results back to the system controller via Altera's "Avalon" bus fabric [10] [11].

The researchers indicate a significant improvement in the matrix operations reported in [11] of more than 20%. Still, even with these enhancements, overhead exists similar to that seen in their workstation-based relatives. Matrix processing time is sacrificed since inter-processor communication is required. However, the research in [9], [10], and [11] clearly demonstrates that LU factorization of non-trivial matrices in an FPGA is possible.

#### 2.5 DEDICATED PROCESSING LOGIC

So far, every solution to the LU factorization problem presented involves the use of a traditional Von Neumann or Harvard CPU to perform calculations. In an effort to increase performance, multiple CPUs are used. When partitioning the design across multiple CPUs, some time must be dedicated to communication of intermediate results. This indicates that some processing time must be sacrificed so that communication results are broadcast to interested processors.

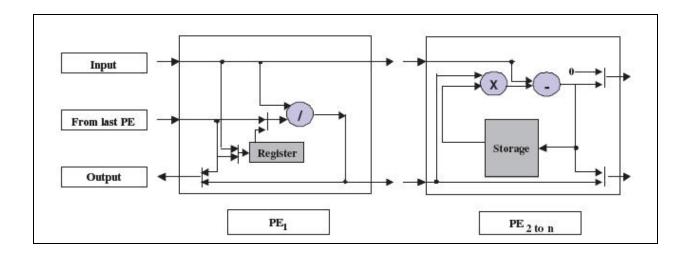

A potential solution to the communication bottleneck is the use of dedicated hardware to solve LU factorization. While the 3D Paul-Mickle pipeline proposes such custom hardware, researchers at the University of Southern California actually implemented a similar solution in 2004 in that a custom pipeline is used to solve LU factorization for any size of matrix. The linear pipeline is implemented such that it assumes data is being sent to the pipeline in a word by word format since the research assumes that hardware accelerators are fed streaming data from external CPUs or external memory [12].

Figure 9: Linear array solution presented in [12]

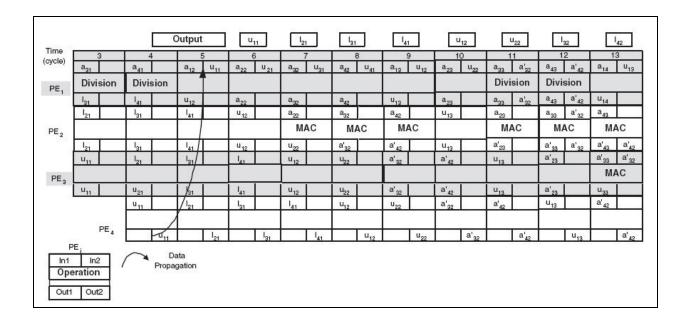

The logic accepts data in a word by word, streaming format that arrives at the node labeled "Input" in Figure 9. The first processing element ( $PE_1$ ) is responsible for the division required at each stage of the factorization algorithm. These quotients, as well as the initial values of the matrix are forwarded to the subsequent processing elements denoted  $PE_{2 \text{ to n}}$  in the linear array. Control logic in  $PE_1$  directs matrix data to either the divide function or directly to the output. Control logic in subsequent stages directs data to either the multiply or subtraction function as well as fetching of previous results from local storage when needed. Output that is needed for the next stage of the algorithm is fed back into the pipeline as needed. Also, the pipeline can begin to accept a new input matrix when the final stage of the current matrix being processed is performed. The following diagram from [12] details the operations that occur in each processing element of a pipeline that solves LU factorization for a 4x4 matrix.

Figure 10: Dataflow of architecture presented in [12]

This architecture clearly demonstrates that implementing a custom pipeline via the use of a device like an ASIC or FPGA is feasible as opposed to a system using distributed CPUs. Each mathematical function is designed to support IEEE single precision format floating point operations and the design is functioning on a Xilinx Virtex-II Pro-125 device. Performance is exactly as expected. The latency achieved by this solution is  $n^2 + n$  cycles [12]. So, when comparing these results to the results in [9] and [11] a substantial performance increase is observed. The 5X5 case in this architecture would only require 30 arithmetic cycles as opposed to the 4,583 cycles observed in the other FPGA research. Even if one factors in the amount of latency in the divide, multiply, and subtract functions, the end result is well over three quarters the number cycles required by the Nios based parallel processing system. While the latency reduction is impressive, it most certainly is improvable with a different, custom logic solution.

#### 3.0 THE THREE DIMENSIONAL LU FACTORIZATION PIPELINE

In the previous chapter, various architectures were explored from prior research that details various schemes used to solve LU factorization. Earlier implementations used banks of parallel processors to perform the function while later solutions migrated similar solutions performed on large scale workstations to single-chip implementations. Parallel processing solutions involving CPUs, as well as the more recent, distributed cluster architecture, provide a high-speed solution to the LU factorization problem with the tradeoff of significant computing resources being required, not to mention the classic communication overhead problem associated with parallel processing and overhead associated with the complex scheduling and load balancing algorithms. The later solutions utilizing FPGA technology reduce the physical requirements to a single device, but suffer from sub-optimal latency. A solution must exist that eliminates the communication overhead issue and effectively minimizes latency.

In 1998, Dr. JoAnn M. Paul and Dr. Marlin H. Mickle of the University of Pittsburgh presented an architecture that does not require a massive amount of parallel processors while, simultaneously, reducing the latency to perform LU factorization of a matrix size n\*n down to 4n-4 arithmetic operation cycles. Moreover, in sustained operation, a new LU factorization is computed every single cycle for the minimal block pipelining period of 1 [1]. To date, this architecture is the optimal solution to LU factorization in terms of latency. The only question remaining is if it is at all feasible to create the pipeline to optimally solve LU factorization for non-trivial matrix size using custom hardware such as an FPGA.

This section presents the architecture devised by Dr. Paul and Dr. Mickle. Next, the hardware used to implement the pipeline is presented. Finally, an overview of the design flow, from resource estimation to final implementation is discussed.

## 3.1 THREE DIMENSIONAL ARCHITECTURE OVERVIEW

In Figure 2, the pseudocode used to implement LU factorization, also known as Crout Elimination, was presented. As stated, the loop appears trivial at first glance, but for non-trivial matrix sizes, it is clear that Crout Elimination required a substantial number of arithmetic operations. The following figure shows the Crout loop "unrolled" for a 4x4 matrix revealing all of the computations required to perform the function.

```

# DIVIDE ON ITERATION #1

\# a(1,2) = a(1,2) / a(1,1)

\# a(1,3) = a(1,3) / a(1,1)

\# a(1,4) = a(1,4) / a(1,1)

# Multiply-Subtract operations on iteration #1

\# a(2,2) = a(2,2) - a(2,1) * a(1,2)

\# a(3,2) = a(3,2) - a(3,1)

* a(1,2)

\# a(4,2) = a(4,2) - a(4,1) * a(1,2)

\# a(2,3) = a(2,3) - a(2,1) * a(1,3)

\# a(3,3) = a(3,3) - a(3,1) * a(1,3)

\# a(4,3) = a(4,3) - a(4,1) * a(1,3)

\# a(2,4) = a(2,4) - a(2,1) * a(1,4)

\# a(3,4) = a(3,4) - a(3,1) * a(1,4)

\# a(4,4) = a(4,4) - a(4,1) * a(1,4)

# DIVIDE ON ITERATION #2

\# a(2,3) = a(2,3) / a(2,2)

\# a(2,4) = a(2,4) / a(2,2)

# Multiply-Subtract operations on iteration #2

\# a(3,3) = a(3,3) - a(3,2) * a(2,3)

\# a(4,3) = a(4,3) - a(4,2) * a(2,3)

\# a(3,4) = a(3,4) - a(3,2) * a(2,4)

\# a(4,4) = a(4,4) - a(4,2) * a(2,4)

# DIVIDE ON ITERATION #3

\# a(3,4) = a(3,4) / a(3,3)

# Multiply-Subtract operations on iteration #3

\# a(4,4) = a(4,4) - a(4,3) * a(3,4)

```

Figure 11: Crout loop unrolled for the 4x4 case

As seen in the loop, a significant number of operations are required for even a smaller case like n = 4. Crout Elimination requires  $n^3/3$  arithmetic operation pairs. When  $n^3$  is not an integer multiple of three,  $n^3/3$  is rounded to the nearest integer [1].

With the loop unrolled, it is apparent that parts of the Crout algorithm can be made parallel as enough data is present to perform partial computations in each stage. Overall, the first operations that must be performed are the division functions in the first "active" row of each stage where the "active" row number is equal to the current stage number. Once the quotients

are computed, the multiply operations can be performed. Thereafter, the subtraction function can be performed. After all three arithmetic functions are performed, it is safe to begin the computations for the next iteration of the Crout loop.

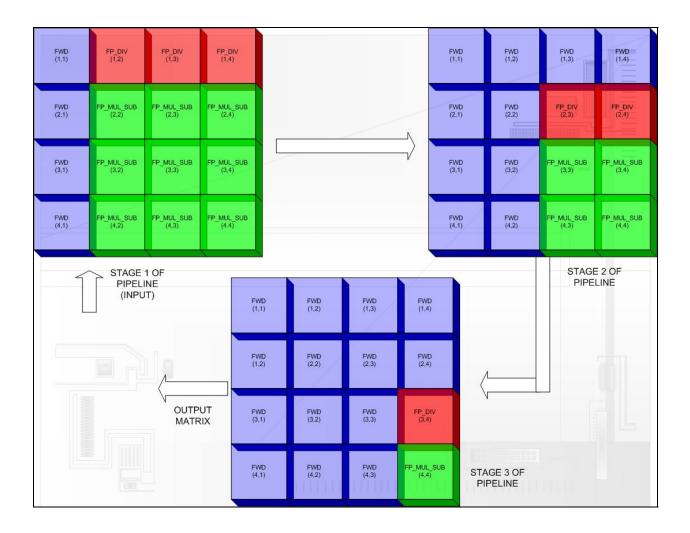

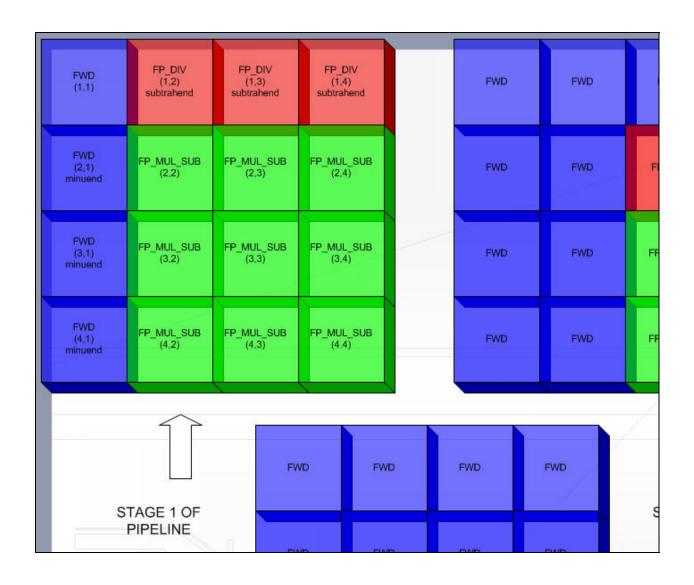

Figure 12: Crout 3D pipeline

Figure 12 helps graphically depict the structure of the 3D pipeline for a 4x4 case. The Paul-Mickle 3D architecture groups these Crout loop processing iterations into matrix pipeline stages. The elements of each stage of the matrix correspond to one of three functions. First, the

function labeled "FWD" simply forwards data to the next matrix stage without any arithmetic operation being performed. Next, the function labeled "FP\_DIV" divides the current contents of the matrix by the element (*stage,stage*) where *stage* corresponds to the current stage of the matrix pipeline. All quotients are computed in parallel.

After the quotients are available, the function "FP\_MUL\_SUB" performs an arithmetic pair of operations. First, the quotient is multiplied by the corresponding row element under the element (*stage,stage*). For clarity, suppose one was examining element (3,2) during matrix stage 1 of the pipeline. The quotient computed in element (1,2) would be multiplied by the corresponding row element under (*stage,stage*) which, in this example, is element (3,1). After the product is computed, the product is subtracted from the current value of the element being processed. At this point, all computed values are forwarded to either the next stage of the matrix pipeline or are output from the pipeline in the final stage since the solution is now known.

The pipeline falls into the "3D category" due to matrix stage stacking. Each matrix pipeline stage is a 2D pipeline. Each element of the matrix stage is a linear pipeline. The "FWD" function is a linear pipeline of no-operations that is equal in latency to the total number of cycles it takes to divide, multiply, and subtract. The "FP\_DIV" function is a divide pipeline. The "FP\_MUL\_SUB" pipeline includes three different pipelines. The first is the multiply pipeline used to multiply the quotient by the corresponding row element under (*stage,stage*). Once the product is computed, the subtraction can occur. However, a pipeline is hidden in that the current contents of the matrix stage element that has the multiply-subtract requirement must be maintained until both division and multiplication are complete. The final pipeline in each matrix stage is the actual subtraction pipeline. Also, an additional, no operation pipeline stages at the output of the divider function must be added to compensate for the latency of the multiply-

subtract function. So long as the matrix stage is created as described, a full matrix can be input on each cycle making the 2D pipeline fully systolic. The third dimension is the stacking of each matrix stage. The output of a stage's current element connects directly to the input of the corresponding element of the next stage.

## 3.1.1 3D Pipeline Example

This section details the "flow" of a matrix element through the pipeline in an effort to clarify the pipeline operation. To simplify the description, a 3x3 matrix example is used to demonstrate all arithmetic operations required on a particular element. In particular, the flow of data for element (3,3) of the 3x3 case is examined. Once this flow is understood for the 3x3 case, any user of this logic should be capable of scaling the logic to accommodate any size of matrix.

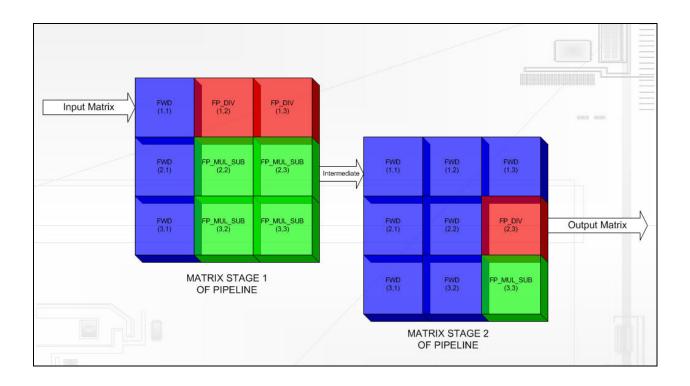

Figure 13: Overview of the 3x3 example.

A 3x3 Paul-Mickle pipeline requires 2 matrix pipeline stages. Figure 13 details the arithmetic operations that occur in each element of the particular stages. The structure of the pipeline is identical to stages 2 and 3 of the 4x4 example presented in Section 3.1. A complete matrix arrives at the node "Input Matrix" and exits the pipeline at the node "Ouput Matrix". Since each computing element (i.e. FWD, FP\_DIV, or FP\_MUL\_SUB) is pipelined, a new matrix can be presented at the node "Input Matrix" each clock cycle. After the initial latency of the computing elements passes, a solved matrix arrives at the node "Ouptut Matrix" on each clock cycle. The intermediate node is the point where computations are complete for the first pipeline stage and data enters the second stage. Finally, the output of each element is connected to the input of the corresponding element.

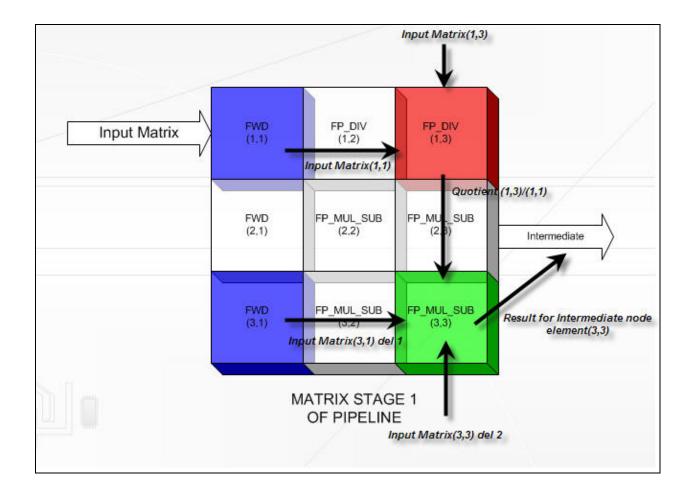

Figure 14: Dataflow for matrix stage 1

Referencing Figure 14, data arriving at the node "Input Matrix" is immediately used as input for the FP\_DIV processing element. In the case of a 3x3 matrix, the FP\_DIV logic at location (1,3) uses both Input  $Matrix_{(1,3)}$  and  $Input Matrix_{(1,1)}$  to compute the quotient (1,3) / (1,1). After the quotient is present, the product of  $quotient_{(1,3)}$  \* Input  $Matrix_{(3,1)}$ . Since each processing element of the matrix is considered to be systolic, a delay is required so that one meets the requirement of introducing a new matrix every clock cycle. The delay required for the multiplication at element (3,3) is denoted in Figure 14 as "del 1". This delay is equivalent to any delay introduced by the division function.

Once the product is calculated, the subtraction of  $\operatorname{product}_{(3,3)}$  from Input  $\operatorname{Matrix}_{(3,3)}$  can be performed. Both multiplication and subtraction are performed in the processing element FP\_MUL\_SUB. Again, another delay must be introduced on the data at node "Input Matrix" to keep the pipeline systolic. This delay is denoted in Figure 14 as "del 2". This delay is equal to the number of cycles required by both the division and multiplication functions. After subtraction is complete, all results are available at the node labeled "Intermediate" for the second stage of the pipeline.

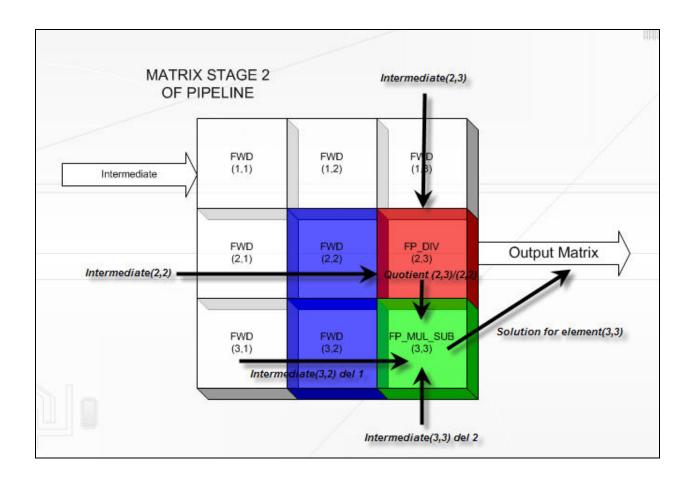

Figure 15: Second matrix stage of the 3x3 example.

Figure 15 details the flow of data in the second stage of the pipeline. Data arrives at the intermediate node and the quotient is computed at element<sub>(2,3)</sub> from Intermediate<sub>(2,3)</sub> and Intermediate<sub>(2,2)</sub>. After the quotient at element<sub>(2,3)</sub> is ready, the subsequent multiplication of quotient<sub>(2,3)</sub> and Intermediate<sub>(3,2)</sub> at element<sub>(3,3)</sub> can occur after the delay denoted by "del 1". Finally, subtraction of the product calculated at element<sub>(3,3)</sub> from Intermediate<sub>(3,3)</sub> can be performed after the delay "del 2". After these operations are performed, the solution is present at the "Output Matrix" node.

#### 3.2 HARDWARE SELECTION

Now that the architecture is understood, work can begin on the implementation of the pipeline. Based on the description of [1], it is quite apparent that numerous divide, multiply, and subtraction processing elements are required. In an effort to demonstrate feasibility of "real world" implementation, the processing elements are chosen to support IEEE single precision floating point representation. Since floating point computations typically require a significant amount of logic to implement, a rather large FPGA must be used. Moreover, a non-trivial matrix size must be selected.

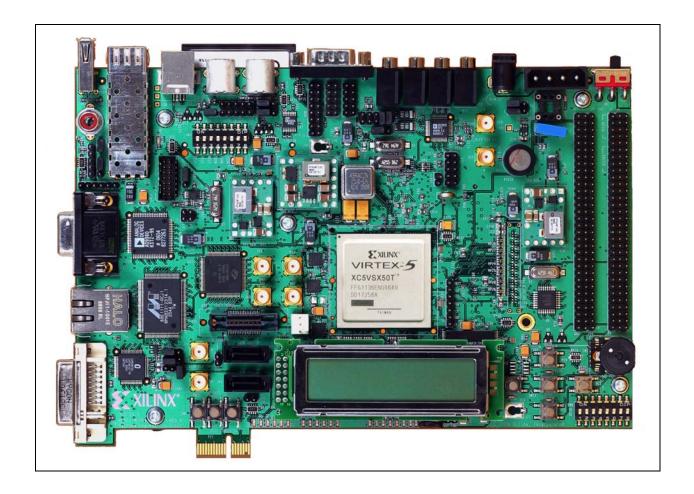

To satisfy the "large FPGA" requirement, the Xilinx Virtex 5 SXT 50 is selected. The device provides 32,640, 6 input look up tables (LUTs) as well as 32,640 flip flops. Moreover, an additional 288 48-bit dedicated multiply-accumulate functions known as DSP48 blocks are available for general use [13]. To avoid the intricacies involved with creating a custom printed circuit board, the Xilinx ML506 development board is chosen to implement the design. This

board has the Virtex 5 device required to implement the pipeline as well as peripheral circuitry useful to test the pipeline once developed.

Figure 16: The Xilinx ML506 development kit

In an effort to demonstrate a non-trivial matrix pipeline is reasonable for implementation, a 5x5 matrix pipeline is chosen. While Crout Elimination is complex for any size of matrix, a 5x5 matrix shall require a significant amount of floating point processing to demonstrate that the 3D pipeline can be realized for a non-trivial size. Overall, the Virtex 5 SXT 50 should be able

to hold all of the logic and test circuitry required for the 5x5 solution using IEEE754 single precision floating point numbers.

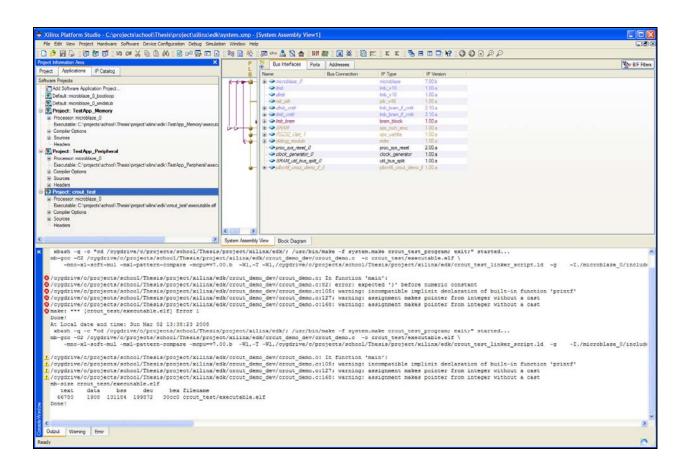

#### 3.3 DESIGN FLOW OVERVIEW

Although the design is targeting FPGA technology, a design methodology similar to that of ASICs is used. First, primitives required for the design are required to be created. Overall, this entails determining solutions for the floating point functions required in the pipeline. For demonstration purposes, it is desirable to use floating point functions that consume as little FPGA resources as possible.

Once these floating point functions are chosen, they are assembled to form the 3D Crout Elimination pipeline. VHDL is used to assemble the pipeline as it is one of the major languages used for logic synthesis. A VHDL simulator as well as a custom written VHDL testbench is used to verify the functionality of the pipeline. While an FPGA is reconfigurable unlike its ASIC brethren, it is rather inefficient as well as difficult to correct errors by synthesizing and uploading results to the FPGA as opposed to simulating the functionality of the device. FPGA build times can take hours for designs as complex as a 5x5 Crout Elimination pipeline.

After the Crout Elimination pipeline functionality is verified, work begins on a way to test the circuit in-system. Overall, an interface is required to both drive data into the pipeline as well as capture results. The simplest way to perform this task on a wide range of test vectors is to have a CPU drive these test vectors into the pipeline. The CPU chosen to perform this task is the Xilinx Microblaze processor. Also, since the input and output bit widths of the Crout pipeline are rather wide (25 matrix elements at 32 bits wide is equal to 800 total bits), some form

of translation is required to convert the 32 bit accesses of the Microblaze to the 800-bit wide vectors the pipeline requires. This translation can be achieved using on-chip memory available on the Xilinx device.

Once the pipeline and associated test circuitry are created, the design is synthesized and uploaded to the target device using the Xilinx ISE tools. Ideally, a simple test program is written to exercise the hardware and observe the results. Should these results match expected results, the development of the design is complete and the 3D Crout Elimination pipeline will be realized!

#### 4.0 DESIGN, IMPLEMENTATION AND VERIFICATION OF THE PIPELINE

This chapter details the design, implementation, and verification of the 3D Paul-Mickle LU Factorization Pipeline. First, the development of IEEE 754 floating point primitives is discussed in an effort to determine logic utilization requirements. Next, the design of the pipeline is discussed along with simulation results. Third, the creation of an embedded system using a Xilinx FPGA to physically test the pipeline in hardware is presented. Overall, this chapter is intended to present the design flow to implement the architecture proposed in chapter three.

#### 4.1 IEEE 754 FLOATING POINT PRIMITIVES

The core mathematical primitives required to perform Crout Elimination are simply divide, multiply, and subtract. Unfortunately, IEEE754 arithmetic functions are typically expensive in terms of hardware utilization or CPU cycles given the algorithms required to perform the said functions. However, floating point functions are virtually required as they provide precision not found using integer or fixed point numerical representation. As a result, using the IEEE754 format is almost mandatory for real-world applications. Many vendors provide intellectual property that performs floating point arithmetic. For this thesis, two available solutions are examined.

The first solution explored is a synthesizable IEEE HDL floating point library known as 1076.3. The goal of IEEE1076.3 is to provide a floating point synthesis package for VHDL and Verilog based on IEEE 754 [14]. Currently, this package is freely available for download and is actively maintained as of 2008. Unfortunately, after some experimentation, this package is not ready for the tool suite used in this thesis. While the maintainer of the package has had success using the package with the Synplify Synplicity synthesis tool, Xilinx ISE synthesis tools, as of version 9.2.04, do not support some of the VHDL constructs required by the package [15]. Fortunately, some features of the new package are used for verification purposes and are discussed later.

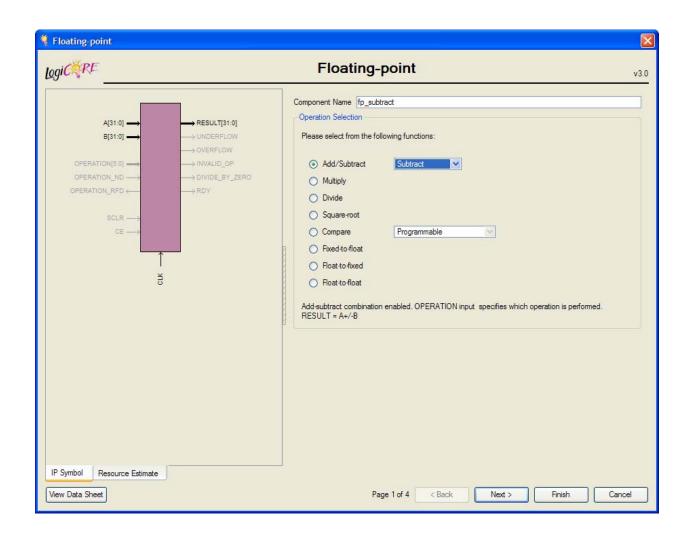

The solution used in the implementation of the pipeline is provided by Xilinx via the Coregen FPGA IP generator [16]. Assuming a Xilinx user has a license to use ISE, Xilinx provides a netlist generator that creates a fully working floating point core. Moreover, the floating point core can be customized in various ways to provide users flexibility in examining performance vs. area tradeoffs. Since this solution is known to work, it was chosen for this implementation. With that in mind, creation of the cores and resource utilization must be considered to see if these cores do not exceed the available resources in the target device.

## 4.1.1 Floating Point Logic Creation

Since the target device is a Xilinx Virtex 5 SXT 50, the following key resources are available for use. First, the device has 32,640, 6-input Look Up Tables (LUTs) as well as 32,640 flip flops on the FPGA fabric. Next, the device has 288 DSP slices available that contain logic for creating both adders and multipliers without using FPGA LUT and flip flop resources. Finally, the device contains 144 36 kilobit "blockRAMs" for use as general purpose memory.

While the embedded memory is not critical to the Crout pipeline itself, it will serve a useful purpose as seen later in this thesis.

With these area constraints known, the parameters used to generate the floating point cores for the 5x5 pipeline can be determined. Again, the floating point cores are created using the Xilinx tool Coregen. Coregen allows one to custom tailor the floating point core to fit their area requirements two ways: pipeline latency and cycles per operation when using IEEE754 floating point numbers. The following overview details the approach used to generate the cores.

First, the user selects the function to create. This is done via a simple menu after a user chooses to generate a floating point core in the Coregen IP menu.

Figure 17: Xilinx Coregen Floating Point Selection Menu.

The menu presents various floating point functions the user can choose. In this example, a floating point subtraction function is created. Once the function is chosen, the user then customizes the precision of the core.

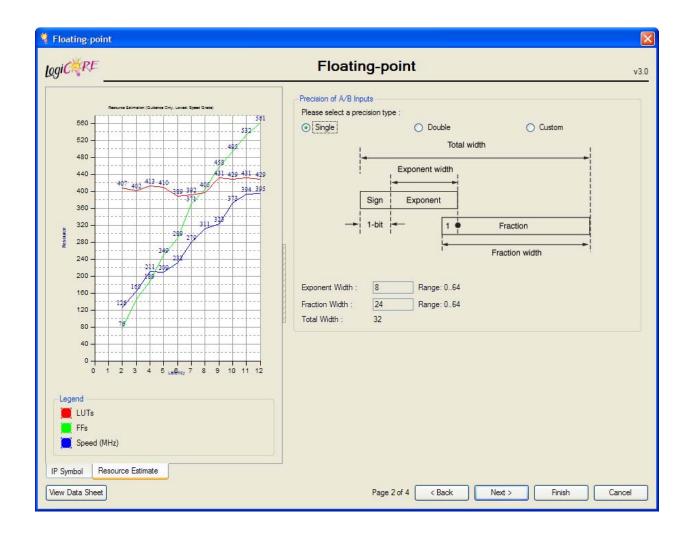

Figure 18: Floating point precision menu

For the Crout pipeline, "single precision" floating point numbers are chosen as indicated by the "precision type" checkboxes. As specified in IEEE754, there is one sign bit, 8 exponent bits, and 23 mantissa bits. Be aware that if more logic were available in the target device, a user could choose double precision or custom field widths for their applications. If a custom format is required, the user would input the field lengths in the "Exponent Width" and "Fraction Width" boxes.

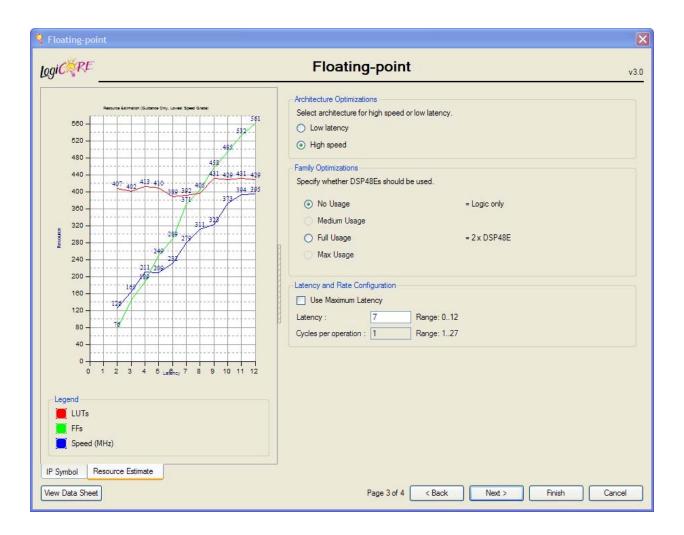

The final option provided by Coregen allows the user to tweak the area of the core by trading off performance.

Figure 19: Floating point performance vs. area tradeoffs

As seen in Figure 19, LUT utilization for a subtraction function remains relatively constant while flip flop utilization increases as the required maximum frequency of the core increases since additional pipeline stages are required. Also, the user may choose to use Xilinx DSP48 elements to reduce the logic required for the addition and multiplication functions. DSP48 elements lower

the LUT and flip flop count requirements and boost the overall performance of the core. However, the tradeoff is the limited number of DSP elements in the FPGA: there are only 288 of these present in the targeted device. DSP elements also restrict the portability of the design to other FPGA platforms as many FPGA platforms do not have this functionality.

After experimenting with the various tradeoffs given the resource limitations, the parameters chosen for the design indicate that a 5x5 solution is feasible in the target device under certain constraints. First, the IEEE754 subtraction and multiplication functions will consume an acceptable amount of resources while still maintaining full systolic functionality. A pipeline latency of 7 is chosen for the subtraction function with zero DSP slice utilization since this value balances out performance versus logic utilization. Next, the multiply function is chosen to be an 8 stage pipeline with full systolic operation for the same reasons as the subtraction function: performance versus logic utilization. However, multipliers tend to consume significant LUTs, so one DSP48 element is used per multiplier in an effort to fit the design in the target device.

The divide function needs to be created in a non-systolic fashion as logic utilization increases if the function is "fully pipelined". Documentation on the divide function shows that the number of flip flops required for a systolic divide function is over 5 times greater than one that requires wait states [17]. As a result, the wait-state version of the core is used along with its 26 cycle latency. This does not disqualify the 3D pipeline from implementation in an FPGA since the goal is to prove that a new matrix can begin processing as soon as a current matrix is done being processed in the first stage of the pipeline. However, more logic would be required if the user desired a solution that clocks a new matrix into the pipeline on each edge of the system clock.

Since the design is using arithmetic functions that are not "fully systolic", shift registers are not required to delay the input and subsequent intermediate nodes. This saves a logic as well since the input and intermediate nodes will only be registered at each matrix stage. However, a "complete" systolic implementation will require these shift registers thus boosting the total logic count for the design.

## **4.1.2** Floating Point Logic Utilization

Since the demonstration pipeline is four "matrix" stages, the total logic required by all of the floating point elements based on the architecture discussed in Chapter 3 must be determined. The following table details expected logic utilization for all of the floating point cores required by the pipeline. The number of cores required is derived from the unrolled loop of a 5x5 matrix as discussed in Section 3.1 and detailed in Figure 11.

**Table 1 : Resource Estimation**

|          |                  | <u>LUTs</u> | Flip Flops       |               |

|----------|------------------|-------------|------------------|---------------|

|          | <u>Primitive</u> | Required    | Required         | DSPs Required |

|          | FP Divide        | 227         | 233              | 0             |

|          | FP Multiply      | 293         | 242              | 1             |

|          | FP Subtract      | 392         | 371              | 0             |

|          |                  |             |                  |               |

|          | Number of        |             |                  |               |

| Stage 1  | Primitives       | Total LUTs  | Total Flip Flops | Total DSPs    |

|          |                  |             |                  |               |

| Divide   | 4                | 908         | 932              | 0             |

| Multiply | 16               | 4688        | 3872             | 16            |

| Subtract | 16               | 6272        | 5936             | 0             |

|          |                  |             |                  |               |

| Stage 2  |                  |             |                  |               |

|          |                  |             |                  |               |

| Divide   | 3                | 681         | 699              | 0             |

| Multiply | 9                | 2637        | 2178             | 9             |

| Subtract | 9                | 3528        | 3339             | 0             |

|          |                  |             |                  |               |

| Stage 3  |                  |             |                  |               |

|          |                  |             |                  |               |

| Divide   | 2                | 454         | 466              | 0             |

| Multiply | 4                | 1172        | 968              | 4             |

| Subtract | 4                | 1568        | 1484             | 0             |

|          |                  |             |                  |               |

| Stage 4  |                  |             |                  |               |

| D: : 1   | 4                | 007         | 000              |               |

| Divide   | 1                | 227         | 233              | 0             |

| Multiply | 1                | 293         | 242              | 1             |

| Subtract | 1                | 392         | 371              | 0             |

| <b>T</b> | 70               |             | 20722            | -             |

| Totals   | 70               | 22820       | 20720            | 30            |

It is determined that the parameters chosen indicate that the pipeline fits in the target device. More than 10,000 logic elements are remaining. These will be reserved for the simple, processor based system functions required to drive the pipeline in hardware once the pipeline is synthesized.

## 4.2 PIPELINE AND TEST CIRCUITRY DEVELOPMENT

Now that all issues pertaining to the creation of floating point logic are resolved, focus is shifted to the creation of the pipeline itself. This section details the design methodologies used in the creation of the three dimensional LU factorization pipeline as well as support circuitry needed to test the pipeline. Overall, a hierarchical design approach is used so that a relatively clear method of using conditional instantiation techniques available in HDLs is facilitated.

# 4.2.1 Multiply-Subtract Component

The first component in the design hierarchy required is a multiply followed by subtraction function. Recall a "matrix stage" in the pipeline:

Figure 20: Single stage of 3D pipeline

As seen in the figure above from the 4x4 example detailed in Chapter Three, the multiply and subtract functions occur consecutively after the quotient is calculated from the floating point division functions. To express this clearly, suppose one is looking at the calculations for element A(3,3) and A represents stage one of the pipeline.

First, the following divide function must occur on element A(1,3):

$$A(1,2) = A(1,2) / A(1,1)$$

Once division is complete, we are free to perform:

$$A(3,3) = A(3,3) - A(3,1)*A(1,3)$$

So, in maintaining a proper design hierarchy, a circuit is developed to accept the results of both the current value of element being processed as well as both the result of the division function and the column of values used as the minuend of the subtraction function. Once these functions are performed, the results are forwarded to the next matrix stage of the pipeline. This multiply-then-subtract function begins once the divide function for the current stage is complete.

Creating this logic as a single component allows easy instantiation of multiple multiplythen-subtract functions via the use of VHDL generics. In the next section, this component is combined with the floating point divide function as well as conditional instantiation to create the basis of the pipeline.

## **4.2.2** Crout Matrix Stage Component

With the "multiply then subtract" function complete, conditional instantiation is used to determine connectivity in each stage of the matrix pipeline. The following pseudocode details this instantiation. It is a basic nested instantiation loop where the term MATRIX\_M indicates the size of the matrix while the term STAGE represents the pipeline stage we wish to generate. Also, the term "mtx\_in" represents the input from the previous stage of the pipeline while the term "rslt m i" indicates an output of the stage.

```

create_proc_i_0 : for i in 1 to MATRIX_M

generate

create_proc_j_0 : for j in 1 to MATRIX_M

generate

check_if_divide : if ((i = STAGE) and (j > STAGE))

generate

-- Instantiate divide component

Divide_function (

Inputs :

=> mtx_in(i,j)

=> mtx_in(STAGE,STAGE)

b

Outputs:

result => quotient(j)

=> quotient_rdy)

rslt_m_i(i,j)  <= quotient(j)

end generate;

```

Figure 21: Conditional component instantiation for Crout pipeline (divide).

In the first section of the instantiation of components that create a Crout pipeline stage, dividers are placed in the first row where dividers are required to be instantiated given the current stage. The only exception is the first element of the row since this element is used as the divisor of the current stage. The flag "quotient\_rdy" indicates when division is complete and that the upcoming multiply-subtract logic can begin processing with the quotient. Finally, the quotient itself can be forwarded to the next stage since no other operations are required on this particular element of the matrix. To be clear, no values of the current stage will be forwarded to the next stage until the whole divide/multiply/subtract function is complete in the actual implementation!

```

-- Instantiate a mult/subtract if we're "under the

-- dividers"...

check_if_multsub : if ((i>STAGE) and (j>STAGE))

generate

mult_then_sub function (

Inputs:

-- New data flag

new_data => quotient_rdy

-- Input operands...

quot_in => quotient(j)

mlt_in => mtx_in(i,STAGE)

sbt_in => mtx_in(i,STAGE)

sbt_in => mtx_in(i,j)

Outputs:

-- Result of above computations.

result_rdy => rslt_rdy

result => rslt_m_i(i,j)

)

end generate

```

Figure 22: Conditional component instantiation for Crout pipeline (multiplysubtract)

The above conditional instantiation determines placement of the "multiply-then-subtract" components created in the previous section. Again, this component starts processing new data once the floating point division is complete. Once the "rslt\_rdy" flag is asserted, the results on the term "rslt\_m\_i" are ready for forwarding to the next stage. In the actual hardware implementation, the assertion of "rslt\_rdy" indicates that the stage is ready to accept a new matrix.

```

-- Pass results if NOP occurs on this element.

check_if_pass : if ((i < STAGE) or (j <= STAGE))

generate

rslt_m_i(i,j) <= mtx_in(i,j);

end generate;

-- End nested loop

end generate;

end generate;

```

Figure 23: Conditional component instantiation for Crout pipeline (pass current element).

With the divide, multiply, and subtraction components instantiated, the final "component" is instantiated. Depending on the stage being generated, some elements require no mathematical functions performed. Therefore, the current input to the stage is simply forwarded to the output of the stage. Nothing is changed.

In general, this pseudocode creates a single stage of the 3D Crout pipeline. While the actual VHDL solution resembles this pseudocode, it is important to note that some additional conditions must be added to prevent unwanted latches during synthesis. These conditions are included in the source code provided in the Appendix and design files. With the pipeline stage created, one can proceed to the next level of hierarchy: the creation of the 5x5 pipeline with additional circuitry to drive data through the pipeline.

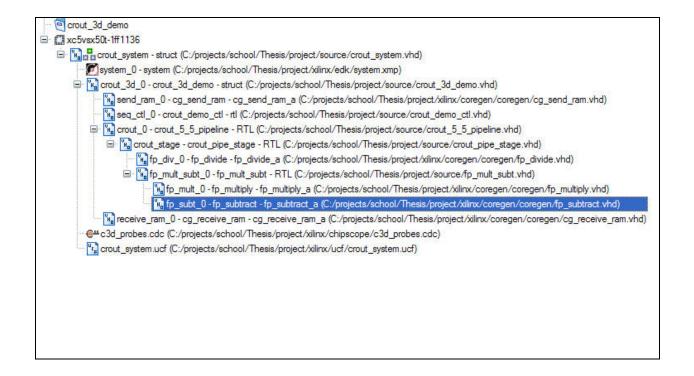

# 4.2.3 Complete Crout Pipeline and Associated Test Circuitry

Now that a single, generic stage of the Crout pipeline is complete, the actual 5x5 processing pipeline is created as well as additional support circuitry required to test the pipeline on an FPGA. First, at the next level of hierarchy up from the creation of the Crout single pipeline stage, the actual pipeline requires instantiation. Since the Crout pipeline stage was made using generics, this is a relatively painless process. One simply uses a generate loop to create the four stages required to solve a 5x5 matrix. The following is the actual VHDL instantiation used in the design.

```

-- Instantiate a 4 stage pipeline to solve the 5x5 case.

crout_5_5_pipe : for k in 1 to MATRIX_M-1

generate

crout_stage : entity work.crout_pipe_stage

generic map(

MATRIX M

=> MATRIX M, -- This is a 5x5 matrix

FLOATVEC_LEN => 32, -- Precision is 32 bits.

STAGE

=> k -- We're on stage "K"

port map(

-- Main Clock & reset

clk

=> clk.

=> reset.

reset

-- Input operands...

crout_rfd => crout_rfd_i(k-1),

crout_din => crout_data_i(k-1),

crout_ivalid => crout_dvalid(k-1),

-- Results

crout dout => crout data i(k),

crout ovalid => crout dvalid(k)

):

end generate:

```

Figure 24: 5x5 Crout Pipeline Instantiation

The Crout pipeline is configured by the MATRIX\_M, STAGE, and FLOATVEC\_LEN vectors. MATRIX\_M is the size of the matrix (i.e. 5x5), STAGE is used by the generate loop to allow the lower level "crout\_pipe\_stage" logic know the stage it is creating, and FLOATVEC\_LEN is a generic provided for future use should a user want to expand the width of the elements of the matrix being processed. The generate loop insures that the outputs of stage 1 connect to the inputs of stage 2, the outputs of stage 2 connect to the inputs of stage 3, etc.

Overall, the control signals are rather straightforward. The signal "crout\_rfd" indicates that a new matrix can be pushed into the pipeline. This signal is only used by the logic responsible for pushing a new matrix into the pipeline only when the first stage is not busy. The "crout\_dvalid" signal indicates that valid data is being pushed into the pipeline. At the output, a simple signal called "crout\_dvalid" qualifies the matrix data on the output "crout\_data\_i".

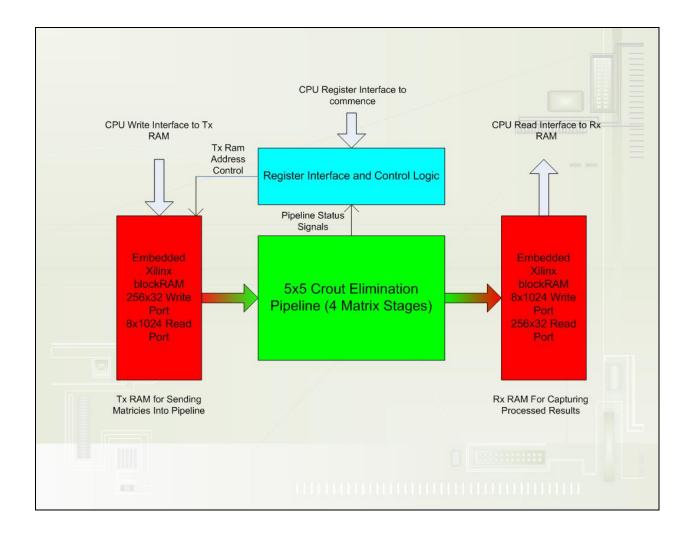

Driving the pipeline requires some additional circuitry as seen in the following block diagram. Since streaming data is not available, circuitry must be added to mimic matrix data streaming into the Crout pipeline.

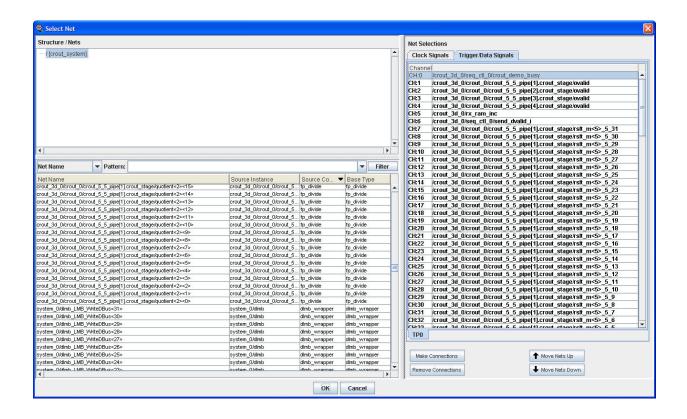

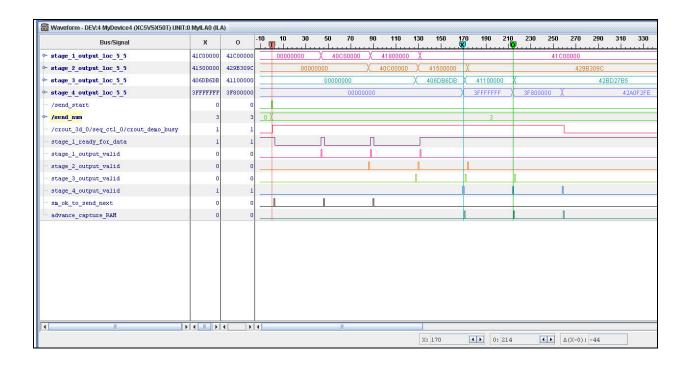

Figure 25: Block Diagram of Crout Pipeline Test Circuit

Overall, two memories (generated by Xilinx Coregen) are required to both send and receive matrices via a standard CPU interface (i.e. address, 32 bit data, write enable, etc.). A feature of Xilinx embedded memories is the ability to configure varying widths on the read and write ports of the blockRAM. For matrix loading purposes, the user loads all matrix data into the write side of the 256x32 transmit RAM in row major format. The size of the SRAM constrains the user to loading up to 8 matrices at a time. Be aware that this is not due to a limitation of the Crout pipeline: it can obviously service more than 8 matrices at a time provided the user waits

for the first stage of the pipeline to be free before pushing another matrix into the pipeline. The read port of the transmit RAM is 1024 bits wide with matrix element (1,1) corresponding to bits (31:0) of this vector. Element (1,2) would be bits (63:32) and so on. Since a 5x5 matrix only requires 25 elements (800 bits), all remaining bits are unused. The user must account for these unused bits when loading the transmit RAM (i.e. matrices must be loaded on 32 DWORD boundaries).

The "Register Interface and Control Logic" provides a means for a user to start the transfer of matrix data from the transmit RAM to the Crout pipeline. It also monitors the "ready for data" signal so that the "first matrix stage is free" rule is obeyed. Finally, it subsequently increments the read address pointer of the transmit RAM. This register is written with a "number of matrices to send" value after loading the transmit RAM. This register write subsequently starts pushing matrix data into the pipeline.

Processed data is captured by the receive RAM. The write port of this RAM is 8x1024 bits wide. The format of this data is the same as the transmit RAM. The user can read data out via the read port of the receive RAM using the CPU interface. The CPU interface is identical to the transmit RAM (256x32). The unused bits of the matrix vector remain unused, but the user must account for these unused locations in receive RAM. Matrices are stored on 32 DWORD boundaries.

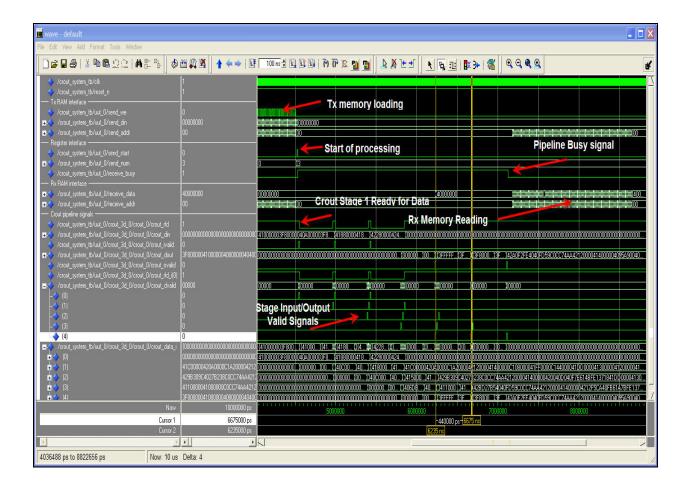

## 4.3 PIPELINE AND TEST CIRCUITRY SIMULATION

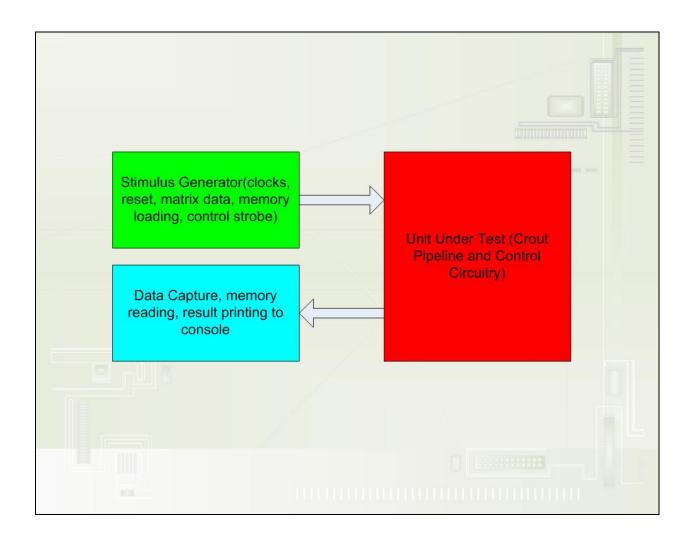

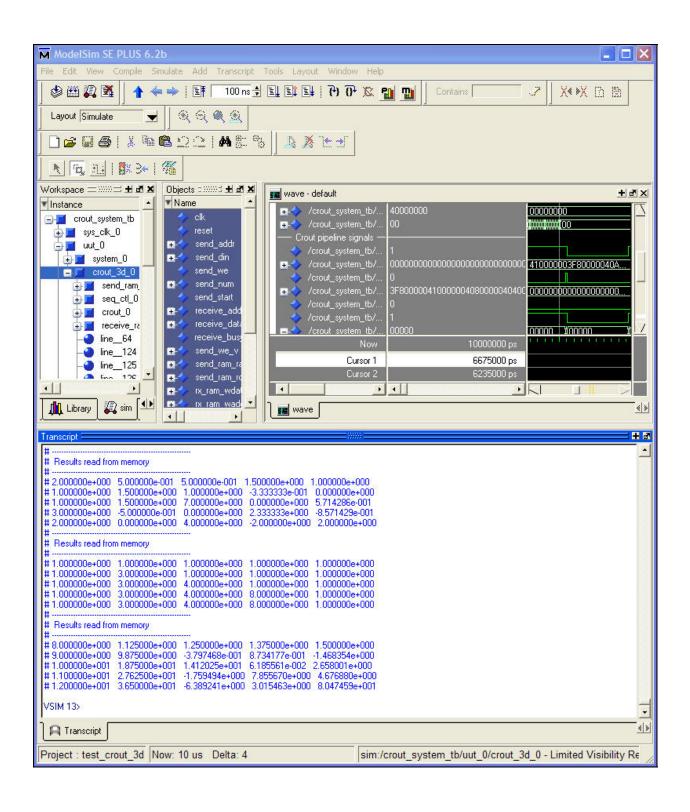

Now that the concept is developed, it is best to simulate the design to insure that the circuit is behaving as expected functionally! For this purpose, a test environment is created in

VHDL and the logic is simulated using Modelsim. While additional logic, namely a simple microcontroller and external memory controller for test code storage, are added later, it is rather useless to simulate the entire chip because our component of interest is the Crout pipeline. Simulation of a full CPU for this application is rather unnecessary. As a result, the testbench shall mimic the actions of the CPU.

Figure 26: Testbench block diagram

Overall, the stimulus generator basically mimics the functions of the soon-to-be-added CPU as well as the core FPGA functions (clock management, etc). The testbench code instantiates the Crout logic discussed in previous sections as well as components to simulate clock generation, power-on reset, and data driving. The user of the testbench simply loads VHDL "real" values into the transmit RAM. Since VHDL inherently lacks the concept of an IEEE754 floating point data-type, this task may seem rather difficult at first. Fortunately, the proposed IEEE floating point library for synthesis has procedures to provide "real to IEEE754" and vice-versa to substantially ease the amount of work required to verify the Crout pipeline. Basically, these functions can convert a real number to the equivalent IEEE754 logic vector.

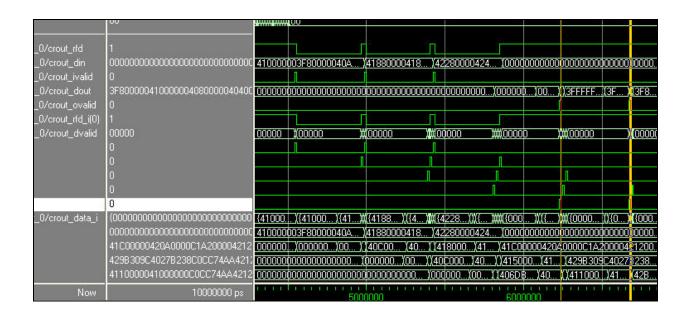

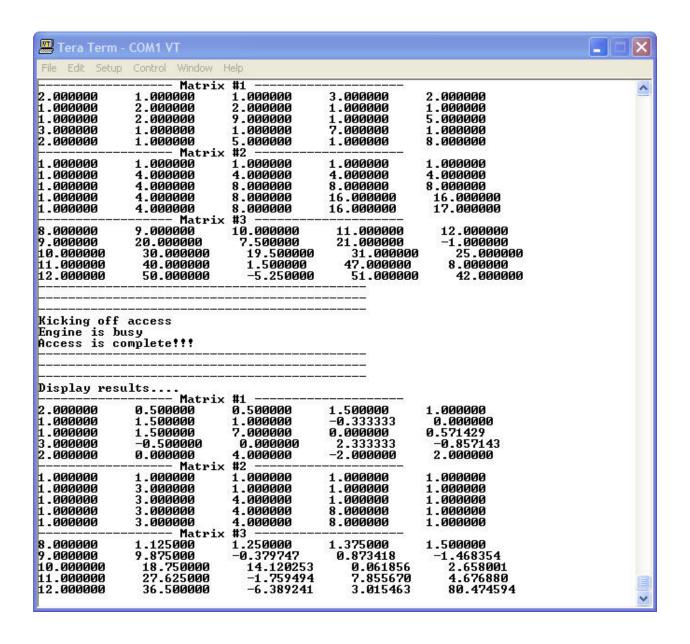

Once the user loads the matrix data via the testbench procedures that mimic CPU accesses, the user is required to strobe the control logic with the number of matrices to process. The simulation displays the expected solutions before proceeding. The testbench then polls the "busy flag" to wait for processing to complete. Once complete, the testbench displays the results. Moreover, assertions are added in the Crout code itself to show intermediate results as data is passing from stage to stage in the pipeline. Obviously, these assertions are not synthesized, but are useful for feedback during development.