# A CO-SIMULATION ENVIRONMENT FOR MIXED SIGNAL, MULTI-DOMAIN SYSTEM LEVEL DESIGN EXPLORATION

by

David Kent Reed

BS, University of Pittsburgh, 2002

Submitted to the Graduate Faculty of the School of Engineering in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

University of Pittsburgh

2004

# UNIVERSITY OF PITTSBURGH

# SCHOOL OF ENGINEERING

This thesis was presented

by

David K. Reed

It was defended on

July 20, 2004

and approved by

James T. Cain, Professor, Electrical Engineering

Raymond R. Hoare, Assistant Professor, Electrical Engineering

Thesis Advisor: Steven P. Levitan, Professor, Electrical Engineering

## A CO-SIMULATION ENVIRONMENT FOR MIXED SIGNAL, MULTI-DOMAIN SYSTEM LEVEL DESIGN EXPLORATION

David Kent Reed, MS

University of Pittsburgh, 2004

This thesis presents a system-level co-simulation environment for mixed domain design exploration. By employing shared memory IPC (Inter-Process Communication) and utilizing PDES (Parallel Discrete Event Simulation) techniques, we examine two methods of synchronization, lock-step and dynamic. We then compare the performance of these two methods on a series of test systems as well as real designs using the Chatoyant MOEMS (Micro-Electro Mechanical Systems) simulator and the mixed HDL (Hardware Description Language) simulator from Model Technology, ModelSim. The results collected are used to ascertain which method provides the best overall performance with the least overhead.

# TABLE OF CONTENTS

| ABSTRACT                                                         | iii      |

|------------------------------------------------------------------|----------|

| ACKNOWLEDGMENTS                                                  | .xiv     |

| 1.0 INTRODUCTION                                                 | 1        |

| 1.1 STATEMENT OF PURPOSE                                         | 5        |

| 1.2 STATEMENT OF WORK PERFORMED                                  | 5        |

| 1.3 LIMITATIONS OF WORKED PERFORMED                              | 6        |

| 1.4 CHAPTER DESCRIPTIONS                                         | 6        |

| 2.0 BACKGROUND                                                   | 9        |

| 2.1 MODELSIM                                                     | 9        |

| 2.2 PTOLEMY                                                      | 17       |

| 2.3 CHATOYANT: A MIXED SIGNAL, MULTI-DOMAIN MOEMS SIM<br>TOOL 23 | IULATION |

| 2.4 PROPOSING THE CHATOYANT/MODELSIM CO-SIMULATION               | 26       |

| 3.0 SIMULATION CONCEPTS AND CONSIDERATIONS                       | 28       |

| 3.1 DISCRETE EVENT SIMULATION FUNDAMENTALS                       | 29       |

| 3.1.1 Synchronous Simulation Methodology                         | 34       |

| 3.1.2 Asynchronous Simulation Methodology                        | 36       |

| 3.2 USING PDES FOR THE CHATOYANT/MODELSIM CO-SIM<br>INTERFACE    |          |

| 3.2.1 Lock-Step Co-Simulation                                    | 43       |

| 3.2.2 Dynamic Co-Simulation                       | 46  |

|---------------------------------------------------|-----|

| 3.3 DIGITAL/ANALOG SIGNAL TRANSFORMATION          | 52  |

| 3.4 CO-SIMULATION PERFORMANCE ANALYSIS            | 56  |

| 4.0 CO-SIMULATION ENVIRONMENT IMPLEMENTATION      | 58  |

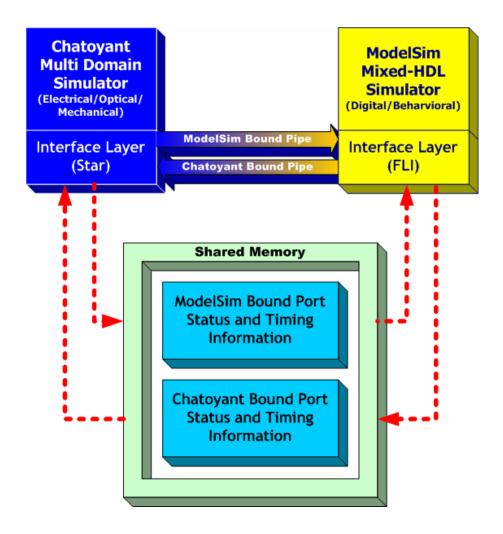

| 4.1 GENERAL CO-SIMULATION ARCHITECTURE            | 58  |

| 4.2 IMPLEMENTATION                                | 60  |

| 4.2.1 Common Structures and Methods               | 67  |

| 4.2.2 Chatoyant Interface Star                    | 67  |

| 4.2.3 ModelSim FLI Interface                      |     |

| 4.3 AUTOMATED CO-SIMULATION INTERFACE GENERATOR   |     |

| 5.0 SYSTEM APPLICATIONS                           |     |

| 5.1 INTRODUCTION                                  |     |

| 5.2 SINGLE BIT, MODELSIM TO CHATOYANT APPLICATION |     |

| 5.2.1 System Description                          |     |

| 5.2.2 Runtime Results and Analysis                |     |

| 5.3 SINGLE BIT, CHATOYANT TO MODELSIM APPLICATION |     |

| 5.3.1 System Description                          |     |

| 5.3.2 Runtime Results and Analysis                |     |

| 5.4 MULTI-BIT, MODELSIM TO CHATOYANT APPLICATION  | 101 |

| 5.4.1 System Description                          | 101 |

| 5.4.2 Runtime Results and Analysis                | 104 |

| 5.5 MULTI-BIT, CHATOYANT TO MODELSIM APPLICATION  | 108 |

| 5.5.1 System Description                          | 108 |

| 5.5.2 Runtime Results and Analysis                          | . 111 |

|-------------------------------------------------------------|-------|

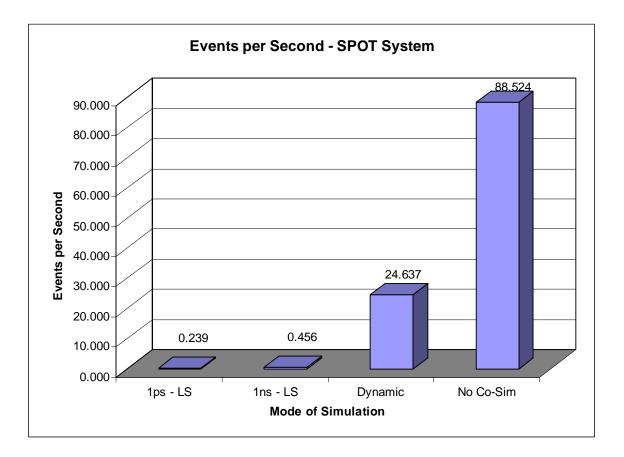

| 5.6 SMART PIXEL OPTICAL TRANSCEIVER – SPOT                  | . 116 |

| 5.6.1 System Description                                    | . 116 |

| 5.6.2 Runtime Results and Analysis                          | . 120 |

| 5.7 FIBER IMAGE GUIDE - FIG                                 | . 126 |

| 5.7.1 System Description                                    | . 126 |

| 5.7.2 System Description                                    | . 130 |

| 5.8 ANALYSIS OF RESULTS                                     | . 136 |

| 6.0 CONCLUSION AND FUTURE WORK                              | . 145 |

| 6.1 PURPOSE RESTATED                                        | . 145 |

| 6.2 THESIS SUMMARY                                          | . 146 |

| 6.3 WORK PERFORMED                                          | . 147 |

| 6.4 CONCLUSIONS FROM RESULTS                                | . 147 |

| 6.5 FUTURE WORK                                             | . 148 |

| APPENDIX A - TERMS                                          | . 150 |

| APPENDIX B – SINGLE-BIT MODELSIM TO CHATOYANT RESULTS       | . 152 |

| APPENDIX C – SINGLE-BIT CHATOYANT TO MODELSIM RESULTS       | . 156 |

| APPENDIX D – MULTI-BIT MODELSIM TO CHATOYANT RESULTS        | . 160 |

| APPENDIX E – MULTI-BIT CHATOYANT TO MODELSIM RESULTS        | . 165 |

| APPENDIX F - SMART PIXEL OPTICAL TRANSCEIVER (SPOT) RESULTS | . 169 |

| APPENDIX G – FIBER IMAGE GUIDE (FIG) RESULTS                | . 173 |

| BIBLIOGRAPHY                                                | . 177 |

# LIST OF TABLES

| Table 1 Voltage to MVL-9 mapping for a generic 5V CMOS technology (voltages <sup>(26)</sup> )          | s provided in<br>55 |

|--------------------------------------------------------------------------------------------------------|---------------------|

| Table 2 Single-bit, ModelSim to Chatoyant Lock-Step Data                                               | 152                 |

| Table 3 Single-bit, ModelSim to Chatoyant Lock-Step events per second                                  | 152                 |

| Table 4 Single-bit, ModelSim to Chatoyant 1ps lock-step code profile                                   | 153                 |

| Table 5 Single-bit, ModelSim to Chatoyant 1ns lock-step code profile                                   | 153                 |

| Table 6 Single-bit, ModelSim to Chatoyant dynamic co-simulation results                                | 154                 |

| Table 7 Single-bit, ModelSim to Chatoyant dynamic co-simulation events per second                      | d 154               |

| Table 8 Single-bit, ModelSim to Chatoyant dynamic co-simulation code profile                           | 154                 |

| Table 9 Single-bit, ModelSim to Chatoyant event processing profile for Chatoyant dynamic co-simulation | •                   |

| Table 10 Single-bit, ModelSim to Chatoyant runtime and events per second for no c<br>in ModelSim.      |                     |

| Table 11 Single-bit, Chatoyant to ModelSim Lock-Step Data                                              | 156                 |

| Table 12 Single-bit, Chatoyant to ModelSim Lock-Step events per second                                 | 156                 |

| Table 13 Single-bit, Chatoyant to ModelSim 1ps lock-step code profile                                  | 157                 |

| Table 14 Single-bit, Chatoyant to ModelSim 1ns lock-step code profile                                  | 157                 |

| Table 15 Single-bit, Chatoyant to ModelSim dynamic co-simulation results                               | 158                 |

| Table 16 Single-bit, Chatoyant to ModelSim dynamic co-simulation events per second                     | nd158               |

| Table 17 Single-bit, Chatoyant to ModelSim dynamic co-simulation code profile                          | 158                 |

| Table 18 Single-bit, Chatoyant to ModelSim event processing profile for Chatoyant running the dynamic co-simulation                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 19 Single-bit, Chatoyant to ModelSim runtime and events per second for no co-simulation in Chatoyant                                                                                                                                                                                                                                                                                                                                       |

| Table 20 Multi-bit, ModelSim to Chatoyant lock-step data    160                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 21 Multi-bit, ModelSim to Chatoyant lock-step events per second       160                                                                                                                                                                                                                                                                                                                                                                  |

| Table 22 Multi-bit, ModelSim to Chatoyant 1ps lock-step code profile       162                                                                                                                                                                                                                                                                                                                                                                   |

| Table 23 Multi-bit, ModelSim to Chatoyant 1ns lock-step code profile       162                                                                                                                                                                                                                                                                                                                                                                   |

| Table 24 Multi-bit, ModelSim to Chatoyant dynamic co-simulation results 163                                                                                                                                                                                                                                                                                                                                                                      |

| Table 25 Multi-bit, ModelSim to Chatoyant dynamic co-simulation events per second 163                                                                                                                                                                                                                                                                                                                                                            |

| Table 26 Multi-bit, ModelSim to Chatoyant dynamic co-simulation code profile 163                                                                                                                                                                                                                                                                                                                                                                 |

| Table 27 Multi-bit, ModelSim to Chatoyant event processing profile for Chatoyant running the dynamic co-simulation                                                                                                                                                                                                                                                                                                                               |

| Table 28 Multi-bit, ModelSim to Chatoyant runtime and events per second for no co-simulation in ModelSim                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data    165                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data    165                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data165Table 30 Multi-bit, Chatoyant to ModelSim lock-step events per second165                                                                                                                                                                                                                                                                                                              |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data165Table 30 Multi-bit, Chatoyant to ModelSim lock-step events per second165Table 31 Multi-bit, Chatoyant to ModelSim 1ps lock-step code profile166                                                                                                                                                                                                                                       |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data165Table 30 Multi-bit, Chatoyant to ModelSim lock-step events per second165Table 31 Multi-bit, Chatoyant to ModelSim 1ps lock-step code profile166Table 32 Multi-bit, Chatoyant to ModelSim 1ns lock-step code profile166                                                                                                                                                                |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data165Table 30 Multi-bit, Chatoyant to ModelSim lock-step events per second165Table 31 Multi-bit, Chatoyant to ModelSim 1ps lock-step code profile166Table 32 Multi-bit, Chatoyant to ModelSim 1ns lock-step code profile166Table 33 Multi-bit, Chatoyant to ModelSim dynamic co-simulation results167                                                                                      |

| Table 29 Multi-bit, Chatoyant to ModelSim lock-step data165Table 30 Multi-bit, Chatoyant to ModelSim lock-step events per second165Table 31 Multi-bit, Chatoyant to ModelSim 1ps lock-step code profile166Table 32 Multi-bit, Chatoyant to ModelSim 1ns lock-step code profile166Table 33 Multi-bit, Chatoyant to ModelSim dynamic co-simulation results167Table 34 Multi-bit, Chatoyant to ModelSim dynamic co-simulation events per second 167 |

| Table 38 SPOT lock-step data    169                                                      |   |

|------------------------------------------------------------------------------------------|---|

| Table 39 SPOT lock-step events per second                                                |   |

| Table 40 SPOT 1ps lock-step code profile    170                                          |   |

| Table 41 SPOT 1ns lock-step code profile    170                                          |   |

| Table 42 SPOT dynamic co-simulation results    171                                       |   |

| Table 43 SPOT dynamic co-simulation events per second    171                             |   |

| Table 44 SPOT dynamic co-simulation code profile                                         |   |

| Table 45 SPOT vent processing profile for Chatoyant running the dynamic co-simulation172 | 2 |

| Table 46 SPOT runtime and events per second for no co-simulation in ModelSim 172         |   |

| Table 47 FIG lock-step data                                                              |   |

| Table 48 FIG lock-step events per second    173                                          |   |

| Table 49 FIG 1ps lock-step code profile                                                  |   |

| Table 50 FIG 1ns lock-step code profile                                                  |   |

| Table 51 FIG dynamic co-simulation results    175                                        |   |

| Table 52 FIG dynamic co-simulation events per second                                     |   |

| Table 53 FIG dynamic co-simulation code profile    175                                   |   |

| Table 54 FIG event processing profile for Chatoyant running the dynamic co-simulation176 |   |

| Table 55 FIG runtime and events per second for no co-simulation in Chatoyant 176         |   |

# LIST OF FIGURES

| Figure 1 Reproduction of ModelSim's VHDL simulation flow using a discrete event methodology <sup>(30)</sup>            |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 2 A snapshot of the ModelSim graphical environment from a test design simulation <sup>(44)</sup>                |

| Figure 3 How blocks connect through portholes and how particles are transferred between them in Ptolemy <sup>(7)</sup> |

| Figure 4 Illustration of a Ptolemy Universe with Stars and Galaxies, derived from <sup>(7)</sup> 20                    |

| Figure 5 The modeling process, in Chatoyant, for non-linear devices <sup>(39)</sup>                                    |

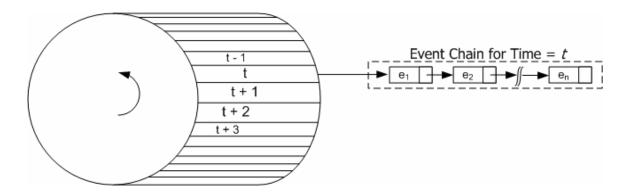

| Figure 6 Representation of a Discrete Event Scheduler as a timing wheel, adapted from <sup>(12)</sup>                  |

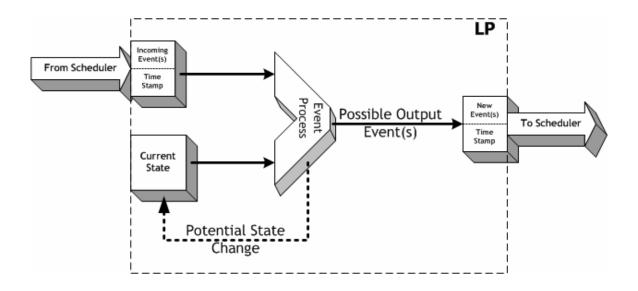

| Figure 7 Generalized LP block diagram                                                                                  |

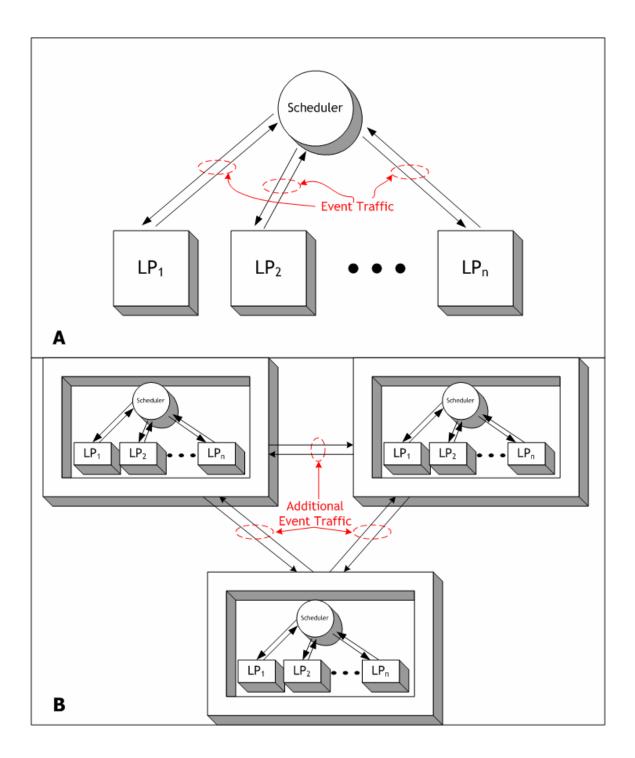

| Figure 8 The sequential simulation (A) architecture and the asynchronous PDES (B) architecture                         |

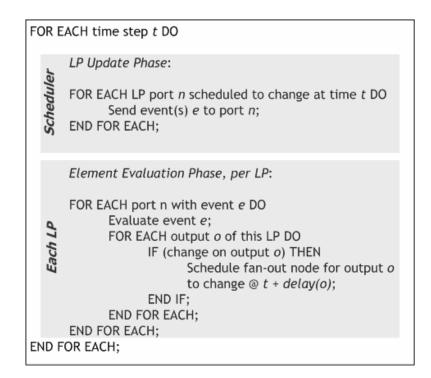

| Figure 9 Pseudo code for the synchronous PDES algorithm <sup>(12)</sup>                                                |

| Figure 10 Asynchronous, conservative based PDES synchronization pseudo code <sup>(12)</sup> 38                         |

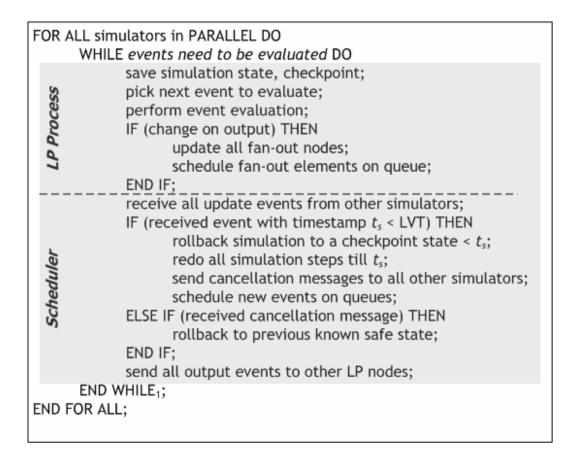

| Figure 11 Asynchronous optimistic synchronization pseudo code reproduced from <sup>(12)</sup> . 41                     |

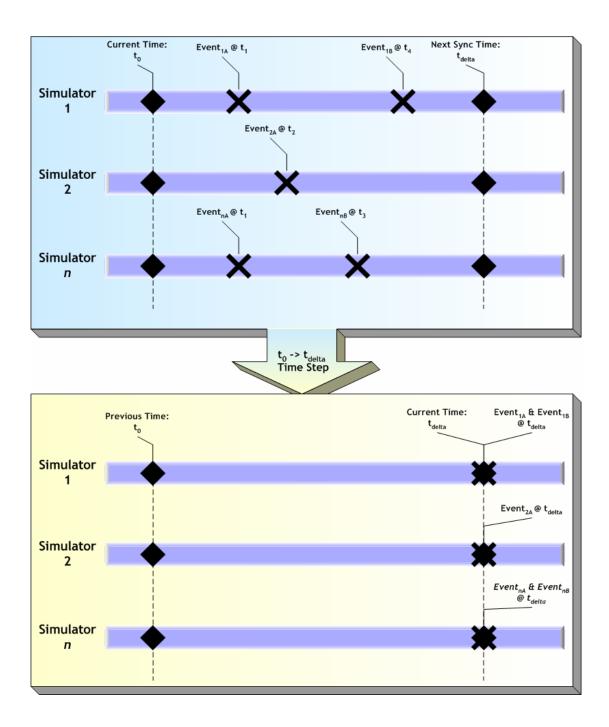

| Figure 12 An example of a lock-step co-simulation                                                                      |

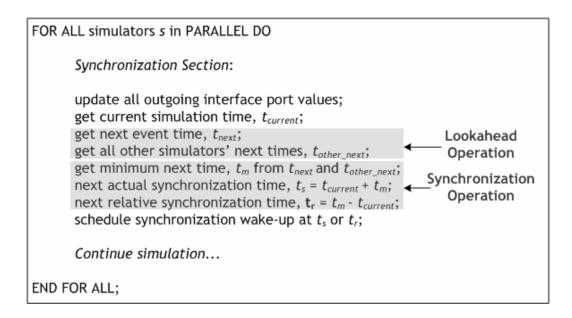

| Figure 13 Dynamic synchronization pseudo code adapted from <sup>(16)</sup>                                             |

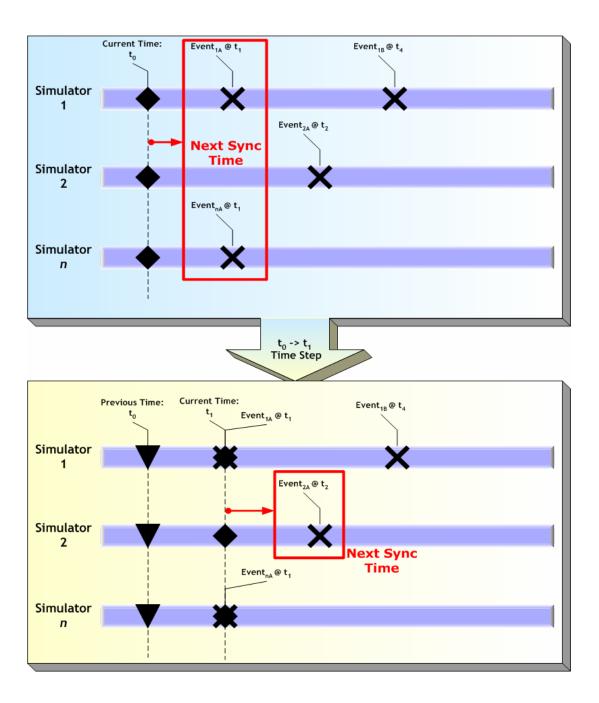

| Figure 14 Our example of dynamic synchronization                                                                       |

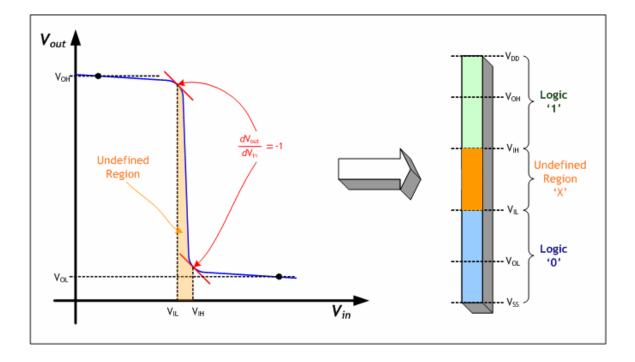

| Figure 15 Sample voltage threshold graph for TTL and CMOS technologies adapted from <sup>(26)</sup>                    |

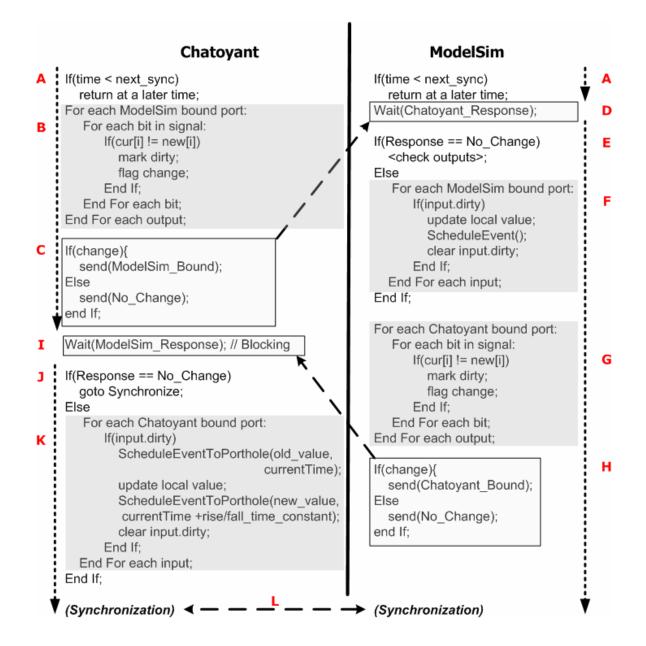

| Figure 17 Synchronization independent interface pseudo code for both ModelSim and Chatoyant          |

|------------------------------------------------------------------------------------------------------|

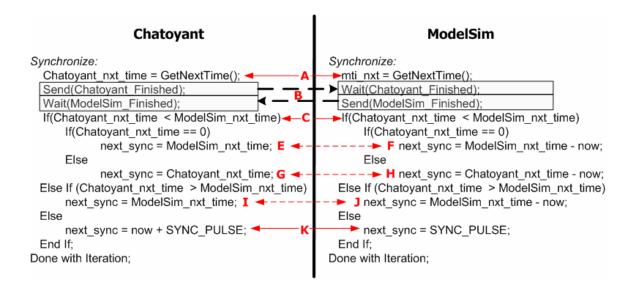

| Figure 18 The dynamic synchronization pseudo code                                                    |

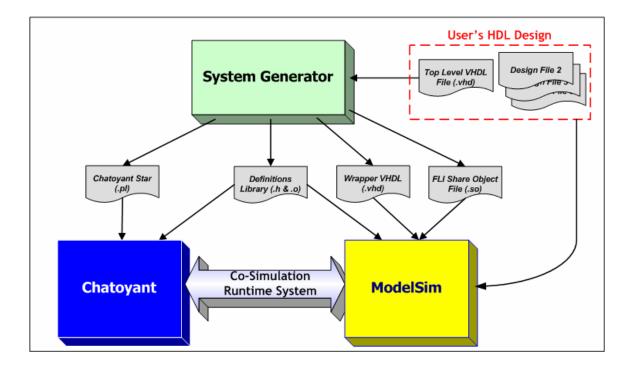

| Figure 19 Co-Simulation system flow with the generator                                               |

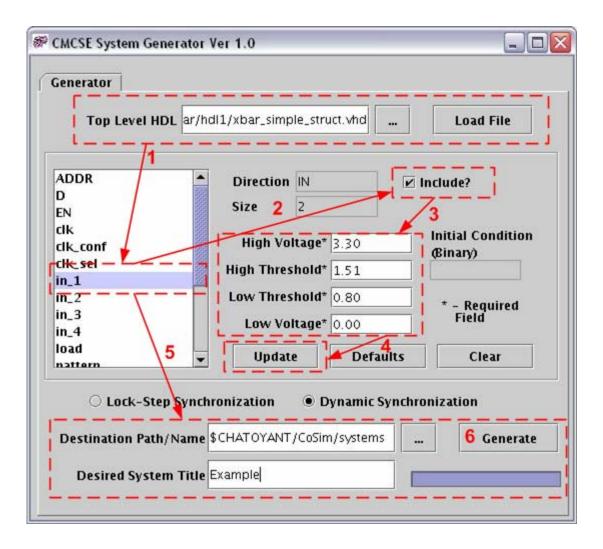

| Figure 20 Chatoyant-ModelSim Co-Simulation Environment System Generator GUI snapshot                 |

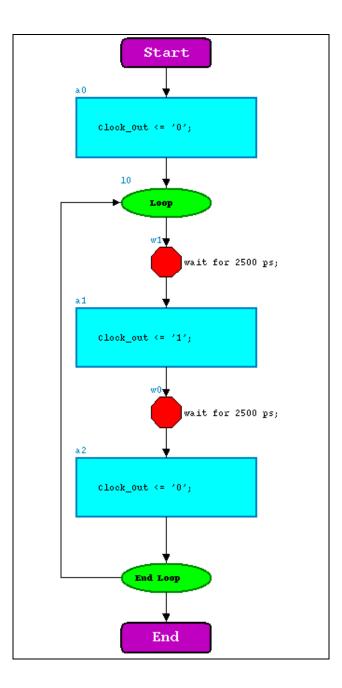

| Figure 21 ModelSim behavioral VHDL for the single bit clock from ModelSim to Chatoyant               |

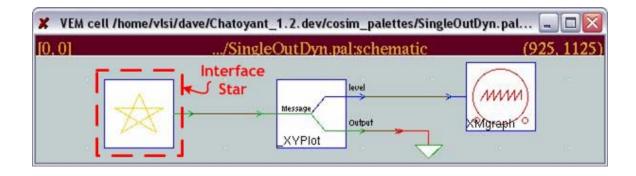

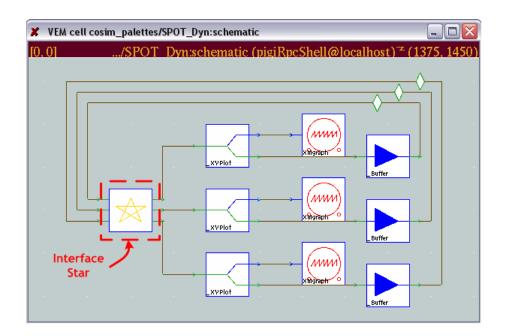

| Figure 22 The Chatoyant side of the single-bit from ModelSim (Dynamic system shown)86                |

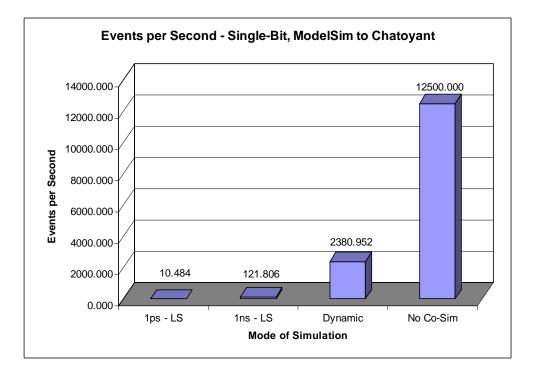

| Figure 23 The events per second for the single-bit, ModelSim to Chatoyant test system 88             |

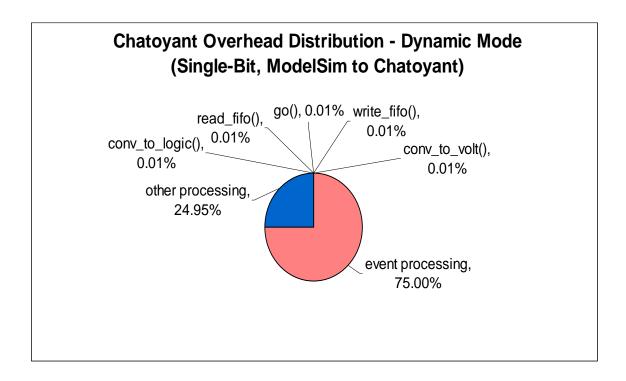

| Figure 24 The Chatoyant runtime distribution graph for the dynamic synchronization co-<br>simulation |

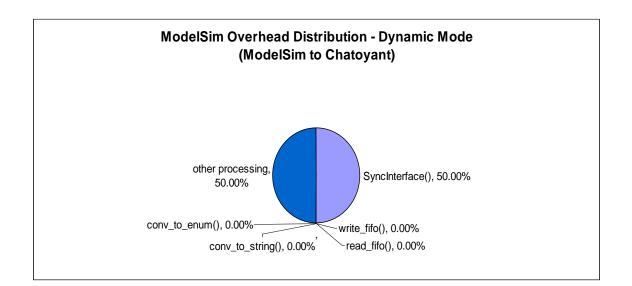

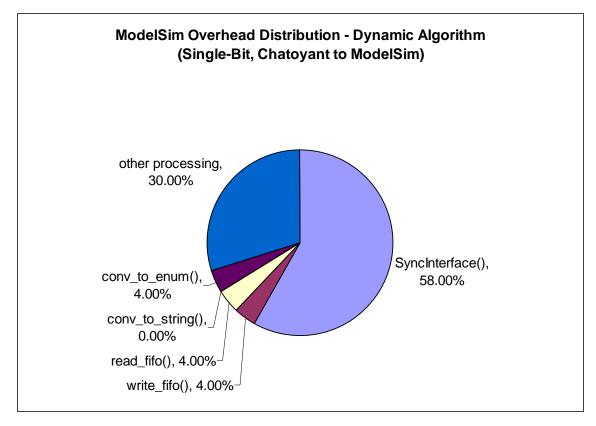

| Figure 25 The ModelSim overhead distribution graph for the dynamic co-simulation 91                  |

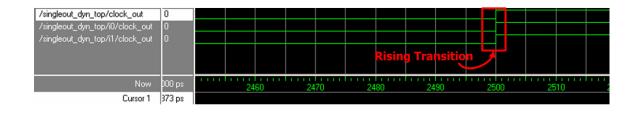

| Figure 26 ModelSim waveform for the single-bit, ModelSim to Chatoyant system in dynamic mode         |

| Figure 27 Chatoyant waveform for the single-bit, ModelSim to Chatoyant co-simulation in dynamic mode |

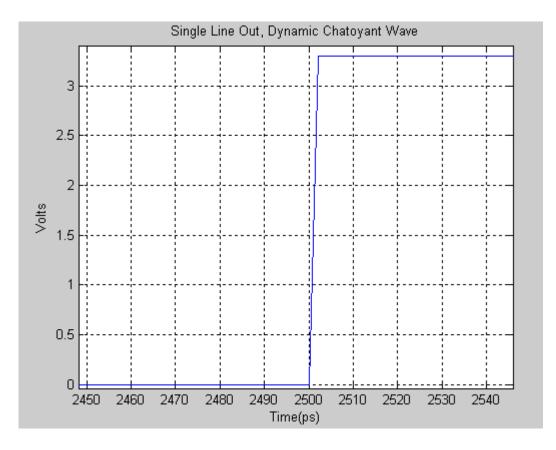

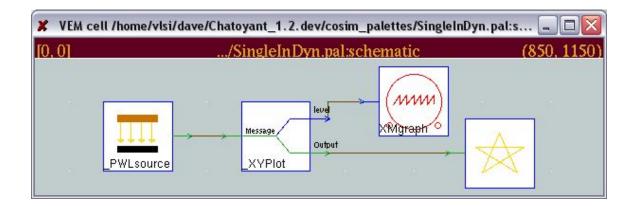

| Figure 28 The Chatoyant palette for the single-bit, Chatoyant to ModelSim test system 94             |

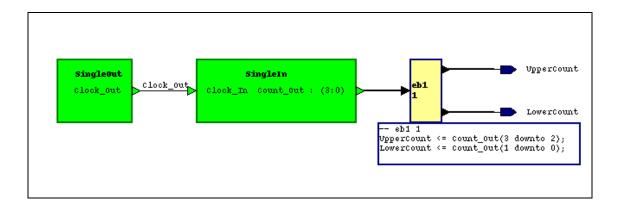

| Figure 29 VHDL source code for the counter that will use the single bit from the interface95         |

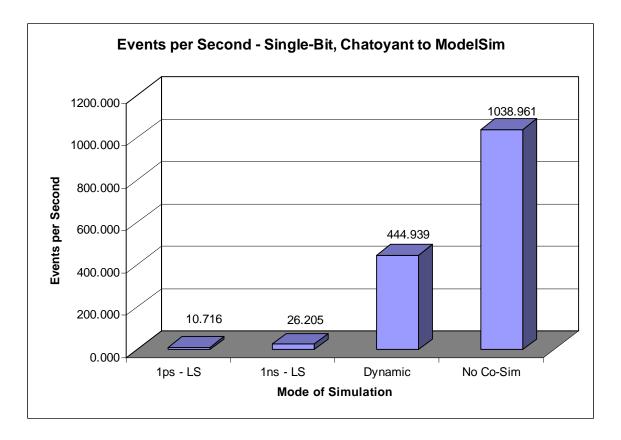

| Figure 30 The events per second for the single-bit, Chatoyant to ModelSim execution modes            |

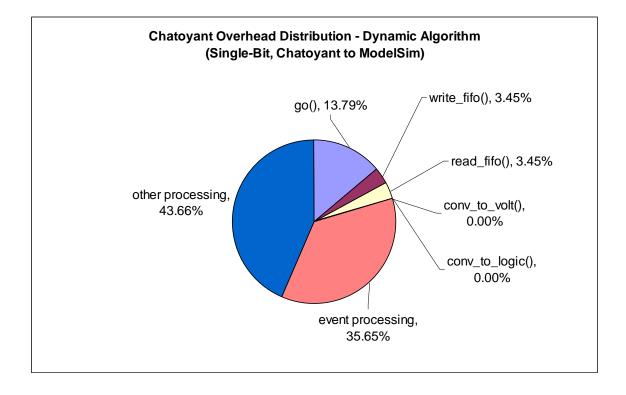

| Figure 31 The Chatoyant code profile using the dynamic synchronization                               |

| Figure 32 The ModelSim code profile for the dynamic synchronization                                  |

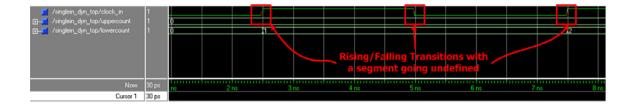

| Figure 33 The Chatoyant waveform using the dynamic synchronization mode 100                          |

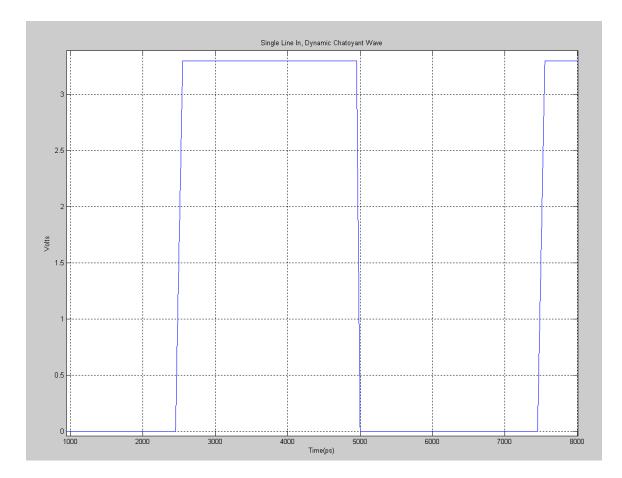

| Figure 34 The ModelSim waveform using the dynamic synchronization mode 100                           |

| Figure 35 VHDL based block diagram for the multi-bit test system from ModelSim to Chatoyant |

|---------------------------------------------------------------------------------------------|

|                                                                                             |

|                                                                                             |

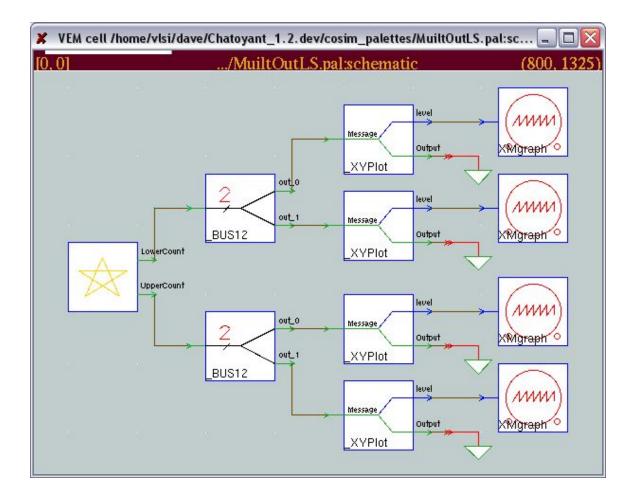

Figure 36 The Chatoyant palette for the multi-bit test from ModelSim to Chatoyant ... 103

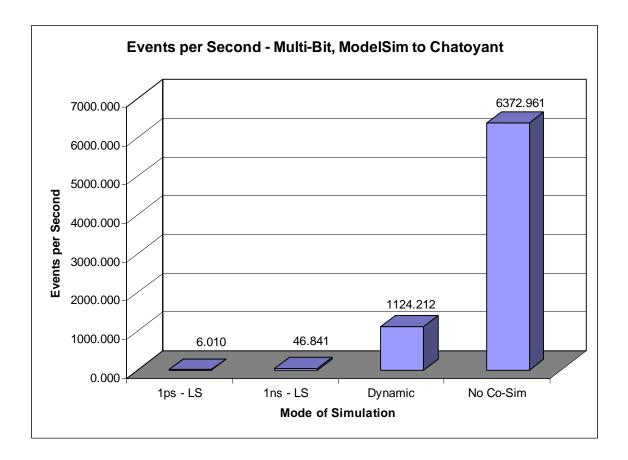

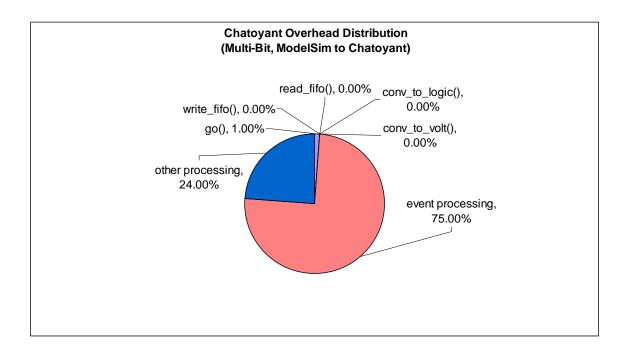

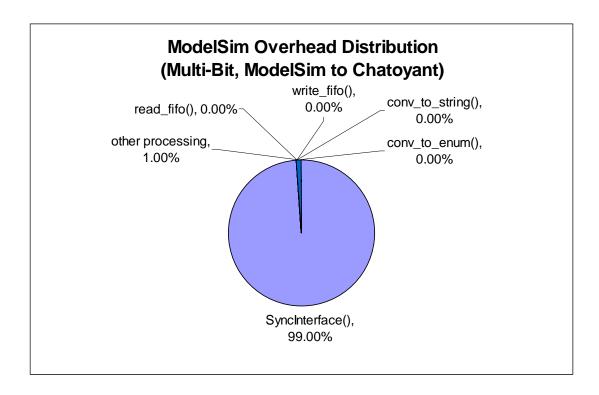

Figure 37 The events per second for the multi-bit, ModelSim to Chatoyant test system104

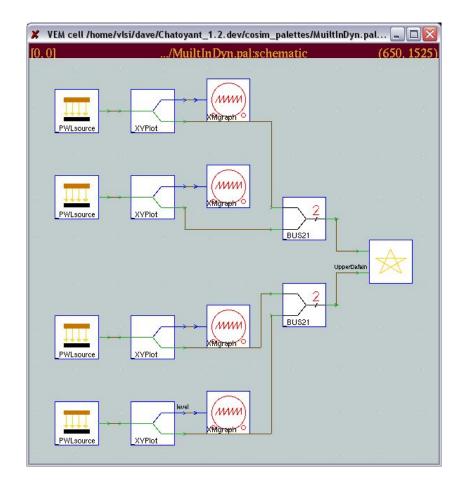

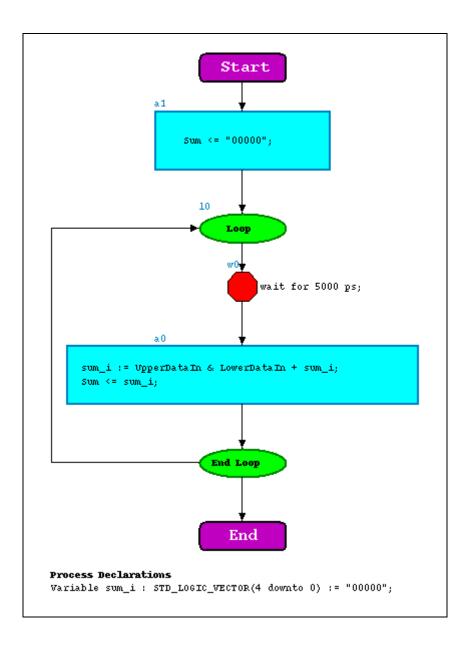

Figure 42 Chatoyant palette for the multi-bit, Chatoyant to ModelSim test system ..... 109

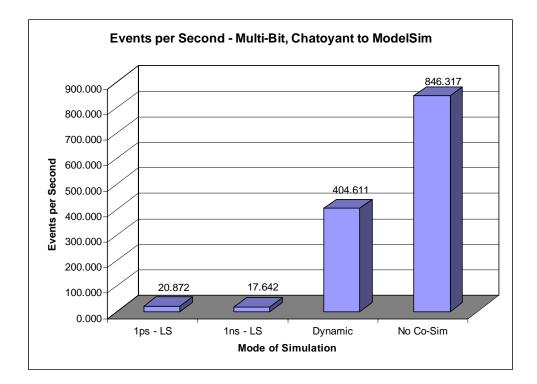

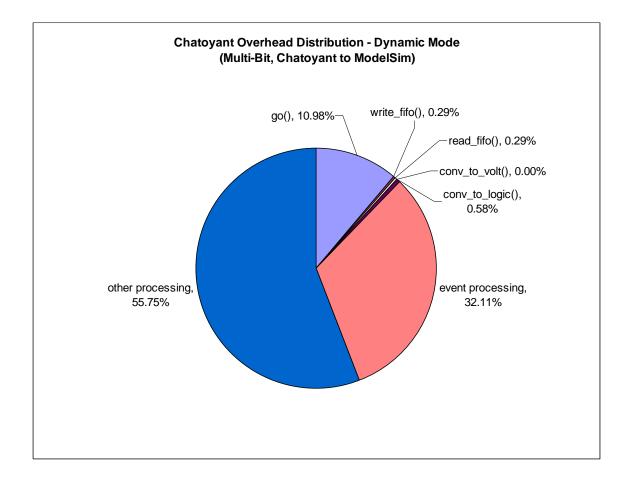

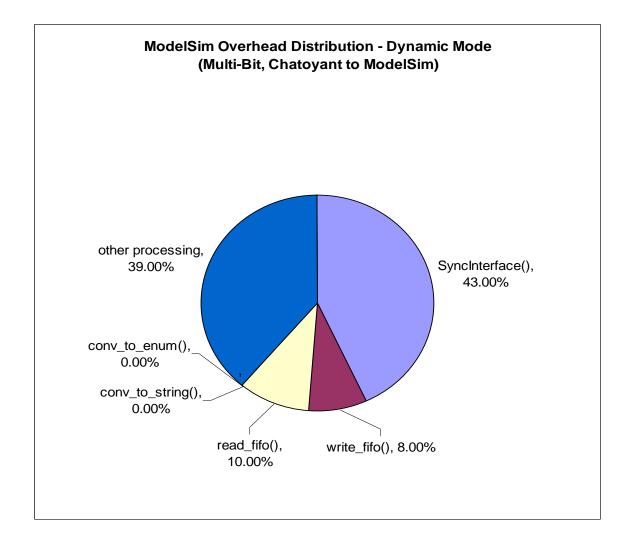

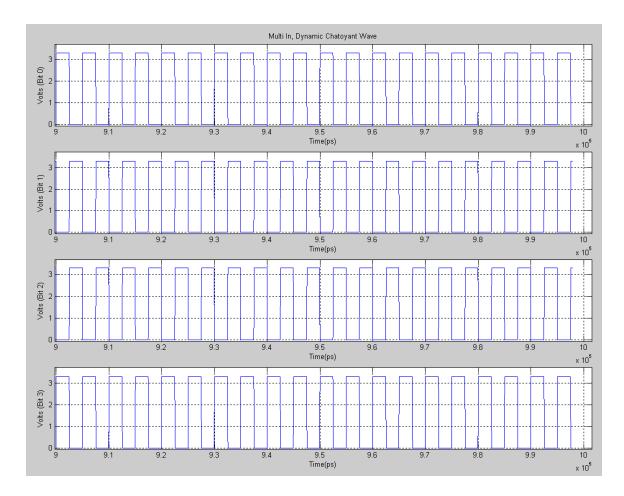

- Figure 44 Events per second results for the multi-bit, Chatoyant to ModelSim test system111

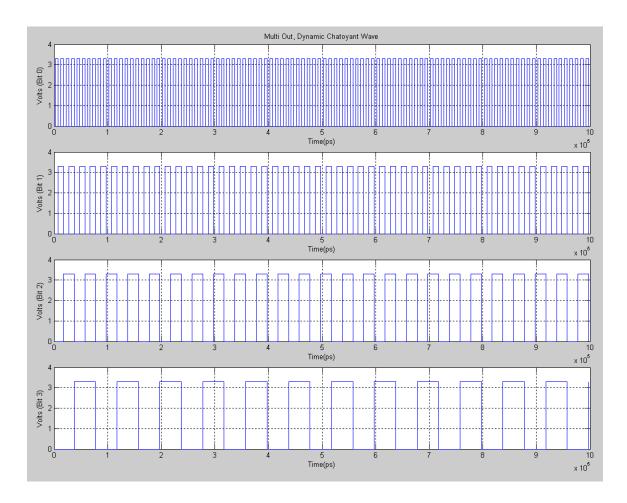

- Figure 47 Chatoyant waveform for the multi-bit, Chatoyant to ModelSim test system. 115

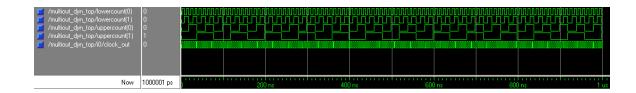

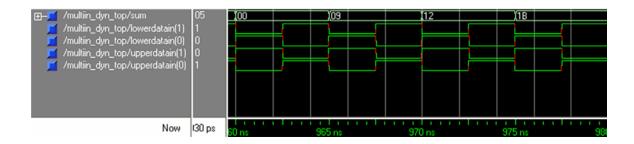

Figure 48 ModelSim waveform for the multi-bit, Chatoyant to ModelSim test system 116

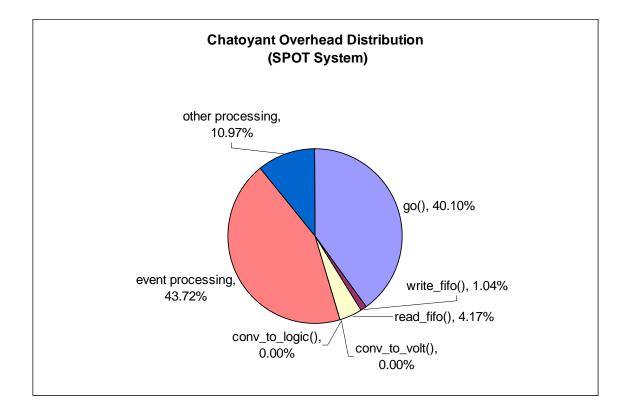

- Figure 53 Chatoyant code profile for the SPOT system in dynamic mode ...... 122

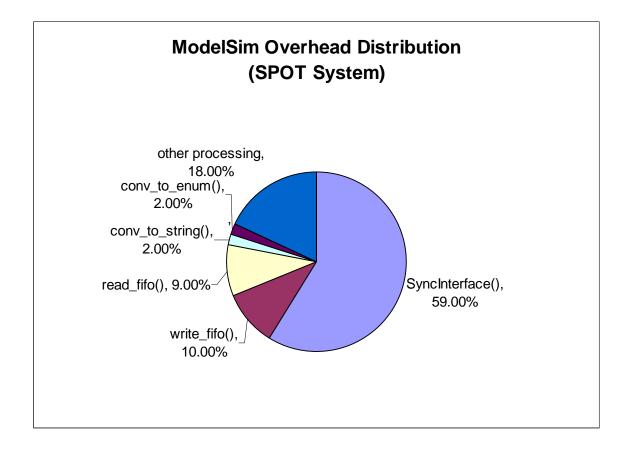

| Figure 54 ModelSim code profile for the SPOT system in dynamic mode 123                                       |

|---------------------------------------------------------------------------------------------------------------|

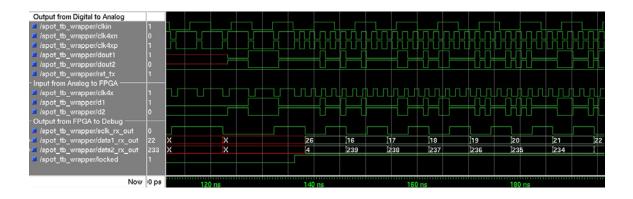

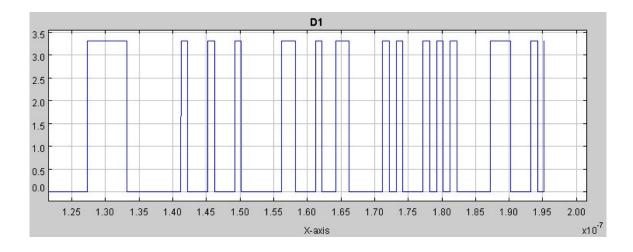

| Figure 55 ModelSim waveform for the SPOT test system in dynamic mode 124                                      |

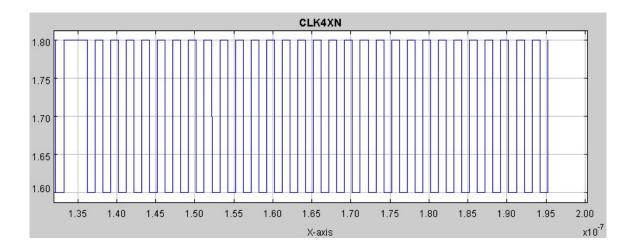

| Figure 56 Chatoyant waveform for the 4X clock for the SPOT system in dynamic mode124                          |

| Figure 57 Chatoyant waveform for the first data channel for the SPOT system in dynamic mode                   |

| Figure 58 Chatoyant waveform for the second data channel for the SPOT system in dynamic mode                  |

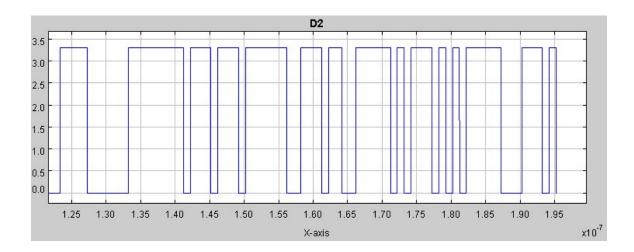

| Figure 59 The FIG MCM architecture <sup>(42)</sup>                                                            |

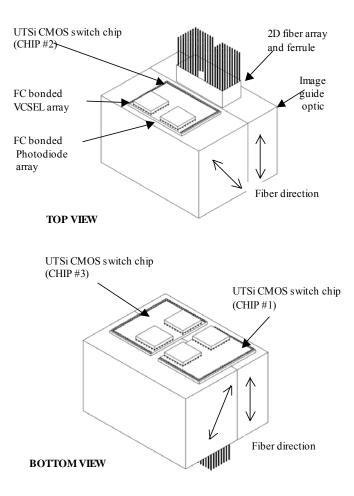

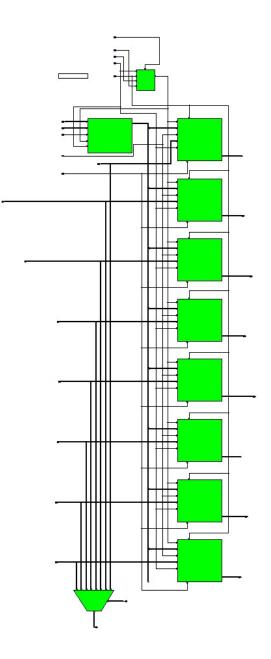

| Figure 60 Chatoyant palette for the FIG co-simulation test 128                                                |

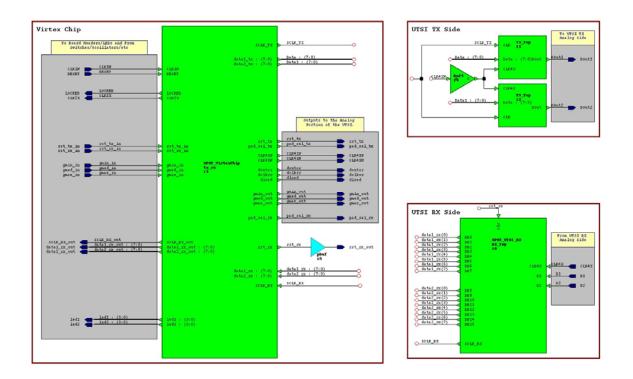

| Figure 61 VHDL diagram of the FIG crossbar chip <sup>(41, 42)</sup>                                           |

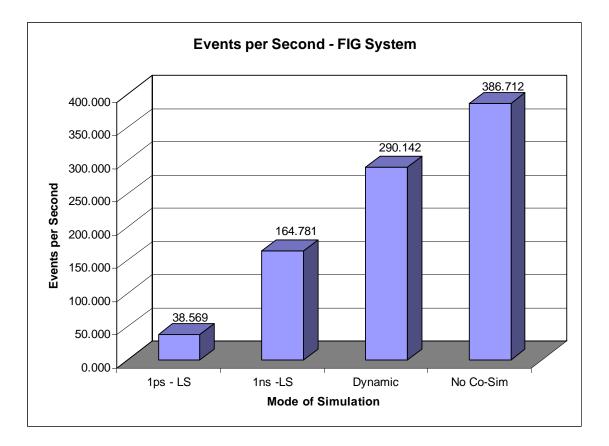

| Figure 62 Events per second measurement for the FIG simulation                                                |

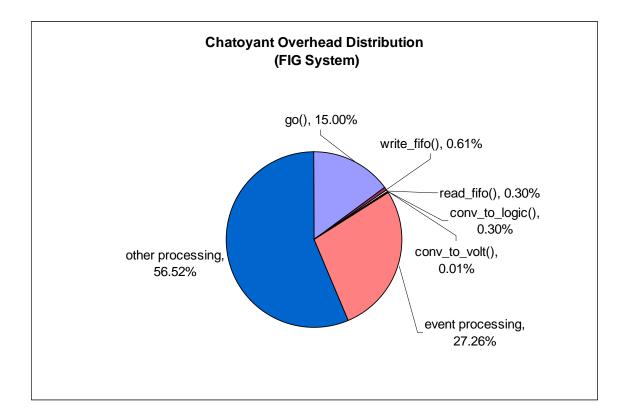

| Figure 63 Chatoyant code profile for the FIG co-simulation in dynamic mode 132                                |

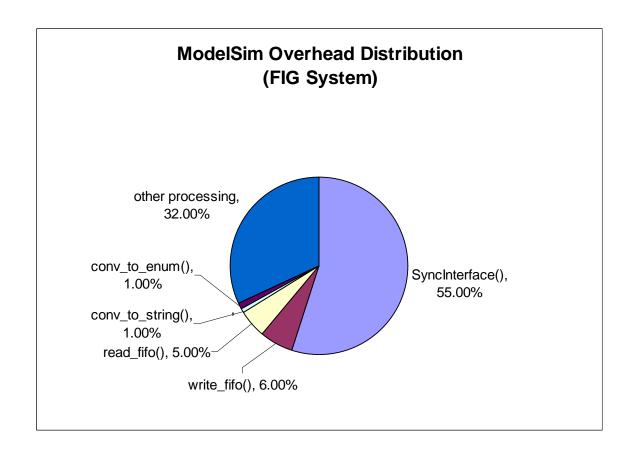

| Figure 64 ModelSim code profile for the FIG co-simulation in dynamic mode                                     |

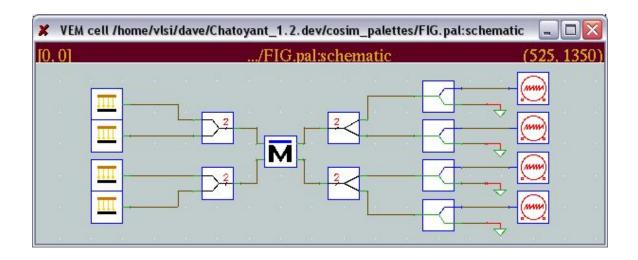

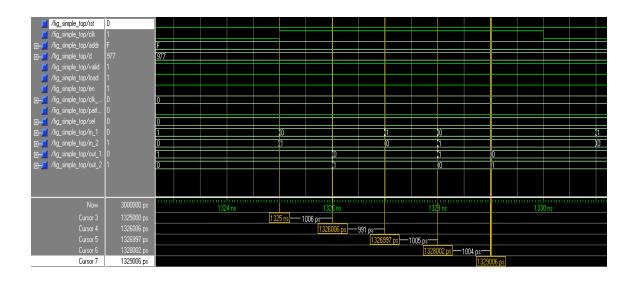

| Figure 65 ModelSim waveform for the FIG co-simulation in dynamic mode 134                                     |

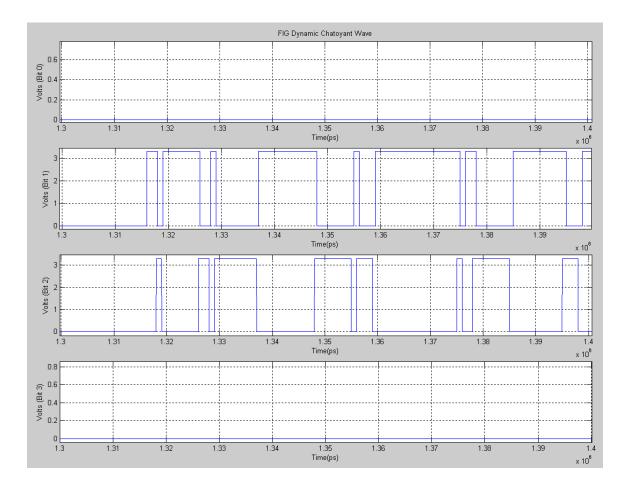

| Figure 66 Chatoyant waveform for the FIG co-simulation using the dynamic mode 135                             |

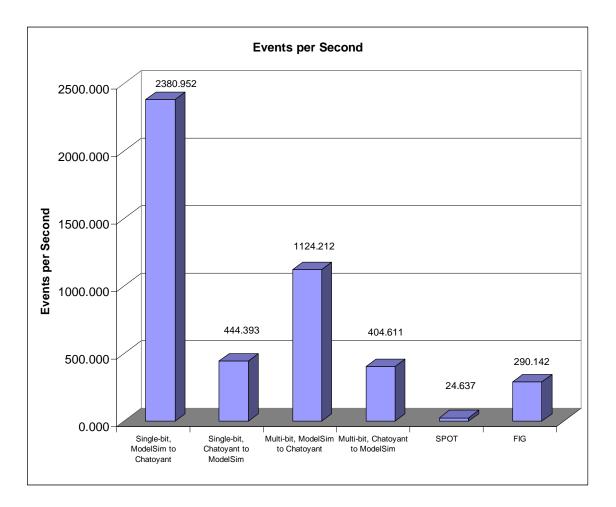

| Figure 67 Summary of events per second for the six systems discussed in this chapter 137                      |

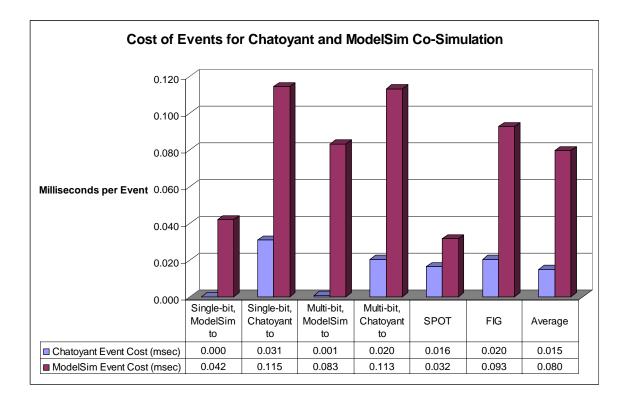

| Figure 68 Time calculations spent on an event in the co-simulation interface for both Chatoyant and ModelSim  |

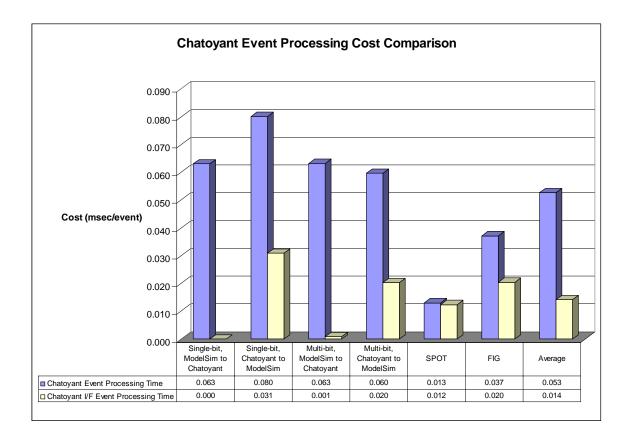

| Figure 69 Event processing cost comparison between Chatoyant and the co-simulation interface within Chatoyant |

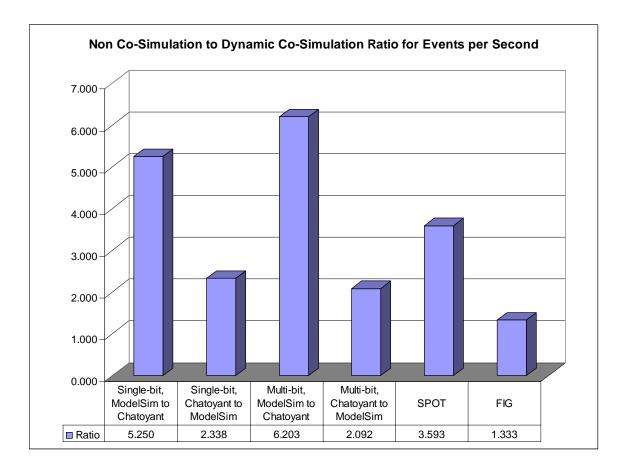

| Figure 70 Ratio of non co-simulation to dynamic co-simulation events per second 143                           |

#### ACKNOWLEDGMENTS

First, I sincerely thank Dr. Steve Levitan, my advisor, for the awesome opportunity to work with him. His guidance and discipline has transformed me, in many ways, into a harder worker and more versatile engineer. Secondly, I would like to thank Dr. Ray Hoare for his time and effort in evaluating my work and for being an important part in the completion of my thesis. I extend a special thanks to Dr Tom Cain for his help and guidance throughout my graduate experience, including being a part of the completion of my thesis work.

I extend my thanks and everlasting friendship to the many friends I have made in the Keystone CAD group, both past and present. Jason, Mike, Craig, Jose, Majd, and Amit: you all have been incredibly supportive and good friends. I especially thank Jason for his diligent help in helping me during this project. I also would like to thank Gustavo for being a good friend and partner in the struggle for attaining our Master's degrees. I wish all of you the best of luck in all of your endeavors.

I would not be here if it had not been for the love and support of my parents, sister, and the rest of my family. They have been there in thick and thin. I specially thank my mother for being the best help and critic in the world and my father for being the supporter of my many conquests throughout life. I also thank my sister for being a great sounding board and sharing those midnight trips to eat and shop. I also thank my grandmother for her prayers that helped me through everything, as well as the rest of my grandparents, wherever they may be. I also thank my new family, Mariya and Josef, for their support and help throughout the past 3 ½ years.

Lastly, though he is not family, I would like to thank Scott for being the brother I never had and his support since we first met at Engineering 11.

Lastly, I cannot begin to find the words and emotions to thank my wife, Juliya. She has been my biggest fan and the source of my sanity throughout everything. Without her I would truly be lost and still looking for my way. I can only hope that this work and everything that I will do can prove to her that I am worthy of everything she has done for me. I can only say to you, Julz, Я тебя люблю.

## **1.0 INTRODUCTION**

There have been significant advances in the area of mixed signal technologies in terms of digital and analog circuits as well as optical and mechanical devices. Using System-on-a-Chip (SoC) concepts and fabrication mechanisms such as Multi-Chip-Modules (MCM), these four technologies can now be integrated together permitting a new realm of system development. Such developments as Micro-Electro-Mechanical Systems (MEMS) and Micro-Optical-Electro-Mechanical Systems (MOEMS) are possible and thus advancing computing technology <sup>(1, 2)</sup>.

With the above in mind, there have been efforts put forth in designing the verification tools used for these systems, however, mostly pertaining to a specific domain. Due to the complexity of these systems, it is difficult to verify that all components are operating correctly. This difficulty lies in the fact that there are not many tools that provide end-to-end simulation of MEMS or MOEMS <sup>(2)</sup>.

Nevertheless, the need for a system wide simulation tool that can prove digital, analog, mechanical, and optical components that all function together is evident. Also, such a system simulation must be as fast and accurate as possible. One way to provide these features is to create a co-simulation environment that is capable of handling the digital, analog, mechanical, and optical technological domains. Each domain is handled by the most fitting simulator available and then coupled via an efficient co-simulation architecture. This in turn provides a system simulation environment needed to perform analysis and verification.

A complete system level simulation encompasses and examines many aspects required to verify that every component will function and operate with other pieces of the system. Unlike circuit or digital simulation and likewise mechanical or optical modeling and analysis, all of which focus on a particular domain, system level simulation must process every element, regardless of its physical domain, simultaneously.

In examining modern co-simulation technology, we have found that much of the current research on system simulation is in the realm of embedded system design <sup>(3, 4, 5)</sup>. This involves the co-simulation of both hardware and software systems in a framework or toolset. Hardware/software co-verification is limited to RTL or behavioral hardware description language (HDL) simulation and an interface to an instruction set simulator (ISS) <sup>(5)</sup>. As a result, design exploration and verification is reduced to digital and software based analysis and does not typically account for analog circuitry, mechanical modeling, or optical analysis.

Optical and mechanical simulation typically involves performing both static as well as dynamic analysis. Static simulation is used to measure mechanical tolerance, crosstalk, as well as power and insertion loss. Dynamic simulation analyzes noise, data streams, and bit error rates <sup>(1)</sup>. The simulations just mentioned, whether static or dynamic, are typically performed in a simulator created for a certain physical domain <sup>(2)</sup>. Examples of such tools are ANSYS Finite Element Analysis <sup>(8)</sup> for mechanical modeling and RSoft for optical analysis <sup>(9)</sup>.

There is an attempt to unify the simulation environment for the physical domains found within MOEM systems with a common toolset and language. The core concept is to provide a universal language that has the capability to describe the behavioral functionality of every domain found in a system. Once this description is created, a software simulator is utilized to perform a system level simulation <sup>(4)</sup>. This is seen in the many SystemC simulators and language

flavors available <sup>(3)</sup>. This concept, coupled with the use of HDL's and other modeling techniques, provides a method for performing system level simulation <sup>(3, 4)</sup>.

When considering system level description languages such as SystemC, there are other languages available for modeling system level components. These languages are based on the hardware description language (HDL) varieties available for digital system design. Mixed Signal HDL's provide a designer with the same language semantics already found in the digital system realm, however, with the added benefit providing facilities to describe other components <sup>(2)</sup>. Examples of the Mixed Signal HDL's are VHDL-AMS and Verilog A. VHDL-AMS is an extension to the VHDL 93 language. VHDL-AMS provides the facility to describe mathematical expressions as well as maintaining a larger built-in type definition for real voltages, lumens for optics, and force measurements for mechanical simulations <sup>(10)</sup>. Similarly, Verilog-A is built on the similar constructs of Verilog, providing the same modeling capabilities as VHDL-AMS <sup>(10)</sup>.

Utilizing a higher level object-oriented approach, C++ is also a viable option for system level modeling. For purposes of this thesis as well as an example of the using C++, Chatoyant provides an environment for simulating components, independent of what their behavior is, in a true mixed-signal, multi-domain platform. Chatoyant, built on and utilizing Ptolemy <sup>(1, 2)</sup>, expresses the components within a particular system as C++ objects, each encapsulating data types and behavior unique to a particular device. Chatoyant takes advantage of the different simulation domains within Ptolemy (i.e. Dynamic Data Flow, or DDF, and Discrete Event, or DE) to perform analysis of optical, mechanical, and electrical components at both the macro and micro level <sup>(1, 2)</sup>. This tool will be discussed in more detail in Chapter 2.

One potential problem that arises from the existence of the simulation and system analysis tools previously mentioned, with the exception of Chatoyant, is the inability to handle a particular physical domain, albeit optical, mechanical, analog, digital, etc. Another potential problem is that there is no direct connection to another simulator that performs a different analysis that would bridge this gap in a complete system simulation. In such a case, a co-simulation, or real-time link between two or more simulators, becomes a solution. A design is typically partitioned into the pieces that will simulate in the appropriate simulator. Then an interface is defined between these simulators created based on the signals that will connect from one domain to another.

A simple example for such a need for co-simulation is in a digital and analog system design. If the digital portion of the design was created using VHDL or Verilog, and the analog sub-system was specified in the form of a SPICE netlist, a standard HDL simulator could only execute the VHDL description and only a SPICE simulator could simulate the netlist. Therefore, to perform a complete simulation, concurrently, a co-simulation interface must be used between the HDL and SPICE simulator. Some factors to consider in this case is first, how the two simulators will remain synchronized throughout the simulation time and second, how information is translated between the two physical domains <sup>(3)</sup>. These considerations are discussed in detail in Chapter 3. The concept of co-simulation and the potential need for it brings us to the purpose of this research. The following section will detail techniques, results, and limitation of the work accomplished. It constitutes the statement of the purpose for this thesis

## **1.1 STATEMENT OF PURPOSE**

The purpose of this research is to examine and create an efficient co-simulation interface between Chatoyant and ModelSim. As mentioned in the previous section, Chatoyant is a simulation environment for performing MOEM system level design exploration and simulation. ModelSim is a commercially available mixed-language HDL simulator. This research addresses the lack of HDL simulation support found in Chatoyant for digital systems by bridging Chatoyant to ModelSim for a real-time simulation interface.

#### **1.2 STATEMENT OF WORK PERFORMED**

To implement the co-simulation interface needed to address Chatoyant's lack of HDL simulation support, many approaches were researched and examined. Among the different techniques considered, the realm of Parallel Discrete Event Simulation <sup>(12)</sup> was studied in depth. Since both simulators were discrete event by nature, the issue of time synchronization was readily solved by many techniques found in the domain of PDES. This thesis provides the details of the theory used to implement the interface It also discusses the trade-offs between two common synchronization algorithms used in PDES. The remainder of the thesis focuses on the

background, theory, implementation, and testing of the co-simulation environment. The following section describes what each chapter discusses in more detail.

#### **1.3 LIMITATIONS OF WORKED PERFORMED**

The co-simulation interface presented in the previous section is based entirely on discrete event (DE) simulation. This process, though one of the more detailed simulation techniques for time-based simulation, also has one of the highest overheads in terms of scheduling processes, when compared to cycle-based or instruction level simulation <sup>(7)</sup>. Also, since both of the simulators used in the co-simulation simulate using discrete event simulation, the interface between them must transfer individual events. As seen in Chapter 5 with the test systems, this works well for sparsely distributed events. However, for systems that have a clock or periodic signal that cross the interface, there is a large performance penalty due to a high volume of intersimulator event traffic. The future work section of Chapter 6 describes potential solutions to this problem and possible methods of modifying this particular co-simulation interface to obtain reduced inter-simulator event traffic and lower synchronization overhead.

### **1.4 CHAPTER DESCRIPTIONS**

Chapter 2 covers the background on the technology used in the co-simulation interface described by this thesis. This includes a look into ModelSim, the commercial mixed language digital simulator, Ptolemy, a multi-domain simulation framework from the University of California at Berkeley, and Chatoyant, a complete simulation environment for performing MOEMS system simulation, built on top of Ptolemy. This provides the foundation of the toolsets used in the cosimulation system described in Chapter 4.

Chapter 3 provides a look into the different components needed for the co-simulation environment. Topics covered by this chapter include what simulation techniques are applicable to the co-simulation interface's design, described in this thesis, as well as a more detailed look into parallel discrete event simulation concepts. The chapter concludes with a discussion on how we measure the performance of the co-simulation interface.

Chapter 4 describes the details behind the architecture of the co-simulation environment between ModelSim and Chatoyant. This includes a detailed look into the algorithms and setup of both simulators for the two types of synchronization that we describe in Chapter 3. Finally, there is a discussion about the automated system generator that creates all of the necessary files needed to implement the co-simulation environment for a particular system.

Chapter 5 provides the descriptions and results of a series of test systems. These systems provide insight into how the co-simulation environment operates from simple to complex systems and real-world designs. Runtime results such as the number of messages, cycles per second, and system resource utilization are examined for all of these systems, utilizing two different synchronization algorithms. This chapter concludes with a cross comparison of all of the systems and a general conclusion as to which synchronization approach is the overall best.

Chapter 6 summarizes and concludes this thesis, reiterating the general concepts and goals of the research performed. It reviews the systems used to test the interface and provide final remarks about the results collected. Finally we look into what improvements can be made to

7

the co-simulation interface and what is required to make the co-simulation interface a more complete and efficient tool.

A set of appendices contain a list of key definitions used throughout this thesis along with the complete set of runtime measurements that we use in Chapter 5.

### 2.0 BACKGROUND

The co-simulation interface between Chatoyant and ModelSim utilizes three tools. ModelSim is a commercial product, from Model Technology Incorporated, a subsidiary of Mentor Graphics. We discuss, in more detail, ModelSim in Section 2.1. Chatoyant, a tool for performing mixed signal multi domain system, or MSMD <sup>(1)</sup>, was developed at the University of Pittsburgh. Chatoyant was developed to support the modeling and simulation of optical, mechanical, and electrical components found MOEM systems. Chatoyant utilizes the Ptolemy heterogeneous simulation framework for the actual simulation process <sup>(1, 2)</sup>.

Ptolemy utilizes an object-oriented programming, or OOP, paradigm to model user designs and components <sup>(7)</sup>. After we discuss ModelSim, we first examine Ptolemy to provide a proper background for Chatoyant. Second, we examine Chatoyant and its contribution in the realm of system-level simulation. We then conclude with a brief look into the need for a co-simulation interface between Chatoyant (ultimately Ptolemy) and ModelSim.

### 2.1 MODELSIM

$ModelSim_{\mathbb{R}}$  works on a single kernel concept which means that all design components, independent of their source language, are compiled into one primary executable object. This

executable object provides dynamic links to all compiled design objects. After all components have been compiled by the ModelSim compiler, the top level master design file is loaded, which in turn engages an elaboration procedure. This process links in all external components and loads them into the ModelSim memory space. Coincidentally, at this time all external C applications are linked as well from any foreign language interface (FLI) or programming language interface (PLI) callouts. Likewise, any delay annotation files such as SDF (Standard Delay Format) for back-annotated simulation, are linked and applied. At this point ModelSim begins preparation for simulation.

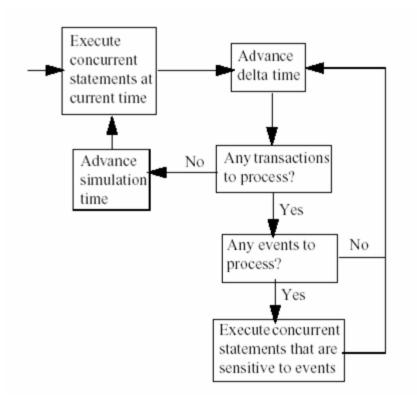

ModelSim is considered a discrete event simulator <sup>(30)</sup>, which means that all activity within components and between them is treated as individual events with timestamps. In the ModelSim environment, the user can force events on any visible net and then tell the simulator to advance to a stop point. Since ModelSim is a mixed language simulator, it supports of both Verilog and VHDL. The implication of this feature requires ModelSim to simulate Verilog designs differently than VHDL. In Figure 1 we illustrate ModelSim's method of performing simulation for any VHDL design.

Figure 1 Reproduction of ModelSim's VHDL simulation flow using a discrete event methodology <sup>(30)</sup>

This diagram, reproduced from the ModelSim User's Guide, <sup>(30)</sup>, shows the flow of every VHDL simulation. First, every concurrent statement at the current time is executed. Next, a delta cycle counter is incremented and any new event transactions are detected. If there are any transactions to be processed, then the simulator checks to see if there any events to be executed. If there are events that need to be executed, they are now processed and the delta cycle is incremented again. If there are no transactions, then the simulator determines that it is safe to advance the simulation clock. This process repeats until the user determined stop time or there is an infinite zero-delay loop detected. The infinite loop problem is the next topic for investigation.

An issue with this flow, as well as many discrete event simulators, is that of zero-delay feedbacks. These are typically defined by user logic that contains a combinatorial feedback

without any type of storage. This design issue creates a problem in discrete event simulators since events are constantly scheduled for the same time on the same set of nets, with the possibility of looping in this cycle forever <sup>(9, 30)</sup>. ModelSim deals with this issue by using deltacycles <sup>(30)</sup>. This feature, as seen on the top of Figure 1, is used to determine if stability is attainable, by cycling through a series of delta iterations until a stable value is determined in a feedback loop. If the loop iterates a preset maximum number of times, the simulator stops and reports a maximum loop iteration error <sup>(30)</sup>.

Verilog simulation, in ModelSim, extends the VHDL simulation flow described above. However, the Verilog Language Reference Manual, or LRM, from the Verilog 1364 standard, places constraints on how simultaneous events are processed <sup>(30)</sup>. Verilog is defined by the 1364 LRM such that the simulator cannot control the order in which simultaneous events are handled <sup>(38)</sup>. Since some designs require that events be processed in a particular order, the expected simulation results will vary from the actual results seen by the user <sup>(30)</sup>. Verilog requires that ModelSim and every other Verilog capable simulator maintain a total of seven event queues. These queues are processed in a particular order, also defined by the Verilog standard. Listed below are the event queues, in order of how they are processed during a simulation, and brief description of what each queue holds, as defined by the Verilog LRM.

- Active events These are the current events being processed and are in an arbitrary order.

- *Inactive event* These events are events that are waiting for all active events to be processed.

- Non blocking update events These events are similar to concurrent statements in VHDL, and are processed after all inactive events have be processed.

- Monitor events These events are events that are left over from the active, inactive, and non-blocking events executions.

- *Future events* These are events scheduled to occur in the simulation future time, and are divided into:

- o Future inactive events

- Future non-blocking events

Zero delay oscillations, by the Verilog standard, are handled in the active event portion of the simulation <sup>(30, 38)</sup>. According to the Verilog 1364 standard, all events are simulated only from the active event queue, and all other queues are used to sort event types and priorities <sup>(38)</sup>. For more on this topic refer to the ModelSim User's Manual <sup>(30)</sup> and the Verilog 1364 LRM Standard <sup>(38)</sup>.

One powerful feature ModelSim provides is the ability to support executing C based object files embedded within VHDL and Verilog designs. This is possible through the Foreign Language Interface, or FLI, used with VHDL or the Programming Language Interface, or PLI, used with Verilog. We will focus on the fundamentals of the FLI since it is used in the implementation of the Chatoyant/ModelSim co-simulation interface.

The FLI, as defined in the ModelSim FLI Reference Manual <sup>(31)</sup>, provides a set of functions that will allow a user to have access to information within the ModelSim environment. These functions will allow the user to traverse a design's hierarchy, obtain and set values of HDL objects such as arrays and signals, obtain information about the ModelSim runtime environment, and within a set of defined limits, control the simulation <sup>(31)</sup>. The FLI code, written in C, can contain operating system dependent functions such as calls to pipes and sockets or shared memory <sup>(31)</sup>. Each FLI program is compiled into a shared object file (.so in UNIX/Linux)

or dynamically linked library (.dll in Windows). These programs are then referenced in part of the user's VHDL code, specifically within the architecture of a design unit, with the object file's name and name of the initialization method to call when the simulator begins loading the object file.

The FLI defines two types of methods above the standard functions and procedures found in C. The first of these new types of method is a callback, which defines a function that is registered in the simulator and activated when some criteria, such as simulator restart, are met in the ModelSim environment. For example, there is a callback function that the user can define if the simulation is closing. If the user closes ModelSim, this callback will be activated and executed before the simulator is terminated <sup>(31)</sup>. The second type of function defined by the FLI is a *process* method. This function type is the same as a VHDL process block <sup>(27)</sup>, except it is implemented as a C function <sup>(31)</sup>. The features defined in the FLI reference manual <sup>(31)</sup> are used in the implementation of the Chatoyant/ModelSim interface. The use of the FLI are discussed in more detail in Chapter 4.

The last topic to discuss about ModelSim is the user interface. ModelSim can operate in both console mode and graphical mode. Both are based on a TCL (Tool Command Language) user interface and the ModelSim GUI makes use of the Tk extension package  $^{(30)}$ . In terms of user features, ModelSim provides many graphical tools for performing code verification and analysis. The user can select and log all signal and variable activity and view it in a waveform or tabular form. Code can also be debugged in a step-wise fashion similar to a standard software debugger. This is most useful for functional and behavioral simulation. Code performance can be measured using a mechanism based on the GNU code profiler, *gprof* <sup>(30)</sup>, which reports to the user the quantity of time spent in particular segments of the user's code. This is a useful tool for

measuring performance in the Chatoyant/ModelSim co-simulation interface. Other tools, such as a coverage measurement feature for performing different types of coverage analysis as well as a waveform comparison feature for measuring mismatches between two simulation runs, exist in ModelSim.

To provide a view as to the look and feel of ModelSim, Figure 2 shows an example snapshot from a ModelSim simulation, courtesy of Mentor Graphics. The design comes from one of the tutorials ModelSim provides as a teaching tool. In this particular example, we show a simple counter running in the ModelSim simulator. We ran this simulation and provided some of the GUI windows found within ModelSim. The upper left window in the screen shows the main ModelSim command console. The upper right window shows the HDL code editor and debug window. The window in the lower right corner displays the dataflow view for the design component selected. The center window shows the current state of all processes found in the current design unit that is selected. The lower right corner shows the waveform view for the simulation.

| ModelSim SE 5.8c            |                                                                                                                |                                                         | 🖸 source - cou   | inter.vhd                                                                                                |

|-----------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|

| File Edit View Compile Simu | late Tools Window Help                                                                                         |                                                         | File Edit View   | Tools Window                                                                                             |

| 🔓 🖻 🛍 🖉 🖉 🖉                 | 🛔 🚹 📑 100 ns 🕏 🖹                                                                                               | 1 II II (7) (7)                                         | 🕸 🚘 🖬 🖨          | 🐰 🛍 🛍 ሷ 🚧 🄆 👯   🔠 🛛 100 ns 式 💷 💷 💷 🕼   🎝 🗘 🖸                                                             |

| Workspace                   |                                                                                                                |                                                         | 🔶 In #           | sim:/counter:C:/FPGAdv62LSPS/Modeltech/examples/projects/vhdl/counter.vhd                                |

| ▼ Instance                  | Design unit Design unit I                                                                                      | VSIM 5> restart -f                                      |                  | secture only of counter is                                                                               |

| counter                     | counter(only) Architecture                                                                                     | VSIM 6> log -r *                                        | 11               | constant tpd_reset_to_count : time := 10 ns;                                                             |

| standard                    | standard Package                                                                                               | VSIM 7> do C:/FPGAdv62LSPS/Modeltech/ex                 | 12               | constant tpd_clk_to_count : time := 5 ns;                                                                |

|                             | and a second | do                                                      | 13               | function increment (val : bit vector) return bit vector                                                  |

|                             |                                                                                                                | # Reset OK. COUNT is 00000000.                          | 15               | is                                                                                                       |

|                             |                                                                                                                | # Test passed. COUNT is 01100100.<br>VSIM 8> add wave * | 16               | normalize the indexing                                                                                   |

|                             |                                                                                                                | view source                                             | 17               | alias input : bit_vector(val'length downto 1) is val;                                                    |

|                             |                                                                                                                | # .source                                               | 18               | <pre>variable result : bit_vector(input'range) := input;</pre>                                           |

|                             |                                                                                                                | view dataflow<br>#_dataflow                             | 19               | <pre>variable carry : bit := '1';<br/>begin</pre>                                                        |

|                             |                                                                                                                | view process                                            | 21               | for i in input'low to input'high loop                                                                    |

|                             |                                                                                                                | # .process<br>view structure                            | 22               | result(i) := input(i) xor carry;                                                                         |

|                             |                                                                                                                | # .structure                                            | 23               | carry := input(i) and carry;                                                                             |

|                             |                                                                                                                | destroy .structure<br>view variables                    | 24               | <pre>exit when carry = '0';<br/>end loop;</pre>                                                          |

|                             |                                                                                                                | # .variables                                            | 25               | end loop;<br>return result;                                                                              |

|                             |                                                                                                                | destroy variables<br>view memory                        | 27               | end increment;                                                                                           |

|                             |                                                                                                                | # .memory                                               | 28 begin         |                                                                                                          |

| 1                           |                                                                                                                | destroy memory                                          | 29               |                                                                                                          |

|                             |                                                                                                                | VSIM 18>                                                | 30               | ctr:<br>process(clk, reset)                                                                              |

| _ibrary_sim_Files           |                                                                                                                |                                                         | 32               | begin                                                                                                    |

| ow: 10,100 ns Delta: 1      | sim:/counter                                                                                                   |                                                         | 33               | if (reset = '1') then                                                                                    |

| dataflow                    |                                                                                                                |                                                         | 34               | if reset'event then                                                                                      |

| le Edit View Navigate Tra   | ar Tasla Utadam                                                                                                | process                                                 |                  | <pre>count &lt;= (others =&gt; '0') after tpd_reset_to_com<br/>end if;</pre>                             |

|                             |                                                                                                                | File Edit View Window                                   |                  | elsif clk'event and (clk = '1') then                                                                     |

| 😂   📐 🗗   👗 🖻               | 🛍 🖸 🗋 🖊   Je 🌜                                                                                                 | 🦕 🔆 ➔ 🚽 🗸 (Wab) dr                                      | ·                | count <= increment(count) after tpd clk to count;                                                        |

| H+E 20 20 00 0              | Ð, Q, 🍳   🗗 📠                                                                                                  |                                                         |                  | end if;                                                                                                  |

|                             |                                                                                                                |                                                         |                  | end process;                                                                                             |

|                             | - <b>L</b>                                                                                                     |                                                         | -                | ly;                                                                                                      |

|                             | ctr                                                                                                            |                                                         |                  |                                                                                                          |

|                             |                                                                                                                | sim:/counter                                            |                  | tandard.vhd Lin: 10 Col: 0 Read                                                                          |

| <u></u>                     |                                                                                                                | L.                                                      |                  |                                                                                                          |

| 🔍 🔍 💷                       |                                                                                                                | wave - default                                          |                  |                                                                                                          |

|                             | S                                                                                                              | File Edit View Insert For                               | nat Tools Window |                                                                                                          |

|                             | <u>ب</u>                                                                                                       | <b></b> & <b>b (b</b> )                                 | M 🔉 🕅 🗠 🗄        |                                                                                                          |

| res                         | set ⊑ ∣                                                                                                        | / /counter/count                                        | 00000010         | ασοσσοσο χαράο, γρασο, χαράο, χροσο, χρούο, χροσο, γραφο, χροσο, χροφο, χροσο, χροάο, χροσο, χροσο, χροσ |

|                             | set In os                                                                                                      | /counter/clk                                            | 1                |                                                                                                          |

|                             | 8                                                                                                              | 🗾 🗾 /counter/reset                                      | 0                | والملاد الملاد الملاد الملاد الملاد ا ملاد الد                                                           |

|                             |                                                                                                                |                                                         |                  |                                                                                                          |

|                             |                                                                                                                |                                                         |                  |                                                                                                          |

|                             | <u></u>                                                                                                        |                                                         |                  |                                                                                                          |

|                             | 0                                                                                                              |                                                         |                  |                                                                                                          |

|                             | <u> </u>                                                                                                       | Now                                                     | 10100 ns         | 1 200 400 600 900 1 us 1200 1400                                                                         |

|                             | ŏ                                                                                                              | Cursor 1                                                | 351 ns           | 200 400 800 800 10s 1200 1400                                                                            |

|                             |                                                                                                                |                                                         |                  |                                                                                                          |

| Extended mode enabled       | Keep 0                                                                                                         | Ø ns to 1442 ns                                         |                  |                                                                                                          |

|                             | , , , , ,                                                                                                      | 0 IIS 10 1442 IIS                                       |                  |                                                                                                          |

Figure 2 A snapshot of the ModelSim graphical environment from a test design simulation <sup>(44)</sup>

We now conclude our discussion about ModelSim and turn the discussion to the other tools used in the Chatoyant/ModelSim co-simulation interface. This will include a discussion about Ptolemy and Chatoyant.

## 2.2 PTOLEMY

Our discussion continues about the tools used in the Chatoyant/ModelSim co-simulation interface with an examination of Ptolemy <sup>(7)</sup>. Ptolemy, from the University of California at Berkeley, is the simulation framework that Chatoyant uses, and therefore we must examine how Ptolemy works and what information it provides. Ptolemy uses the object oriented programming (OOP) paradigm and C++ to define classes that describe different parts of a system. A system in this case is what the user of Ptolemy wishes to model and simulate. Within Ptolemy, there are a series of predefined classes, the most general of which is the *domain* <sup>(7)</sup>.

The domain, for the scope of this research, defines the computation model used to simulate a system. There are numerous domains available in Ptolemy. For example, there is the discrete event domain (used in the Chatoyant/ModelSim co-simulation interface), which is used for digital hardware and network simulations. Another domain is the dynamic data flow domain (found in some Chatoyant models), and a subset domain known as the synchronous data flow domain, both of which are targeted for signal processing applications <sup>(7, 35)</sup>.

Every system, regardless of the domain it simulates in, is comprised of a set of basic units called blocks <sup>(7)</sup>. These blocks, contain user defined code that performs some action, in a method called  $go()^{(7)}$ . The block contains other methods such as *startup()*, which defines what the block must do when a simulation begins, and *wrapup()*, which defines what the block must do when a simulation completes <sup>(7)</sup>.

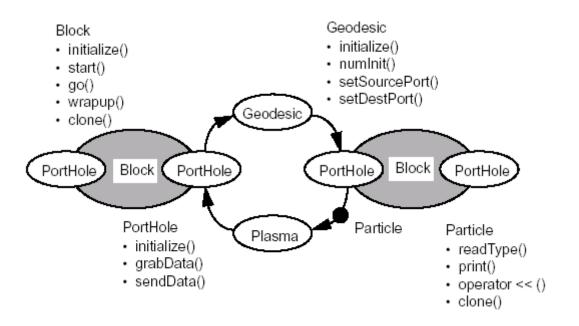

Typically, a block's go() method defines an action based on input stimulus from a Porthole <sup>(7)</sup>. Systems in Ptolemy are created by a series of blocks which connected to another by means of the portholes. Portholes are defined as standard interface by which blocks communicate to one another <sup>(7)</sup>. A domain will define the mechanism for transporting information from porthole to porthole through a scheduler. The data sent through the portholes is defined as a stream of particles <sup>(7)</sup>. Particles also adhere to the OOP style found in Ptolemy and can be primitive data types such as floating point numbers or integers or more complex objects, as seen in the case of Chatoyant. Two other important classes that assist in the connection and transfer of particles between portholes is the *Geodesic* class which establishes the connection between two portholes and the *Plasma* class which acts a garbage collector when a particle has been consumed by the destination porthole <sup>(7)</sup>. In Figure 3, we show a diagram of the flow between two blocks, with portholes, and particles being transported between them.

Figure 3 How blocks connect through portholes and how particles are transferred between them in Ptolemy  $_{(7)}$

As seen in Figure 3, each block contains a series of methods that the user must define. These methods perform a specific operation, defined in more detail in <sup>(9)</sup>. Any data that requires transmission to other blocks is done so through the porthole object. In the case of sending, the block will call the sendData() method in the porthole instance. Once again, this data can be in the form of primitive floating point numbers or integers or a complex user-defined data type. The porthole will then pass a particle, which acts as a generic wrapper for the data being transmitted, through an instance of the Geodesic object. The Geodesic instance will contain the destination pointer for the particle. The scheduler of the domain these blocks reside in will call the grabData() method of the destination block. The destination block will then process the data and the particle will be collected by the Plasma instance between the two blocks. This will happen for every connection between every block in a system. <sup>(7, 9)</sup>

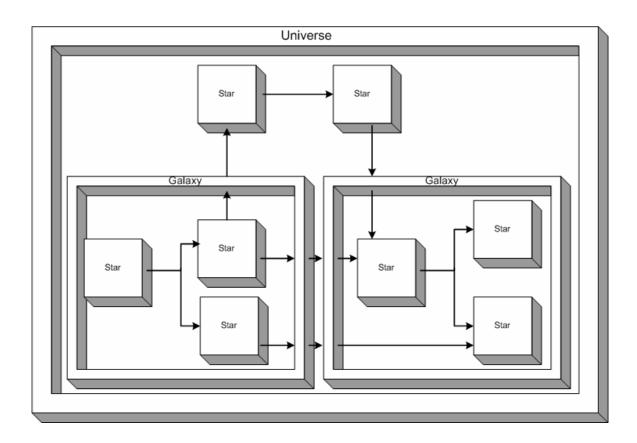

Ptolemy also provides support for a hierarchy when building systems. Every block now becomes defined as a star, which is the atomic unit of component description. The next level of abstraction available in Ptolemy is a collection of Stars called a Galaxy. A Galaxy, models system behavior (through a collection of Stars) and can have portholes the same as Stars. A Galaxy and all of the stars within it, are all confined to a specific domain of simulation (e.g. discrete event or dynamic data flow). All Galaxies or groups of Stars are ultimately contained in a Universe which has similar properties as a Galaxy. A Universe also has the ability of invoking a scheduler and executing a simulation <sup>(7)</sup>.

Figure 4 Illustration of a Ptolemy Universe with Stars and Galaxies, derived from <sup>(7)</sup>

The diagram in Figure 4 shows the how a system can be described using the hierarchical constructs in Ptolemy. First, the stars represent the atomic level block. Each line with an arrowhead represents the connection between the ports of the stars. Next, the borders with the "Galaxy" label represent the description of a particular galaxy. Signals traverse the galaxy border using the same system as seen in the stars using portholes. Finally, the universe border defines the entire system as a whole, acting as a container for all stars and galaxies. The universe will activate the scheduler referenced by all of the stars and galaxies for the domain these items reside in. <sup>(7)</sup>

As we discuss the methodology of how a system is modeled in Ptolemy, one key item found in a domain and used by a universe, galaxy, and star is the scheduler. The scheduler is responsible for managing the flow of data throughout a simulation as well as the execution of the simulation. There are different schedulers for different domains in Ptolemy <sup>(7)</sup>. For example, there is a scheduler that maintains the order and flow of data particles in the dynamic data flow (DDF) domain. This scheduling methodology is used in signal processing simulations <sup>(9)</sup>. The discrete event (DE) domain requires the scheduler to manage time instead of the flow of data. The DE scheduler maintains an event queue and the global time of the universe during a simulation <sup>(9)</sup>. The DE scheduler must resolve zero-delay oscillations (the same issue handled by ModelSim). Instead of detecting this at runtime, Ptolemy detects a zero-delay loop at compile time, as a universe is loaded, before simulation. More details concerning the different schedulers for the different domains is available in <sup>(9)</sup>.

Ptolemy also provides a feature for allowing simulation between multiple domains. This heterogeneous simulation is limited to a particular combination of domains. First, the main universe of a system is defined, defining the scheduler needed for its operation. For example, a

DE based universe will instantiate the DE scheduler. Secondly, the user can then define a subgalaxy within the universe that calls upon a different a scheduler, such as the synchronous data flow (SDF) domain and scheduler.

The communication system between both the domains and schedulers is resolved by using a Wormhole object in Ptolemy. A wormhole makes use the EventHorizon interface to resolve the difference in scheduling requirements between the two schedulers as well as any encapsulation differences needed to transfer particles between the two domains. For a more detailed description of the Wormhole, EventHorizon, and domains that work together, see references <sup>(7, 9)</sup>. The importance of mentioning this capability in Ptolemy is relevant for discussing the different components found in Chatoyant. Chatoyant contains objects that utilize domains such as SDF due to their signal processing behavior while other components utilize the DE domain due to the necessity to simulate with a time reference.

The Wormhole, though a powerful mechanism in Ptolemy, is not directly applicable to the Chatoyant/ModelSim co-simulation interface. In order to make use of the Wormhole in the co-simulation interface, either an existing simulation domain, such as DE, must be modified or a new domain needs to be created. If an existing domain is modified, there must be a mechanism implemented to handle both the particle translation to and from ModelSim, as well a substantial modification to the scheduler for it to perform the synchronization. If a new domain is created, it must implement the necessary interfaces, such as the EventHorizon, as well as the scheduler object, in addition to the remainder of the interface to ModelSim. Though this solution could possibly provide a faster co-simulation runtime performance, certain issues such as integration into Ptolemy and ModelSim as well as making a new domain flexible to handle any system, outweighs the potential speedup. With a broad based knowledge of Ptolemy, Chatoyant builds upon the framework provided by Ptolemy to provide a true Mixed Signal Multi-Domain simulation tool. This includes generic stars for describing optical behavior, piece-wise linear circuit solvers, and other customizable components needed for a complete system simulation.

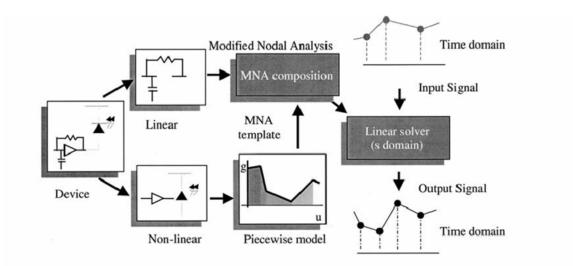

# 2.3 CHATOYANT: A MIXED SIGNAL, MULTI-DOMAIN MOEMS SIMULATION TOOL