## NANOELECTRONICS IN OXIDES AND SEMICONDUCTORS

by

# **Guanglei** Cheng

B.S. University of Science and Technology of China, 2003

M.S. University of Pittsburgh, 2005

Submitted to the Graduate Faculty of the Arts and Sciences in partial fulfillment of the requirements for the degree of Doctor of Philosophy

University of Pittsburgh

2011

### UNIVERSITY OF PITTSBURGH

### DEPARTMENT OF PHYSICS AND ASTRONOMY

This dissertation was presented

by

Guanglei Cheng

It was defended on

April 18, 2011

and approved by

Jeremy Levy, Professor, Physics and Astronomy, Arts and Sciences

Xiaolun Wu, Professor, Physics and Astronomy, Arts and Sciences

Hrvoje Petek, Professor, Physics and Astronomy, Arts and Sciences

Scott Mao, Professor, Mechanical Engineering and Materials Science, Arts and Sciences

Robert Griffiths, Professor of Physics, Carnegie Mellon University

Dissertation Advisor: Jeremy Levy, Professor, Physics and Astronomy, Arts and Sciences

Copyright © by Guanglei Cheng

2011

#### NANOELECTRONICS IN OXIDES AND SEMICONDUCTORS

Guanglei Cheng, PhD

University of Pittsburgh, 2011

The success of silicon industry lies on three major properties of silicon, an easily formed oxide layer to allow field effect operation, tunability of carrier density and high device scalability. All these features exist in oxides, together with some novel properties such as ferroelectricity, magnetic effects and metal-insulator transition. With the recent development in material growth method including molecular beam epitaxy (MBE), pulsed laser deposition (PLD) and reflection high energy electron diffraction (REED), atomically engineered oxide interfaces become available, thus opening the door to the novel oxide nanoelectronics. In this dissertation we create and study nanoelectronics in oxides, semiconductors and hybrid of these two. We used a conductive atomic force microscope tip to write single electron transistors in the 3-unit-cell-LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure and observed ferroelectric tunneling behaviors. We also fabricated ferroelectric field transistors directly on silicon using strained SrTiO<sub>3</sub> ferroelectric film and further confirmed the ferroelectric properties of this device. Meanwhile, we developed an ultrasensitive microwave capacitance sensor to study the electronic properties of selfassembled quantum dots and the switching mechanism of memristive devices. The integration of this sensor to a home made atomic force microscope provides an important tool to study the dielectric properties at nanoscale.

# TABLE OF CONTENTS

| PRI | EFAC | CE           | XIII                                      |  |  |  |

|-----|------|--------------|-------------------------------------------|--|--|--|

| 1.0 | INT  | INTRODUCTION |                                           |  |  |  |

|     | 1.1  | (            | QUANTUM DOTS1                             |  |  |  |

|     | 1.2  | N            | AICROWAVE TRANSMISSION LINE               |  |  |  |

|     |      | 1.2.1        | Transmission line                         |  |  |  |

|     |      | 1.2.2        | Microstrip transmission line              |  |  |  |

|     |      | 1.2.3        | Transmission line terminated with a load7 |  |  |  |

|     |      | 1.2.4        | Scattering parameters7                    |  |  |  |

|     | 1.3  | F            | FERROELECTRICITY                          |  |  |  |

|     |      | 1.3.1        | Origin of ferroelectricity9               |  |  |  |

|     |      | 1.3.2        | Applications10                            |  |  |  |

| 2.0 | EX   | PERIN        | IENTAL METHODS 12                         |  |  |  |

|     | 2.1  | N            | AICROWAVE CAPACITANCE SENSING 12          |  |  |  |

|     | 2.2  | Ι            | OCK-IN DETECTION14                        |  |  |  |

|     | 2.3  | A            | ATOMIC FORCE MICROSCOPY 17                |  |  |  |

|     |      | 2.3.1        | Tip-sample interaction forces    18       |  |  |  |

|     |      | 2.3.2        | Force sensors 19                          |  |  |  |

|     |      | 2.3.3        | AFM working principles 20                 |  |  |  |

|     | 2.4 | F     | PIEZORESPONSE FORCE MICROSCOPY 2                              | 21         |

|-----|-----|-------|---------------------------------------------------------------|------------|

|     |     | 2.4.1 | Piezoelectric effect 2                                        | 22         |

|     |     | 2.4.2 | Application2                                                  | 23         |

|     | 2.5 | S     | CANNING MICROWAVE MICROSCOPY2                                 | 24         |

| 3.0 | SK  | ЕТСНІ | ED OXIDE SINGLE ELECTRON TRANSISTOR 2                         | 25         |

|     | 3.1 | Ι     | AALO3/SRTIO3 HETEROSTRUCTURE 2                                | 25         |

|     |     | 3.1.1 | Polar catastrophe and interface reconstruction2               | 27         |

|     |     | 3.1.2 | LaAlO <sub>3</sub> /SrTiO <sub>3</sub> heterostructure growth | 30         |

|     | 3.2 | (     | CONDUCTIVE AFM LITHOGRAPHY 3                                  | 31         |

|     | 3.3 | S     | INGLE ELECTRON TRANSISTORS 3                                  | 33         |

|     | 3.4 | S     | KETCHSET DEVICE FABRICATION AND SIZE                          |            |

|     | CH  | ARAC  | TERIZATION                                                    | 36         |

|     |     | 3.4.1 | Device fabrication                                            | 36         |

|     |     | 3.4.2 | Device size characterization                                  | 39         |

|     | 3.5 | N     | IEASUREMENT 4                                                 | 10         |

|     | 3.6 | F     | RESULTS AND DISCUSSION 4                                      | 10         |

|     |     | 3.6.1 | Temperature dependence4                                       | 12         |

|     |     | 3.6.2 | Ferroelectric tunnel barriers 4                               | 14         |

|     |     | 3.6.3 | Side gating 4                                                 | <b>1</b> 7 |

|     |     | 3.6.4 | Back gating5                                                  | 50         |

|     | 3.7 | (     | CONCLUSION AND OUTLOOK 5                                      | 53         |

| 4.0 | FE  | RROEI | LECTRIC FFIELD EFFECT TRANSISTORS ON SILICON                  | 54         |

|     | 4.1 | Ι     | NTRODUCTION5                                                  | 55         |

|     | 4.2  | C     | CHAL  | LENGES     | S IN SILIC           | CON FE       | FET    |              |           | 56            |

|-----|------|-------|-------|------------|----------------------|--------------|--------|--------------|-----------|---------------|

|     | 4.3  | A     | A FER | ROELE      | CTRIC FI             | LM ON        | SILIC  | CON          |           | 57            |

|     | 4.4  | S     | SAMP  | LE GRO     | WTH                  | •••••        | •••••  | ••••••       |           | 59            |

|     | 4.5  | F     | FEFE  | Г DEVIC    | E FABRIO             | CATIO        | N      | ••••••       |           | 60            |

|     | 4.6  | N     | AEAS  | UREME      | NT                   | •••••        | •••••  | ••••••       |           | 61            |

|     |      | 4.6.1 | I-V   | curves     | ••••••               | •••••        | •••••  | ••••••       |           | 62            |

|     |      | 4.6.2 | PFN   | 1 measur   | ement                | •••••        | •••••  | ••••••       |           | 63            |

|     |      | 4.6.3 | Rete  | ention me  | asurement            | t            | •••••  | ••••••       |           | 65            |

|     |      | 4.6.4 | Ver   | tical tunn | eling                | •••••        | •••••  | ••••••       |           | 67            |

|     | 4.7  | S     | SUMN  | IARY AN    | ND FUTUE             | RE WO        | RK     | ••••••       |           | 69            |

| 5.0 | NA   | NOSCA | ALE   | CHARA      | CTERIZA              | ATION        | BY     | MICROWAVE    | CAPACITA  | NCE           |

| SEN | ISIN | G     | ••••• | •••••      | ••••••               | •••••        | •••••  | ••••••       |           | 70            |

|     | 5.1  | N     | AICR  | OSTRIP     | САРАСІТ              | <b>FANCE</b> | SENS   | OR           |           | 71            |

|     | 5.2  | 0     | CAPA  | CITANC     | E SENSIN             | IG OF S      | SELF-  | ASSEMBLED QU | ANTUM DOT | ſ <b>S 74</b> |

|     |      | 5.2.1 | Sam   | ple grow   | th                   | •••••        | •••••  | ••••••       |           | 75            |

|     |      | 5.2.2 | Exp   | eriment s  | etup                 | •••••        | •••••  | ••••••       |           | 76            |

|     |      | 5.2.3 | Low   | frequen    | ey measure           | ement        | •••••  | ••••••       |           | 77            |

|     |      | 5.2.4 | Mic   | rowave fr  | equency n            | neasure      | ment   | ••••••       |           | 78            |

|     |      | 5.2.5 | Sun   | mary and   | d future w           | ork          | •••••  | ••••••       |           | 80            |

|     | 5.3  | S     | SCAN  | NING CA    | PACITA               | NCE IN       | 1AGIN  | IG OF Q-2DEG |           |               |

|     | NA   | NOSTR | RUCT  | URES AT    | Γ LAALO <sub>3</sub> | 3/SRTI(      | D3 INT | ERFACE       |           | 80            |

| 6.0 | EL   | ECTRI | C     | CHARAC     | TERIZAT              | ΓΙΟΝ         | OF     | MEMRISTIVE   | DEVICES   | AT            |

| MIC | CRO  | WAVE  | FRE   | QUENCI     | ES                   | •••••        | •••••  | •••••        |           | 85            |

|     | 6.1      | THE FOURTH ELEMENT                         | . 86 |

|-----|----------|--------------------------------------------|------|

|     | 6.2      | MOTIVATION                                 | . 89 |

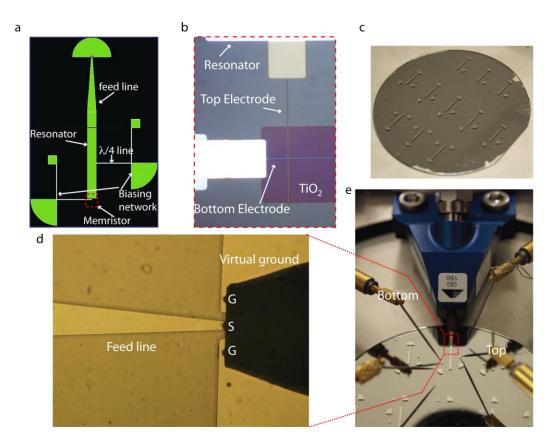

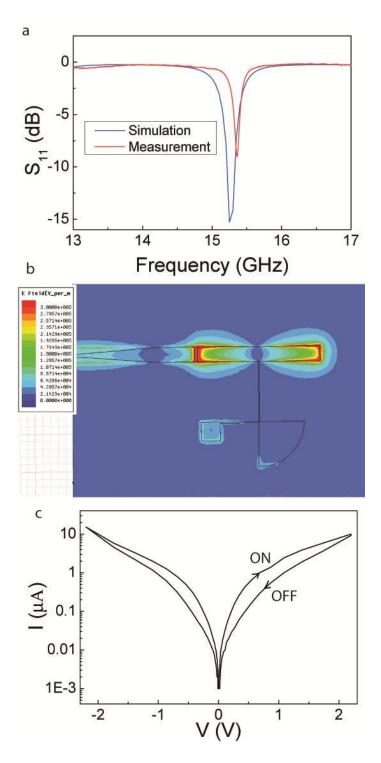

|     | 6.3      | RESONATOR DESIGN AND MEMRISTOR INTEGRATION | . 90 |

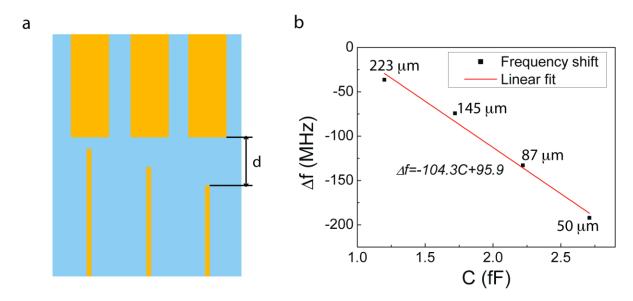

|     | 6.4      | RESONATOR FREQUENCY SENSITIVITY            | . 94 |

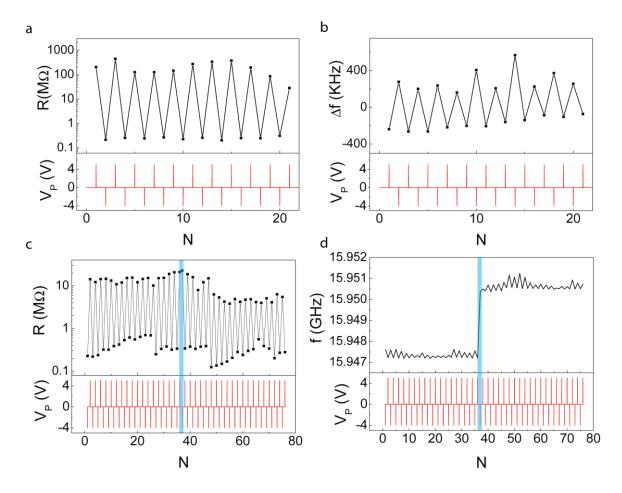

|     | 6.5      | EXPERIMENT RESULTS                         | . 95 |

|     | 6.6      | POSSIBLE MODELS                            | . 97 |

|     | 6.7      | SUMMARY AND FUTURE WORK                    | 100  |

| 7.0 | SUMMA    | ARY AND OUTLOOK                            | 101  |

| API | PENDIX A | L                                          | 103  |

| BIB | LIOGRA   | PHY                                        | 113  |

# LIST OF TABLES

| Table 3.1 Transport parameters of AlGaAs/GaAs and LaAlO <sub>3</sub> /SrTiO <sub>3</sub> 2DEG | 27 |

|-----------------------------------------------------------------------------------------------|----|

|                                                                                               |    |

| Table 3.2 Device sketching parameters.                                                        | 38 |

# LIST OF FIGURES

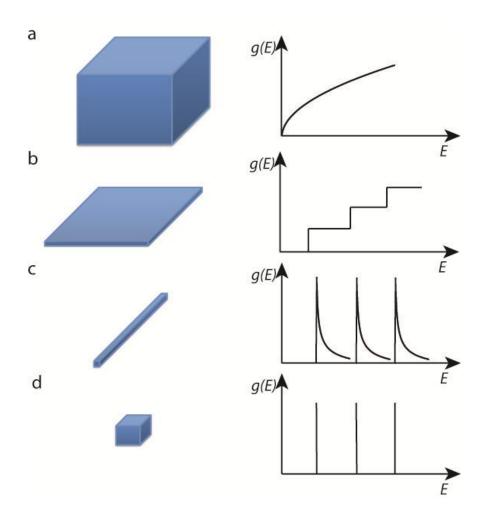

| Figure 1.1 Densities of states versus energy at different dimensions                                        | . 3 |

|-------------------------------------------------------------------------------------------------------------|-----|

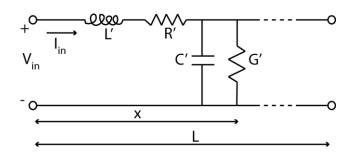

| Figure 1.2 Transmission line lumped model                                                                   | . 4 |

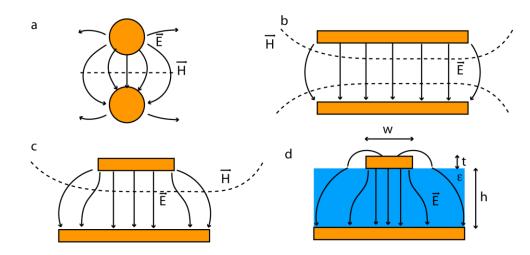

| Figure 1.3 Evolution of microstrip transmission line.                                                       | . 6 |

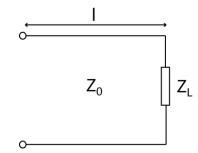

| Figure 1.4 Transmission line terminated with a load                                                         | . 7 |

| Figure 1.5 2-port network                                                                                   | . 7 |

| Figure 1.6 P-E loop                                                                                         | . 8 |

| Figure 2.1 Working principle for RCA's CED microwave capacitance sensing                                    | 13  |

| Figure 2.2 Schematic of a lock-in amplifier and measurement setup                                           | 15  |

| Figure 2.3 Forces between tip and sample                                                                    | 18  |

| Figure 2.4 Force sensors (a) Cantilever based. (b) Tuning fork based.                                       | 19  |

| Figure 2.5 AFM working principle                                                                            | 20  |

| Figure 2.6 Working principle of PFM.                                                                        | 22  |

| Figure 2.7 Topography and PFM image of BaTiO3                                                               | 23  |

| Figure 3.1 Polar catastrophe and interface reconstruction                                                   | 29  |

| Figure 3.2 Growth of LaAlO <sub>3</sub> layer on SrTiO <sub>3</sub> substrate                               | 31  |

| Figure 3.3 Conductive AFM lithography in 3 unit cell LaAlO <sub>3</sub> /SrTiO <sub>3</sub> heterostructure | 32  |

| Figure 3.4 Single electron transistor and constant interaction model                                        | 34  |

| Figure 3.5 Device A, B and C structures.                                                                    | 38  |

| Figure 3.6 SketchSET schematic and transport characteristics                                      |

|---------------------------------------------------------------------------------------------------|

| Figure 3.7 Temperature dependent differential conductance and capacitance of Device A.            |

| transition in the SrTiO <sub>3</sub>                                                              |

| Figure 3.8 Ferroelectric contribution to electron energy shifts in a SketchSET                    |

| Figure 3.9 Side gating for device A and B at T=25 K                                               |

| Figure 3.10 Illustration of energy levels for device B at different electrochemical potentials of |

| source and gate1 electrodes                                                                       |

| Figure 3.11 Differential conductance and capacitance dependence on the back gate voltage at       |

| <i>T</i> =16 K, Device C                                                                          |

| Figure 3.12 SketchSET capacitance model                                                           |

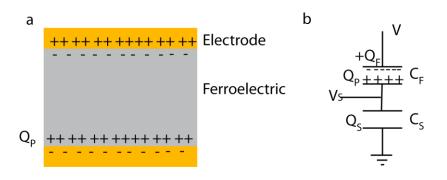

| Figure 4.1 (a) Metal-ferroelectric-metal capacitor structure. (b) equivalent circuit model        |

| involving ferroelectric polarization                                                              |

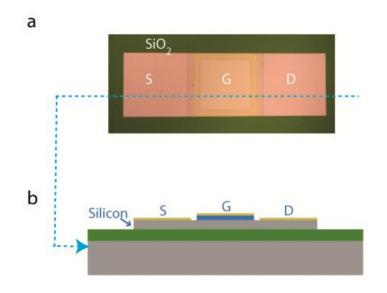

| Figure 4.2 FeFET device schematic                                                                 |

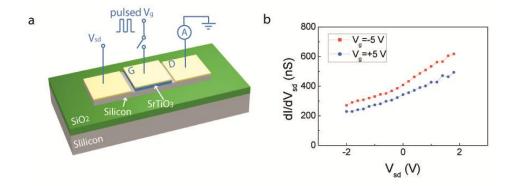

| Figure 4.3 Measurement setup and <i>I-V</i> curves                                                |

| Figure 4.4 Piezoresponse force microscopy study of the 5 ML SrTiO <sub>3</sub> film               |

| Figure 4.5 Device performance of FeFETs on p-type and n-type silicon                              |

| Figure 4.6 Tunneling behavior of the metal-SrTiO3-Si tunnel junction in device A                  |

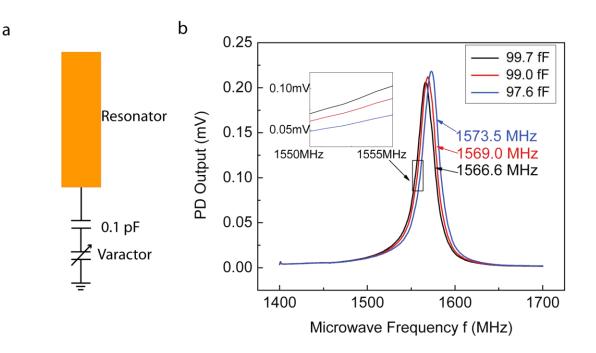

| Figure 5.1 Microwave capacitance measurement based on a microstrip resonator72                    |

| Figure 5.2 Frequency sensitivity measurement                                                      |

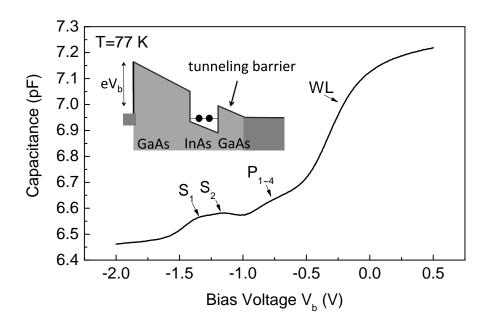

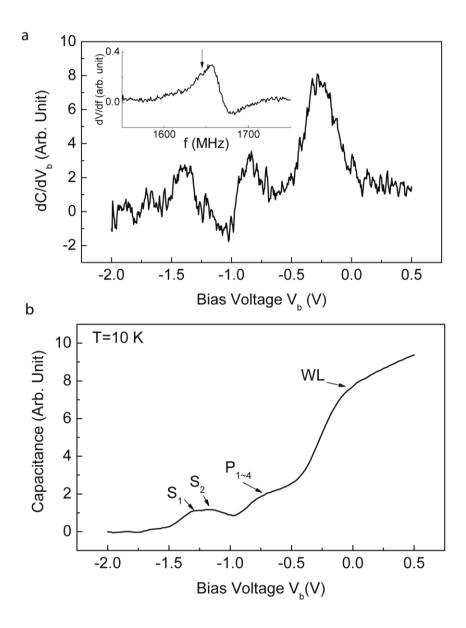

| Figure 5.3 Low frequency <i>C</i> - <i>V</i> curve                                                |

| Figure 5.4 Microwave C-V spectroscopy 79                                                          |

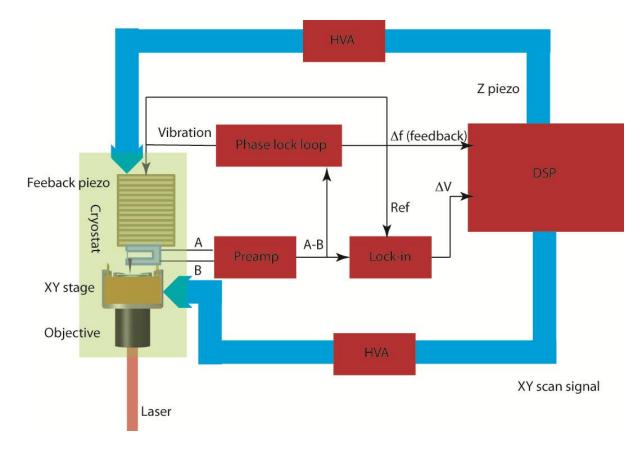

| Figure 5.5 A home-made Scanning microwave microscope setup                                        |

| Figure 5.6 Microwave Imaging                                                                      |

| Figure 5.7 Microwave imaging of q-2DEG nanowires at the LaAlO <sub>3</sub> /SrTiO <sub>3</sub> interface |

|----------------------------------------------------------------------------------------------------------|

| Figure 6.1 Symmetry in fundamental circuit elements indicates the existence of missing                   |

| memristors                                                                                               |

| Figure 6.2 Memristor model and mesoscopic picture                                                        |

| Figure 6.3 Resonator design and memristor integration                                                    |

| Figure 6.4 Resonator and memristor characteristics                                                       |

| Figure 6.5 Resonator calibration                                                                         |

| Figure 6.6 Memristor resistance and resonant frequency shift under ON/OFF cycles                         |

| Figure 6.7 Possible models                                                                               |

| Figure A.1 Photograph of the microscope                                                                  |

| Figure A.2 Approach motor                                                                                |

| Figure A.3 XY scanner                                                                                    |

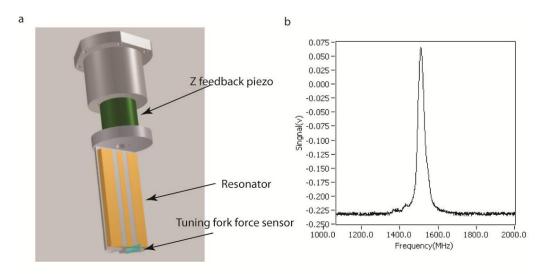

| Figure A.4 Feecback piezo assembly with the microstrip resonator                                         |

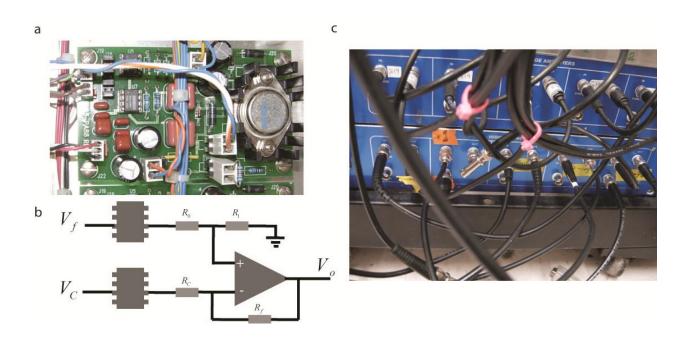

| Figure A.5 High voltage Amplifier                                                                        |

| Figure A.6 Working principle                                                                             |

| Figure A.7 GXSM main window111                                                                           |

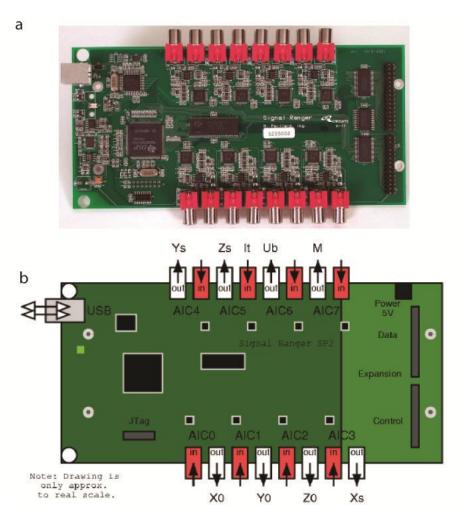

| Figure A.8 Signal ranger DSP board                                                                       |

#### PREFACE

I have enjoyed nearly every moment of my life here in Pittsburgh, not only because Pittsburgh is ranked as "the most livable city in US", but also most importantly the people I'm working with.

I gratefully thank my advisor Jeremy Levy. Without his support, guidance, patience, hand-by-hand help and academic intuition I would not have been able to accomplish this dissertation. It is a great fun working with current labmates Patric Irvin, Cheng Cen, Dongyue Yang, Yanjun Ma, Feng Bi, Vanita Srinivasa and Mengchen Huang. Thanks to the easy lab environment, we help each other and improve together. Also many thanks to formal members Hongzhou Ma, Peti Fodor and Daniela Bogorin, they help me a lot with their expertise and warm hearts.

I had great time with the talented guys at HP labs memristor device group. Special thanks to Gilberto Medeiros-Ribeiro, without him I would not have the opportunity for the HP labs experience and accomplish my project.

My Ph.D. committee is a great collection of distinguised professors, they guided me along the proper path using their professional suggestions and care.

Finally I want to thank my family, they have been always supportive and patient.

### **1.0 INTRODUCTION**

Compared to conventional semiconductor silicon or compounds of III-V elements in the periodic table, transition metal oxides exhibit a broad range of novel functionalities such as superconductivity, piezoelectricity and ferroelectricity, high dielectric permittivity, colossal magnetoresistance, ferromagnetism and metal-insulator transitions. These functionalities enable novel device integration of oxide and semiconductor, or the emerging of oxide electronics, an even more ambitious field. With Moore's law foreseeing the scaling limit of conventional electronics, even the silicon industry is trying to find an alternative material system. Motivated by these points, this dissertation studies nanoelectronic devices made of semiconductor, oxides and the hybrid of semiconductor and oxides.

In the following subsections, I will cover some basic physical concepts that are essential to this dissertation.

### 1.1 QUANTUM DOTS

A quantum dot (QD) is a semiconductor nanostructure in which the electrons are spatially confined in 3 dimensions(1, 2). In other words, the QD is a zero-dimensional system in terms of electron freedom. When then size of a QD is comparable to electron wavelength, the QD shows discrete energy levels similar to that of a hydrogen atom. It is some times referred to as an

"artificial atom". For an array of quantum dots, they can also from an artificial two-dimensional crystal.

Figure 1.1 shows the density of states (DOS) at systems with different dimensions based on basic quantum mechanical calculations. For a 3 dimensional system the density of states g(E) for a free electron is given by

$$g(E) = \frac{a^3}{2\pi^2} \left(\frac{2m^*}{\hbar}\right)^{3/2} \sqrt{E}$$

(1.1)

where  $m^*$  is the effective electron mass, *a* is the lattice constant of a cubic lattice and  $\hbar$  is the reduced Planck constant. And for 2 dimensional electron gas, the DOS is

$$g(E) = \frac{a^2 m^*}{\pi \hbar^2} \tag{1.2}$$

which is not dependent on the energy. For 1 dimensional system like quantum wires, the DOS is

$$g(E) = \frac{a}{\pi} \sqrt{\frac{2m^*}{h^2}} \frac{1}{\sqrt{E}}$$

(1.3)

For a zero dimensional system like a quantum dot, the energy spectrum is discrete

$$g(E) = \frac{2}{a^3}\delta(E - E_n) \tag{1.4}$$

Numerous methods are used to confine electrons in 3 dimensions. For example, (CdSe)ZnS core-shell quantum dots buries the CdSe core in a large band gap semiconductor ZnS. Lateral quantum dots confine electrons using depletion gates above 2DEG using lithography techniques. Self-assembled quantum dots (SAQD) are formed by island nucleation for a material grown on a lattice-mismatched substrate by molecular beam epitaxy (MBE). In this dissertation, we study the SAQDs by looking at the capacitance spectroscopy, which reflects the spin information in the SAQDs for quantum information processing.

Figure 1.1 Densities of states versus energy at different dimensions. (a)Three dimensions, (b) two dimensions, (c) one dimension, (d) zero dimension.

### **1.2 MICROWAVE TRANSMISSION LINE**

In this dissertation, one important technique that is developed and advanced is microwave capacitance sensing. This capacitance sensor monitors the resonance frequency shifts of a microstrip resonator perturbed by a capacitor attached to it. Here I will briefly review the transmission line theory that forms the basis of this sensor.

### 1.2.1 Transmission line

Figure 1.2 Transmission line lumped model

A transmission line is a medium that guides electromagnetic waves. A simple onedimensional transmission line can be modeled as a composition of distributed lumped elements, as shown in Fig. 1.2. In this model, the transmission line is divided into infinite sections that have length  $\Delta x$  and total length *L*. Each section has *L'*, *R'*, *C'* and *G'* representing inductance per length, resistance per length, capacitance per length and conductance per length respectively. From basic circuit theory, we have

$$\frac{\partial i}{\partial x} = -\nu G' - \frac{\partial v}{\partial t} C' \tag{1.1}$$

$$\frac{\partial v}{\partial x} = -iR' - \frac{\partial i_{in}}{\partial t}L' \tag{1.2}$$

where i and v are current and voltage in each section. These two equations are often referred as *Telegrapher's Equations*. Differentiating the equations with t and x we get

$$\frac{\partial^2 v}{\partial x^2} = -\frac{R'\partial i}{\partial x} - \frac{L'\partial^2 i}{\partial x\partial t}$$

(1.3)

$$\frac{\partial^2 v}{\partial x \,\partial t} = -\frac{R' \partial i}{\partial t} - \frac{L' \partial^2 i}{\partial t^2} \tag{1.4}$$

$$\frac{\partial^2 i}{\partial x \,\partial t} = -\frac{G' \partial v}{\partial t} - \frac{C' \partial^2 v}{\partial t^2} \tag{1.5}$$

$$\frac{\partial^2 i}{\partial x^2} = -\frac{G'\partial v}{\partial t} - \frac{C'\partial^2 v}{\partial t \partial x}$$

(1.6)

Substituting (1.1) and (1.2) to (1.3), (1.4), (1.5) and (1.6) we have

$$\frac{\partial^2 v}{\partial x^2} = v(R'G') + \frac{\partial v}{\partial t}(R'C' + L'G') + \frac{\partial^2 v}{\partial t^2}(L'C')$$

(1.7)

$$\frac{\partial^2 i}{\partial x^2} = i(G'R') + \frac{\partial i}{\partial t}(L'G' + C'R') + \frac{\partial^2 i}{\partial t^2}(L'C')$$

(1.8)

The above second-order differential equations have universal solutions with  $v(x,t) = v'(x)e^{j\omega t}$ ,  $i(x,t) = i'(x)e^{j\omega t}$ . By substituting these forms to the above equations we get,

$$\frac{\partial^2 v}{\partial^2 x} = v(x,t)[(R'+j\omega L')(G+j\omega C')]$$

(1.9)

The solution to (1.9) has form

$$v(x,t) = Ae^{-\gamma x}e^{-j\omega t} + Be^{\gamma x}e^{-j\omega t}$$

(1.10)

where the *propagation constant*  $\gamma = \sqrt{(R' + j\omega L')(G' + j\omega C')}$ . It is also written in a complex form  $\gamma = \alpha + j\beta$  with  $\alpha$  the *attenuation constant* and  $\beta$  the *phase constant*. This solution essentially contains two waves propagating in two opposite directions (+*x*/-*x*). Similarly we have

$$i(x,t) = \frac{-\gamma A e^{-\gamma x} e^{-j\omega t} + \gamma B e^{\gamma x} e^{-j\omega t}}{(R' + j\omega L')}$$

(1.11)

And the *characteristic impedance*  $Z_0$  is defined as the ratio of the voltage and current of a single wave propagating in one direction

$$Z_0 = \frac{v^+(x,t)}{i^+(x,t)} = \sqrt{\frac{R'+j\omega L'}{G'+j\omega C'}}$$

(1.12)

For a lossless transmission line R'=G'=0, so that  $Z_0 = \sqrt{L'/C'}$ .

### 1.2.2 Microstrip transmission line

The microstrip is a type of electric transmission line that consists of an upper conductor strip and a ground plane with a dielectric in between. Fig. 1.3 shows the evolution from coaxial transmission system. First the coaxial line in (a) is deformed to a rectangle shape (b), and then the top conductor is shrunk to a strip (c) while most of the fields are confined between two conductors. Finally the dielectric material with dielectric constant  $\varepsilon$  is introduced. Due to the inhomogeneity of dielectric medium (air versus dielectric), the effective dielectric constant  $\varepsilon_{eff}$  or effective microstrip width  $w_{eff}$  is often used to describe the characteristics of a microstrip. Analytical expression of characteristic impedance is hard to reach due to this inhomogeneity, an empirical expression from Wheeler(3) is often used.

$$Z_m = \frac{Z_0}{2\pi\sqrt{2(1+\epsilon_r)}} \ln\left(1 + \frac{4h}{w_{eff}} \left(\frac{14+\frac{8}{\epsilon_r}}{11}\frac{4h}{w_{eff}} + \sqrt{\left(\frac{14+\frac{8}{\epsilon_r}}{11}\frac{4h}{w_{eff}}\right)^2 + \pi^2 \frac{1+\frac{1}{\epsilon_r}}{2}}\right)$$

(1.13)

where  $Z_0$  is the characteristic impedance in air.

Figure 1.3 Evolution of microstrip transmission line. (Adapted from Ref. (4))

## 1.2.3 Transmission line terminated with a load

Figure 1.4 Transmission line terminated with a load

The transmission line is often terminated with a load, which perturbs the waves in the transmission line. Writing the solution to the telegrapher's equations with hyperbolic functions, the *generalized impedance*  $Z_{in}$  for a transmission with a load  $Z_L$  (as shown in Fig. 1.4) is

$$Z_{in} = Z_0 \left( \frac{Z_R \cosh \gamma l + Z_0 \sinh \gamma l}{Z_0 \cosh \gamma l + Z_R \sinh \gamma l} \right)$$

(1.14)

For a lossless transmission line, attenuation constant  $\alpha=0$ ,  $\gamma=j\beta$  and  $\beta=2\pi/\lambda$ .

$$Z_{in} = Z_0 \left( \frac{Z_R \cos\beta l + jZ_0 \sin\beta l}{Z_0 \cos\beta l + jZ_R \sin\beta l} \right)$$

(1.15)

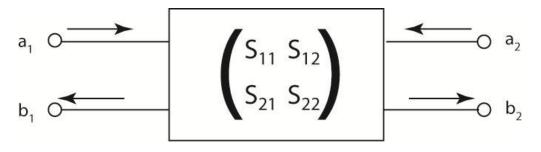

## 1.2.4 Scattering parameters

Figure 1.5 2-port network

The scattering parameters (S-parameters) describe the electric behavior of a linear electric network when a signal passes through. It is a transfer matrix that correlates incoming waves and outgoing waves, namely for a 2-port network

$$\binom{b_1}{b_2} = \binom{S_{11} \quad S_{12}}{S_{11} \quad S_{22}} \binom{a_1}{a_2}$$

(1.16)

where  $\binom{a_1}{a_2}$  and  $\binom{b_1}{b_2}$  are incoming and outgoing waves, and  $\binom{S_{11}}{S_{11}} = \binom{S_{12}}{S_{22}}$  are S-parameters.

To be specific, the  $S_{11}$  is the input signal reflection coefficient;  $S_{12}$  is the reverse gain;  $S_{21}$  is the forward gain and  $S_{12}$  is the signal reflection coefficient at the output port.

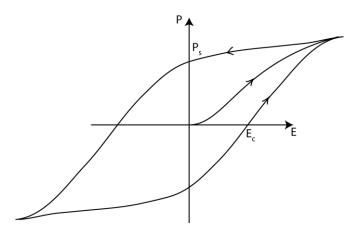

#### **1.3 FERROELECTRICITY**

Figure 1.6 P-E loop

Ferroelectricity is a property for materials that have a spontaneous or permanent polarization that can be hysterically reversed by external electric field(5). It was first observed by Anderson and Cady in Rochelle salt in 1918(6, 7). Later Busch and Scherrer(8) observed ferroelectricity in potassium dihydrogen phosphate (KDP) and then extended to all tetragonal

dihydrogen phosphate. Another important discovery of ferroelectricity is among perovskite oxides including  $BeTiO_3(9, 10)$ ,  $PbTiO_3(11)$ ,  $KTaO_3(12)$ , and  $NaVO_3(12)$ . Today, over 700 materials are found ferroelectric and many novel applications are made.

Analogous to ferromagnetism that shows hysteresis behavior under external magnetic field, the ferroelectric polarization is reserved when the external electric field switches direction until it reaches a value  $E_c$  that is called *coercive field*. In ordinary dielectric materials, the polarization  $\vec{P}$  induced by external field has a simple linear relation with electric field  $\vec{E}$  by giving  $\vec{P} = \varepsilon_0 \chi \vec{E}$ , where  $\varepsilon_0$  is the dielectric constant of air and  $\chi$  is the electric susceptibility of the dielectric. The ferroelectric material, however, does not have a simple analytic relation, as shown in Fig. 1.6.

### **1.3.1** Origin of ferroelectricity

The origin of ferroelectricity is much more complicated than ferromagnetism. It is widely viewed by a net dipole moment caused by the displacement of atoms under interatomic forces. Under external field, the dipole moment of atoms aligns with it. And after the field is removed, the dipoles still keep the favored polarization, namely the *remnant polarization*. The ferroelectric behavior can be very different even among materials with similar crystalline structures. For example, oxides with perovskite structure all have ABO<sub>3</sub> crystal structure, but the chemically different atoms result in different long-range and short-range Coulomb forces, which stabilizes the atoms in different structural phase. Cohen calculated the electronic structures of BeTiO<sub>3</sub> and PbTiO<sub>3</sub>, the well-known ferroelectric perovskite oxides, using all electron, full potential, linearized augmented plane-wave method(*13*). He revealed that the hybridization of titanium 3d states and oxygen 2p states play an important role in ferroelectricity. The PbTiO<sub>3</sub> is stabilized in a tetragonal phase by a large strain from hybridization of lead and oxygen states.

While the  $BaTiO_3$  in rhombohedral structure that caused by ionic interaction between barium and oxygen atoms.

A ferroelectric material is often only ferroelectric under certain temperature called Curie temperature  $T_c$ , accompanied by a structural phase transition. Above the Curie temperature, the material is *paraelectric*. Multiple Curie temperature can co-exist for one material. For example, BaTiO<sub>3</sub> has 3 Curie temperatures, 393 K, 278 K and 183 K. Accompanied phase transitions are cubic to tetragonal at 393 K, tetragonal to orthorhombic at 278 K and orthorhombic to rhombohedral at 183 K.

Beyond bulk ferroelectricity, some thin film materials show ferroelectricity under external strains, which modifies the interatomic forces and produce a net dipole moment. One striking example is  $SrTiO_3$  which is not ferroelectric in the bulk, however it shows ferroelectricity when grown on different substrates with epitaxial strain(*14-16*). In this dissertation, I will cover the ferroelectricity of strained  $SrTiO_3$  under various circumstances.

### 1.3.2 Applications

Ferroelectrcity is such a novel property that it finds use in many aspects of device applications(*17*). Ferroelectric random access memories (FeRAM) use the non-volatile remnant polarization to regulate the current floating through the device (ferroelectric field effect transistor) or keep the non-volatile voltage even the external power is shut off (ferroelectric capacitor), making "instant-on" computers possible. The capacitance of a ferroelectric capacitor is tunable under external field by tuning the dielectric constant. The value of the dielectric constant is also considerably huge close to the phase transition compared to regular capacitors, which made it a

smaller size in application. All ferroelectrics are also pyroelectric, and all pyroelectrics are piezoelectric, which provides possibilities for sensor applications.

#### 2.0 EXPERIMENTAL METHODS

In this chapter, I will introduce some important experimental techniques that are important in nanoelectronics. These techniques involve basic electronic characterization of nanoscale devices, nanoscale imaging of topographic and dielectric properties of sample surface as well as sensing ultra small capacitance at microwave frequencies.

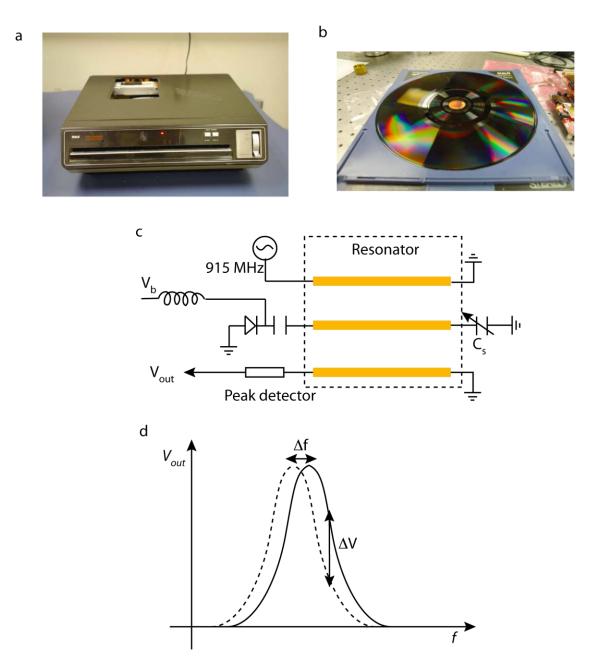

### 2.1 MICROWAVE CAPACITANCE SENSING

In 1964, Radio Corporation of America (RCA) introduced a video play back system called Capacitance Electronic Disc (CED) VideoDisc (Fig. 2.1a). In this system, information (0s and 1s) is encoded in hills and valleys in a plastic disc (Fig.2.1b). A metal stylus moves above the disc and senses the capacitance changes between the stylus and disc. To sense the capacitance change, the stylus is attached to a microwave resonator excited at an off-resonance frequency 915 MHz, as shown in Fig. 2.1c. The resonance frequency of the resonator is perturbed by the capacitance between the stylus to the disc(*18, 19*). The transmitted microwave power is finally detected by a microwave peak detector, converting power to voltage. A small capacitance change will cause the resonance frequency to shift, as well as causing the output voltage to change (Fig. 2.1d). The operating frequency is chosen at the frequency with maximum voltage response, normally at the largest slope of the resonance curve. Owing to the

high operating frequency, the sensitivity of this capacitance sensor is extremely high, typically  $10^{-16} \sim 10^{-19} F / \sqrt{Hz}$  for RCA sensors.

Figure 2.1 Working principle for RCA's CED microwave capacitance sensing. (a) Photograph of RCA CED play back system. (b) Photograph of CED disc. (c) Detection circuit. (d) Capacitance shift causes resonance frequency shift, resulting an ultimate voltage change in the peak detector output.

In this dissertation work, we developed an improved version of RCA sensor to measure the ultra small capacitance of quantum dots and memristive devices. We also integrated this sensor to an AFM for scanning capacitance imaging, as will be introduced in Chapter 5 and Appendix A.

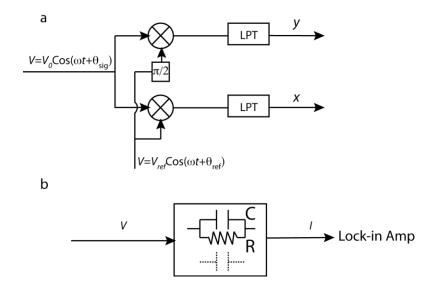

## 2.2 LOCK-IN DETECTION

In experiment, the real physical signal is often overwhelmed by all kinds of noises, e.g. 60 Hz power line noise, Johnson noises coming from the resistors due to thermal fluctuations, shot noise due to statistical fluctuations of charge carriers and acoustic noise coming from vibration sources etc. The signal to noise ratio can be as small as 10<sup>-9</sup>, i.e. measuring 1 nV in 1V noise. Since the noises are either random or have specific frequencies, one smart way is to "dye" (modulate) the signal with certain frequency that is away from any noise frequencies, then detect the signal only at that modulated frequency (reference frequency), effectively filtering out the noises. This is the idea of lock-in detection and a lock-in amplifier is used to detect small AC signal. The signal is often modulated by applying a small AC voltage to the source. In other experiments like optical experiment, the laser beam can be chopped so that the light intensity is modulated, resulting a modulated AC signal in the optical detector.

Figure 2.2a shows a simplified schematic of a lock-in amplifier. A small AC signal  $\tilde{V} = V_0 \cos(\omega t + \theta_{sig})$  passes through *x* and *y* channel mixers and get mixed with the reference signal with same frequency  $\tilde{V}_{ref} = V_{ref} \cos(\omega t + \theta_{ref})$ . The output from the *x* channel after the mixer turns into

$$\tilde{V} \otimes \tilde{V}_{ref} = V_0 V_{ref} \cos(\omega t + \theta_{sig}) \cos(\omega t + \theta_{ref})$$

$$= \frac{1}{2} V_0 V_{ref} \cos(\theta_{ref} - \theta_{sig}) + \frac{1}{2} V_0 V_{ref} \cos(2\omega t + \theta_{ref} + \theta_{sig})$$

(2.1)

Figure 2.2 Schematic of a lock-in amplifier (a) and measurement setup (b).

After passing through a low pass filter, the second term with  $2\omega$  frequency is filtered out and only the DC term  $\frac{1}{2}V_0V_{ref}\cos(\theta_{ref}-\theta_{sig})$  is reserved. Finally the signal is subjected to an amplifier to compensate the term  $\frac{1}{2}V_{ref}$  so that the x channel reads

$$X = V_0 \cos(\theta_{ref} - \theta_{sig}) \tag{2.2}$$

Similarly the y channel reads

$$Y = V_0 \sin(\theta_{ref} - \theta_{sig}) \tag{2.3}$$

since the phase of the reference signal in the y channel is shifted by 90°. Noises with different frequencies will be also filtered out as far as the cut off frequency of the low pass filter is smaller than the difference between noise frequency and reference frequency.

This lock-in technique can be used to measure the capacitance of quantum dots, which can be modeled as a capacitor in parallel with a resistor (Fig. 2.2b). Prior to the measurement, a test capacitor  $C_0$  (dashed object in Fig. 2.2)) is used to adjust the phase  $\theta_{ref} = \theta_{sig} + \pi/2$  such that the entire capacitive signal is in *x* channel and resistive signal in *y* channel. This can be seen by calculating the current that is the inputted to the lock-in amplifier

$$I = V_0 \omega C_0 \cos(\omega t + \theta_{sig} + \frac{\pi}{2})$$

(2.4)

After mix with the reference signal  $V_{ref} \cos(\omega t + \theta_{ref})$ , the *x* channel reads  $V_0 \omega C_0 \cos(\theta_{sig} + \frac{\pi}{2} - \theta_{ref})$  and *y* channel reads  $V_0 \omega C_0 \sin(\theta_{sig} + \frac{\pi}{2} - \theta_{ref})$ . Setting  $\theta_{ref} = \theta_{sig} + \pi/2$  will set *y* channel to zero and *x* channel contains the capacitance information.

Then replace the test capacitor with QD of complex impedance  $\frac{R}{1+j\omega CR}$ , and the current is  $I = V_0 \omega C \cos\left(\omega t + \theta_{sig} + \frac{\pi}{2}\right) + \frac{V_0}{R} \cos(\omega t + \theta_{sig})$ (2.5)

After the *x* channel mixer,

$$I \otimes V_{ref} \cos\left(\omega t + \theta_{ref}\right) = \frac{V_0 V_{ref} \omega C}{2} \cos\left(\theta_{sig} + \frac{\pi}{2} - \theta_{ref}\right) + \frac{V_0}{2R} \cos\left(\theta_{sig} - \theta_{ref}\right) + f(2\omega)$$

$$= \frac{V_0 V_{ref} \omega C}{2} + f(2\omega)$$

(2.6)

Then the *x* channel reads

$$X = V_0 \omega C \tag{2.7}$$

Similarly in *y* channel,

$$Y = \frac{V_0}{R} \tag{2.8}$$

Finally we have the capacitance and resistance in x and y channels, repectively:

$$C = \frac{X}{V_0 \omega} \tag{2.9}$$

### 2.3 ATOMIC FORCE MICROSCOPY

$R = \frac{V_0}{V}$

The phenomenal success of Scanning Tunneling Microscope (STM) enables people to image individual atoms(20) at the first time. However several limitations apply: (a) The sample surface must be conductive to allow tunnel current to occur, and usually it requires ultra high vacuum; (2) Significant forces will act collaterally with the tunnel current. The latter was then speculated that these forces might actually be useful for imaging, i.e. a force microscope. In 1986, Binning (the same inventor of STM) invented atomic force microscope (AFM) by regulating the atomic forces at a constant value above sample surface. With the fact that an individual atom can also interact with the AFM tip, AFM now reaches atomic resolution(21).

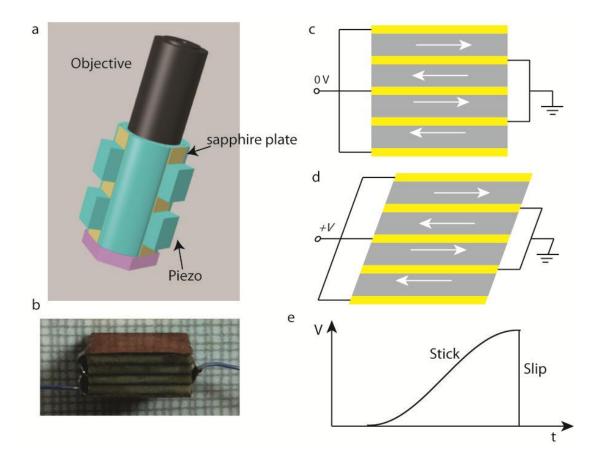

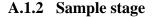

Nowadays, AFM provides a very important versatile tool to nano-scale sciences not only for basic imaging capabilities, but also it is used for measuring other physical properties like piezoelectricity (peizoresponse force microscopy(22)), capacitance(23), conductance, manipulating individual atoms and cells, AFM lithography and many more. In this dissertation, I will introduce two AFMs I developed for low temperature application and for capacitance imaging. The instrumentation details can be found in Appendix A, and the applications of AFM are covered in nearly every following chapters. In the following sections, I will introduce some basic concepts as well as the working mechanism on AFM.

### 2.3.1 Tip-sample interaction forces

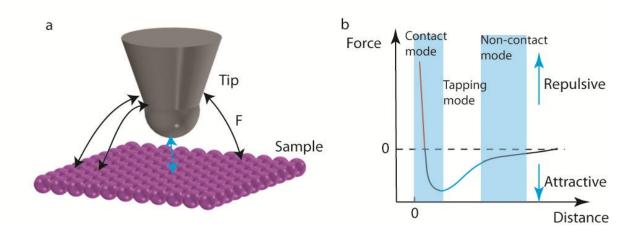

Figure 2.3 Forces between tip and sample. Black and blue arrows indicate long-range forces and short-range forces, respectively. (b) Force curve and imaging modes.

When an AFM tip is brought close to the surface (<100 nm), numerous atomic forces will interact between the tip and sample. Basically there are two types of force, long ranges forces (tens of nanometers range) like Van der Waas forces caused by the fluctuations and electric dipole of atoms and their mutual polarization, electrostatic forces and magnetic forces caused by excess surface/tip charges and magnetic dipoles, and short range force (sub-nanometer) from chemical bonding(24) (Fig. 2.3). Figure 2.3b shows the force curve as a function of tip sample distance. Different tip sample distance will induce different types of forces that allow different imaging modes, which will be introduced in Sec. 2.3.3.

#### 2.3.2 Force sensors

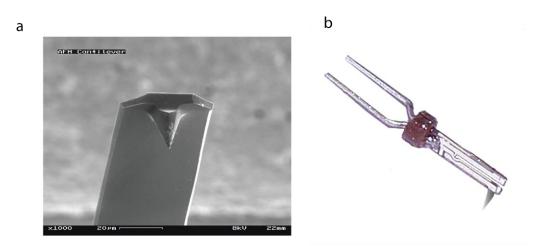

Figure 2.4 Force sensors (a) Cantilever based. (b) Tuning fork based.

The AFM tip is attached to a force sensor that detects the atomic forces. To achieve high resolution, the tip must have a sharp radius to reduce the interaction area on the sample surface; in the mean time the force sensor should be sensitive enough to sense the force changes due to changing of tip-sample separation in a scan. Two types of force sensors are commonly used, cantilever based and tuning fork based (Fig. 2.4). The cantilever beam is usually made by silicon or silicon nitride with various spring constants. A laser beam is focused on the highly reflective backside of the cantilever beam to detect beam deflection caused by atomic forces. With proper setup it can detect forces as small as several piconewtons (10<sup>-12</sup> N). While the AFM cantilever works by detecting the amplitude of deflection, AFM tip with a tuning fork works totally a different way. A typical tuning fork force sensor is made of quartz, which has very high quality factor (several thousand at room temperature). Owing to this high quality factor, a small perturbation by the atomic forces will cause a significant resonance frequency shift. To recap, the tuning fork is driven by an external piezo stack at a frequency close to resonance frequency.

up by two prolongs of the tuning fork. This electric signal provides a feed back signal to a phase locked loop (PLL), which actively compensates the frequency shifts caused by the tip-sample separation during a scan. With the frequency shift information, sample topography can be reconstructed.

#### 2.3.3 AFM working principles

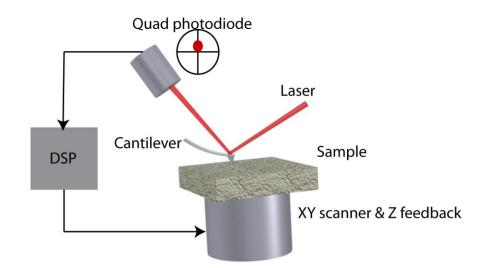

Figure 2.5 AFM working principle

The modern form of AFM comes from Meyer and Amer's approach in 1988(25). As shown in Fig. 2.5, a laser beam is focused on the backside of cantilever beam, and the reflected laser beam is detected by a quad photodiode. This photodiode has four quadrature in which the difference between the sum signals of top two and bottom two gives out the cantilever deflection. The deflection signal is then input to a digital signal processor (DSP) that generates real time feedback signals. The feedback signal in turn controls the Z feedback piezo to maintain constant tip-sample separation during a scan. In our home-made AFM, we use a DSP that is found on a sound board (Signal Ranger).

Before scanning, the tip has to be brought close to the sample surface until engaging atomic forces, this procedure is called "touch down". The touch down procedure is done by driving a Z motor to approach either tip or sample to the other, in the mean time the DSP continuously monitor the deflection signal (or resonance frequency if using a tuning fork) to prevent tip crash. When a "set point" is reached, i.e. the cantilever is bent by a preset amount, the tip is touched down. Two types of operation mode are common, contact mode and noncontact mode. In contact mode the cantilever is usually soft and in contact with sample surface. The deflection signal is generated by cantilever bending due to sample topography changes in a scan. In the non-conctact mode, the cantilever is vibrating all the time instead of touching sample surface. The vibrating amplitude serves as feedback signal as atomic forces can dampen it.

### 2.4 PIEZORESPONSE FORCE MICROSCOPY

Piezoresponse force microscopy (PFM) studies the mechanical response of a piezoelectric material under external electric field. Since all ferroelectrics are piezoelectric, PFM is a powerful tool to image and manipulate the ferroelectric domain walls, encode and read out information(26), and even has biological applications(27, 28).

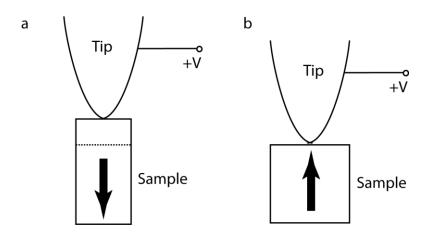

During the operation, the tip is in contact with the sample surface. The voltage applied on the tip will cause local deformation of sample due to piezoelectric effect. When the polarization is vertical and pointing down normal to the sample surface, i.e. c- axis, positively applied voltage will cause the material to expand (Fig. 2.6a). And the electromechanical response is in phase with external field (phase  $\varphi = 0^{\circ}$ ). In the opposite, when the polarization is along the c+ axis, the material will contract under positive voltage and the electromechanical response is out of phase ( $\varphi = 180^\circ$ , Fig. 2.6b).

Figure 2.6 Working principle of PFM. (a) Sample expands when the polarization is aligned with external electric field. (b) Sample contracts when the polarization is reversely aligned with external electric field. The arrows in (a) and (b) represent polarization direction.

### 2.4.1 Piezoelectric effect

The strain effect under the external electric field in piezoelectric materials is described by a rank-3 tensor with relation  $S_i = d_{ki}E_k$ , where  $S_i$  is strain tensor,  $d_{ki}$  is piezoelectric tensor and  $E_k$  is the electric field. For vertical polarization (c axis) that a typical PFM detects, the corresponding tensor is  $d_{33}$ . For example, BaTiO<sub>3</sub> has a  $d_{33}$  component of 85.6 pm/V, which means under 1 V applied voltage along the c-axis the displacement of the barium atom is 85.6 pm.

The applied voltage usually has a form

$$V = V_{dc} + V_{ac} \cos \omega t \tag{2.11}$$

where  $V_{dc}$  is the DC voltage that manipulates the sample polarization and the second term is the AC part that detects the electromechanical response. And the electromechanical response can subsequently written as

$$\Delta = V_{dc}d_{33} + V_{ac}d_{33}\cos(\omega t + \varphi) \tag{2.12}$$

Where  $\varphi$  is the phase that takes values of 0° and 180°.

In real operation, the AC modulation frequency is chosen at the resonance frequency of the tip-sample mechanical system to allow optimal piezoresponse signal.

### 2.4.2 Application

Figure 2.7 Topography (a) and PFM image (b) of BaTiO3. Scale bar: 10 µm. Images are taken from http://en.wikipedia.org/wiki/File:Bulk\_BTO\_PFM\_scan.png.

Different working modes lead to different applications for PFM. One basic mode is vertical or lateral polarization imaging, in which the tip is only biased by AC modulation during the scan. Figure 2.7 shows vertical PFM imaging of BaTiO3, and in the PFM image the sample shows a series of ferroelectric domain wall strips that does not show up in the AFM topography. AFM lithography is also feasible by manipulating ferroelectric domains with a DC voltage and image at 0 V. Ultra dense ferroelectric memory application (>16 Gbit inch<sup>-2</sup>) is demonstrated by writing domains on highly strained BaTiO<sub>3</sub> film and reading out the polarization dependent

tunnel current(26). Instead of scanning, PFM can also working at the spectroscopy mode. In this mode, PFM tip is located at one position while the DC voltage is swept, enabling study of polarization on external field (e.g. *P-E* hysteresis loop). We will use this mode to study the ferroelectricity of strained SrTiO<sub>3</sub> sample in chapter 4. PFM also finds use in many other applications, e.g. biological applications to differentiate organic and mineral components of biological systems.

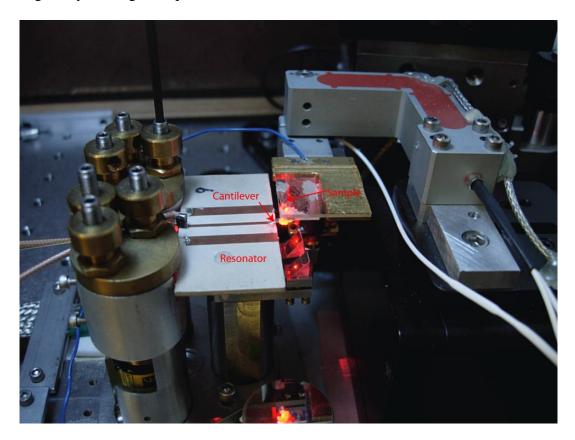

# 2.5 SCANNING MICROWAVE MICROSCOPY

As introduced in previous sections, sample topography and piezoresponse can be readily mapped out at nano-scale using AFM and PFM. In many cases, sample surface impedance, capacitance and dielectric constants are of great interests. Such material properties can be locally probed by looking at the electromagnetic interaction of microwave between the tip and sample. Integrating the microwave resonator sensor with an AFM, we are capable of doing scanning microwave microscopy (SMM), by which we can map the capacitance information, dopant density and impedance information together with sample topography.

Numerous forms of microwave sensors have been applied to SMM including broadband waveguide, resonant slots(29), stripline and microstrip resonators(30) and coaxial resonator(31). In our case we integrated a microstrip resonator similar to RCA's sensor, which will be covered in Chapter 5 and Appendix A.

#### 3.0 SKETCHED OXIDE SINGLE ELECTRON TRANSISTOR

Devices that confine and process single electrons represent the ultimate scaling of electronics(*32*, *33*). Such control has been achieved in a variety of materials(*34-36*), resulting in devices with remarkable electronic, optical and spintronic properties. Oxide heterostructures formed from ultrathin layers of LaAlO<sub>3</sub> grown on TiO<sub>2</sub>-terminated SrTiO<sub>3</sub>(*37*, *38*), combined with a reversible nanoscale patterning technique(*39*), provide a versatile platform for nanoscale control at the single-electron limit. Here shown in this chapter we use this technique to develop "sketched" single-electron transistors (SketchSET) whose properties are probed through temperature-dependent transport. Shell filling from *N*=0 up to *N*=2 electrons by single-electron tunneling can be tuned by both bottom and side gates. Hysteresis in electron occupation is observed and attributed to ferroelectricity within the SrTiO<sub>3</sub> tunnel barrier. These single-electron devices may find use as nanoscale hybrid piezoelectric/charge sensors, and as elemental building blocks for solid-state quantum computation and quantum simulation platforms.

#### 3.1 LaAlO<sub>3</sub>/SrTiO<sub>3</sub> HETEROSTRUCTURE

Recently, a new high-mobility 2 dimensional electron gas (2DEG) was discovered at the interface of two wide-bandgap insulators LaAlO<sub>3</sub> and SrTiO<sub>3</sub>(37). Since this discovery,

extensive interests are drawn on this novel material system. The transition between insulating and conducting states in this system is an atomically-sharp function of the number of LaAlO<sub>3</sub> unit cells (uc)(*38*). At or below a thickness of 3 uc LaAlO<sub>3</sub>, the interface is insulating, while for  $\geq$ 4 uc the interface is conducting. Also this metal-insulator transition can be tuned by applying a large back gate voltage. The conductance of films grown at a critical thickness (3uc-LaAlO<sub>3</sub>/SrTiO<sub>3</sub>) can be locally and reversibly controlled using a conductive atomic force microscope (c-AFM) probe technique(*39*). Positive voltages applied to the c-AFM tip locally switch the 3uc-LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface to a conducting state, while negative voltages locally restore the insulating state. Besides these findings, magnetoresistance effect at the interface of these two non-magnetic perovskites was also observed. Superconductivity with a transition temperature 200 mK further indicates the quantum nature of this 2DEG.

Compared to its semiconductor analogue AlGaAs/GaAs heterostructure, the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface has similar electronic properties (Table 3.1). Meanwhile, unlike the AlGaAs/GaAs where the 2DEG globally exist at the interface, the c-AFM lithography technique enables us locally control the conductivity at the interface of 3uc-LaAlO<sub>3</sub>/SrTiO<sub>3</sub>, which provides us a versatile template for oxide nanoelectronics. As a result, nanowires(*39*), field effect nano-transistors(*40*), rectified nano-junctions(*41*) and photoconductive switches(*42*) have been realized. Moreover, the quantum nature of the 2DEG brings more possible novel device applications, e.g. single electron transistor that represent the ultimate scaling of electronics.

|                         | AlGaAs/GaAs                                 | LaAlO <sub>3</sub> /SrTiO <sub>3</sub>    |  |  |

|-------------------------|---------------------------------------------|-------------------------------------------|--|--|

| Thickness               | order of 10 nm                              | 10 nm (4 K)<br>≤4 nm (300 K)              |  |  |

| Carrier density         | $10^{10} \sim 10^{11} \text{ cm}^{-2}$      | $10^{13}$ ~ $10^{14}$ cm <sup>-2</sup>    |  |  |

| Host layer thickness    | Tens of nanometer                           | ≥4 u.c. (1.6 nm)                          |  |  |

| Mobility                | $\geq 10^{7} \text{cm}^{2}/\text{Vs}$ (4 K) | $\leq 10000 \text{ cm}^2/\text{Vs}$ (4 K) |  |  |

| Effective electron mass | 0.03 m <sub>0</sub>                         | 3 m <sub>0</sub>                          |  |  |

| Mean free path          | order of 100 um                             | tens of nanometer                         |  |  |

| Fermi velocity          | 107 cm/s                                    | 0.6-6×106 cm/s                            |  |  |

| Fermi energy            | 14 meV                                      | 0.4-4 meV                                 |  |  |

| Scattering time         | 0.38-38 ps                                  | 3 ps                                      |  |  |

Table 3.1 Transport parameters of AlGaAs/GaAs and LaAlO<sub>3</sub>/SrTiO<sub>3</sub> 2DEG.

# 3.1.1 Polar catastrophe and interface reconstruction

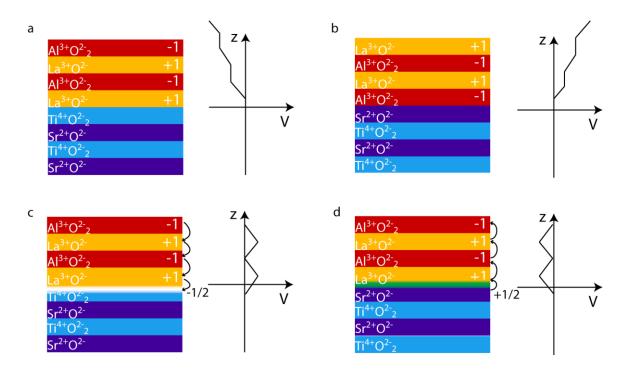

When expitaxially grow a polar material on a non-polar material, the interface is subject to atomic abruptness, resulting a polar discontinuity. Such discontinuity is unstable and an electronic reconstruction takes place to compensate for it. This process is called "polar catastrophe" and is considered as the mechanism behind the conductivity at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface(*43*).

The perovskite oxides LaAlO<sub>3</sub> and SrTiO<sub>3</sub> can be decomposed into a series of alternating planes (La<sup>3+</sup>O<sup>2-</sup>, Al<sup>3+</sup>O<sup>2-</sup><sub>2</sub>, Sr<sup>2+</sup>O<sup>2-</sup>, Ti<sup>4+</sup>O<sup>2-</sup><sub>2</sub>) on (001) plane. Among them the La<sup>3+</sup>O<sup>2-</sup> and Al<sup>3+</sup>O<sup>2-</sup><sub>2</sub> planes are polar with +/-1 net charge, while Sr<sup>2+</sup>O<sup>2-</sup> and Ti<sup>4+</sup>O<sup>2-</sup><sub>2</sub> planes are neutral.

Figure 3.1 shows two configurations that  $LaAlO_3$  is grown on TiO<sub>2</sub> or SrO terminated SrTiO<sub>3</sub> substrate. A quick examination to the structure using parallel plate capacitor model can reveal that, if there are no interface charges (Fig. 3.1a and b), unrealistic voltages will accumulate as a function of LaAlO<sub>3</sub> thickness. Therefore, interface reconstruction must happen to allow compensate charges to cancel the divergent built-in voltages. For TiO<sub>2</sub> terminated LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure, half an electron per unit cell can migrate from LaAlO<sub>3</sub> to the interface so that Ti ion at the interface become Ti<sup>3.5+</sup> (Fig. 3.1c). This electronic interface reconstruction leaves whole structure neutral and an n-type 2DEG at the interface. Such n-type interface was confirmed by transport measurement, as pointed out in the introduction section of this chapter. While for SrO terminated heterostructure, half a hole must be acquired by the SrO to maintain structure neutral and avoid voltage divergence (Fig. 3.1d). Such hole transfer is realized by atomic interface reconstruction, i.e. by moving oxygen vacancy. However, electrically this interface is not conductive, since the mobility of holes is much lower than n-type interface. Further first principle calculation shows that the formation energy of oxygen vacancy is much smaller at the interface than at the LaAlO<sub>3</sub> surface. Oxygen vacancies can spontaneously form to compensate the holes at interface, leaving a low density of mobile holes(44).

Figure 3.1 Polar catastrophe and interface reconstruction. (a) LaAlO<sub>3</sub> is grown on TiO<sub>2</sub> terminated SrTiO<sub>3</sub> substrate. Both SrTiO<sub>3</sub> and LaAlO<sub>3</sub> are decomposed into a series of (001) planes. A potential is built up in the LaAlO<sub>3</sub> film due to the non-zero charges of reconstructed planes. (b) LaAlO<sub>3</sub> is grown on SrO terminated SrTiO<sub>3</sub> substrate. As same as (a), a potential is built up in the LaAlO<sub>3</sub> film due to the non-zero charges of reconstructure as (a), half electron per unit cell is transferred from LaAlO<sub>3</sub> to the interface to compensate the physically unrealistic buit-in potential and keep LaAlO<sub>3</sub> crystal neutral. As a result, a two dimensional electron gas forms at the interface. (d) Similarly to (c), half hole per unit cell is acquired by the SrO to maintain structure neutral for SrO terminated heterostructure. However these holes at the interface are not mobile to form a conductive interface.

## 3.1.2 LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure growth

The LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostrucutre samples used in this work were all grown at Chang-Beom Eom's group at University of Wisconsin-Madison using pulsed-laser deposition (PLD).

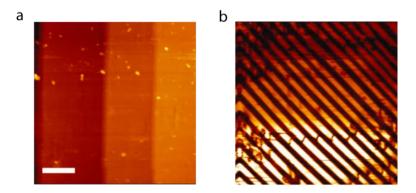

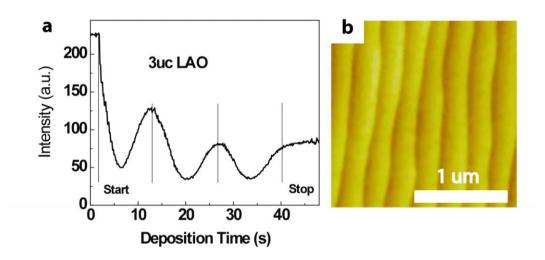

In the growth, ultrathin layers of epitaxial LaAlO<sub>3</sub> were grown on SrTiO<sub>3</sub> substrates by PLD system equipped with high-pressure reflection high-energy electron diffraction (RHEED), which enabled the precise layer-by-layer growth of the thin films to be monitored *in-situ*. Before deposition, low miscut ( $<0.10^\circ$ ) SrTiO<sub>3</sub> substrate were etched using buffered HF acid for 30~90 seconds to maintain Ti-termination and the substrates were annealed in oxygen at 1000  $^{\circ}$ C for 2~12 hours to create atomically smooth surfaces with single unit cell height steps. The film deposition was achieved utilizing a resistive heater. A KrF excimer laser (248 nm) beam was focused on a stoichiometric LaAlO<sub>3</sub> single crystal target to an energy density of 2.0~2.5 J/cm<sup>2</sup> and pulsed at 3Hz. Two different growth conditions were used. For the first, the substrate growth temperature was set at 780  $^{\circ}$ C and chamber oxygen background pressure of 7.5×10<sup>-5</sup> mbar, and the samples were annealed at 600 °C, 400 mbar for 1 hour. While for the second the substrate growth temperature was set at 550  $\,^{\circ}\mathrm{C}$  and chamber oxygen background pressure of  $1 \times 10^{-3}$  mbar, and samples were cooled down to room temperature. The LaAlO<sub>3</sub> RHEED intensity oscillations for the second sample are shown in Fig. 3.2a, which indicated a layer-bylayer mode. The resulting surface of the LaAlO<sub>3</sub> thin films were atomically smooth with single unit cell height steps measured by atomic force microscopy (AFM), as seen in Fig. 3.2b.

Figure 3.2 Growth of  $LaAlO_3$  layer on  $SrTiO_3$  substrate. (a), RHEED intensity oscillations of the  $LaAlO_3$  film. The vertical dot lines indicate the growth time of  $LaAlO_3$  unit-cell layer. (b), AFM images of 3 uc  $LaAlO_3$  films on  $SrTiO_3$  substrate.

## **3.2 CONDUCTIVE AFM LITHOGRAPHY**

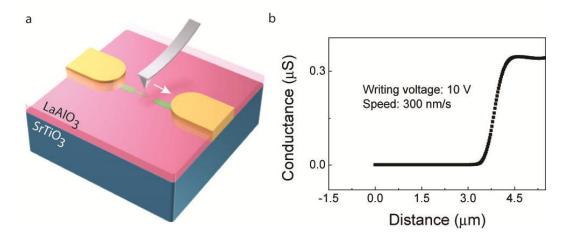

As introduced in Sec. 3.1, the polar catastrophe induces metal-insulator transition at the interface between LaAlO<sub>3</sub> and TiO<sub>2</sub> terminated SrTiO<sub>3</sub>. When the thickness of LaAlO<sub>3</sub> is smaller or equal to 3 unit cells, the built in potential is not big enough to induce polar catastrophe. This 3 unit cell thickness is such a critical thickness that external doping of charges on LaAlO<sub>3</sub> surface could easily switch the insulating interface to a conducting state. In our previous work, we used a positively biased (8~10 V) AFM tip to locally induce a metal-insulator transition so that conducting nanostructure could be written on demand using this AFM lithography. In the mean time, negative voltages on the tip can erase the nanostructure and restore the insulating state.

Figure 3.3 shows the nanowire writing in the 3 uc LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure. The tip is biased with 10 V and slowly dragged from one electrode to the other at 300 nm/s. As soon as the tip reaches the other electrode, the conductance between the two electrodes has several orders of increase, which means a nanowire is written under the tip path. We can also cut the across the wire by with -10 V on tip, and the conductance is found to drop back to the insulating value, effectively creating a nano junction. The wire width is determined to be as small as 2 nm by looking at the sharpness of the conductance decrease. Using this method, we can write a third nanowire perpendicular to the nano junction as a gate to tune the conductance in the junction, effectively creating a field effect transistor(40). The nano junction is also found photo sensitive, creating photo current under light illumination, which is essentially a rewritable photodetector(42). By applying an asymmetric voltage (triangle function from -10 V to 10 V) to reconnect the nano junction, we can write a diode(41).

Figure 3.3 Conductive AFM lithography in 3 unit cell LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure.

The writing procedure is attributed to a "water cycle" mechanism, as Steve Hellberg (Naval Research Laboratory) suggested in an unpublished work after first principle calculations. In a regular sample environment, the 3-uc LaAlO<sub>3</sub> surface is covered by a thin layer of water molecules. A positively biased tip will break up the bonds between  $H^+$  and  $OH^-$  and removes  $OH^-$  atoms in a writing process, leaving an excess of  $H^+$  atoms locally charging the surface. Such charged surface will switch the insulating interface to conductive and functions as an effective modulation doping to the interface.

This mechanism was further proved by our group by testing the writing procedure in different environment conditions(45). We found that writing in nitrogen gas, dry air helium gas and vacuum environment, no metal-insulator transition was observed. While writing in air with controlled humidity, the writing procedure worked. Furthermore, the written nanostructure preserves much longer in the environment that forbids writing than in air.

# 3.3 SINGLE ELECTRON TRANSISTORS

For over decades the Moor's law dictates the trend of semiconductor industry development by shrinking device size down at a constant speed. However in the very near future it will meet the scaling limits when the quantum effects emerge. Mesoscopic electron transport study reveals novel phenomena that may lead to future device applications. Single electron transistor (SET) is the striking example that reflects the ultimate scaling of electronics. As the name indicates, a single electron transistor (SET) is an electronic device that allows only one electron to pass through at a time.

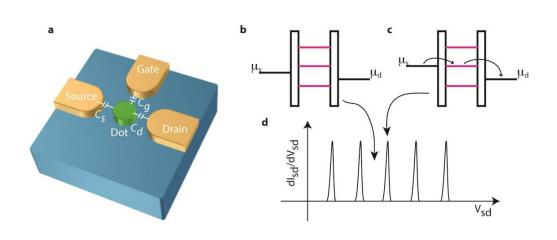

Figure 3.4 Single electron transistor and constant interaction model. (a) Schematic for a single electron transistor. The gate, source and drain electrode are capacitively coupled to the central island. (b) When the electrochemical potential of the quantum dot lies outside the bias window  $\mu_s - \mu_d$ , the QD is in Coulomb blockade and no current can flow from the source to drain. (c) When the electrochemical potential of the quantum dot aligns with the electrochemical potential of source or drain electrode, resonant electron tunneling is observed and current can flow between source and drain. (d) Differential conductance exhibits a series of Coulomb peaks when resonant tunneling happens.

A typical SET consists of a source, drain and gate electrode as well as an island (quantum dot) that is separated by two tunnel barriers (Fig. 3.4a). The concept of SET is originated from the observation of quantized charges ( $\sim e^2/h$ ) in a metal particle surrounded by tunnel junctions back to the 1960s(46). Later on the theory of Coulomb blockade was proposed to explain the resonant tunneling behavior, and the SET was realized in silicon MOSFET inversion layer 2DEG and AlGaAs/GaAs 2DEG material systems(47). In modern efforts, as more interests were casted on SET, it was reported in numerous material systems like carbon nanotube, graphene and organic molecular(35, 36, 48). The function of SET does not only rely on regulating the electron number, but also the SET can serve as an electron thermometer(49), transistor memory(50), a

device to single-shot read out electron spins(51), a nano-mechanical sensor(52) and can be integrated to an AFM probe to invasively detect nano-scale electric fields(53).

The electronic states of SET is described using constant interaction (CI) model(54) (33, 55). The model states that electrons can resonantly tunnel through the tunnel barrier once at a time to the quantum dot (QD) when the electrochemical potential of the QD  $\mu_{dot}$  lies in the bias window, i.e. between the electrochemical potentials of the source ( $\mu_s$ ) or drain ( $\mu_d$ ) electrodes (Fig. 3.4c). In the opposite case  $\mu_{dot}$  is outside the bias window (Fig. 3.4b), the device is in Coulomb blockade, i.e. electrons can not tunnel through the barriers due to Coulomb repulsion. Two assumptions are made in this model: (a) A single capacitor *C* is parameterized to describe the Coulomb interaction among the electrons in the QD and between the QD and the environment. Namely as shown in Fig. 3.4a,  $C=C_s+C_d+C_g$ , where  $C_s$  is the capacitance between the source and QD,  $C_d$  is the capacitance between the drain and QD, and  $C_g$  is the capacitance between the gate and QD. (b) The single particle energy levels in SET are not affected by these interactions. Defining  $V_{s}$ ,  $V_d$  and  $V_g$  as the respective potentials of source, drain and gate, the total energy of U(N) of QD with N electrons can be described as

$$U(N) = \frac{(-|e|(N-N_0) + C_s V_s + C_d V_d + C_g V_g)}{c} + \sum_{n=1}^N E_n(B)$$

(3.1)

where -|e| is the electron charge,  $N_0$  is the number of electrons at zero external gate voltage and  $E_n$  is the single particle level which is a function of external magnetic field *B*.  $C_sV_s$ ,  $C_dV_d$  and  $C_gV_g$  are effective induced charges that can alter the electrochemical potential of the QD.

The electrochemical potential of the QD is defined as

$$\mu(N) \equiv U(N) - U(N-1)$$

=  $\left(N - N_0 - \frac{1}{2}\right) E_C - \frac{E_C}{|e|} \left(C_s V_s + C_d V_d + C_g V_g\right) + E_n$  (3.2)

where  $E_c = e^2/C$  is the charging energy and  $\mu(N)$  denotes the transition between Nth and (N-1)th ground state.

The addition energy is defined as the spacing of electrochemical potentials of transitions between two successive ground states.

$$E_{add} = \mu(N) - \mu(N - 1) = E_{C} + \Delta E$$

(3.3)

where  $\Delta E$  is the level spacing in the QD. From the equation we can see to add one electron, the required energy has two parts: one is the electrostatic part to charge the dot, the other one is the chemical part that determines the level spacing.

The electrochemical potential of the QD is changed linearly with the gate voltage, and the corresponding proportion factor  $\alpha = C_g/C$ . This proportion factor directly correlates the Coulomb peak spacing in measurement (specified by voltage) to the addition energy (specified by meV).

# 3.4 SketchSET DEVICE FABRICATION AND SIZE CHARACTERIZATION

In this section, I will introduce how to create single electron transistors using c-AFM lithography in the 3 uc LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterostructure, as well as how to characterize the device size.

## **3.4.1** Device fabrication

The 5 mm x 5 mm LaAlO<sub>3</sub>/SrTiO<sub>3</sub> samples are patterned with 6 gold electrodes contacting the interface by ion milling 25 nm and backfilling with 2 nm Ti and 23 nm Au. Device "sketching" is performed using conductive-AFM lithography (c-AFM) in a commercial

AFM system (Asylum MFP-3D). The following procedures are typical in SketchSET fabrication:

(1) Virtual electrodes writing: q-2DEG "virtual electrodes" (500 nm wide, ~10 m long) are written in contact with the gold electrodes by applying a 10 V (or 8 V) voltage to the tip and raster scanning at constant (typically 800 nm/s) speed. As a result, a 5  $\mu$ m × 5  $\mu$ m working area surrounded by virtual electrodes is defined for fine device writing.

(2) *Source, drain and side gate electrodes definition:* Source and drain virtual electrodes are connected by writing a q-2DEG nanowire using the same parameters. Side-gate nanowires are written either 50 nm away from the center of source-drain nanowire, or directly cross the source-drain nanowire in the perpendicular direction.

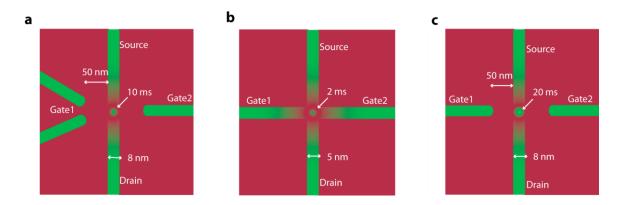

(3) *Tunnel barrier and QD creation:* After source, drain and wire electrodes are written, the AFM tip is positioned at the center of source-drain nanowire. A brief negative pulse (-10 V or -8 V, 15 ms to 1000 ms duration) is applied to create a barrier. Writing this barrier typically causes 10% decrease in conductance at room temperature as measured between any two of the electrodes. Finally a subsequent positive pulse with the same magnitude and much shorter duration (2 ms to 20 ms) is applied to create the QD. Detailed parameter values are listed in Table 3.2 and Fig. 3.5. Five devices are fabricated and the results of three devices are discussed in this dissertation.

Table 3.2 Device sketching parameters. Five SketchSET devices as well as a control device are sketched. Device A, B and C are presented in this dissertation.

|          | Sample<br>growth<br>conditions                            | Electrodes<br>writing<br>amplitude<br>(V)/width<br>(nm) | Erase<br>pulse<br>amplitude<br>(V) | Erase<br>pulse<br>duration<br>(ms) | Write<br>pulse<br>amplitude<br>(V) | Write<br>pulse<br>duration<br>(ms) | Side gate<br>distance to<br>dot (nm) |

|----------|-----------------------------------------------------------|---------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|--------------------------------------|

| Device A | 7                                                         | 10/8                                                    | -10                                | 1000                               | 10                                 | 10                                 | 50                                   |

| Device B | 80 C° at<br>7.5 ×10 <sup>-5</sup>                         | 8/5                                                     | -8                                 | 15                                 | 8                                  | 2                                  | N/A                                  |

| Device C | mBar                                                      | 10/8                                                    | -10                                | 2000                               | 10                                 | 20                                 | 50                                   |

| Device D | 5                                                         | 8/3.3                                                   | -10                                | 1000                               | 10                                 | 5                                  | N/A                                  |

| Device E | $50 \text{ C}^{\circ} \text{ at}$<br>$1.0 \times 10^{-3}$ | 8/3.3                                                   | -10                                | 1000                               | 10                                 | 1                                  | N/A                                  |

| Device F | mBar                                                      | 8/3.3                                                   | -10                                | 100                                | N/A                                | N/A                                | N/A                                  |

Figure 3.5 Device A, B and C structures. (a), Device A. The side gates are sketched 50 nm away from the QD. (b), Device B. Two crossed nanowires are written first then the barrier and QD are pulsed. (c), Device C. Two side gates are sketched 50 nm from the QD.

#### **3.4.2** Device size characterization

The sizes of the nanowire electrodes, tunnel barrier and the QD are dependent on the writing/erasing parameters, sample growth conditions, sample surface conditions, and relative humidity. We perform a similar calibration method as Ref. (*39*) to estimate the wire width and QD diameter.

To estimate a nanowire width, the AFM tip is slowly moved across the wire (-10 V, 10 nm/s) and the conductance is measured simultaneously as a function of tip position. The full width of half maximum of the deconvolved differential conductance gives out the wire width. For a wire written at 10 V, 800 nm/s speed, the wire width averages 8 nm.

To estimate the QD diameter, an array of dots is written in a 1-µm gap. The spacing between the dots is varied from large to small values until the observance of a steady conductance increase, i.e. the dots connected each other and the gap was filled. 2 ms, 10 ms and 20 ms QD write pulse durations (10 V) will produce QD "diameters" of 0.8 nm, 1.5 nm and 2.8 nm respectively. For a diameter of 1.5 nm, one can roughly estimate the number of electrons able to reside within the QD, based on typical two-dimensional carrier densities for nanoscale writing  $n\approx5\times10^{13}$  cm<sup>-2</sup> at the 3uc-LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface:  $N=\pi d^2n/4\approx1$  electron. This estimate agrees well with the observed behavior, described in the following sections.

The barrier size is estimated in a reverse way. An array of erase pulses (-10 V) is applied across a predefined rectangle q-2DEG area of 1 um width. For certain pulse spacing the conductance of the rectangle area drops to zero, which means the barriers connects each other and the pulse spacing is the barrier diameter. As a result, a 1 second -10 V pulse creates 6 nm barrier diameter. However, this value is under estimated especially for shorter pulse durations. Since thermally activated carriers can still contribute to the conductance even when the barriers

successfully connects each other, which gives false indication that the area has not been completely cut.

## 3.5 MEASUREMENT

After AFM lithography, the sample is quickly transferred without to a closed cycle cryostat with careful prevention to light illumination. Then the cryostat is pumped down to vacuum  $(2 \times 10^{-5} \text{ Torr})$  and no significant conductance drop is observed at room temperature. Low temperature transport measurement is carried out at temperatures varying from 16 K to 40 K, with the differential conductance  $G_{sd}$  and capacitance  $C_{sd}$  measured using a dual phase lock-in amplifier (Stanford Research SR830, same method as described in section 2.2). In the set up, a DC voltage  $V_s$  plus a small ac modulation  $V_s+V_{ac}\cos(2\pi ft+\varphi)$  are applied to source electrode through a bias box, where f=25.5 Hz is the modulation frequency and  $\varphi$  is the reference phase. The phase  $\varphi$  is adjusted such that the X channel measures the capacitance of the device and Y channel is measures the differential conductance of the device. Besides temperature sweep, side gate and back gate effects to the single electron charging are also explored.

## 3.6 RESULTS AND DISCUSSION

In this section, I will discuss the results of electronic characterization of Device A, B and C. Experiments focus on the effect of the side gates ( $V_{g1}$  and  $V_{g2}$ ) and back gate ( $V_{gb}$ ) on the source-drain differential conductance ( $G_{sd}$ ) and capacitance ( $C_{sd}$ ).

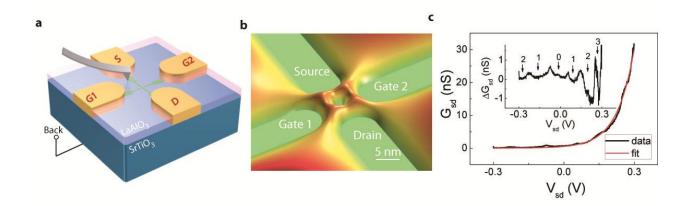

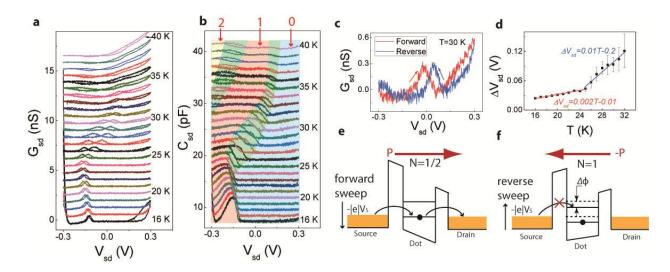

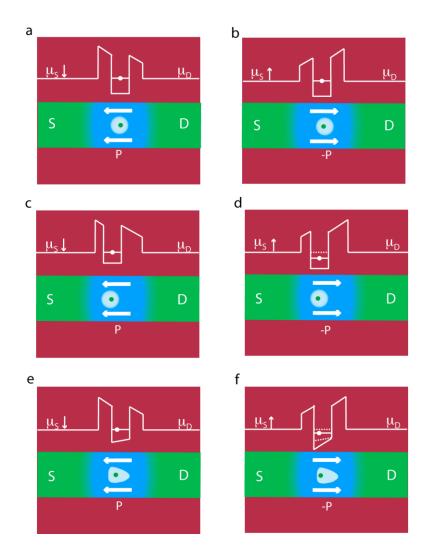

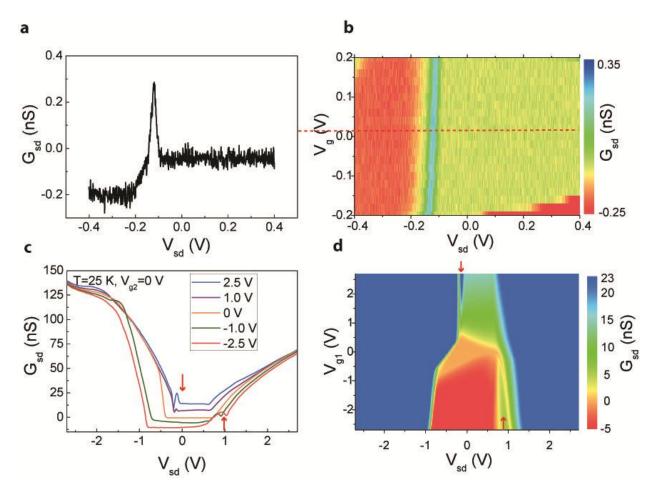

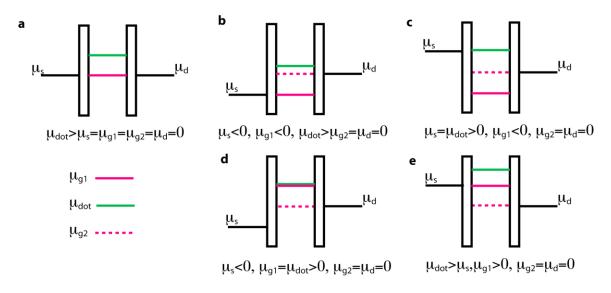

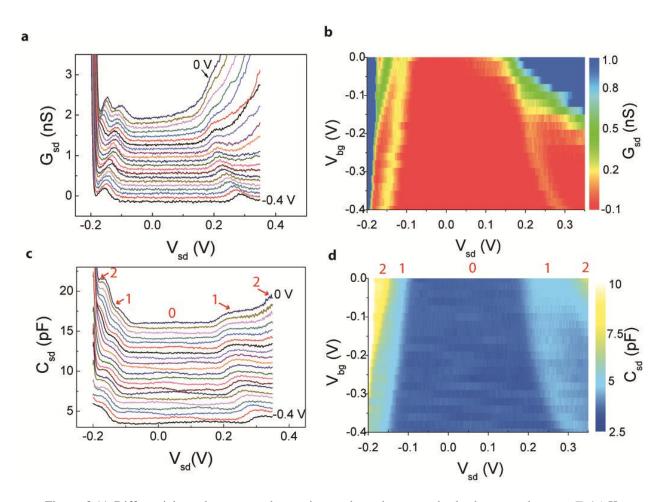

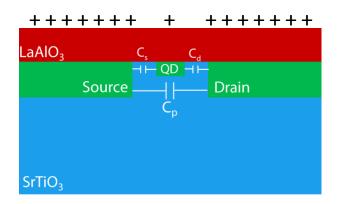

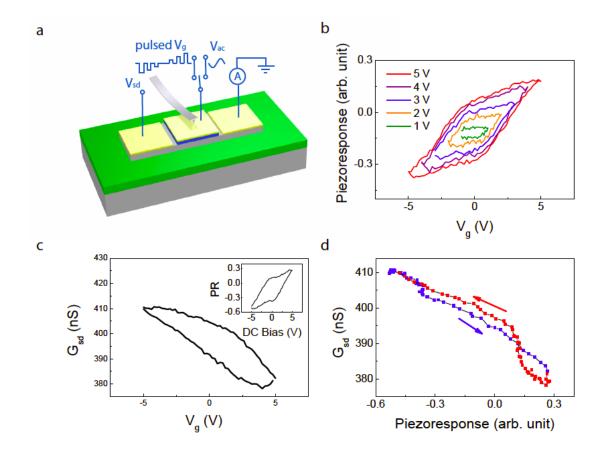

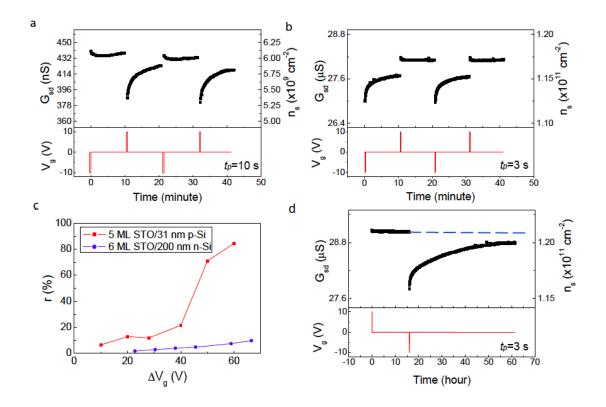

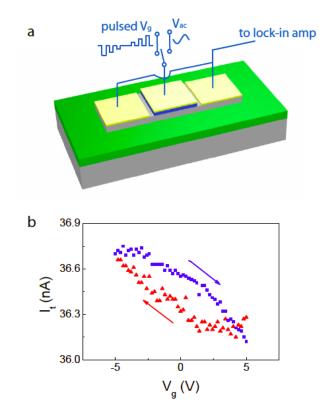

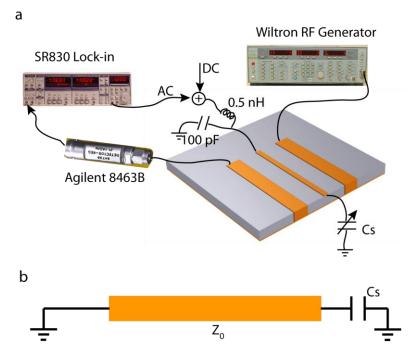

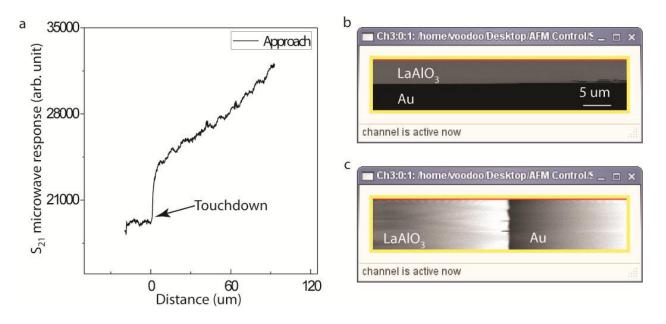

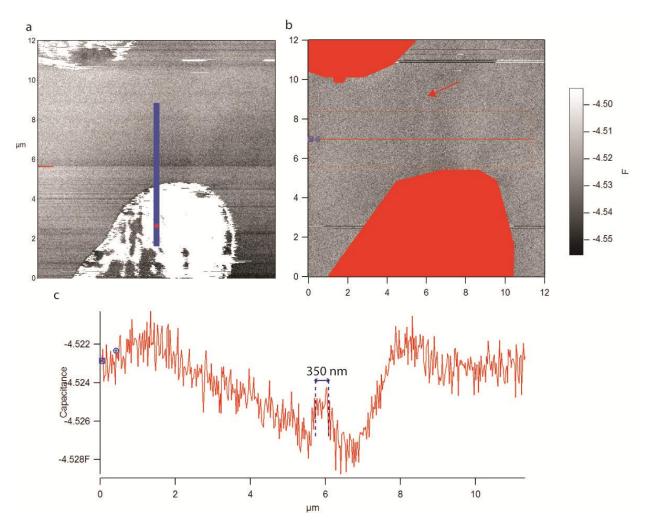

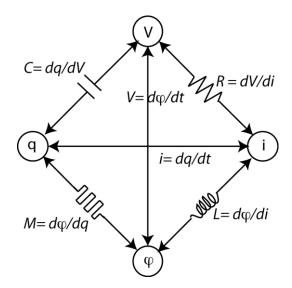

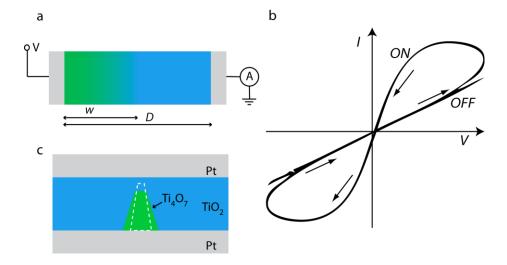

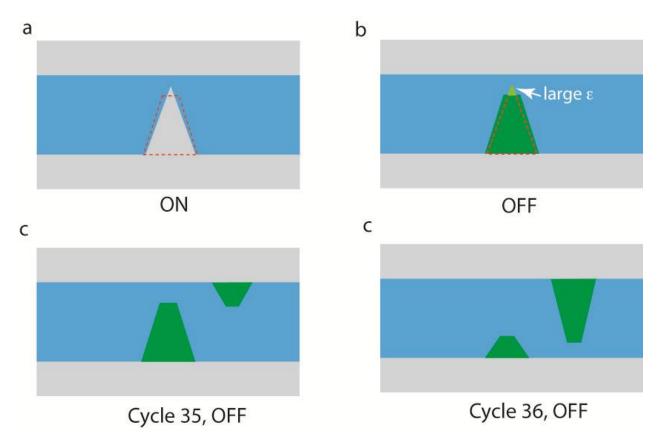

We use COMSOL finite element analysis to illustrate the electron energy barriers of the device (Fig. 3.6b). Figure 3.6c shows the differential conductance curve for Device A immediately after cooldown, where the side gates and  $V_{gb}$  are all grounded and the drain  $V_d$  (where current is measured) is held at virtual ground. For sufficiently small source-drain voltage ( $V_{sd}$ ), the differential conductance is strongly suppressed, and increases rapidly above a well-defined threshold. Though the structure is nominally symmetric, the threshold for positive and negative  $V_{sd}$  is generally different owing to hard-to-control variations at the scale of ~1 nm. Figure 1c shows two clearly resolved "Coulomb peaks" for  $V_{sd}$ <0, and other three are observed for  $V_{sd}$ >0 before being obscured by the large conducting background. Subsequent voltage cycles result in fewer peaks (see Fig. 3.7). Structures that do not have islands at the intersection (e.g., SketchFET devices) do not exhibit any Coulomb peaks.