# REAL TIME 3-D GRAPHICS PROCESSING HARDWARE DESIGN USING FIELD-PROGRAMMABLE GATE ARRAYS.

by

James Ryan Warner

B. S. in Computer Engineering, Pennsylvania State University, 1999

Submitted to the Graduate Faculty of

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

University of Pittsburgh

2008

# UNIVERSITY OF PITTSBURGH

# SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

James Ryan Warner

It was defended on

September 18, 2008

and approved by

Dr. Alexander Jones, Assistant Professor, Department of Electrical and Computer

Engineering

Dr. Allen Cheng, Assistant Professor, Department of Electrical and Computer Engineering

Thesis Advisor: Dr. James T. Cain,

Professor Emeritus, Department of Electrical and Computer Engineering

Copyright © by James Ryan Warner

2008

# REAL TIME 3-D GRAPHICS PROCESSING HARDWARE DESIGN USING FIELD-PROGRAMMABLE GATE ARRAYS

James Ryan Warner, M.S.

University of Pittsburgh, 2008

Three dimensional graphics processing requires many complex algebraic and matrix based operations to be performed in real-time. In early stages of graphics processing, such tasks were delegated to a Central Processing Unit (CPU). Over time as more complex graphics rendering was demanded, CPU solutions became inadequate. To meet this demand, custom hardware solutions that take advantage of pipelining and massive parallelism become more preferable to CPU software based solutions. This fact has lead to the many custom hardware solutions that are available today.

Since real time graphics processing requires extreme high performance, hardware solutions using Application Specific Integrated Circuits (ASICs) are the standard within the industry. While ASICs are a more than adequate solution for implementing high performance custom hardware, the design, implementation and testing of ASIC based designs are becoming cost prohibitive due to the massive up front verification effort needed as well as the cost of fixing design defects.

Field Programmable Gate Arrays (FPGAs) provide an alternative to the ASIC design flow. More importantly, in recent years FPGA technology have begun to improve in performance to the point where ASIC and FPGA performance has become comparable. In addition, FPGAs address many of the issues of the ASIC design flow. The ability to reconfigure FPGAs reduces the upfront verification effort and allows design defects to be fixed easily.

iv

This thesis demonstrates that a 3-D graphics processor implementation on and FPGA is feasible by implementing both a two dimensional and three dimensional graphics processor prototype. By using a Xilinx Virtex 5 ML506 FPGA development kit a fully functional wireframe graphics rendering engine is implemented using VHDL and Xilinx's development tools. A VHDL testbench was designed to verify that the graphics engine works functionally. This is followed by synthesizing the design and real hardware and developing test applications to verify functionality and performance of the design. This thesis provides the ground work for push forward the use of FPGA technology in graphics processing applications.

# TABLE OF CONTENTS

| PRI | EFAC | CEXIX                                                         |

|-----|------|---------------------------------------------------------------|

| 1.0 |      | INTRODUCTION1                                                 |

|     | 1.1  | OVERVIEW1                                                     |

|     | 1.2  | STATEMENT OF THE PROBLEM 7                                    |

|     | 1.3  | OUTLINE9                                                      |

| 2.0 |      | COMPUTER GRAHPICS RENDERING 10                                |

|     | 2.1  | MATHMATICS OVERVIEW 12                                        |

|     |      | 2.1.1 Homogenous vectors                                      |

|     |      | 2.1.2 Coordinate System13                                     |

|     |      | 2.1.3 Object Representation15                                 |

|     |      | 2.1.4 Affine Geometric Transformations                        |

|     |      | 2.1.4.1 Translation Transformation17                          |

|     |      | 2.1.4.2 Scaling Transformation                                |

|     |      | 2.1.4.3 Rotation Transformation                               |

|     |      | 2.1.4.4 Transformation Compositions 22                        |

|     | 2.2  | THE GRAPHICS PIPELINE                                         |

|     |      | 2.2.1 Object Definition                                       |

|     |      | 2.2.2 Scene Composition using World Coordinate Transformation |

|     |     | 2.2.3 View Coordinates and the View Transformation   | 29    |

|-----|-----|------------------------------------------------------|-------|

|     |     | 2.2.4 3D Projections and the Clipping Transformation | 34    |

|     |     | 2.2.4.1 Perspective Projection                       | 37    |

|     |     | 2.2.4.2 Parallel Projection                          | 39    |

|     |     | 2.2.5 Clipping                                       | 41    |

|     |     | 2.2.5.1 Cohen-Sutherland Two Dimensional Clipping    | 41    |

|     |     | 2.2.5.2 Cohen-Sutherland Three Dimensional Clipping  | 45    |

|     |     | 2.2.6 Screen Coordinate Transformation               | 49    |

|     |     | 2.2.7 Rasterization                                  | 51    |

| 3.0 |     | THE GRAPHICS PROCESSING UNIT                         | 56    |

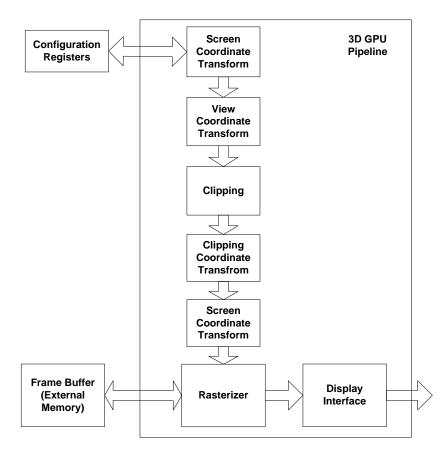

|     | 3.1 | GRAPHICS PIPELINE                                    | 61    |

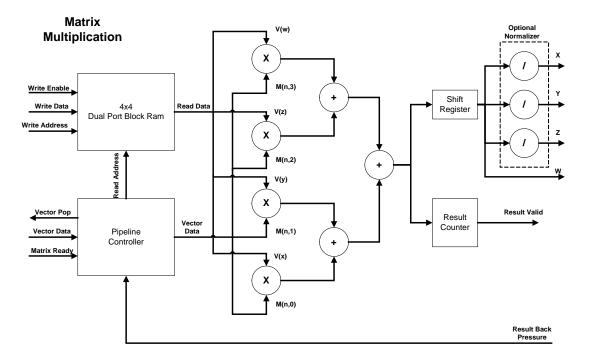

|     |     | 3.1.1 Matrix Multiplier Accelerator                  | 64    |

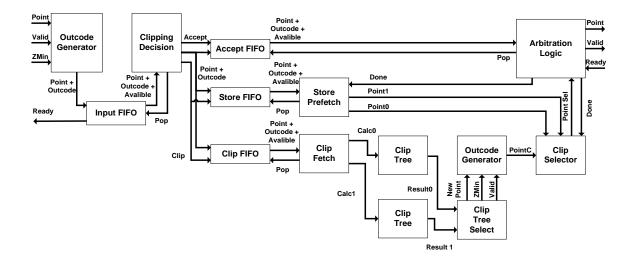

|     |     | 3.1.2 Clipping Design                                | 67    |

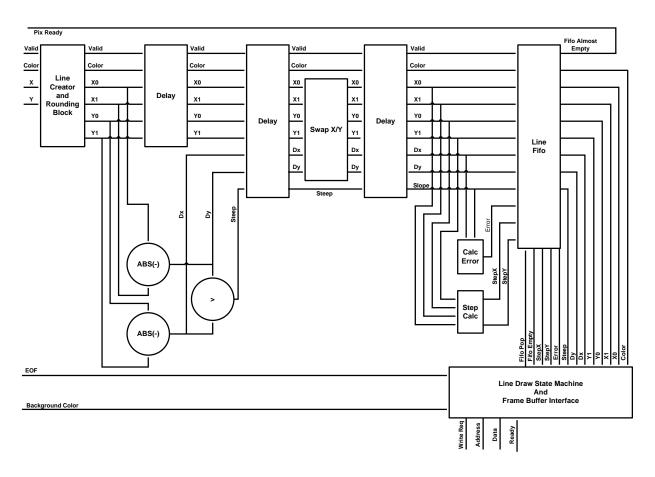

|     |     | 3.1.3 Line Rasterization                             | 79    |

|     |     | 3.1.4 Frame Buffer and Display Interface             | 83    |

|     | 3.2 | CENTRAL PROCESSING UNIT                              | 87    |

|     |     | 3.2.1 Graphics Pipeline Control Registers            | 89    |

|     |     | 3.2.2 Other Peripherals                              | 90    |

| 4.0 |     | GRAPHIC PROCESSING UNIT IMPLEMENTATION AND TESTING   | 91    |

|     | 4.1 | HARDWARE DEVELOPMENT PLATFORM                        | 91    |

|     | 4.2 | GRAPHICS PROCESSING UNIT IMPLEMENTATION              | 94    |

|     |     | 4.2.1 Floating Point Primitives                      | 96    |

|     |     | 4.2.2 Microblaze Implementation                      | . 100 |

|     | 4.2   | 2.2.1 B  | ase System Builder                           | 106 |

|-----|-------|----------|----------------------------------------------|-----|

|     | 4.    | 2.2.2 D  | VI IIC PLB Interface                         | 116 |

|     | 4.2   | 2.2.3 N  | 64 PLB controller interface                  | 117 |

|     | 4.    | 2.2.4 G  | raphics Pipeline Registers PLB interface     | 119 |

|     | 4.2.3 | Graphic  | cs Pipeline Implementation                   | 120 |

|     | 4.    | 2.3.1 F  | loating Point Conversion and Matrix Selector | 121 |

|     | 4.2   | 2.3.2 M  | Iatrix Transformation and Selection          | 122 |

|     | 4.    | 2.3.3 C  | ohen-Sutherland Clipping                     | 123 |

|     | 4.2   | 2.3.4 B  | resenham's Line Rasterizer                   | 124 |

|     | 4.    | 2.3.5 F  | rame Buffer and the ZBT Memory Controller    | 125 |

|     | 4.2   | 2.3.6 V  | GA Display Interface and the Line Doubler    | 125 |

| 4.3 | G     | RAPHIC   | CS PIPELINE FUNCTIONAL TESTBENCH             | 128 |

| 4.4 | G     | PU SYN   | THESIS                                       | 134 |

|     | 4.4.1 | Xilinx F | EDK and Microblaze                           | 134 |

|     | 4.4.2 | ISE and  | l Full GPU Synthesis                         | 136 |

|     | 4.4.3 | Synthes  | is Results                                   | 137 |

| 4.5 | SC    | OFTWA    | RE BASED HARDWARE TESTING                    | 138 |

|     | SUMM  | IARY, C  | CONCLUSIONS, AND FUTURE WORK                 | 144 |

| 5.1 | SU    | UMMAF    | RY AND CONCLUSIONS                           | 144 |

| 5.2 | F     | UTURE    | WORK                                         | 146 |

|     | 5.2.1 | Feature  | Additions                                    | 146 |

|     | 5.2.2 | Direct N | Memory Access                                | 148 |

|     | 5.2.3 | Transfo  | ormation Element Calculations                | 150 |

5.0

| 5.2.4 Using external processor over PCI express         | 151 |

|---------------------------------------------------------|-----|

| 5.2.5 More Parallelism in Rasterization                 | 152 |

| 5.2.6 Partial Reconfigurablity                          | 154 |

| APPENDIX A: GRAPHICS PIPELINE CONTROL REGISTERS         | 156 |

| APPENDIX B: N64 CONTROLLER REGISTERS                    | 163 |

| APPENDIX C: VHDL SOURCE CODE                            | 166 |

| C.1 TOP LEVEL VHDL FILE                                 | 166 |

| C.2 GRAPHICS PIPELINE TOP LEVEL VHDL FILE               | 175 |

| C.3 MATRIX MULTPLIER                                    | 191 |

| C.4 MATRIX MULTIPLIER WITH BUFFERING AND NORMILIZATION. | 199 |

| C.5 CLIPPING TREE                                       | 205 |

| C.6 OUTCODE GENERATOR                                   | 211 |

| C.7 CLIPPING LOGIC                                      | 214 |

| C.8 ABSOLUTE VALUE                                      | 235 |

| C.9 BRESENHAM'S ALGORITHM                               | 237 |

| C.10 ZBT FRAME BUFFER                                   | 250 |

| C.11 ZBT MEMORY CONTROLLER                              | 257 |

| C.12 ZBT PHYSICAL INTERFACE                             | 264 |

| C.13 ZBT PORT INTERFACE                                 | 267 |

| C.14 ZBT ARBITER                                        | 274 |

| C.15 ZBT WIDTH CONVERSION                               | 281 |

| C.16 ZBT MEMORY CONTROLLER PACKAGE                      | 284 |

| C.17 DVI PHYSICAL INTERFACE                             | 287 |

| C.18 VGA FRAME READER            |  |

|----------------------------------|--|

| C.19 VGA SYNC GENERATOR          |  |

| C.20 VGA CONTROLLER              |  |

| C.21 GRAPHICS PIPELINE TESTBENCH |  |

| APPENDIX D: C TESTCODE           |  |

| BIBLIOGRAPHY                     |  |

# LIST OF TABLES

| Table 2.1: 2D Outcode Assignment Table                                   |     |

|--------------------------------------------------------------------------|-----|

| Table 2.2: 2D Clipping Intersection Equations                            |     |

| Table 2.3: 3D Parallel Projection Outcode Assignment                     |     |

| Table 2.4: 3D Perspective Projection Outcode Assignment                  |     |

| Table 2.5: 3D Parallel Projection Clipping Intersection Equations.       |     |

| Table 2.6: 3D Perspective Projection Clipping Intersection Equations     |     |

| Table 3.1: 2D Outcode Assignment Table                                   | 69  |

| Table 3.2: 3D Perspective Outcode Assignment Table                       | 69  |

| Table 3.3: 2D Clipping Intersection Equations                            |     |

| Table 3.4: 3D Perspective Projection Clipping Intersection Equations     |     |

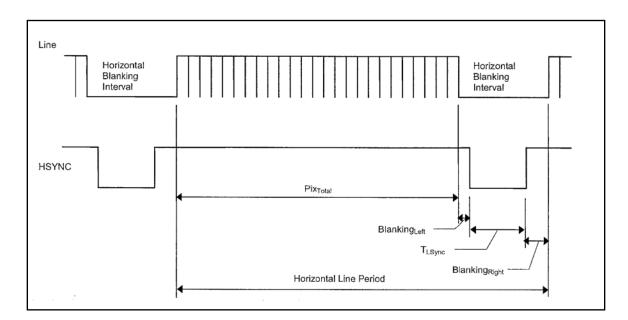

| Table 4.1: VGA Horizontal Timing Table                                   | 127 |

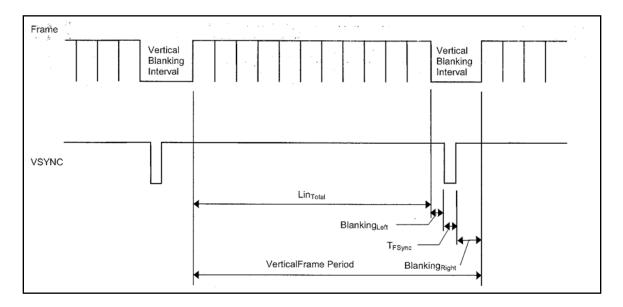

| Table 4.2: VGA Vertical Timing Table                                     | 127 |

| Table A.1: GPU Configuration Register Memory Map and Register Definition |     |

| Table B.1: N64 Controller Interface Memory Map and Register Definition   |     |

# LIST OF FIGURES

| Figure 1.1: Classic Graphics Pipeline (1)                        | 2  |

|------------------------------------------------------------------|----|

| Figure 1.2: GeForce 8800 CUDA Architecture (3)                   | 3  |

| Figure 1.3: Wireframe Modeling(1)                                |    |

| Figure 2.1: Computer Graphics Processing Pipeline(1)             | 11 |

| Figure 2.2: 2D Coordinate System                                 | 14 |

| Figure 2.3: 3D Cartesian Coordinate System                       | 14 |

| Figure 2.4: Polygon Mesh Representation(7)                       | 15 |

| Figure 2.5: Translation of a cube                                |    |

| Figure 2.6: Scaling of a cube.                                   | 19 |

| Figure 2.7: Differential Scaling of a cube                       | 19 |

| Figure 2.8: Right Handed Coordinate System with Rotational Angle |    |

| Figure 2.9: Rotation of a cube                                   |    |

| Figure 2.10: Object Centered on P1                               |    |

| Figure 2.11: Local to World Coordinate Translation               |    |

| Figure 2.12: Example Graphics Pipeline(1)                        |    |

| Figure 2.13: Cube in Object Coordinates                          |    |

| Figure 2.14: Cubes in World Space Coordinates                    |    |

| Figure 2.15: Viewing Point with Viewing Direction in World Coordinates      | 29 |

|-----------------------------------------------------------------------------|----|

| Figure 2.16: Viewing plane                                                  | 30 |

| Figure 2.17: View coordinate system.                                        | 31 |

| Figure 2.18: View Volume                                                    | 31 |

| Figure 2.19: Viewing coordinate system defined with World coordinate system | 33 |

| Figure 2.20: Viewing Coordinate System                                      | 34 |

| Figure 2.21: Example Graphics Pipeline(6)                                   | 35 |

| Figure 2.22: Parallel Projection                                            | 36 |

| Figure 2.23: Perspective Projection                                         | 36 |

| Figure 2.24: Perspective Projection (7)                                     | 37 |

| Figure 2.25: Perspective Projection (7)                                     | 38 |

| Figure 2.26: Parallel Projection (8)                                        | 40 |

| Figure 2.27: Clipping Region Definitions.                                   | 42 |

| Figure 2.28: Illustration of 2D Cohen Sutherland Clipping.                  | 45 |

| Figure 2.29: Parallel Projection                                            | 46 |

| Figure 2.30: Perspective Projection                                         | 46 |

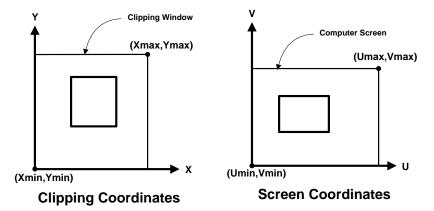

| Figure 2.31: Clipping to Screen Coordinates                                 | 49 |

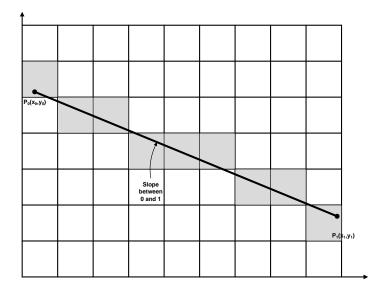

| Figure 2.32: Rasterized Line(10)                                            | 52 |

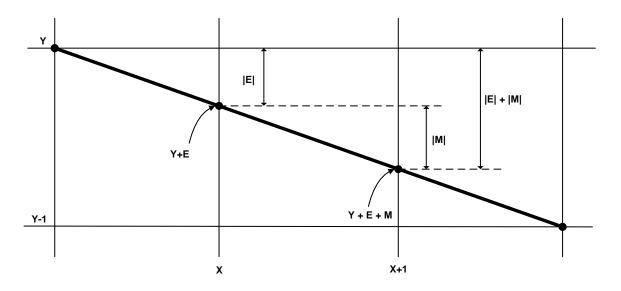

| Figure 2.33: Bresenham's Line Algorithm Diagram(11)                         | 53 |

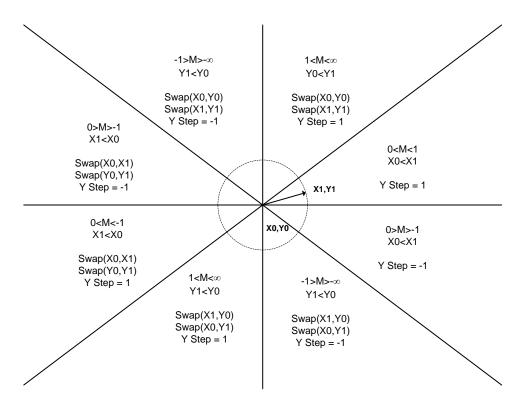

| Figure 2.34: Line Rasterization Pseudo code.                                | 54 |

| Figure 2.35: Slope Octet Ranges                                             | 55 |

| Figure 3.1: Graphics Pipeline(1)                                            | 58 |

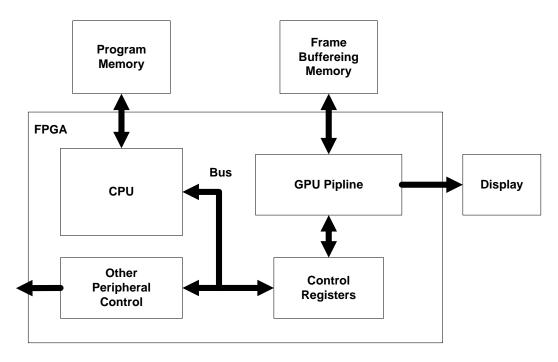

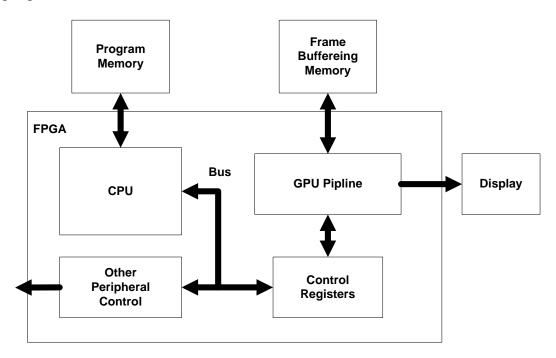

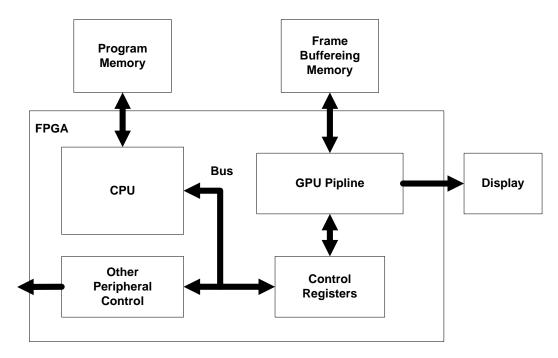

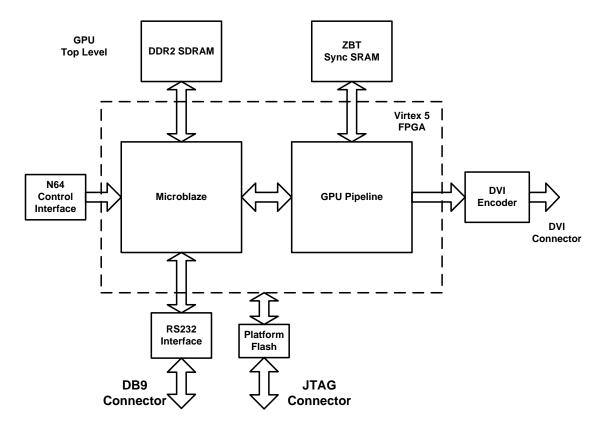

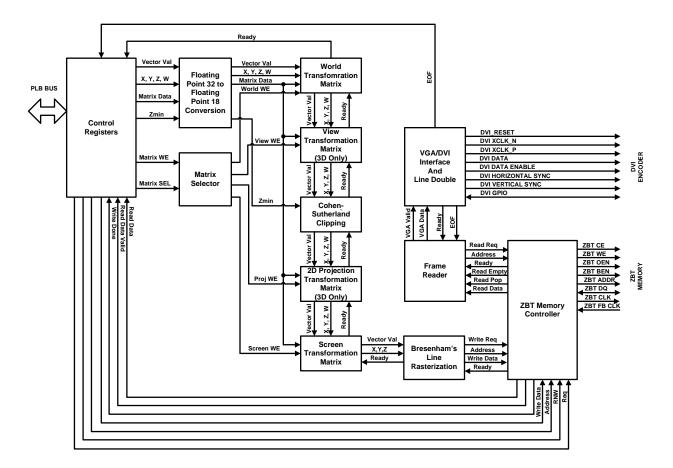

| Figure 3.2: GPU Top Level Block Diagram                                     | 59 |

| Figure 3.3: Computer Graphic Pipeline(1)                             | 61 |

|----------------------------------------------------------------------|----|

| Figure 3.4: 3D Graphics Pipeline                                     | 62 |

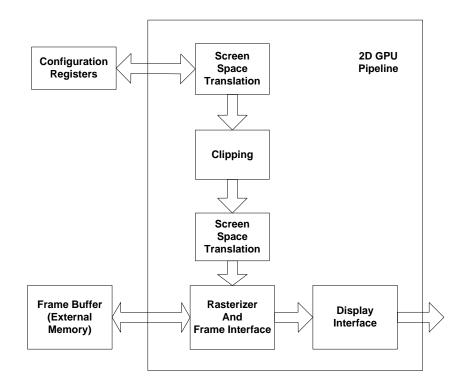

| Figure 3.5: 2D Graphics Pipeline                                     | 63 |

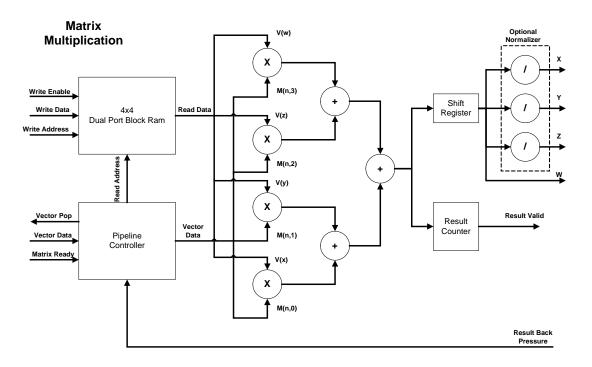

| Figure 3.6: Floating Point Matrix Multiplication Block Diagram       | 65 |

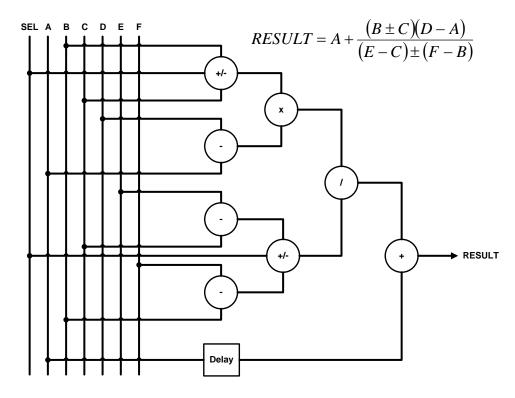

| Figure 3.7: Clipping Logic                                           | 68 |

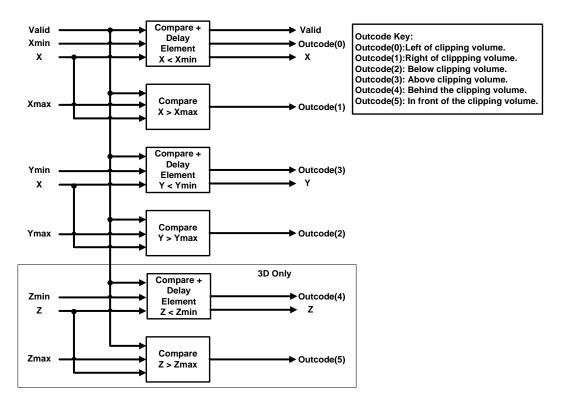

| Figure 3.8: Outcode Generator for Clipping Logic.                    | 70 |

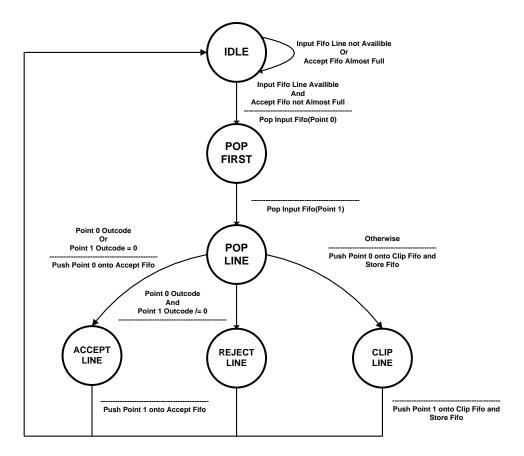

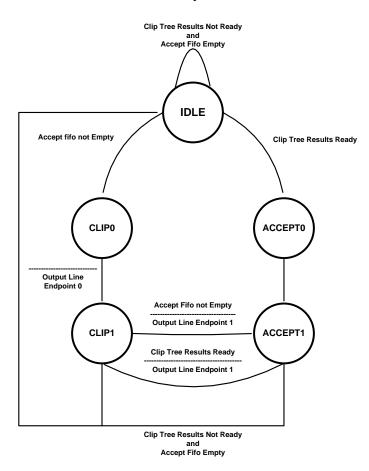

| Figure 3.9: Clipping Decision Logic State Machine                    | 71 |

| Figure 3.10: Cohen-Sutherland Line Clipping with outcodes            | 75 |

| Figure 3.11: Edge Intersection calculator.                           | 76 |

| Figure 3.12: Round Robin Arbiter                                     | 78 |

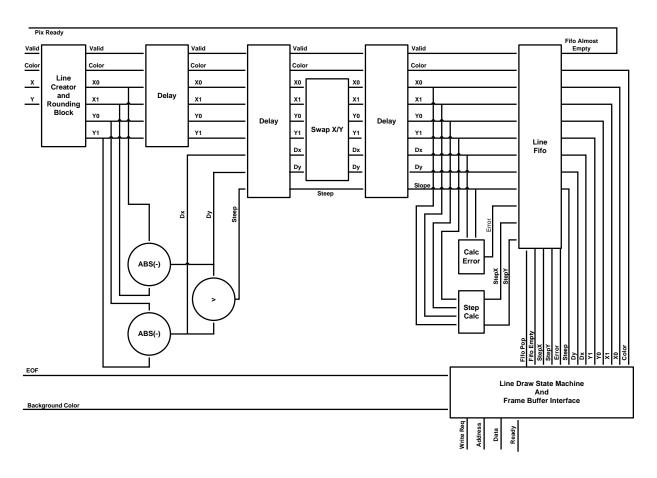

| Figure 3.13: Bresenham's Line Rasterizer Design                      | 80 |

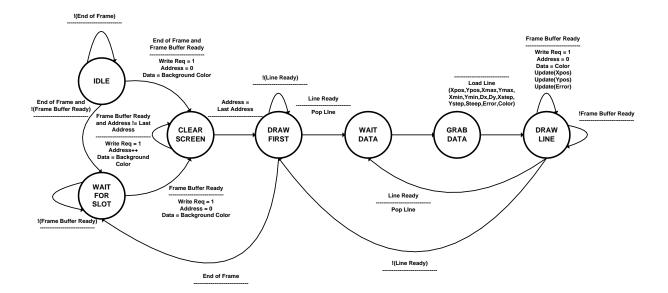

| Figure 3.14: Line Drawing State Machine                              | 82 |

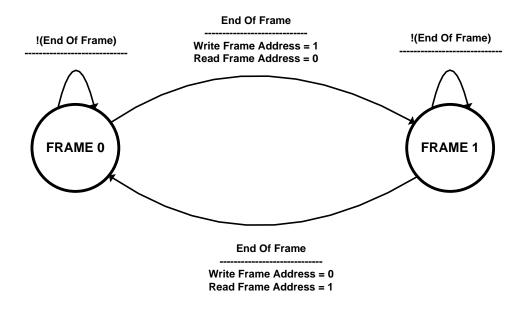

| Figure 3.15: Double Buffer State Machine                             | 84 |

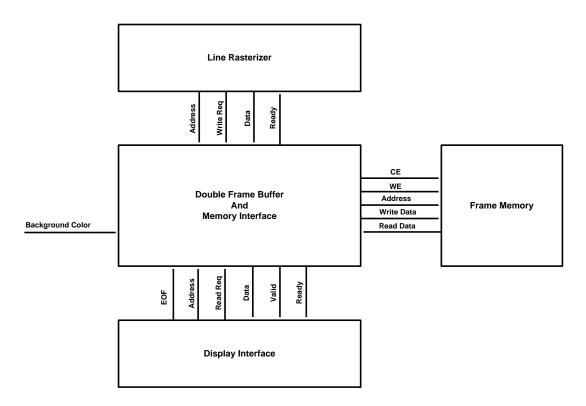

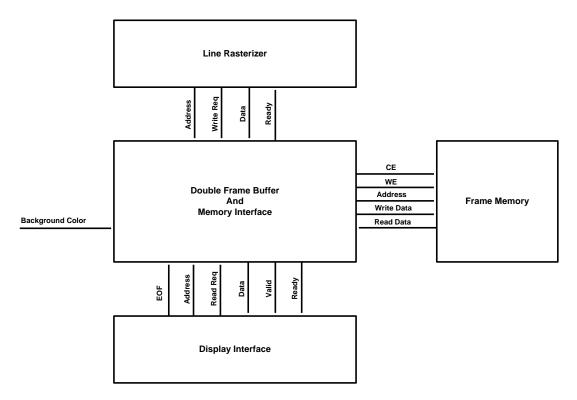

| Figure 3.16: Frame Buffer Interface with Frame Memory                | 85 |

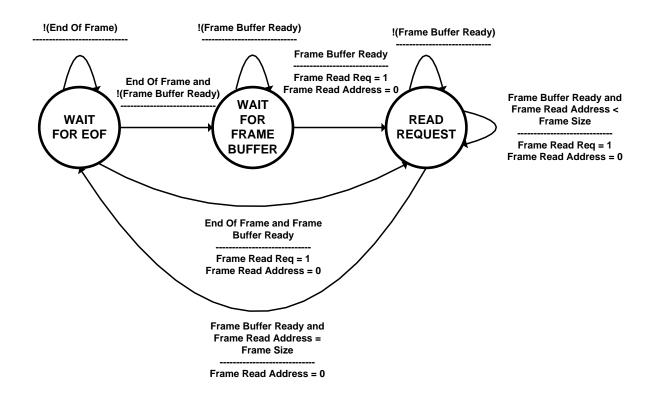

| Figure 3.17: Frame Reading State Machine                             | 86 |

| Figure 3.18: GPU Top Level Block Diagram                             | 87 |

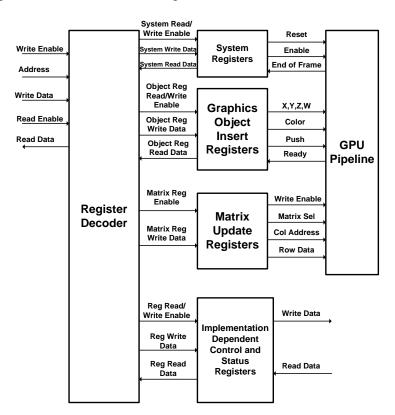

| Figure 3.19: GPU Control Registers                                   | 89 |

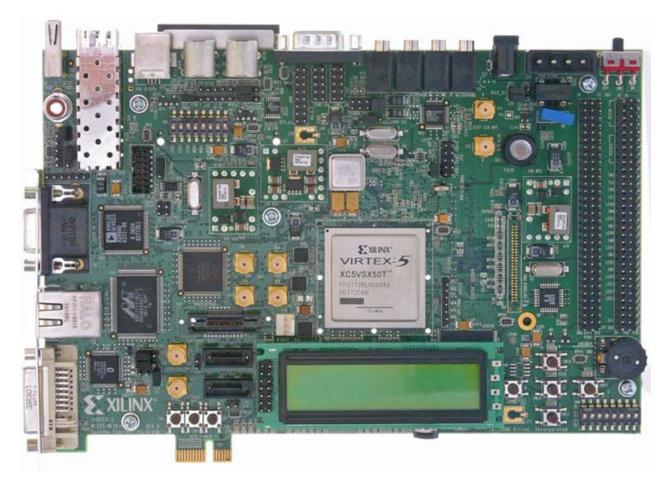

| Figure 4.1: ML506 Development Board (13)                             | 93 |

| Figure 4.2: GPU Top Level Design                                     | 94 |

| Figure 4.3: GPU Top Level Implementation Block Diagram               | 95 |

| Figure 4.4 : IEEE 754-1985 32 Bit Floating Point Number              | 97 |

| Figure 4.5 : Custom 18 Bit Floating Point Number                     | 97 |

| Figure 4.6: Xilinx Coregen Floating Point Operation Selection Window | 98 |

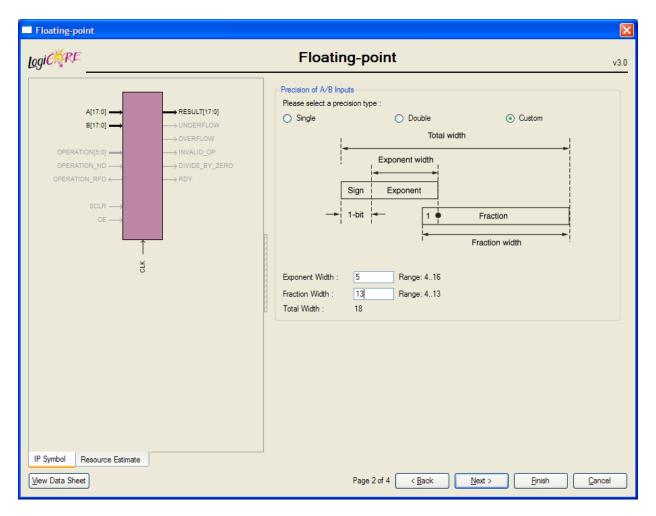

| Figure 4.7: Floating Point Precision Selection Window                      | 99  |

|----------------------------------------------------------------------------|-----|

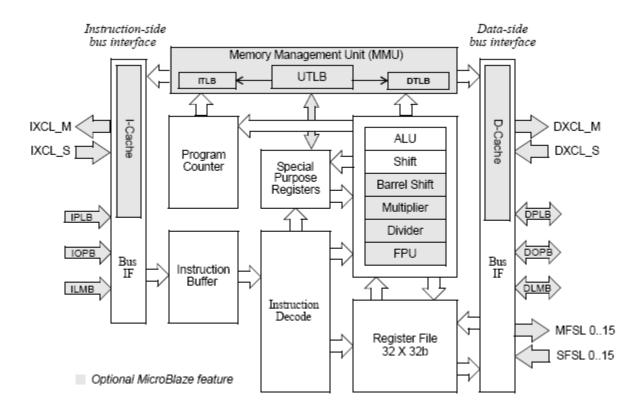

| Figure 4.8: Microblaze Core Block Diagram(17)                              | 101 |

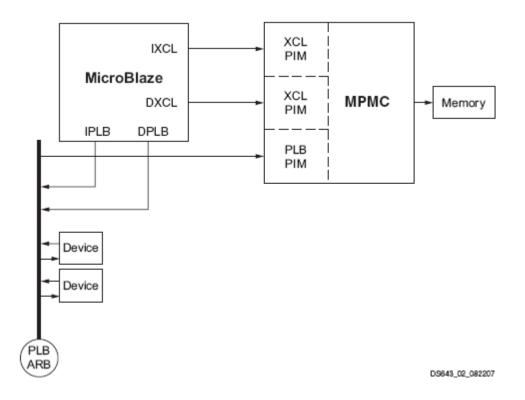

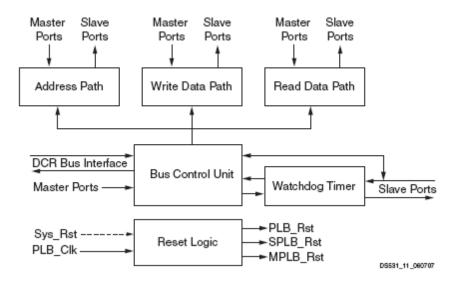

| Figure 4.9: Multi-port Memory Interface Layout (18).                       | 103 |

| Figure 4.10: PLB Block Diagram (19)                                        | 104 |

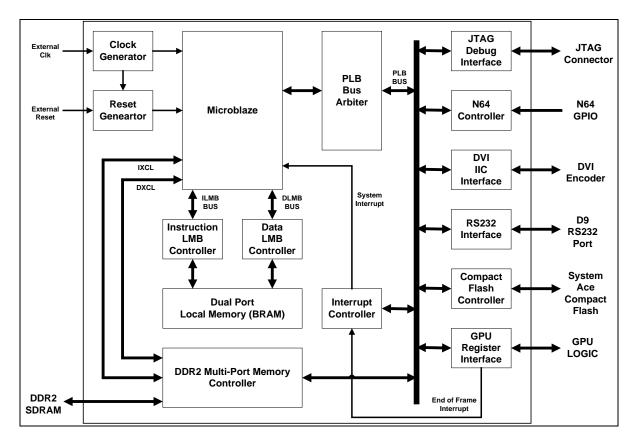

| Figure 4.11: Microblaze System                                             | 105 |

| Figure 4.12: Xilinx Platform Studio's Project Opener                       | 106 |

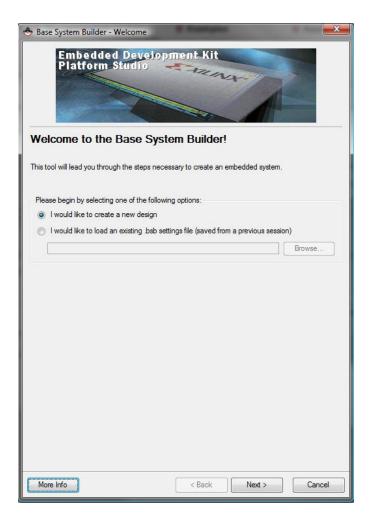

| Figure 4.13: Base System Builder Welcome Window                            | 107 |

| Figure 4.14: Base System Builder Board Selector                            | 108 |

| Figure 4.15: Base System Builder Processor Selector                        | 109 |

| Figure 4.16: Base System Builder Microblaze Processor Configuration Window | 110 |

| Figure 4.17: Base System Builder IO Interfaces Configuration Windows       | 111 |

| Figure 4.18: Base System Builder Cache Setup Window                        | 112 |

| Figure 4.19: Base System Builder Software Setup Window                     | 113 |

| Figure 4.20: Base System Builder System Created Window                     | 114 |

| Figure 4.21: Original Base System without Custom Peripherals.              | 115 |

| Figure 4.22: Peripheral Creation Window.                                   | 116 |

| Figure 4.23: N64 Controller(20)                                            | 117 |

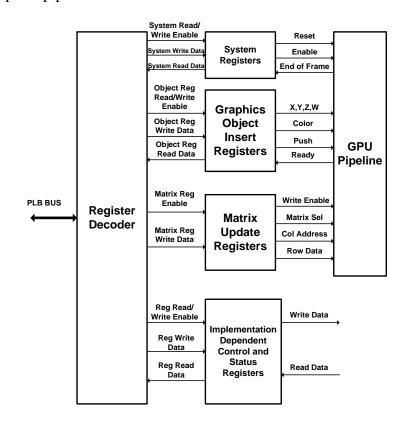

| Figure 4.24: GPU Pipeline Register PLB Interface                           | 119 |

| Figure 4.25: GPU Pipeline Top Level Implementation.                        | 120 |

| Figure 4.26: Matrix Multiplier Accelerator                                 | 122 |

| Figure 4.27: Cohen Sutherland Clipping Implementation                      | 123 |

| Figure 4.28: Bresenham's Line Rasterizer Design                            | 124 |

| Figure 4.29: Frame Buffer Interface with Frame Memory                      | 125 |

| Figure 4.30: VGA Horizontal Sync Timing.                     |     |

|--------------------------------------------------------------|-----|

| Figure 4.31: VGA Vertical Sync Timing                        | 127 |

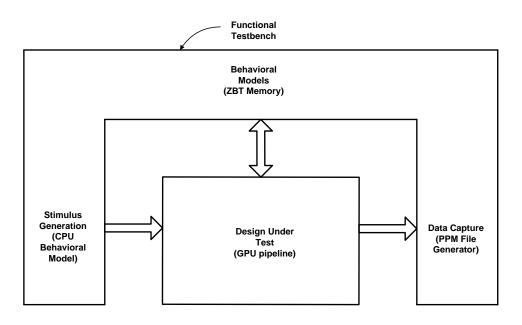

| Figure 4.32: GPU Testbench Block Diagram                     | 129 |

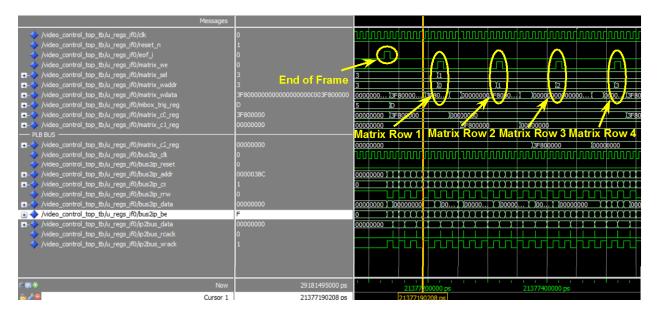

| Figure 4.33: Matrix Programming in Simulation                |     |

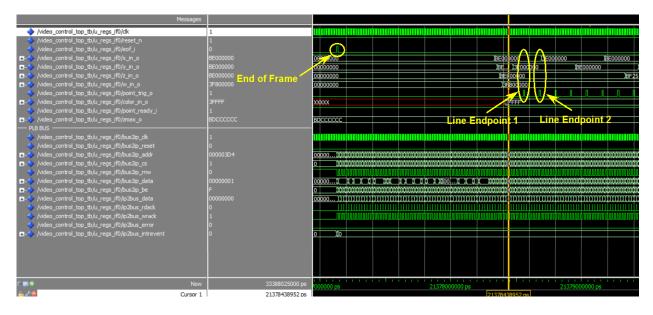

| Figure 4.34: Pushing Line in Simulation                      |     |

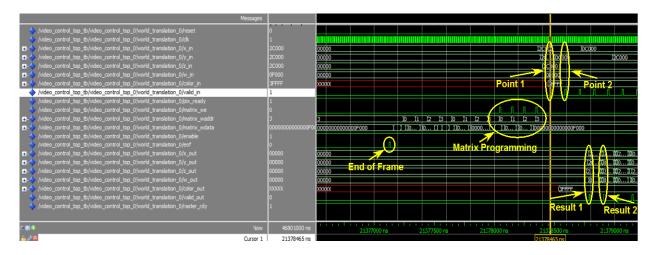

| Figure 4.35: Matrix Multiplication in Simulation             |     |

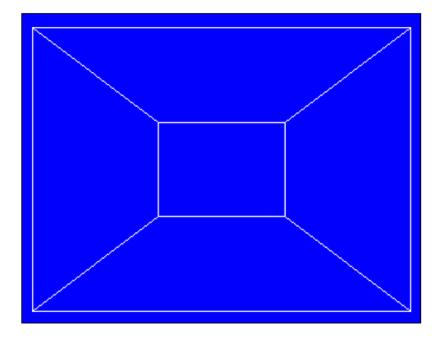

| Figure 4.36: PPM unit cube.                                  |     |

| Figure 4.37: Xilinx's EDK showing processor sub-system       |     |

| Figure 4.38: ISE 3D GPU hierarchy                            |     |

| Figure 4.39: Serial terminal output from test software       |     |

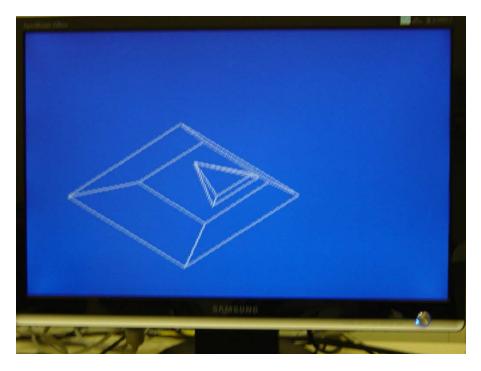

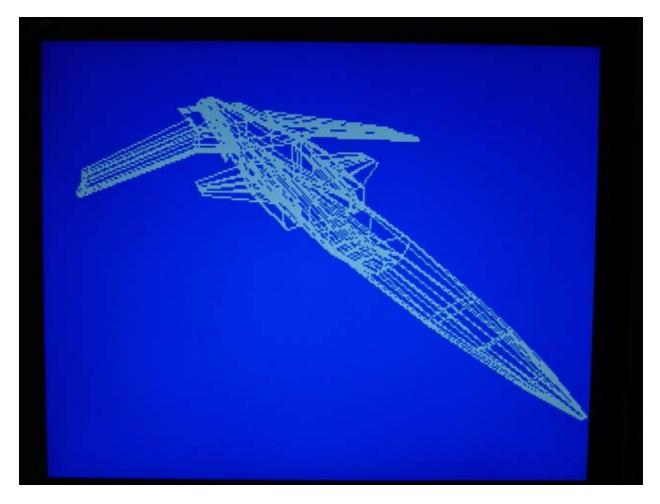

| Figure 4.40: 3D Graphics Processor Output                    | 139 |

| Figure 4.41: 3D Object rotation                              |     |

| Figure 4.42: 3D Object Scaling                               |     |

| Figure 4.43: 3D Objects Translated and clipped.              |     |

| Figure 4.44: Model Plane Rendered using GPU                  |     |

| Figure 4.45: Development Kit with JTAG, VGA and N64 Hardware |     |

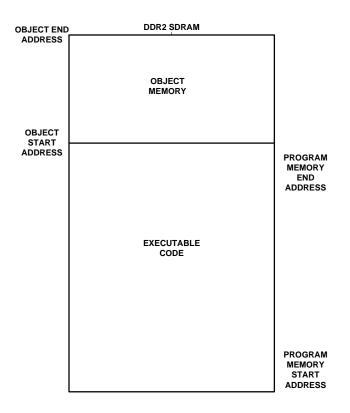

| Figure 5.1: Program Memory and Object Memory Division        |     |

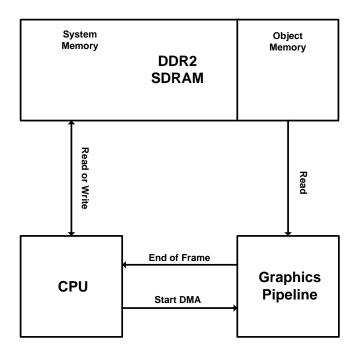

| Figure 5.2: Graphics Pipeline DMA                            | 150 |

| Figure 5.3: Interleaved memory organization                  | 153 |

| Figure 5.4: Contiguous Partitioning                          | 154 |

# LIST OF EQUATIONS

| Equation 2.1: Two Dimensional and Three Dimensional Vectors                          |

|--------------------------------------------------------------------------------------|

| Equation 2.2: Two Dimensional and Three Dimensional Homogenous Vectors               |

| Equation 2.3: Matrix Representation of Translation, Scaling and Rotation of a Vertex |

| Equation 2.4: 3D Translation Transformation Matrix                                   |

| Equation 2.5: 3D Scaling Matrix Transformation (1)                                   |

| Equation 2.6: Z Axis Rotation Transformation Matrix (1)                              |

| Equation 2.7: Y Axis Rotation Transformation Matrix (1)                              |

| Equation 2.8: X Axis Rotation Transformation Matrix (1)                              |

| Equation 2.9: 2D Local to World Coordinate Transformation Matrix                     |

| Equation 2.10: 3D rotation transformation matrix                                     |

| Equation 2.11: 3D Local to World Coordinate Transformation                           |

| Equation 2.12: View Coordinate Transformation                                        |

| Equation 2.13: Similar Triangle Rations with solutions for x and y (7)               |

| Equation 2.14: Perspective Projection Transformation Matrix (1)                      |

| Equation 2.15: Perspective Projection Transformation Matrix (1)                      |

| Equation 2.16: 2D Parametric Equations                                               |

| Equation 2.17: 3D Parametric Equations                                               |

| Equation 2.18: General Screen Transformation Matrix                                  |

| Equation 2.19: General Screen Transformation Matrix        | 51 |

|------------------------------------------------------------|----|

| Equation 2.20: General line equation through two endpoints | 52 |

| Equation 2.21: Line equation solved for y                  | 53 |

| Equation 3.1: Matrix Multiplication(6)                     | 65 |

| Equation 4.1: Floating point calculation                   | 97 |

# PREFACE

I would like to thank Dr. Cain for the opportunity to pursue the project and for all the guidance he has provided through this ordeal. Also, thanks to my committee of Dr. Jones and Dr. Chang for their input and guidance. I would also like to thank my family for all their help and support while working on this project. Lastly, I would like to dedicate this work to my loving wife Marcie whose support was instrumental in my ability to complete this thesis.

#### **1.0 INTRODUCTION**

#### **1.1 OVERVIEW**

Real-time computer graphics hardware designs have massively changed over the years. In early stages of graphics processing, such tasks were delegated to a Central Processing Unit (CPU). CPUs are highly flexible programmable devices that excel at performing sequential tasks. Despite CPUs flexibility and usefulness, they do not do as well at executing tasks which can take advantage of parallelism such as graphic processing. Graphic processing requires many complex mathematical operations to be performed in real-time. In the late 90s and early 2000s demand for more complex graphic processing increased. This has led to custom hardware solutions which take advantage of pipelining and the massive parallelism inherent in graphics processing. Today, these custom hardware solutions are implemented using Application Specific Integrated Circuits or ASICs. Until recently ASIC based graphics processors used fixed pixel pipelines architectures. Today, many modern graphics processors have switched to programmable vertex and pixel processors greatly increasing the graphics processors performance and flexiblity.

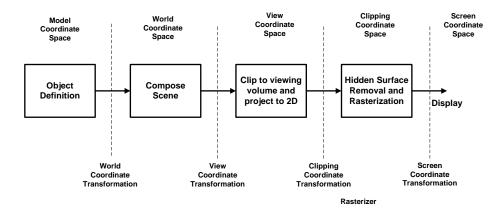

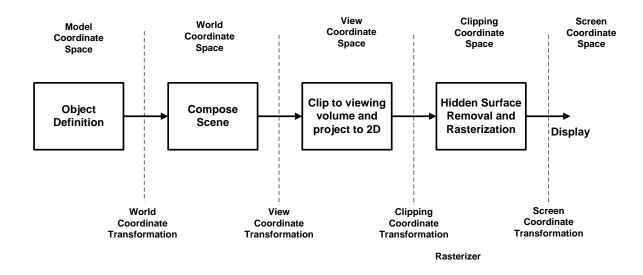

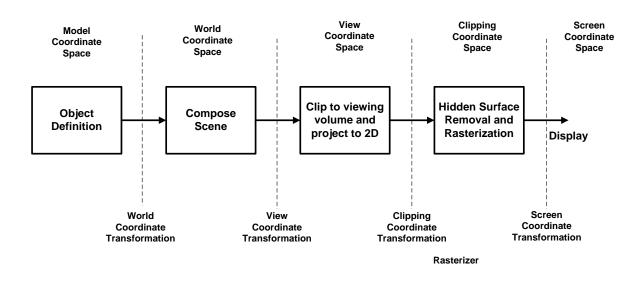

Until this recent change, graphics processing used the more traditional fixed pipeline shown in Figure 1.1.

Figure 1.1: Classic Graphics Pipeline (1)

This pipeline architecture uses dedicated hardware blocks to render a 3D scene. A pipeline such as this operates on three dimensional vertices. Vertices are 3D points which are grouped together to form complex objects. The object definition step in Figure 1.1 is storage space for groups of vertices that form objects. Grappics processors are ofter paired with cental processing units (CPUs). In most systems, graphics objects are stored in CPU memory and then passed to the pipeline by the CPU itself. These objects are then passed to the compose scene block where coordinate transformations and lighting calculations are performed. Coordinate transformations are necessary to place 3D objects into a 3D virtual world. In addition, clipping and projections are necessary to display the 3D virtual world onto a 2D screen. These 3D transformations, 2D projections and other fuctions are discussed in more detail in Section 2.0. Next, in the hidden surface removal and rasterization stage, objects are converted to pixels (called rasterization), shaded, anti-aliased and then textured. Pixels are discrete points of color on a 2D screen and the process of rasterizing 3D objects into pixels will be discussed further in Section 3.0. Lastly, these pixels are stored into the graphic's pipeline's local memory (called the frame buffer) in the hidden surface removal and rasteriazation stage to create a 2D frame of pixel data. This pixel data is then read from the frame buffer and driven to a human display interface.

The graphics pipeline has basically included these same stages for the past two decades with successive improvements over the years. The largest improvements have been finding ways to increase the memory bandwidth of the frame buffer through parallelism and memory interleaving. In addition, improvements have been made by brute force simply by creating many graphics pipelines such as the one above which operate on a 3D scene in parallel.

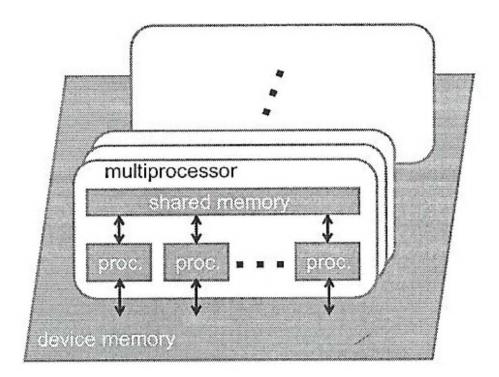

Today, graphics processing is taking a radical new direction. An example of this is the Geforce 8800 GS graphics processor from NVIDA (2). The 8800 uses the Computer Unified Device Architecture (CUDA) which provides a multiprocessor based solution for graphics processing. The architecture is shown in Figure 1.2.

Figure 1.2: GeForce 8800 CUDA Architecture (3)

The CUDA architecture differs from the classic graphics pipeline in that instead of set pipelined hardware blocks, many specialized scalar processors are used. The Geforce 8800 CUDA architecture can perform tens of thousands of threads concurrently. Using the CUDA

architecture, each scalar processor can be tasked with vertex, pixel or geometic calculations to perform any function implemented in the classic pipeline.

The CUDA architecture in Figure 1.2 consists of 16 multiprocessors which each share 768 MB of system memory. Within each of the 16 multiprocessors, there are eight scalar processors which share a local 16 KB cache. In total there are 128 scalar processor (16 multiprocessor \* 8 scalar processors) each running at 1.35 GHz. These scalar processors specialize at executing matrix-vector multiplication efficiently. Matrix-vector multiplication, as will be scene later in Section 2.1.4, is a very common operation in graphics processing. Using architectures such as this, today's graphics processors are capable of rendering very complex 3D worlds in real-time.

Currently, the majority of graphics processing units (GPUs), such as the state of the art Geforce 8800 GS, are designed and implemented as Application Specific Integrated Circuits (ASICs). ASICs can be a good choice because of a GPU's high speed performance requirements. However, ASICs are very expensive to develop and manufacture due the high cost of photomasks as well as the massive up front verification effort needed. It is not uncommon for ASICs to require multiple revisions to iron out all the flaws of a particular design. With the development of each photomask costing in the millions, development cost can escalate quickly.

In contrast, Field Programmable Gate Arrays (FPGAs) are devices that contain programmable logic blocks with a programmable interconnected fabric to connect these various blocks. FPGAs can eliminate many of the problems associated with ASIC design. FPGAs are reconfigurable devices and due to this fact do not require the large scale up front verification of ASICs. In addition, FPGA's reconfigurablity eliminates the expensive photomask cost penalty that ASIC design defects would accrue through design defects. These facts make FPGAs ideal for digital system prototyping.

FPGAs also present a variety of additional advantages. For instance, if an FPGA based design is found to have a design defect in the field, firmware updates allow the defects to be fixed without massive hardware recalls or hardware replacement. In addition, new features can be added based on new customer needs. Lastly, new techniques such as on the fly reconfigurablity enable parts of the FPGA to be reconfigured to implement different functions using the same physical hardware.

Some disadvantages of FPGAs is that they cost more per unit as compared to ASICs (eliminating the upfront ASIC development costs) as well as the fact that ASICs generally outperform FPGAs in terms of performance and density. Despite these disavantages, FPGAs have now begun to bridge the performance gap comming close enough in terms of performance of ASICs to be used in many applications where ASICs were traditionally used. Xilinx, a leading FPGA vendor, has recently released the Virtex 5 SXT device (4). This device is a high density high performance FPGA with 32,640 look up tables, 32,640 registers and a maximum clock speed of 550 MHz. Altera, a competing FPGA vender, offers similar performing products to the Virtex 5.

These FPGA specs, while impressive by FPGA standards, make developing graphics processors that can compete with today's state of the art ASIC based graphics processors, such as the Geforce 8800, impractical. The sheer size of the Geforce 8800 (coming in at 754 million transistors (2)) is very unlikely to be implemented in such a way as to fit into the limited number of logic elements an FPGA provides. Another problem is the clock speeds of the scalar processors, where the Geforce 8800 has its processing cores running at 1.35Ghz, far above what

today's FPGA can achieve. Although the state of the art is currently impractical, many legacy GPU designs have core clock speeds in the 200 to 300 MHz range. GPU such as these also use the classic GPU architecture shown in Figure 1.1. This architecture is simpler to conceptualize due to the fact that each stage is a well defined custom hardware structure as opposed to a fully functional scalar processor as in the Geforce 8800.

Taking the advantages of FPGAs into concideration, an FPGA based graphics processor using the architecture in Figure 1.1 could be used in many applications. For instance, a FPGA based graphics processor could be use in many embedded applications where a fully featured graphics processor is not needed. One such field is image processing. In image processing many autonomous robots use combinations of cameras for visual data and things such as LADAR scanners to acquire 3D depth information. LADAR is an acronym for Laser Radar. This technique uses echoed laser beams as opposed to sound waves to get a 3D information from a surface. FPGAs could be used to implement basic graphics processing logic which could map the camera's 2D visual information to the LADAR's 3D depth information. This could be used by robots to record a very accurate landscape of what it has scene in the past. The beauty of FPGAs is that the image processing logic, graphics processing logic, and other general purpose logic could all be integrated into a single system on a chip FPGA design. These are just some of the possible applications graphics processing using FPGAs.

Another possible application is legacy ASIC based graphics processor replacement. FPGA based graphics processors could be used to replace legacy ASIC graphics processors where the size and perfomace of the legacy device makes it feasible. FPGA designs have the advantage of being field upgradable as well as on the fly reconfigurable providing several advantages over the standard ASIC based legacy graphics processors as well. These legacy graphics processors could also be integrated in system on chip designs where graphics processing as well as other functionality is needed on a single chip.

Lastly, FPGA base graphics processors could be used for a rapid prototyping where certain features of more complex graphics processor could be tested in physical hardware. This approach could minimize risk in many graphics processing designs. Instead of relying only on simulators the hardware architecture could also be tested in real hardware on an FPGA for basic functionality. This could save millions of dollars in GPU ASIC refabrication due to additional bugs found in the FPGA debugging phase possibly preventing several stages of costly chip refabrication. In order to determine if such applications are feasiable in an FPGA first a basic prototype using FPGA technology must be designed and tested.

## **1.2 STATEMENT OF THE PROBLEM**

The overview above discussed the state of the art of graphics processing. Two different architectures used today were discussed, the classic fixed pipeline and the multiprocessor approach. The overview made a case that the fixed graphics pipeline is the most ideal for implementation in an FPGA. In addition, the overview above showed certain applications could take advantage of an FPGAs based graphics processing implementation as opposed to using ASICs for devlopment.

The objective of this thesis is to test the feasibility of implementing complex graphics processing functions on modern FPGA devices. In order to accomplish this, this thesis presents an FPGA based graphics processor design and implementation that establishes the feasibility of a complex set of graphics processing functions. From this FPGA prototype many conclusions can be drawn about the performance, power and cost of an FPGA based GPU.

The FPGA prototype requirements include the features listed below.

- Graphics processing engine capable of rendering in both 2D and 3D.

- Rendering of wireframe objects.

- Support for a free roaming point of view (or camera) in 3D.

- Support standard display interfaces.

The features above constitute a fully functional graphics system. One such feature, the free roaming camera allows for manipulation of objects within a virtual world. These objects can be rotated, scaled or moved within this virtual world. The objects can then be displayed onto a 2D computer display. For this proof of concept design, the objects to be displayed will be wireframe based. Wire frames models are defined only by the edges of a physical object. Some examples of wireframes are shown in Figure 1.3.

Figure 1.3: Wireframe Modeling(1)

Wire frame modeling is conceptually simple to implement compared textured graphics. The advantage of wire frames are the high frame rates they allow due to the small pixel fill rates needed. Using wireframes in conjunction with clipping and hidden surface removal will allow this first pass system to run complex scenes in real time at 60 frames per second. The use of

wire frames will be sufficient for proof of concept while advanced features such as surface texturing, lighting and shading could be implemented with successive additions to the design.

This thesis presents the work peformed to realize an FPGA based graphics processor prototype. This document first must define requirements which are subset of graphics processing functions to be implemented. Once identified and described, the functions must be designed to run efficiently within an FPGA device. Given the design requirements, an FPGA must be selected that has the logic resource and performance to implement these proposed graphics functions. Following implementation, the FPGA based graphics processor must then be fully verified and tested for functional correctness as well as have its area, power and performance measured. From the graphics processor area and performance numbers, various conclusions can be drawn on what graphics processing features are currently possible to implement in today's FPGA devices as well as what advantages an FPGA based designs presents over an ASIC based design.

## 1.3 OUTLINE

The next section, Section 2.0, is an introduction to computer graphics. It gives the reader all the necessary mathematical background information on the features planned for design and implementation in the following sections. In the third section the functional requirements of the prototype as well as how the prototype has been designed to meet these requirements are presented. Section 4.0 shows the detailed implementation, verification and testing of the system presented in Section 3.0. Finally, Section 5.0 gives the conclusions on the performance of the designed graphics processor and shows some ideas for future work.

### 2.0 COMPUTER GRAHPICS RENDERING

Computer graphics rendering is the process of displaying an image on a computer display given a list of geometrically defined objects. These objects can be defined in either twodimensional space (2D) or three-dimensional space (3D). This 2D or 3D space is referred to as a virtual world.

Though virtual world descriptions are three-dimensional, in contrast computer displays are two dimensional. In order to display a three dimensional image on a two dimensional computer display, a two dimensional projection of the three dimensional image is needed. In addition, clipping to the boarders of portions of the world viewable on the screen may be necessary to increase performance. Given this clipped two dimensional description, the virtual world can then be mapped to the computer display.

Today, most computer displays are raster based. Raster graphics (5) are a rectangular grid of points of color (know as pixels) used to display an image. The two dimensional projected objects defined in vector format must be quantized and converted to a raster image. This process is known as rasterization. Rasterization involves determining which pixels in the raster display are affected by each object in the virtual scene. This process involves functions such as line drawing. Rasterization will be discussed later.

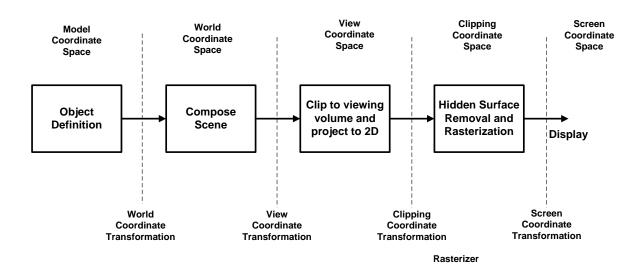

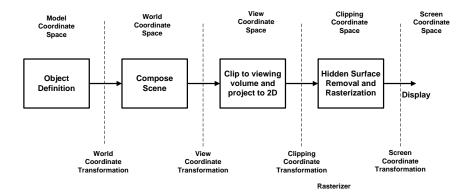

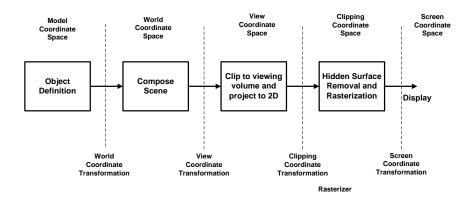

Figure 2.1 shows a high level description of a graphics processing pipeline. In the pipeline, all the consecutive steps needed to display a list of abstract 2D or 3D objects onto a 2D computer display are shown.

Figure 2.1: Computer Graphics Processing Pipeline(1).

As can be seen in the figure above, computer graphics involves converting from one coordinate system to another. Starting at the left, model coordinates are where each object is stored in its own coordinate system. Objects in this coordinates system usually have a control point which is used to move the model around the world coordinate system relative to the control point. The next coordinate system is the world coordinate system. The world coordinate system is the model of the actual 3D or 2D world where various objects defined in model coordinate space can coexist. Next is the view coordinate system. This system can be thought of as the world coordinate system viewed from a single point in space (like a camera). Next follows the clipping space, where the world is constrained into a finite viewing volume and then projected on a 2D plane. Lastly, the screen coordinate system is the rasterized version of the 2D projection. This finial coordinate system corresponds to the physical display and is driven to the display device.

The following section will start with a brief overview of the mathematical principles needed to implement the requirements of the graphics pipeline presented in Section 1.2. This is followed by a detailed discussion of all the steps taken by the graphics pipeline to convert a list of graphics objects to pixels on the screen.

## 2.1 MATHMATICS OVERVIEW

Transformations are tools that can be used to manipulate 2D and 3D objects in a virtual world. They can be used to move an object within the virtual world and project the 3D virtual world onto a 2D plane. This section introduces the notion of a vector as well as how vectors can be grouped together to form graphics objects. These objects can then be transformed using basic 2D and 3D affine geometric transformations discussed here.

### 2.1.1 Homogenous vectors

In computer graphics 2D and 3D objects are defined in respect to a virtual world. This virtual world is nothing more than a mathematical representation of a world's geometry. Objects can be defined in many ways, but are most commonly defined as a group of vertices. These vertices are represented as vectors as shown in Equation 2.1.

$$2D = \begin{bmatrix} x \\ y \end{bmatrix} \qquad 3D = \begin{bmatrix} x \\ y \\ z \end{bmatrix}$$

- -

#### Equation 2.1: Two Dimensional and Three Dimensional Vectors.

The x, y and z value of each vector describes an object's position within a coordinate system Coordinate systems are discussed in Section 2.1.2.

In computer graphics, vertices are often described in homogenous form(6). Homogenous representation can allow affine geometric transformations to be easily represented by a single matrix multiplication. In this representation, coordinates are the same as before except an additional w coordinate is added to the vector as shown in Equation 2.2.

$$2D = \begin{bmatrix} x \\ y \\ w \end{bmatrix} \qquad 3D = \begin{bmatrix} x \\ y \\ z \\ w \end{bmatrix}$$

Equation 2.2: Two Dimensional and Three Dimensional Homogenous Vectors. The need for homogenous vectors will be made apparent in the affine geometric transformation Section 2.1.4.

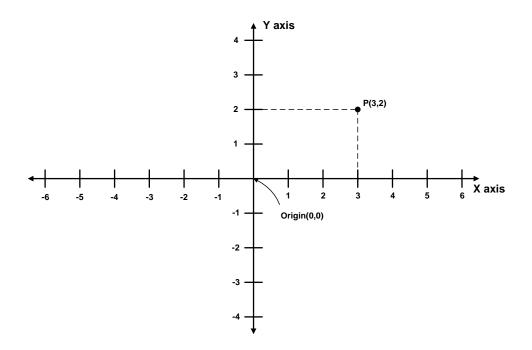

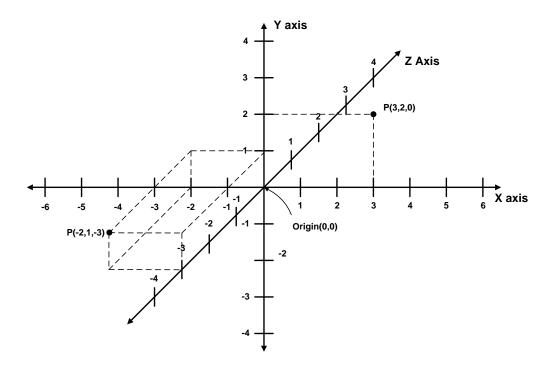

#### 2.1.2 Coordinate System

Coordinate systems are used to define a virtual space in computer graphics. The relative positions of an object as well as its dimensions are all defined within these coordinate systems. 2D and 3D coordinate systems vary by the number of axes each systems has.

For instance, a coordinate system in two dimensions is defined by two axes at right angles to each other forming a xy-plane. A grid on each axis defines uniform distances from center of the coordinate system know as the origin. The basic 2D coordinate system is shown in Figure 2.2

Figure 2.2: 2D Coordinate System

In Figure 2.2 the 2D vector P(3,2) is defined.

The three dimensional Cartesian coordinate system is shown in Figure 2.3.

Figure 2.3: 3D Cartesian Coordinate System

Note that the original vector in the 2D coordinate system of Figure 2.2 is now located at P(3,2,0) where the z coordinate is zero. Another 3D vector at P(-2,1,-3) is also defined in the coordinate system.

Vector objects can be used to describe a group of connected points within a virtual world defined by a coordinate system. These connected points are known as a polygon mesh. These polygon mesh objects can then be moved with ease using affine geometric transformations. Polygon meshes and their use with affine geometric transformations are discussed in the next sub sections.

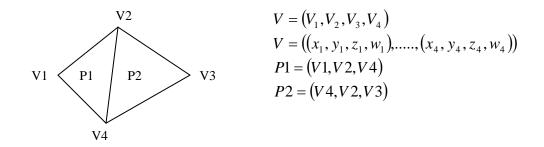

### 2.1.3 Object Representation

Today most commercial graphics processing units use a polygon mesh(7) to represent 2D or 3D objects. A polygon mesh is a collection of vertices joined together to form the polygons of an object. Figure 2.4 below shows and example of a four point object defined as a polygon mesh.  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  define the vertices that make up an object while  $P_1$  and  $P_2$  are the polygons defined by this list of vertices.

#### Figure 2.4: Polygon Mesh Representation(7)

The list of vertices, such as  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  shown in Figure 2.4 can be converted from one coordinate system to another quite easily using a linear transformation matrix. The next section

describes how these objects can be scaled, rotated or translated using affine geometric transformations.

### 2.1.4 Affine Geometric Transformations

Affine geometric transformations can be used to move objects around in a virtual environment, convert between coordinate systems, and implement projections of 3D images on to a 2D plane. This section gives the background on two dimensional and three dimensional affine geometric transformations. An affine transformation is any transformation involving scaling, rotation, or translation from one coordinate system to another.

A set of vectors (or points) which define an object can be transformed into another set of points by an affine geometric transformation. Matrix notation is used in computer graphics to describe an affine geometric transformation. The convention in computer graphics is to have a vector V as a column vector which is multiplied by a transformation matrix.

Using this notation, any vector V can be transformed to a new vector V'. The translation, scaling and rotation transformations calculations are shown below.

$$V' = D + V$$

$$V' = S * V$$

$$V' = R * V$$

#### Equation 2.3: Matrix Representation of Translation, Scaling and Rotation of a Vertex

D is the translation vector and S and R are the scaling and rotation matrices. These three basic operations are the most common in computer graphics and can be combined to perform very complex functions (for example projection of a 3D image onto a 2D plane). The next several sections present each basic transformation individually.

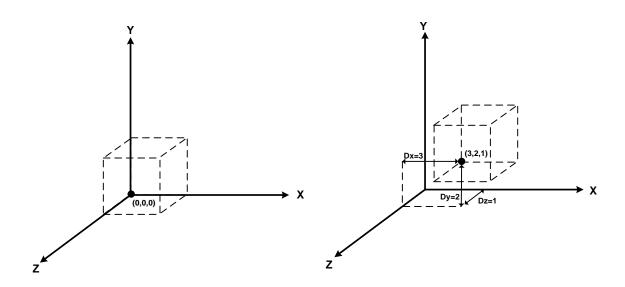

#### **2.1.4.1 Translation Transformation**

Translation is the process of moving vertices from one point in a coordinate system to another by adding a translation amount to each vertex. The algebraic and matrix representation for 3D translation are shown in Equation 2.4 (for 2D removes all z components).

$$V' = D(d_x, d_y, d_z) \cdot V$$

$$\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & d_x \\ 0 & 1 & 0 & d_y \\ 0 & 0 & 1 & d_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} x' = x + d_x \\ y' = y + d_y \\ z' = z + d_z \\ 1 \end{bmatrix}$$

**Equation 2.4: 3D Translation Transformation Matrix**

Note that in Equation 2.3 that the new vector is calculated by using matrix addition while in Equation 2.4 that the new vector uses multiplication. This is where the importance of homogenous coordinates discussed in Section 2.1.1 becomes apparent. Adding the addition homogenous coordinate w=1 allows translation to be expressed as a matrix multiplication instead of a matrix addition. This gives all three operations (scaling, rotation, and translation) a uniform method of calculation. This becomes important in maximizing hardware efficiency both due to the fact that only multiplication is needed and that, as will be shown later, multiple matrix transformations can be multiplied together to be combined into one transformation matrix.

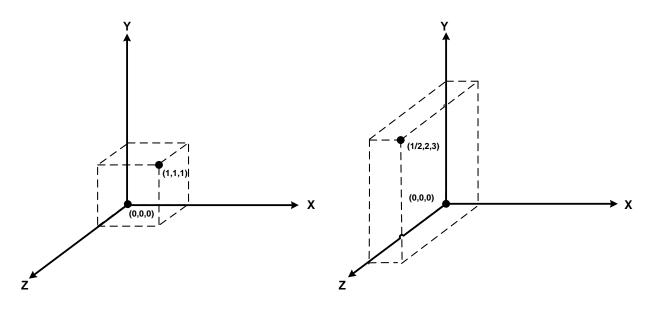

Once again D is the translation matrix and defines the displacement of each component of V. Translation is more concisely explained in Figure 2.5 which shows a cube defined at the origin being moved by the translation values [Dx, Dy, Dz] = [3, 2, 1].

Figure 2.5: Translation of a cube.

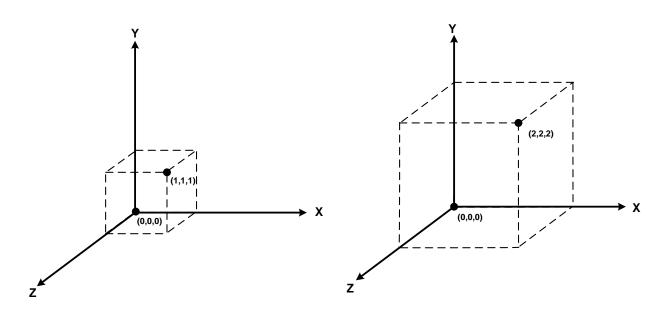

### 2.1.4.2 Scaling Transformation

Scaling is another form of transformation operation. It stretches or compresses vertices within a coordinate system. This is done by multiplying each vector V by scaling factors Sx, Sy, and Sz. The algebraic and matrix representations are shown below (for 2D remove all the z components).

$$V' = S(s_x, s_y, s_z) \cdot V$$

| $\begin{bmatrix} x \end{bmatrix}$ | $\int S_x$ | 0     | 0                    | 0 | $\begin{bmatrix} x \end{bmatrix}$ |   | $\begin{bmatrix} x' = xs_x \end{bmatrix}$ |

|-----------------------------------|------------|-------|----------------------|---|-----------------------------------|---|-------------------------------------------|

| y'                                | 0          | $s_y$ | 0                    | 0 |                                   |   |                                           |

|                                   | 0          | 0     | $\boldsymbol{S}_{z}$ | 0 |                                   | _ | $z' = zs_z$                               |

|                                   | 0          | 0     | 0                    | 1 | 1                                 |   | 1                                         |

#### **Equation 2.5: 3D Scaling Matrix Transformation (1)**

S is the scaling matrix and based on its values the vector V can be either expanded or compressed. This is shown in the example below in Figure 2.6. This particular example shows a cube defined at the origin being scaled by scaling factors [Sx,Sy,Sz] = [2, 2, 2].

Figure 2.6: Scaling of a cube.

Note that above is an example of uniform scaling. Uniform scaling is where Sx=Sy=Sz. If any of the scaling factors Sx, Sy or Sz are not equal the scaling is said to be differential. Differential scaling affects the relative proportions of the object. This can be shown below in Figure 2.7 with the same cube but this time with scaling factors [Sx,Sy,Sz] = [1/2,2,3].

Figure 2.7: Differential Scaling of a cube.

Note that the cube, in difference to the cube scaled by factors [2,2,2], has been stretched more in the Z direction, less in the X direction and the same amount in the Y direction. Differential

scaling is often used when mapping to screen coordinates of a display device that does not have the same number of horizontal and vertical lines. For instance a 640x480 VGA display.

### 2.1.4.3 Rotation Transformation

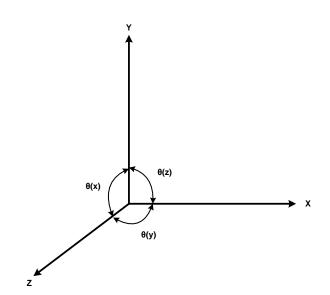

Rotation is revolving a vector around the origin of a coordinate system. This is accomplished by multiplying each vector by a rotation matrix. In three dimensions there are three different angles for which an object can be rotated. Each angle component is show in the Figure 2.8 below.

Figure 2.8: Right Handed Coordinate System with Rotational Angle.

The three transformation matrices below can be used to rotate an object around either the x, y or z axis. These equations are shown below. In each case R represents the rotation matrix and V is the vertex being rotated.

$$V' = R \left(\theta_z\right) \cdot V$$

$$\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} \cos(\theta_z) & -\sin(\theta_z) & 0 & 0 \\ \sin(\theta_z) & \cos(\theta_z) & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} x' = x\cos(\theta_z) - y\sin(\theta_z) \\ y' = x\sin(\theta_z) + y\cos(\theta_z) \\ z' = z \\ 1 \end{bmatrix}$$

Equation 2.6: Z Axis Rotation Transformation Matrix (1)

$$V' = R(\theta_y) \cdot V$$

$$\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} \cos(\theta_{y}) & 0 & \sin(\theta_{y}) & 0 \\ 0 & 1 & 0 & 0 \\ -\sin(\theta_{y}) & 0 & \cos(\theta_{y}) & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} x' = x\cos(\theta_{y}) + z\sin(\theta_{y}) \\ y' = y \\ z' = x\sin(\theta_{y}) - z\cos(\theta_{y}) \\ 1 \end{bmatrix}$$

Equation 2.7: Y Axis Rotation Transformation Matrix (1)

$$V' = R(\theta_x) \cdot V$$

$$\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & \cos(\theta_x) & -\sin(\theta_x) & 0 \\ 0 & \sin(\theta_x) & \cos(\theta_x) & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} x = x \\ y' = y\cos(\theta_x) - z\sin(\theta_x) \\ z' = y\sin(\theta_x) + z\cos(\theta_x) \\ 1 \end{bmatrix}$$

Equation 2.8: X Axis Rotation Transformation Matrix (1)

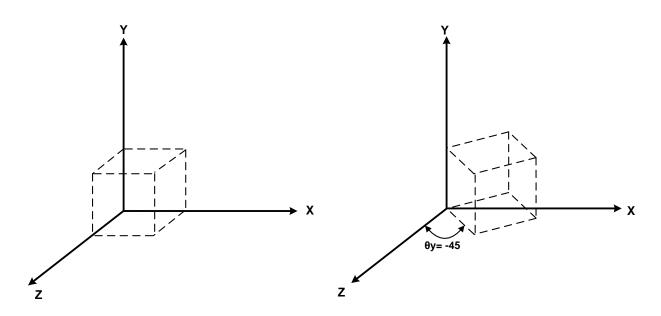

Figure 2.9 shows an example of a cube rotated by  $\theta y = -45$  degrees. Note that both  $\theta x$  and  $\theta z$  can be rotated similarly to the above figure. The next section shows how to compose the various transformations into a single matrix transformation.

Figure 2.9: Rotation of a cube.

# **2.1.4.4 Transformation Compositions**

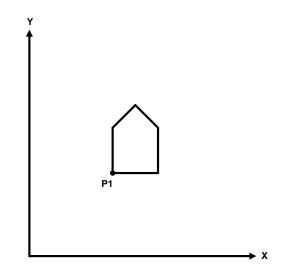

Individual scaling, rotation and translation geometric transformation matrices can be combined to form just about any transformation function that is needed in computer graphics. Though these matrices can be cascaded and multiplied one at a time to achieve the desired result, matrix multiplication is a resource intensive function to implement in hardware. In order to minimize the amount of logic needed to implement a given affine geometric transformation, these matrices can be combined through multiplication to form a single matrix. This multiplication of matrices by one another is known as composition. The above scaling, rotation and translation matrices can be composed together by simple multiplication of the matrices. The main reasoning behind composing transformation matrices is to gain efficiency by applying single transformation matrices to vertices instead of applying a series of transformations. An example of this is the transforming of an object in its local coordinate system, to an object in the world coordinate system. In order to illustrate this consider the 2D object in Figure 2.10 below with a reference point on the house defined by the point P1.

Figure 2.10: Object Centered on P1

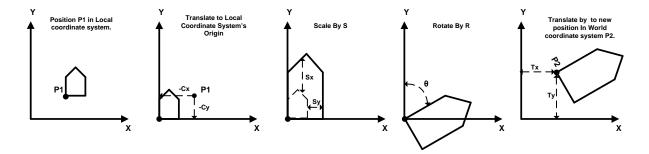

Converting an object from object coordinates to world coordinates can involve translation, scaling, and rotation. In order to properly scale and rotate an object, first the object's reference point must be aligned to the origin of the object coordinate system. Next, the object is transformed through a scaling matrix S. Rotation can follow by transforming the resulting scaled coordinates through the rotation matrix R. Lastly, the scaled, rotated object can be translated to its position in the world coordinate system by a translation matrix T. The sequence is shown in Figure 2.11 below.

Figure 2.11: Local to World Coordinate Translation.

To do the following matrix transformation from local to world coordinates requires four matrix transformations (translation to center, scaling, rotation and translation to world coordinate

position). In order to be more efficient, these four translation matrices can be composed into a single matrix by simple multiplying the four matrices together. This process is shown in Equation 2.9 below where M is the resulting composed matrix.

$$M = D(t_x, t_y) \cdot R(\theta) \cdot S(s_x, s_y) \cdot D(-c_x, -c_y)$$

$$M = \begin{bmatrix} 1 & 0 & t_x \\ 0 & 1 & t_y \\ 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} \cos(\theta) & -\sin(\theta) & 0 \\ \sin(\theta) & \cos(\theta) & 0 \\ 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} s_x & 0 & 0 \\ 0 & s_y & 0 \\ 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 & -c_x \\ 0 & 1 & -c_y \\ 0 & 0 & 1 \end{bmatrix}$$

$$M = \begin{bmatrix} s_x \cos(\theta) & -s_y \sin(\theta) & t_x - c_x s_x \cos(\theta) + c_y s_y \sin(\theta) \\ s_x \sin(\theta) & s_y \cos(\theta) & t_y - c_y s_y \sin(\theta) - c_y s_y \cos(\theta) \\ 0 & 0 & 1 \end{bmatrix}$$

Equation 2.9: 2D Local to World Coordinate Transformation Matrix

Similarly, a matrix for 3D local to world coordinate transformation matrix can be composed. 3D involves three discrete angles as shown previously in Figure 2.8. In order to create the composed matrix for transforming from object coordinates to world coordinates, first the three rotation matrices must be composed as shown below.

$$R(\theta) = \begin{bmatrix} \cos(\theta_z) & -\sin(\theta_z) & 0 & 0\\ \sin(\theta_z) & \cos(\theta_z) & 0 & 0\\ 0 & 0 & 1 & 0\\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 & 0 & 0\\ \cos(\theta_x) & -\sin(\theta_x) & 0 & 0\\ \sin(\theta_x) & \cos(\theta_x) & 1 & 0\\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} \cos(\theta_y) & \sin(\theta_y) & 0 & 0\\ 0 & 1 & 0 & 0\\ -\sin(\theta_x) & \cos(\theta_x) & 1 & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$$R(\theta) = \begin{bmatrix} -\sin(\theta_z)\sin(\theta_x)\sin(\theta_y) + \cos(\theta_z)\cos(\theta_z) & -\sin(\theta_z)\cos(\theta_x) & \sin(\theta_z)\sin(\theta_z)\cos(\theta_y) + \cos(\theta_z)\sin(\theta_y) & 0\\ \cos(\theta_z)\sin(\theta_x)\sin(\theta_y) + \cos(\theta_z)\cos(\theta_y) & \cos(\theta_z)\cos(\theta_x) & -\cos(\theta_z)\sin(\theta_x)\cos(\theta_y) + \sin(\theta_z)\sin(\theta_y) & 0\\ -\sin(\theta_z)\cos(\theta_x) & \sin(\theta_x) & \cos(\theta_x) & \cos(\theta_x) & \cos(\theta_x)\cos(\theta_y) + \sin(\theta_z)\sin(\theta_y) & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$$R(\theta) = \begin{bmatrix} r_{00} & r_{01} & r_{02} & 0\\ r_{10} & r_{11} & r_{12} & 0\\ r_{20} & r_{21} & r_{22} & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$R(\theta) = R(\theta_z) \cdot R(\theta_x) \cdot R(\theta_y)$

#### **Equation 2.10: 3D rotation transformation matrix.**

In the last step in Equation 2.10 the complex elements of the R matrix composed of sine and cosine are referenced by the values  $r_{row,col}$ . This rotation will be used in all calculations using  $R(\theta)$  in future calculations in this thesis. Taking the result for the 3D rotational transformation R and multiplying it by the center translation, scaling, and world translation yield the overall result shown below in Equation 2.11.

$$\begin{split} M &= T\left(t_x, t_y, t_z\right) \cdot R(\theta) \cdot S\left(s_x, s_y, s_z\right) \cdot T\left(-c_x, -c_y, -c_z\right) \\ M &= \begin{bmatrix} 1 & 0 & 0 & t_x \\ 0 & 1 & 0 & t_y \\ 0 & 0 & 1 & t_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} r_{00} & r_{01} & r_{02} & 0 \\ r_{10} & r_{11} & r_{12} & 0 \\ r_{20} & r_{21} & r_{22} & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} s_x & 0 & 0 & 0 \\ 0 & s_y & 0 & 0 \\ 0 & 0 & s_z & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 & 0 & -c_x \\ 0 & 1 & 0 & -c_y \\ 0 & 0 & 1 & -c_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \\ M &= \begin{bmatrix} s_x r_{00} & s_y r_{01} & s_z r_{02} & -c_x s_x r_{00} - c_y s_y r_{01} - c_z s_z r_{02} + t_x \\ s_x r_{10} & s_y r_{11} & s_z r_{12} & -c_x s_x r_{10} - c_y s_y r_{11} - c_z s_z r_{12} + t_y \\ s_x r_{20} & s_y r_{21} & s_z r_{22} & -c_x s_x r_{20} - c_y s_y r_{21} - c_z s_z r_{22} + t_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \end{split}$$

# Equation 2.11: 3D Local to World Coordinate Transformation

The two matrices defined in Equation 2.9 and Equation 2.11 can be used to transform any arbitrary point in 2D or 3D respectively from one coordinate system to another. The next sections use the affine geometric transformations discussed here to transfer objects to different coordinate systems.

# 2.2 THE GRAPHICS PIPELINE

Recall the graphics pipeline shown again in Figure 2.12 below.

Figure 2.12: Example Graphics Pipeline(1)

In a graphics pipeline, objects are stored in a suitable format that allows easy execution of affine geometric transformations. The polygon meshes discussed in Section 2.1.3, are one such modeling technique that allows objects to be converted to different coordinate systems quite easily. Using these mesh models, it will be shown that objects can be converted to a variety of coordinate systems for processing in the graphics pipeline. The end result of the pipeline being a two-dimensional projected image on a raster display. The rest of this section goes through each stage of the graphics pipeline and explains all the operations that take place in each stage.

# 2.2.1 Object Definition

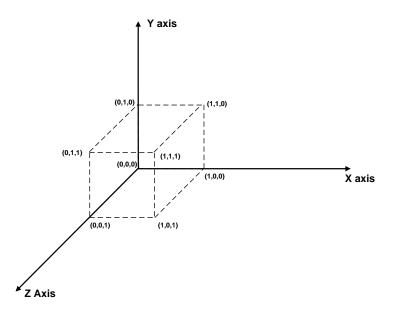

In the object definition stage of the graphics pipeline, polygon mesh objects are each stored in their own local coordinate system (also known as model coordinates). Figure 2.13 shows an example of a unit cube defined in the model coordinate system. Note that one of its corners is lined up around at object coordinates origin. This origin is known as the object's control point. All scaling, rotation and translation of this object will be done centered around that point.

Figure 2.13: Cube in Object Coordinates

Given objects such as these, a geometric transformation can be used to convert objects in model coordinates to the world coordinate system. To make this transformation, each object is associated with scaling, rotation and translation factors. These factors are the same as the S, R and T matrices defined in Equation 2.9 and Equation 2.11. Using these equations a 2D or 3D object in model coordinates can be placed with any position or orientation within the world coordinate system.

# 2.2.2 Scene Composition using World Coordinate Transformation

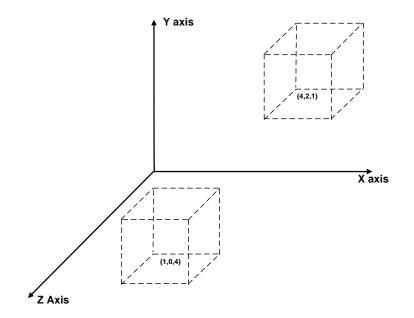

Objects modeled in their own independent model coordinate system can then be placed in the world coordinate system by a simple geometric transformation. The world coordinate system represents each objects relative position to one another in the virtual world. Figure 2.14 below shows two unit cubes modeled from their model coordinate description in Figure 2.13 placed in world space at coordinates (4,2,1) and (1,0,4).

Figure 2.14: Cubes in World Space Coordinates

The geometric transformation for converting an object from model coordinates to world coordinates is identical to the matrix transformations in Equation 2.9 and Equation 2.11 for 2D and 3D objects respectively.

In this stage of the pipeline, objects can be animated by varying the translation, scaling and rotation values in the world transformation matrix. Varying over time will give the viewer a sense of an object moving on the screen. In this stage, lighting and shading can be implemented if desired. These features will not be discussed here because the requirements for this design only necessitate wireframe graphics where lighting and shading are not necessary.

# 2.2.3 View Coordinates and the View Transformation

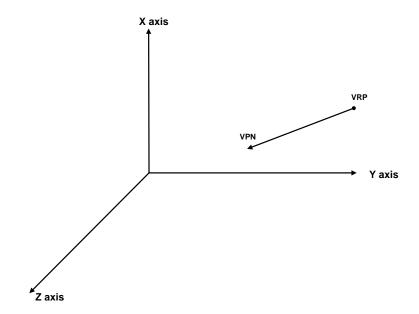

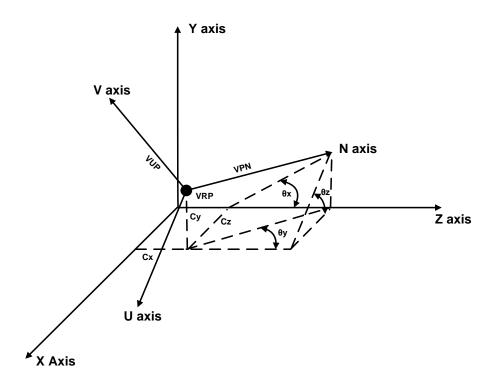

In computer graphics, viewing coordinates or the viewing coordinate system can be conceptualized as a camera pointed in a defined direction. The camera is positioned at a point within the world coordinate system called the viewing reference point (VRP) and is given a direction called the view plane normal (VPN). Figure 2.15 below shows the system in world coordinates.

Figure 2.15: Viewing Point with Viewing Direction in World Coordinates

Using the VRP and VPN, the world coordinates can be transformed to viewing coordinates. The necessity for view coordinates is that certain operations, such as clipping, are more conveniently implemented in the view space.

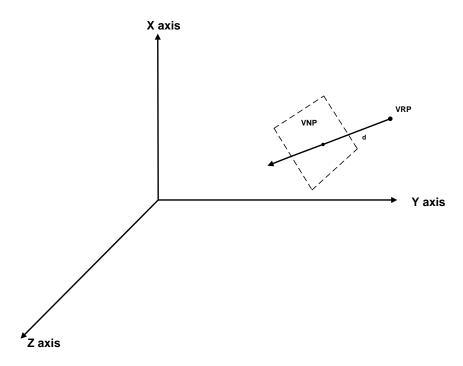

At a minimum, a viewing system must have the following features. First a viewing system must have a vector which establishes the viewer position and direction within the world

coordinate system. This has already been defined in Figure 2.15 as the view reference point (VRP) and view plane normal (VPN) vector. Second, a view normal plane (VNP) must be defined a distance (d) from the VRP. This is shown in the Figure 2.16 below:

Figure 2.16: Viewing plane

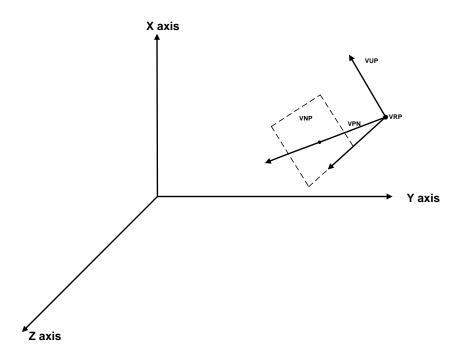

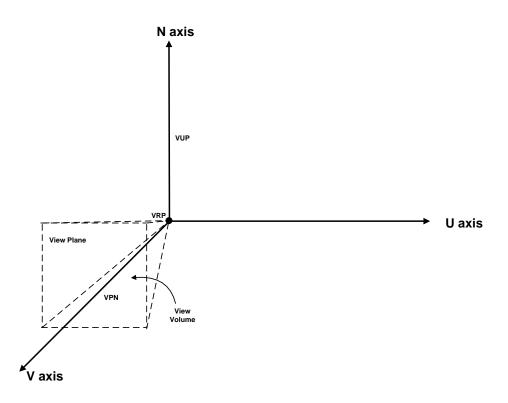

The viewing plane is used to project the 2D image of the 3D scene. Third, using the VRP and VNP and a perpendicular vector to the VPN, the view up vector (VUP), a view coordinate system with a center at the VRP and normal to VNP is defined. This is shown below in Figure 2.17.

Figure 2.17: View coordinate system.

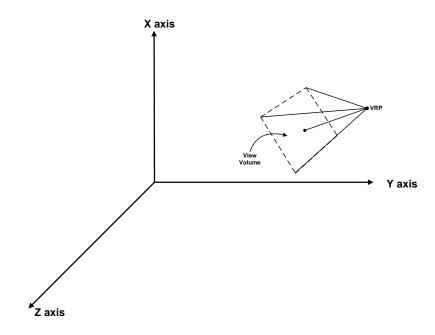

Lastly, the VRP and VNP combine together to form a view volume. This volume will be used in clipping objects outside the field of view. As will be shown later, the viewing volume has well defined planer intersection equations that makes clipping more convenient and justifies the use of view coordinates. The view volume is shown in Figure 2.18.

Figure 2.18: View Volume

Using this viewing system, the view reference point can be positioned anywhere in the world coordinate system and pointed in any direction.

Now that the notion of the viewing coordinate system has been explained, the affine geometric transformation used to convert from world coordinate space to view space will be presented. To do the conversion, a composition of two matrices is required. The first transformation matrix is a translation matrix and is used to move the view reference point in the world coordinate system to the origin of the view coordinate system. Second a rotational transformation matrix is used to align the view plane normal with the z axis of the view coordinate system. The composed transformation matrix is shown below:

$$M = R(\theta_z, \theta_x, \theta_y) \cdot T(-c_x, -c_y, -c_z)$$

$$M = \begin{bmatrix} r_{00} & r_{01} & r_{02} & 0 \\ r_{10} & r_{11} & r_{12} & 0 \\ r_{20} & r_{21} & r_{22} & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 & 0 & -c_x \\ 0 & 1 & 0 & -c_y \\ 0 & 0 & 1 & -c_z \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$$M = \begin{bmatrix} r_{00} & r_{01} & r_{02} & -c_x r_{00} - c_y r_{01} - c_z r_{02} \\ r_{10} & r_{11} & r_{12} & -c_x r_{10} - c_y r_{11} - c_z r_{12} \\ r_{20} & r_{21} & r_{22} & -c_x r_{20} - c_y r_{21} - c_z r_{22} \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

#### **Equation 2.12: View Coordinate Transformation**

Note that the rotational matrix  $R(\theta z, \theta x, \theta y)$  elements are substitutions for the mixed cosine/sine functions in Equation 2.10. This matrix can be used to move objects to the new view coordinate system defined by axes (U,V,N) shown in Figure 2.19. The figure shows this new coordinate system with respect to the world coordinate system before the transformation.

Figure 2.19: Viewing coordinate system defined with World coordinate system.

The result of the transformation has the VRP at the origin, the VPN going straight down the Z axis and the VUP perpendicular to the VPN. The resulting view coordinate system (U,V,N) is shown below:

Figure 2.20: Viewing Coordinate System

Now that the viewing coordinate system and view volume have been defined, the scene can be clipped against the view volume and projected onto the view plane.

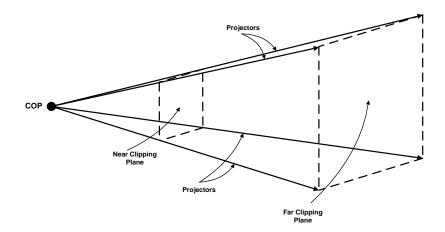

Projection takes the 3D view and projects it onto a 2D projection plane, much like a movie projector and a projection screen. There are two forms of projection, parallel and perspective. Both projection types have a center of projection (COP), but the projection type is determined by whether the projectors are parallel or join together to form a single point. Both parallel and perspective projections are detailed below.

# 2.2.4 3D Projections and the Clipping Transformation

The next coordinate space in the graphics pipeline shown in **Error! Reference source not found.** is called the clipping coordinate space. It is called this because this is the space where all clipping against the view volume will take place. This space exists because it both simplifies the clipping process and projects a 3D image to a 2D plane. The clipping process is discussed in the next sub-section while 3D projections are discussed here.

Figure 2.21: Example Graphics Pipeline(6)

The complexity of viewing 3D objects comes from the fact that the objects are described in three dimensions while a computer screen is only two dimensions. To deal with this mismatch between the three dimensional world and the two dimensional screen, the concept of projections are used. A projection is the process of reducing the number of dimensions for a given geometric object. This section details what projections are as well as how to project a 3D environment to a 2D screen.

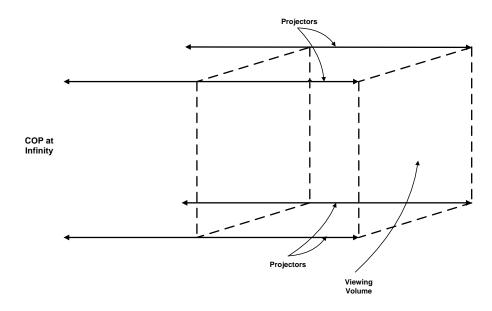

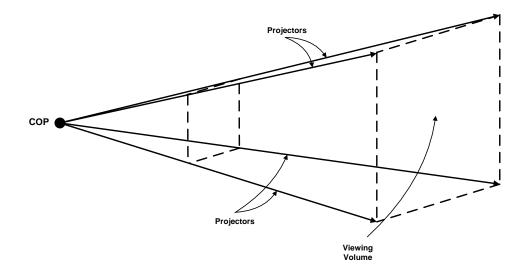

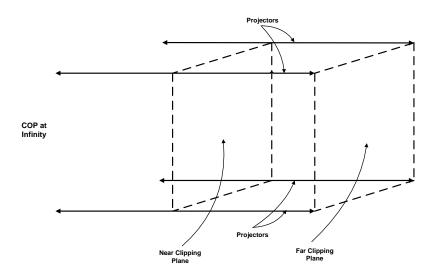

The types of projections that are dealt with here are planar geometric projections meaning that the objects are projected onto a flat plane as opposed to a curved surface. By projecting onto a flat plane, the equations needed to perform the projection can be greatly simplified. There are two types of planar geometric projections dealt with here, parallel and perspective. Parallel projections have a center of projection (COP) with a distance of infinity from the projection plane known as the far clipping plane. In parallel projection, the projectors (lines that intersect with the COP) are all parallel with each other, hence the name parallel projection. This forms a cubic viewing volume that is shown in the Figure 2.22.

**Figure 2.22: Parallel Projection**

Perspective in contrast has a finite distance between the center of projection and the projection plane. All of the projectors in perspective projection intersect at the COP and extend outward to the projection plane. This forms a cut off pyramid viewing volume which is shown below.

**Figure 2.23: Perspective Projection**

The difference between these projection types as well as what they are used for is discussed below. This sub-section goes into more detail on the projection types and their differences and presents the transformation matrices necessary to convert from view coordinates to clipping coordinates for each projection.

### 2.2.4.1 Perspective Projection

Perspective projections are similar to that of how the human eye perceives the world. This effect is known as perspective foreshortening whereby the size of an object varies inversely with distance that the object is from the center of projection. These projections while useful for making realistic looking scenes are not useful for engineering applications which require measuring the size and length of object in 3D (this is where parallel projections come into play).

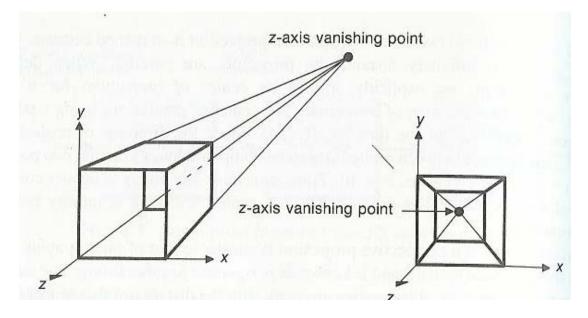

Figure 2.24 below shows a single point perspective projection from two different views.

Figure 2.24: Perspective Projection (7)

In a perspective projection, a set of parallel lines, such as the ones in the cube shown above, converge at a point in infinity. This point is known as the vanishing point which just so happens to be the same point as the center of projection (COP). In general, parallel lines in perspective projections only meet at infinity. If the parallel lines are parallel to the z-axis this vanishing point is known as the principle vanishing point. The figure above has a single principle vanishing point, and hence is known as a single point perspective projection.

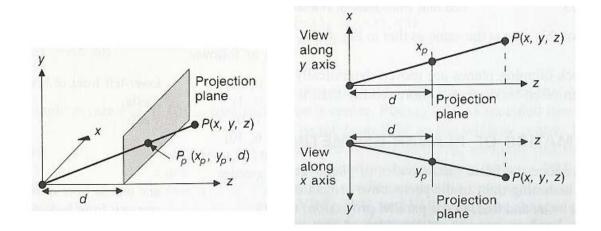

Figure 2.25 shows how a perspective projection point is derived. P(x,y,z) defined in the view coordinate system is to be projected onto the projection plane a distance d from the center of projection which is normal to the z axis. Point  $P_p$  is the projection of this point on the projection plane. The projected point  $P_p$  is a two dimensional vector projection plane. The mathematics for perspective single point planar geometric projections can be made fairly simple by making a few assumptions. First it is assumed that the projection plane is located at distance defined by d shown in Figure 2.25. It is also assumed that the center of projection is located at the origin of the viewing coordinate system. In the figure below the center of projection is at the origin of the coordinate system and the projection plane is parallel with the z axis.

Figure 2.25: Perspective Projection (7)

The object of perspective projections is to find the point  $P_p$ , which is the point where point P intersects the projection plane. In order to find this point, the ratio of similar triangles can be used. These ratios and the solutions for  $x_p$  and  $y_p$  are shown below.

$$\frac{x_p}{d} = \frac{x}{z} \qquad \frac{y_p}{d} = \frac{y}{z}$$

$$x_p = \frac{d \cdot x}{z} = \frac{x}{z/d} \qquad y_p = \frac{d \cdot y}{z} = \frac{y}{z/d}$$

#### Equation 2.13: Similar Triangle Rations with solutions for x and y (7).

Just think of the distance d as a scale factor while the z axis causes a closer object to appear larger and further object to appear smaller. The similar triangle equations in Equation 2.13 can be expressed as a single transformation matrix:

$$M = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1/d & 0 \end{bmatrix}$$

**Equation 2.14: Perspective Projection Transformation Matrix (1)**

### 2.2.4.2 Parallel Projection

Parallel projections in contrast to perspective projections do not mimic the human visual system. Object's sizes in a parallel projection do not vary with depth but instead stay constant. Parallel projections are useful for engineering applications which require measuring the size and length of object in 3D.

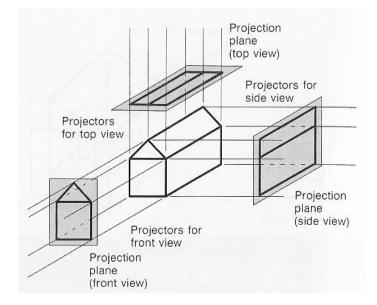

Figure 2.26 displays an example of a parallel projection.

Figure 2.26: Parallel Projection (8)

It can be seen in Figure 2.26 that all the relative lengths of all the sides of the house are preserved. This type of projection is very useful for cad tools and engineering schematics where relative lengths and widths are important.

The parallel projection transformation matrix is fairly trivial. Since the center of projection is at infinity, the distance from the projection plane is also infinity yielding the matrix below.

$$M = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

#### **Equation 2.15: Perspective Projection Transformation Matrix (1)**

This matrix simply throws out all the z components in an object.

Using these projection techniques, an object can be converted from 3D coordinates to 2D coordinates. Before projection is done, the pipeline clips the objects to the view volume. From

here the clipping coordinates can be mapped to the screen coordinates in a process known as rasterization. An explanation of clipping is given in the next section.

### 2.2.5 Clipping

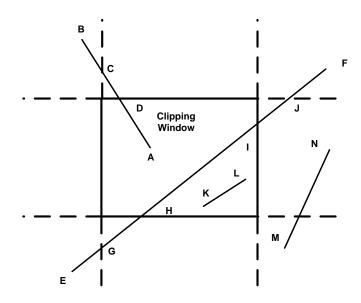

Clipping is the process of removing the parts of a scene that are outside the viewing volume defined in Section 2.2.4. Clipping is important because it filters all non-viewable objects from the graphics pipeline thus increasing performance of the overall system. Many clipping algorithms exist to perform these operations. Since we are dealing with wireframes only, the algorithm dealt with here is the Cohen-Sutherland line clipping algorithm (8). Cohen-Sutherland clips a given line to a rectangular window in 2D or to a cubic or conic volume in 3D.

The key to this algorithm is the initial tests that are performed on each line. First, endpoints are checked for trivial acceptance (the line lies completely in the clipping window or volume). If the object cannot be trivially accepted the object is checked if it can be trivially rejected (the line lies completely outside the clipping window). If a line segment can neither be trivially accepted or rejected then it must be divided into two lines at the edge of the clipping window or volume. These new lines are than checked for trivial acceptance or rejections. If the new lines are not either trivially accepted or rejected the process continues until one line is trivially accepted and the other is trivially rejected. The following sections give a detailed explanation of Cohen-Sutherland clipping in both 2D and 3D.

### 2.2.5.1 Cohen-Sutherland Two Dimensional Clipping

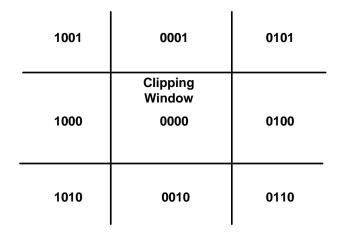

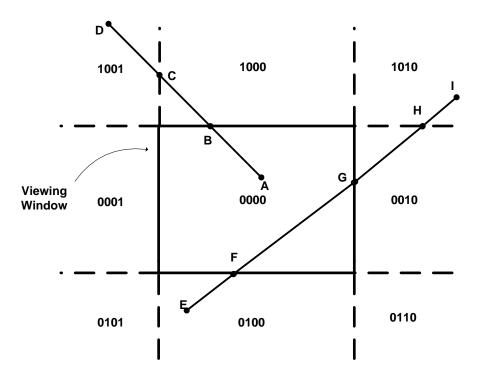

In a 2D graphics pipeline the Cohen-Sutherland clips a line against a rectangular window. The algorithm divides a 2D space into 9 separate regions. These regions are used to determine if a line can be trivially accepted, trivially rejected or if the line needs clipped. The regions are shown in Figure 2.27.

Figure 2.27: Clipping Region Definitions.

From the figure above it can be scene that the nine regions can be defined as a four bit outcode. A four bit outcode is defined for each point of a given line. The outcode bit assignment is shown in the table below.

| Table 2.1: 2D | Outcode | Assignment | Table |

|---------------|---------|------------|-------|

|---------------|---------|------------|-------|

| Bit Number | Location of End Point    | Conditional                               |

|------------|--------------------------|-------------------------------------------|

| First Bit  | Above Clipping Window    | if $y > y_{max}$ then set bit to 1 else 0 |

| Second Bit | Below Clipping Window    | if $y < y_{min}$ then set bit to 1 else 0 |

| Third Bit  | Right of Clipping Window | if $x > x_{max}$ then set bit to 1 else 0 |

| Fourth Bit | Left of Clipping Window  | if $x < x_{min}$ then set bit to 1 else 0 |

For example, given a general line defined by  $p_0 = (x_0, y_0)$  and  $p_1 = (x_1, y_1)$  the algorithm can be defined in these steps.

- 1. Compute the outcodes called  $OC_0$  and  $OC_1$  for both points  $p_0$  and  $p_1$ .

- 2. If  $OC_0$  bitwise  $OR OC_1 = 0000$  then the line is trivially accepted and the line is passed to the next stage of the pipeline.

- 3. If  $OC_0$  bitwise AND  $OC_1 = 0000$  then the line is trivially rejected and the line is dropped and not passed to the next stage of the pipeline.

4. Otherwise, then the line's non visible portion must be clipped.

Step 4 requires the intersection points with the clipping window to be calculated. Parametric equations can be used to calculate the intersection of a line by introducing a new dimension (t). These new parametric line equations can be used to determine the intersection points with each side of the clipping window. The equations are shown below.

$$x = x_0 + t(x_1 - x_0)$$

y = y\_0 + t(y\_1 - y\_0)

#### **Equation 2.16: 2D Parametric Equations**