# COMPILER TECHNIQUES FOR EFFICIENT COMMUNICATIONS IN MULTIPROCESSOR SYSTEMS

by

## Shuyi Shao

B.E. Computer Science and Engineering, Xi'an Jiaotong University, P.R.China, 1996M.S. Computer Science, University of Pittsburgh, 2007

Submitted to the Graduate Faculty of

Arts of Sciences in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

# UNIVERSITY OF PITTSBURGH FACULTY OF ARTS AND SCIENCES

This dissertation was presented

by

### Shuyi Shao

It was defended on

December 6, 2010

and approved by

Rami Melhem, PhD, Professor, Department of Computer Science

Alex K. Jones, PhD, Associate Professor, Department of Electrical and Computer Engineering

Sangyeun Cho, PhD, Associate Professor, Department of Computer Science

Youtao Zhang, PhD, Assistant Professor, Department of Computer Science

Dissertation Co-advisors: Rami Melhem, Professor, Department of Computer Science

Alex K. Jones, Associate Professor, Department of Electrical and Computer Engineering

Copyright © by Shuyi Shao 2010

# COMPILER TECHNIQUES FOR EFFICIENT COMMUNICATIONS IN MULTIPROCESSOR SYSTEMS

Shuyi Shao, PhD

University of Pittsburgh, 2010

Technical advances have brought circuit switching back to the stage of interconnection network design for high performance computing. Although circuit switching has long connection establishment delays and the dedication of connections prevents other communicating nodes from sharing the network, it has simple control logic and significant cost advantage over packet or wormhole switching. With the proper assistance from compilers, circuit switching has the potential of providing significant performance benefits when connections can be established prior to the actual communication.

This dissertation presents a novel compilation framework for achieving efficient communications in circuit switching interconnection networks. The goal of the framework is to identify communication patterns in Single-Program-Multiple-Data (SPMD) parallel applications and compile these patterns as network configuration directives. This can significantly reduce the communication overhead on circuit switching interconnection networks.

A powerful representation scheme is developed in this research to capture the property of communication patterns and allow manipulation of these patterns. Based on the temporal and spatial localities of communications and the capability of the compiler to identify the communication patterns, we classify communication patterns into three categories – *static*, *persistent*, and *dynamic*. We target static and persistent communications, which are dominant in most parallel applications. To identify communication patterns, we develop a novel symbolic

expression analysis. We develop certain compiler techniques for analyzing communication patterns. Since the underlying network capacity is limited, we develop an algorithm to partition the program into phases based on the communication requirements and network capacity.

To demonstrate the effectiveness of our framework, we implement an experimental compiler. The compiler identifies the communication patterns from the source code, partitions the program into phases, and inserts the network configuration directives at phase boundaries to achieve efficient communications. The compiler also can generate communication traces, which provides useful information about the communication pattern correlated to the structure of the source code. We develop a multiprocessor system simulator to evaluate our techniques. Our simulation-based performance analysis demonstrates that using our compiler techniques can achieve the same level, or even better level of communication performance than fast packet switching networks while using much less expensive circuit switches.

# TABLE OF CONTENTS

| AC  | KNO | WLEDG        | MENTS                                          | XIV   |

|-----|-----|--------------|------------------------------------------------|-------|

| 1.0 |     | INTRO        | DUCTION                                        | 1     |

|     | 1.1 | M            | OTIVATION AND BACKGROUND                       | 1     |

|     |     | 1.1.1        | Switching Techniques in Multiprocessor Systems | 3     |

|     |     | 1.1.2        | Communication Locality and Analyzability       | 6     |

|     | 1.2 | O            | VERVIEW OF THIS RESEARCH                       | 7     |

|     | 1.3 | OI           | RGNIZATION OF THIS DISSERTION                  | 11    |

| 2.0 |     | RELAT        | TED WORK                                       | 12    |

|     | 2.1 | CO           | OMMUNICATION CHARACTERISTICS ANALYSIS          | 12    |

|     | 2.2 | CO           | OMPILER TECHNIQUES FOR OPTIMIZING COMMUNICA    | TIONS |

|     |     | ••••         |                                                | 15    |

|     | 2.3 | SI           | MULATIONS OF MULTIPROCESSOR SYSTEMS            | 19    |

| 3.0 |     | OVERA        | ALL DESIGN OF THE COMPILATION FRAMEWORK        | 21    |

|     | 3.1 | $\mathbf{M}$ | ACHINE AND PROGRAMMING MODEL                   | 21    |

|     | 3.2 | CO           | OMPONENTS OF THE COMPILATION FRAMEWORK         | 23    |

|     |     | 3.2.1        | Communication Detection Component              | 25    |

|     |     | 3.2.2        | Communication Analysis Component               | 26    |

|     |     | 3.2.3        | Communication Compiling Component              | 27    |

|     |     | 3.2.4 | Trace Generation Component                                    | 8 |

|-----|-----|-------|---------------------------------------------------------------|---|

|     | 3.3 | US    | SES OF THE COMPILATION FRAMEWORK28                            | 8 |

| 4.0 |     | COMM  | IUNICATION PATTERN                                            | 0 |

|     | 4.1 | C     | OMMUNICATION PATTERN CLASSIFICATION 30                        | 0 |

|     | 4.2 | C     | OMMUNICATION PATTERN REPRESENTATION 33                        | 3 |

|     | 4.3 | C     | DMMUNICAITONS IN NAS BENCHMARKS 39                            | 9 |

| 5.0 |     | SYMBO | OLIC EXPRESION ANALYSIS 42                                    | 2 |

|     | 5.1 | CO    | ONTROL AND DATA FLOW GRAPH43                                  | 3 |

|     | 5.2 | CO    | ONDITIONAL CONTROL FLOW40                                     | 6 |

|     | 5.3 | TI    | RAVERSAL ALGORITHM49                                          | 9 |

|     | 5.4 | Gl    | ENERATING SYMBOLIC EXPRESSIONS FOR LOOPS 55                   | 5 |

|     |     | 5.4.1 | Static Loop Analysis 55                                       | 5 |

|     | 5.5 | CO    | OMMUNICATOR AND RANK 58                                       | 8 |

|     | 5.6 | st    | JMMARY AND DISCUSSIONS 59                                     | 9 |

| 6.0 |     | COMN  | IUNICATION PHASE PARTITION60                                  | 0 |

|     | 6.1 | PF    | HASE MANIPULATIONS60                                          | 0 |

|     | 6.2 | PH    | HASE PARTITION ALGORITHM 67                                   | 7 |

|     |     | 6.2.1 | FilterUntilFit Operation7                                     | 1 |

|     | 6.3 | CA    | ASE STUDY73                                                   | 3 |

| 7.0 |     | RUNTI | ME SCHEDULING 85                                              | 5 |

|     | 7.1 | RU    | UNTIME SYSTEM AND NETWORK SCHEDULING85                        | 5 |

|     | 7.2 | CO    | OMPILER ASISTED RUNTIME SCHEDULING89                          | 9 |

|     |     | 7.2.1 | Establishment of Compiler Identified Network Configuration 89 | 9 |

|     |     | 7.2   | 2.1.1 Synchronized Network Configuration Preloading   | 90  |

|-----|-----|-------|-------------------------------------------------------|-----|

|     |     | 7.2   | 2.1.2 Unsynchronized Network Configuration Preloading | 91  |

|     |     | 7.2.2 | Heuristic Hints at Loop Boundaries                    | 92  |

|     | 7.3 | SU    | J <b>MMARY</b>                                        | 94  |

| 8.0 |     | IMPLE | EMENTATION OF THE FRAMEWORK AND SIMULATOR             | 95  |

|     | 8.1 | IN    | IPLEMENTATION OF EXPERIMENTAL COMPILER                | 95  |

|     |     | 8.1.1 | Communication Detection Pass                          | 97  |

|     |     | 8.1.2 | Communication Analysis Pass                           | 98  |

|     |     | 8.1.3 | Communication Compiling Pass                          | 99  |

|     |     | 8.1.4 | Tracing Generation Pass                               | 100 |

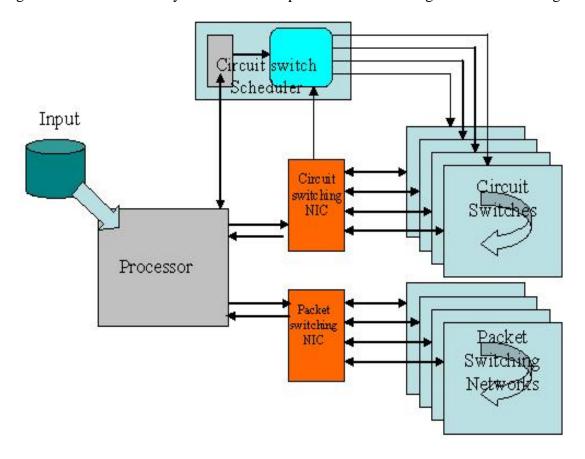

|     | 8.2 | IN    | IPLEMENTAION OF MULTIPROCESSOR SIMULATOR              | 101 |

|     |     | 8.2.1 | Processing Elements                                   | 103 |

|     |     | 8.2.2 | Packet Switching Networks                             | 107 |

|     |     | 8.2.3 | Circuit Switching Networks and Scheduler              | 111 |

|     |     | 8.2.4 | Multiprocessor System Configuration                   | 114 |

| 9.0 |     | EXPER | RIMENTAL RESULTS                                      | 116 |

|     | 9.1 | ID    | DENTIFYING COMMUNICATION PATTERNS                     | 116 |

|     | 9.2 | PF    | ERFORMANCE ANALYSIS                                   | 121 |

|     |     | 9.2.1 | Pure Runtime Scheduling                               | 125 |

|     |     | 9.2.2 | Different Simulated Systems                           | 132 |

|     |     | 9.2.3 | Comparison of RT with SP and FP                       | 136 |

|     |     | 9.2.4 | The Effect of Network Loading Approaches              | 140 |

|     |     | 0.2.5 | The Effect of Phase Partition                         | 144 |

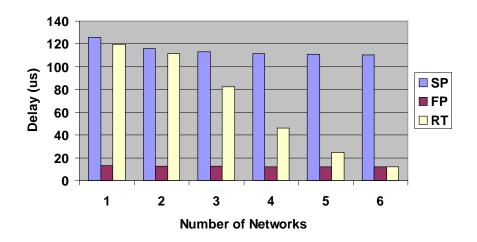

|      |      | 9.2.6 | Comparison of Compiled Communication and FP | 147 |

|------|------|-------|---------------------------------------------|-----|

|      |      | 9.2.7 | Summary                                     | 148 |

| 10.0 |      | CONC  | CLUSIONS                                    | 150 |

|      | 10.1 | N     | MERITS OF THIS RESEARCH                     | 150 |

|      | 10.2 | L     | IMITATIONS OF THIS RESEARCH                 | 152 |

|      | 10.3 | D     | DIRECTIONS FOR FUTURE WORK                  | 153 |

| BIB  | LIO  | GRAPH | HY                                          | 156 |

# LIST OF TABLES

| Table 1. The Communication Pattern of IS                     | 38  |

|--------------------------------------------------------------|-----|

| Table 2. The point-to-point Communications in NAS Benchmarks | 40  |

| Table 3. The Collective Communications in NAS Benchmarks     | 40  |

| Table 4. Simulation Commands                                 | 105 |

| Table 5. Simulation System Parameters and Values             | 124 |

# LIST OF FIGURES

| Figure 1. Veter's MPI Payload Size Distribution                                                | 13 |

|------------------------------------------------------------------------------------------------|----|

| Figure 2. Liang's Adaptive System-on-a-Chip (aSOC) Architecture                                | 16 |

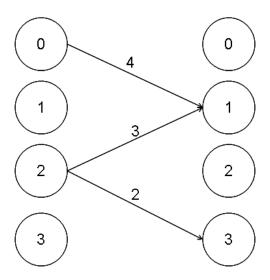

| Figure 3. System Model of Targeted Multiprocessor Systems                                      | 22 |

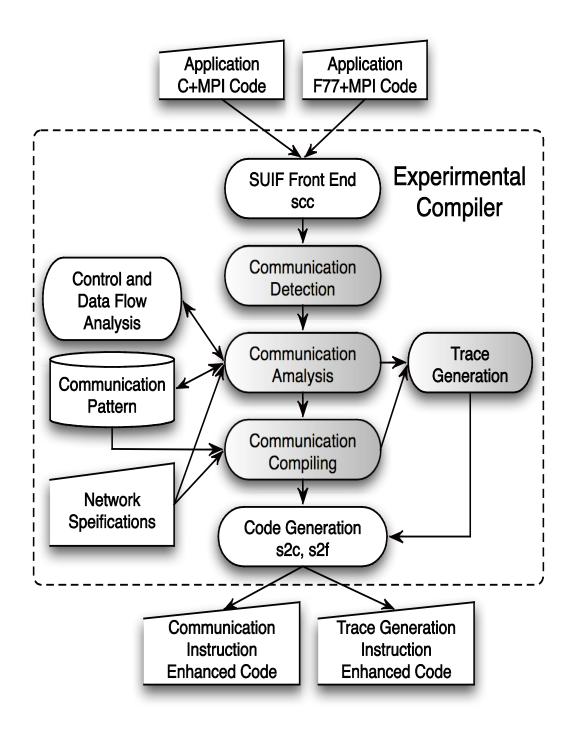

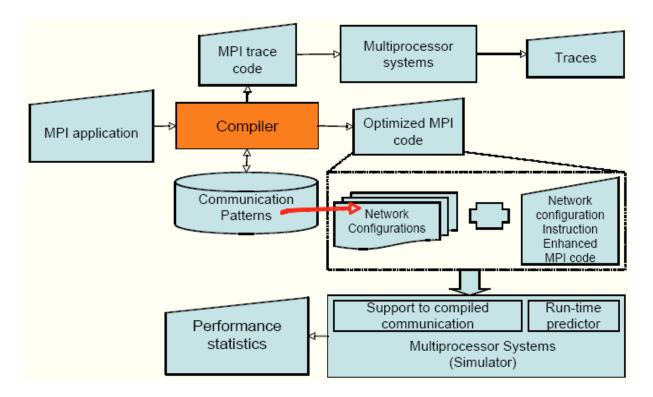

| Figure 4. Overview of the Compilation Framework                                                | 24 |

| Figure 5. Sample MPI Code Segment Where Node 1 Sends a Message to Node 0                       | 25 |

| Figure 6. Static, Persistent and Dynamic Communications                                        | 32 |

| Figure 7. The Grammar for Communication Pattern Representations                                | 36 |

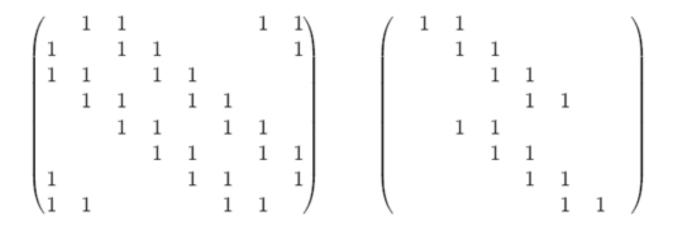

| Figure 8. A Symbolic p-matrix and Its Deterministic Instance Where <i>x</i> =1 and <i>N</i> =4 | 37 |

| Figure 9. p-matrix for IS with 8 Processors                                                    | 38 |

| Figure 10. Code Example for the Demonstration of Symbolic Expression Analysis                  | 42 |

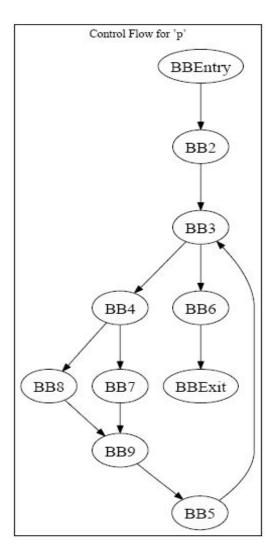

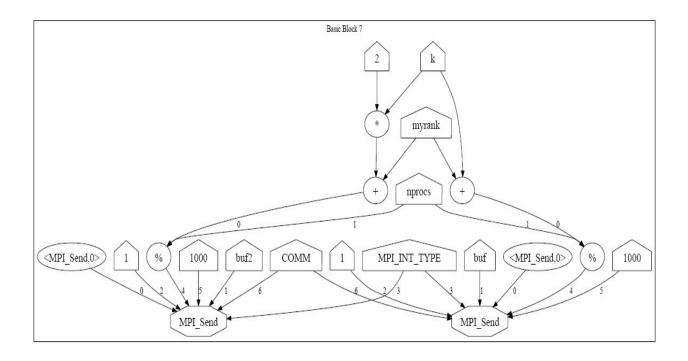

| Figure 11. Control Flow Graph for the Example                                                  | 44 |

| Figure 12. Data Flow Graph for BB7 in the Example                                              | 45 |

| Figure 13. Communication Matrix for the Example                                                | 48 |

| Figure 14. Pseudo Code for Within-DFG Symbolic Analysis                                        | 52 |

| Figure 15. Pseudo Code for CDFG Traversal Algorithm                                            | 54 |

| Figure 16. Phase Partition Algorithm                                                           | 70 |

| Figure 17. A Communication Pattern <i>P</i>                                                    | 71 |

| Figure 18. Edge Coloring Algorithm                                               | 73  |

|----------------------------------------------------------------------------------|-----|

| Figure 19. Code Example for Phase Partition Case Study                           | 74  |

| Figure 20. Runtime Scheduler Circuit Establishment Algorithm                     | 88  |

| Figure 21. Structure of the Experimental Compiler.                               | 96  |

| Figure 22. Paradigm of the Simulated Multiprocessor System                       | 102 |

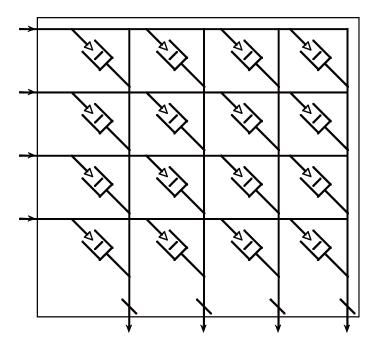

| Figure 23. 4 × 4 Buffered Cross-point Switch                                     | 109 |

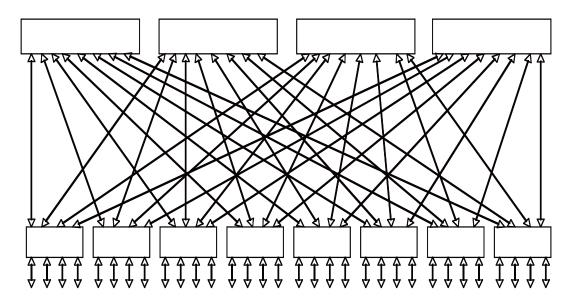

| Figure 24. 32-port 2-stage FAT tree network                                      | 110 |

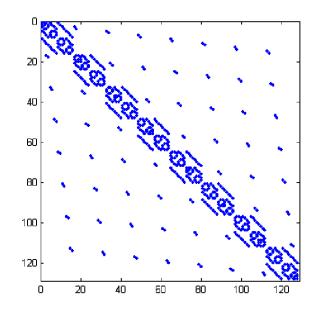

| Figure 25. Single Bit p-matrix PM_LU (N = 16)                                    | 117 |

| Figure 26. The $p$ -matrix of CG (N = 128)                                       | 117 |

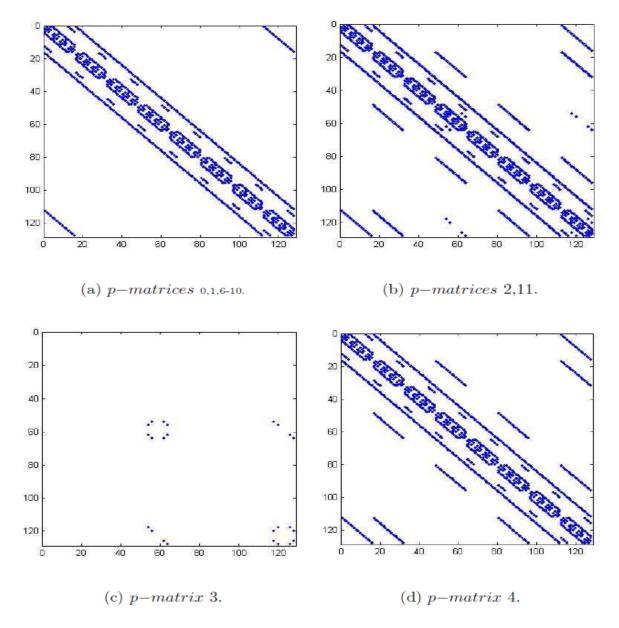

| Figure 27. The <i>p-matrices</i> of MG ( $N = 128$ )                             | 119 |

| Figure 28. LBMHD p-matrix Described by a Formula List Where N = Nx * Ny          | 120 |

| Figure 29. LBMHD p-matrix (N = 64)                                               | 120 |

| Figure 30. Summary of Performance Analysis Methodology                           | 122 |

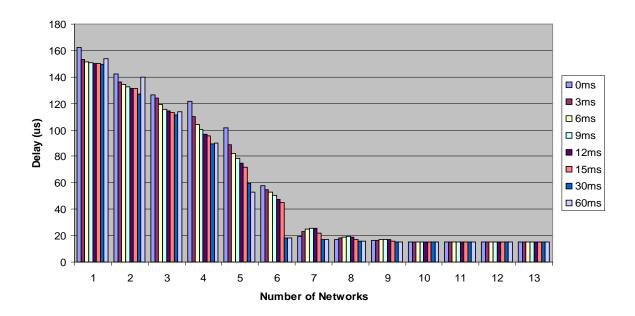

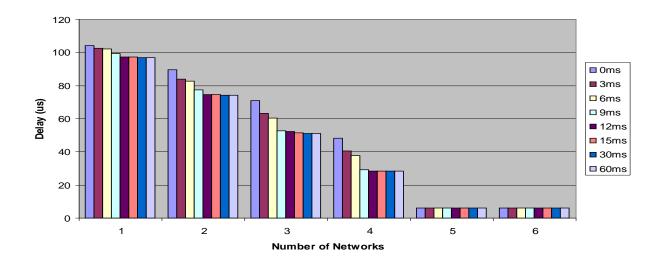

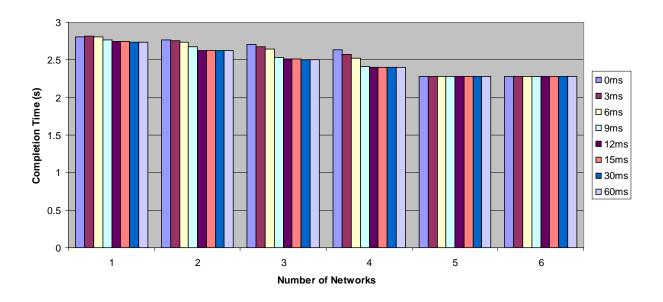

| Figure 31. Message Delay of MG256 with Different Circuit Replacement Threshold   | 126 |

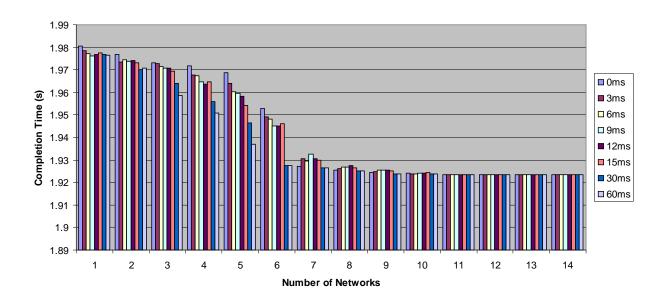

| Figure 32. Completion Time of MG256 with Different Circuit Replacement Threshold | 128 |

| Figure 33. Message Delay of CG256 with Different Circuit Replacement Threshold   | 129 |

| Figure 34. Completion Time of CG256 with Different Circuit Replacement Threshold | 129 |

| Figure 35. Message Delay of SYN256 with Different Circuit Replacement Threshold  | 130 |

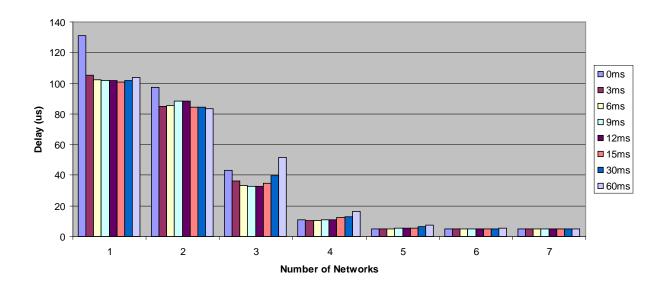

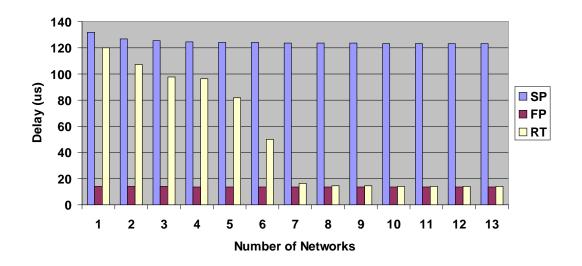

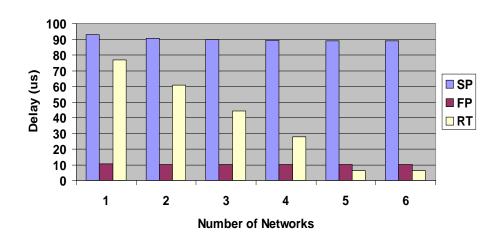

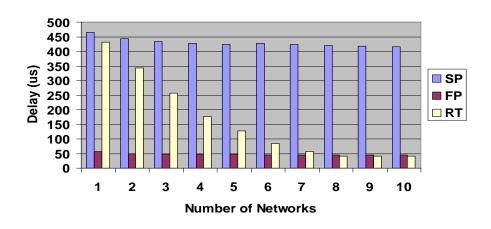

| Figure 36. Message Delay of MG256 in SP, FP, and RT                              | 137 |

| Figure 37. Message Delay of CG256 in SP, FP, and RT                              | 137 |

| Figure 38. Message Delay of SP256 in SP, FP, and RT                              | 137 |

| Figure 39. Message Delay of BT256 in SP, FP, and RT                              | 138 |

| Figure 40. Message Delay of SYN256 in SP, FP, and RT                             | 138 |

| Figure 41. Message Delay of COMOPS256 in SP, FP, and RT    | 138 |

|------------------------------------------------------------|-----|

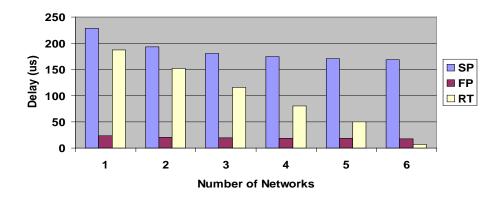

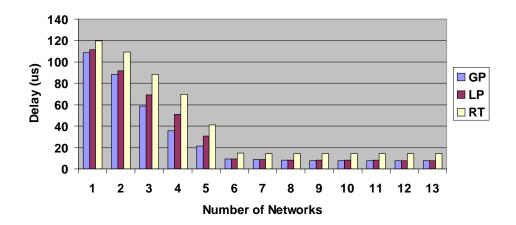

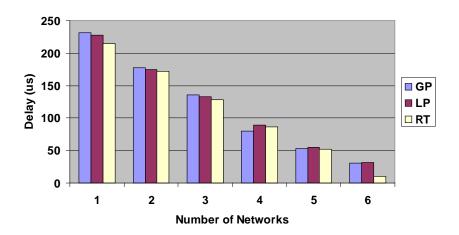

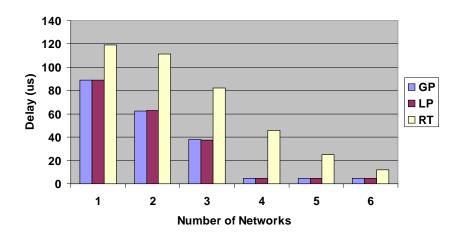

| Figure 42. Message Delay of MG256 in GP, LP, RT            | 142 |

| Figure 43. Message Delay of CG256 in GP, LP, RT            | 142 |

| Figure 44. Message Delay of SP256 in GP, LP, RT            | 142 |

| Figure 45. Message Delay of BT256 in GP, LP, RT            | 143 |

| Figure 46. Message Delay of SYN256 in GP, LP, RT           | 143 |

| Figure 47. Message Delay of COMOPS256 in GP, LP, RT        | 143 |

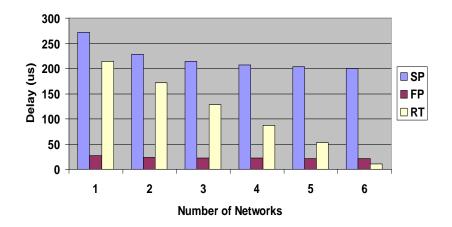

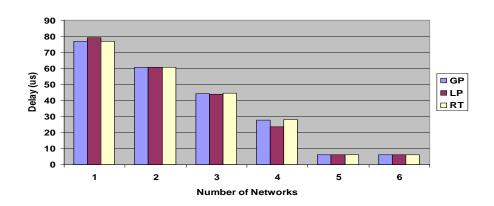

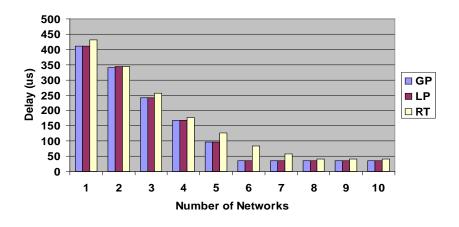

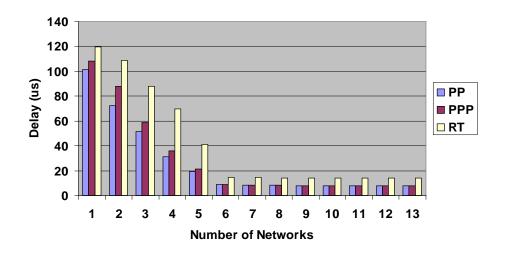

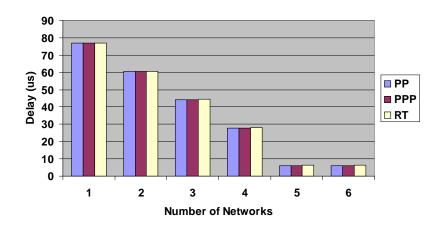

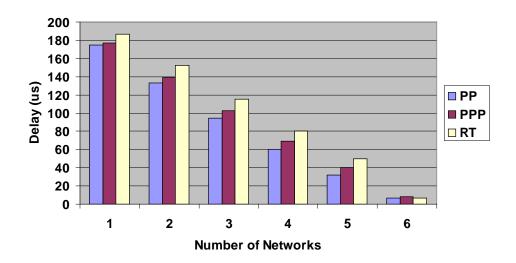

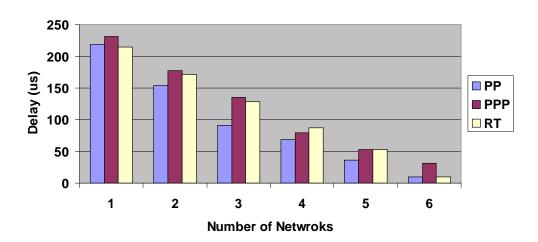

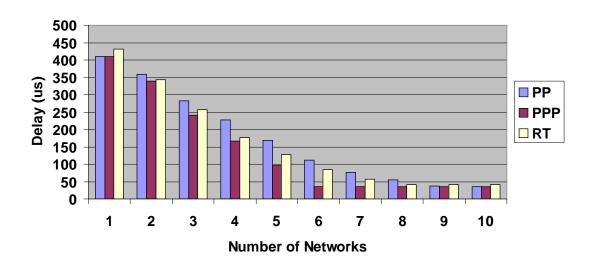

| Figure 48. Message Delay of MG256 in PP, PPP, RT           | 144 |

| Figure 49. Message Delay of CG256 in PP, PPP, RT           | 144 |

| Figure 50. Message Delay of SP256 in PP, PPP, RT           | 145 |

| Figure 51. Message Delay of BT256 in PP, PPP, RT           | 145 |

| Figure 52. Message Delay of COMOPS256 in PP, PPP, RT       | 146 |

| Figure 53. Message Delay of SYN256 in PP, PPP, RT          | 147 |

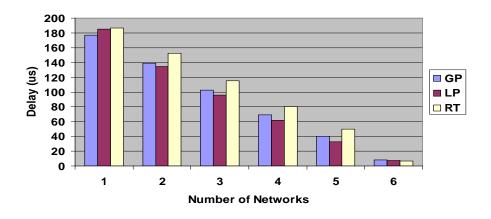

| Figure 54 Comparison between Compiled Communication and FP | 148 |

#### **ACKNOWLEDGMENTS**

During the phase of this research I have been aided by a number of people. I take this opportunity to thank them for the various contributions that they have made to help me reach my goals.

I would like to express my deepest appreciation and thanks to my co-advisors, Dr. Rami Melhem and Dr. Alex K. Jones for their support, encouragement and guidance. Without them, this dissertation would never have happened. I am also grateful to the members of my thesis committee, Dr. Youtao Zhang and Dr. Sanyeun Paul Cho, for their review and suggestions concerning this research.

I would especially like to thank my families. Thanks to my parents for their love and overwhelmingly faith in my ability to achieve my goals. Thanks to wife, my lovely son and daughter for their unconditional love and being my motivation to finish.

Last, I would like to thank my fellow graduate students, the University of Pittsburgh and the cast of thousands that make the University of Pittsburgh such a wonderful place to learn. This research has been supported in part by NSF award number 0702452, the PERCS project at IBM, Defense Advanced Research Projects Agency (DARPA) under Contract NBCH3039004.

#### 1.0 INTRODUCTION

This dissertation tackles the challenges of achieving efficient communications in circuit switched multiprocessor systems. It presents a novel compilation framework for identifying and exploiting communication patterns in parallel applications.

#### 1.1 MOTIVATION AND BACKGROUND

High performance computing systems are being built out of ever-increasing numbers of processors [64, 2, 35, 22, 71, 66, 1]. For example, Roadrunner, the number one supercomputer on the top 500 list in 2009, has 129600 cores [1]. These large systems typically use packet or wormhole switching for inter-processor communication. However, as the system sizes increase, a scalable interconnect can consume a disproportionately high portion of the system cost in order to achieve low-latency and high-bandwidth communication. Although the quest for cheap, low-latency, high-bandwidth packet switching networks to interconnect large numbers of processors is worthwhile, circuit switching [17, 86, 11, 24] can be a cost effective alternative for achieving efficient communication in the high performance computing domain. By establishing direct connections between communicating processors, routing and buffering at intermediate switches can be eliminated, end-to-end protocols can be simplified, and both software and hardware overheads associated with data movement can be minimized.

However, circuit switching technology has two significant drawbacks. The first one is that the overhead of circuit establishment can be relatively large. The second one is that the number of connections that can be established simultaneously is limited. It comes from the fact that the resources used to establish a circuit are exclusively occupied by the circuit. Only when communications in parallel applications exhibit good localities, and these localities can be appropriately exploited, the benefits of circuit switching can outweigh its drawbacks. Using compiler techniques to optimize the communication in parallel applications – known as compiled communication [13, 84, 31] – becomes a promising approach for achieving efficient communications in the high performance computing domain. This approach is to infer the communication patterns of parallel applications at compile time and exposes them to an architecture, in which the multiprocessor systems' run-time components can rely on the compiler statically managing circuit switched interconnections.

The motivation of this work partially stems from the proposal to include an Optical Circuit Switching (OCS) network in the design of next generation high performance computing systems [8]. In the proposal long-lived bulk data transfers are routed through all optical circuit switching networks, which are characterized by high data rates but with high overhead for circuit establishment [25, 83, 8]. An OCS is less expensive than its electronic counterpart as it uses fewer optical transceivers. This interconnection technique is very effective if connections can be pre-established and the relatively long establishment overheads are amortized over the lifetime of the connections. Thus, it is crucial to know which connections will be used during each execution phase to achieve the expected communication performance and cost advantage on circuit switching enabled multiprocessor systems.

Note that, the communication-to-computation ratio of parallel applications can be very high. The communication time can consume more than half of the entire application execution time [107]. Qin et al. reported that communication-aware load balance can improve the performance of communication-intensive applications by up to 75.9 percent and 42.2 percent on average [108]. Generally speeding up communication performance can significantly improve the performance of parallel applications.

#### 1.1.1 Switching Techniques in Multiprocessor Systems

The desire to enable circuit switching in multiprocessor systems is motivated by the investigation on the performance, availability, and cost of different switching techniques in current supercomputers. Circuit switching, packet switching and wormhole routing are three dominant switching methods that have been used in interconnection networks for high performance computing systems [21, 29, 39].

Circuit switching establishes a dedicated circuit between the source and the destination before the source processor can send data to the destination. Once a circuit has been established, the data movements between the source and the destination can happen at very high bandwidth and very low latency compared to packet switching techniques. This is mainly because circuit switching eliminates the needs of routing and buffering at all intermediate switches. Also, the end-to-end protocols can be simplified. However, the overhead of circuit establishment is relatively large. For example, in the design of OCS networks, the switches use optics in all elements of the data path. Setting up such circuits is typically accomplished through the use of MEMS-based (Micro-Electro-Mechanical Systems [25, 83, 8]) mirror arrays that physically move the light beam to establish an optical data path between any input and any output port. The

latency of circuit establishment is measured in milliseconds. Hence, only when the pattern of the communication is known in advance and the circuits can be effectively re-used, the overhead for establish connection can be amortized. Thus the expected benefits of including optical circuit switching in the OCS network can be realized.

In contrast to circuit switching, packet switching does not establish dedicated paths between the sources and destinations. Data, destination address, and other meta-data items are encapsulated into packets. The packets move along the switches and links until they arrive at their destinations or are dropped. The simplest packet switching technique is store-and-forward. Each switch independently determines where to send, and actually sends a packet out after it receives it. Each such step is called a hop and the sender may wait for an acknowledge message from the receiver. In this way, a packet incurs a delay which is at least proportional to the number of hops it has to travel since each switch along the path cannot start sending the packet out until the entire packet has arrived.

In order to reduce this dependence on distance (hops), wormhole switching [65] has been used. In this technique, a packet is further broken into small pieces called *flits* (*flow* control dig*its*). Instead of waiting until the whole packet is received, an intermediate switch can start sending a flit out whenever it is possible. In this way, a packet may spread over many switches on the path from the source to the destination. Wormhole routing was introduced in Ametec 2010 [29], a two-dimensional mesh. It has been widely used in a variety of multiprocessor systems including the Intel Paragon [10], Cray T3D [61, 43], iWarp [31, 28], IBM Power Parallel SP series [72, 5, 14, 81, 12], and the Quadrics switch [26]. Only when the first flit of a packet moves one step ahead or is consumed by the destination, the rest flits of the packet can move one step

forward. Virtual cut-through [45] is similar to wormhole routing except that the flits of a packet can pile up at an intermediate switch. This technique requires more queues at the switches.

As multiprocessor systems scale up, the cost of the interconnection network using packet or wormhole switching increases disproportionately and even dominates the system cost. Therefore, the cost advantage of circuit switching has drawn the interest of many researches in the high performance computing domain. Although not very popular, circuit switching has been used in some multiprocessor systems. For example, the Intel iPSC/2 and iPSC/860 use circuit-switched communication [6, 37, 78, 55]. NEC Earth Simulator [35] uses a statically configured circuit switching network, which has a huge electronic crossbar with 640x640 ports. Interconnection Cache Network (ICN) [33, 34] is similar to the Earth Simulator, in which each processing node has one dedicated channel. Circuit switching also exists in parallel systems which use passive optical components through time-division multiplexing (TDM [16, 30]), wavelength division multiplexing (WDM [23]) or a combination of the two [48, 49, 50].

Circuit switching hardware continues to improve due to improvements in technology. New technologies such as optical switching continue to be an alternative to electronic circuit switching. Optical switching provides several advantages such as capabilities to handle long wire lengths and achieve high bandwidths. However, the reconfiguration time of optical switching is relatively long compared to electronic switching (ms vs  $\mu s$ ) [25, 83, 8]. Hence, techniques are needed to exploit the communication localities in parallel applications to amortize connection establishment overhead on circuit switching interconnect networks. When the communication in a parallel application can be predicted, ideally at compile-time, circuit switching becomes a promising alternative to packet/wormhole switching for efficient communication in multiprocessor systems.

#### 1.1.2 Communication Locality and Analyzability

The feasibility of enabling circuit switching in multiprocessor systems relies on the existence of good communication locality in parallel applications. It has been observed that many parallel applications exhibit high degree of locality [41, 74, 8, 67, 69]. The interconnection networks can benefit from both temporal and spatial communication locality similar to memory systems exploiting locality of references through caches.

Temporal locality represents the effect of temporal aggregation of the inter-processor communications [63]. High temporal locality suggests that the execution of parallel application shows phases and communication aggregates in certain phases. The communication pattern in each phase may be different. But typically in each phase, inter-processor communication stably occurs across a set of connections, which is called a communication working set. This provides the opportunity to reduce communication latency by dynamically grouping and scheduling messages and pre-establishing a certain set of connections.

Spatial locality is determined by the distribution of the connections in the application and determines the size of the working set. It has been shown that each node tends to have only a small number of favored destinations for the messages it sends [47, 3, 4]. For example, the NAS parallel benchmark suite [7] exhibits very high spatial locality and therefore contains small working sets [3]. Although the maximal communication degrees of certain parallel applications can be very large, they can be effectively reduced for many applications to a small number with little performance loss by just filtering out a small percentage of messages [8]. Several research groups observed that the communications in many applications exhibit regular patterns [38, 52, 51, 8]. Additionally, it has been shown that these regular communication patterns can often be discovered through analysis of the source code [27, 13, 18].

Many previous efforts to analyze communications patterns in parallel applications are based on trace analysis [8, 10, 67]. However, traces can provide communication information only for a particular execution instance of an application on a particular platform. Using static compiler techniques can reveal the underlying communication pattern of a parallel application.

In summary, many parallel applications exhibit good communication locality and the locality can be effectively explored by compiler techniques to improve the performance of parallel applications. Thus we can enable circuit switching to take advantage of its cost benefits.

#### 1.2 OVERVIEW OF THIS RESEARCH

The goal of this research is to develop compiler techniques that can achieve efficient communication in multiprocessor systems with circuit switching capabilities.

This research develops a compilation framework for analyzing the communication patterns in the parallel applications, in particular Message Passing Interface (MPI) [56] parallel applications. This compilation framework takes advantage of certain traditional compiler analysis techniques, such as control and data flow analysis, constant propagation, constant folding, and inter-procedural analysis, to collect information about MPI functions and program structure. Based on the collected information and using symbolic expression analysis, the framework identifies communications and partitions communication into phases. Finally, network configurations are generated for each communication phase and compiled into the application. These network configuration instructions are triggered at runtime to pre-establish circuits before actual communication appears.

This research classifies communication patterns into three categories: *static*, *persistent* and *dynamic*, based on the temporal and spatial locality of communications and the compiler capability to identify these localities. The classification implies different possibilities for reducing communication overhead in circuit switching networks. For example, given that the earliest opportunity for determining network configurations for a static communication operation is at compile-time, configurations may be statically inserted into the code by the compiler. This dissertation presents compiler techniques to identify static and persistent communication patterns. In particular, symbolic expression analysis is used to infer and compose symbolic expressions for the communication pattern. The need for symbolic expression analysis is highlighted by persistent communication because it contains variables that can only be represented by symbolic expressions and cannot be resolved at compile-time.

This research develops a powerful scheme to represent communication patterns. The representation describes collective and point-to-point communications using communication vectors and matrices, respectively. The vectors and matrices contain exact values if the communication pattern contains only static communications. Otherwise, they may contain symbolic expressions. One significant advantage of this scheme is that it has the capability to capture and represent the temporal locality by explicitly introducing communication phases in the pattern representation scheme. This scheme allows the manipulation of communication patterns through a set of convenient operations. It is also flexible and can be easily tailored to be used by other types of communication analysis.

Given that the communication working set of a parallel application may change during different phases of execution, an important aspect of the analysis of communication patterns is to identify and partition different communication phases. This research develops an algorithm for

partitioning communication phases, which uses the knowledge of program structure, symbolic expressions of logical connections, and network specifications. Based on the information, the algorithm segregates communication operations into communication phases with proper size for the parallel application. When generating network configuration from the communication pattern for a parallel application, this research uses an algorithm that can schedule as much communication as possible in the available networks when not all circuits can be implemented simultaneously. The application will be instrumented with network configuration instructions to pre-establish network connections during runtime.

This dissertation presents an experimental compiler that implements the compilation framework. This compiler is based on the SUIF compiler infrastructure [79] and integrates the compiler techniques developed in this research. Specifically, it can identify the communication pattern from the parallel application source code; compile the communication pattern as network configuration directives and instrument the application with these network configuration directives.

To evaluate the effectiveness of this research, it is essential to investigate the performance gains of this work in circuit switching enabled multiprocessor systems. Given the infeasibility of building a real system for cost reason and time limits in the context of this research, simulation approach is used. This research develops a multiprocessor system simulator. Our simulation-based experimental results demonstrate the usefulness of the compilation framework developed in this research.

In brief, this dissertation makes the following contributions:

- It extends the classification of communication as static, persistent, and dynamic, by separating persistent communication from traditional dynamic communication. This allows the compiler to tackle the majority of communications in typical parallel applications.

- It develops a compilation framework which integrates traditional and novel compiler techniques to exploit communication locality for achieving efficient communication in multiprocessor systems augmented with circuit switching capabilities.

- It presents a powerful and flexible communication pattern representation scheme which can effectively represent the temporal and spatial localities of communication.

- It develops novel symbolic expression analysis technique to analyze persistent communication patterns.

- It develops a communication phase partition algorithm to separate application into phases based on the underlying network architecture and communication requirement in the application.

- It develops an experimental compiler to implement the framework and a multiprocessor system simulator to evaluate the compiler.

- It explores and summarizes the generic and preferred runtime scheduling strategies for the proposed circuit switching enabled multiprocessor systems.

- It presents experimental study to show the usefulness and effectiveness of compiler techniques developed in this research.

#### 1.3 ORGNIZATION OF THIS DISSERTION

The remainder of this dissertation is organized as follows. Chapter 2.0 presents prior work on studying communication characteristics. The relationship of this research and prior work is also discussed. Chapter 3.0 discusses the overall design of our compilation framework. It describes the machine and programming model that is targeted in the framework. It also describes the components and uses of the framework. Chapter 4.0 presents the classification of communication patterns and a powerful scheme to represent the communication patterns. It also shows the communications in NAS parallel benchmarks. Chapter 5.0 presents symbolic expression analysis for analyzing the communication patterns. Chapter 6.0 describes communication pattern manipulation and our phase partition algorithm. Chapter 7.0 discusses the runtime scheduling strategies. Chapter 8.0 describes the implementation details of our experimental compiler and the multiprocessor system simulator. Chapter 9.0 presents the experimental results to demonstrate the effectiveness of our compilation framework. Experimental results show that our compiler techniques can identify communication patterns. We simulate different types of multiprocessor systems. The performance comparison shows that the overall performance of parallel applications can be significantly improved by using techniques developed in this research. Conclusion, limitation and direction for future research are discussed in Chapter 10.0.

#### 2.0 RELATED WORK

There is a wealth of prior related work that primarily comes from three areas of study. These areas are communication characteristics analysis, compiler techniques to exploit communication patterns, and simulation of multiprocessor systems. In the following sections, we discuss prior work and describe the relationship between them and this research.

#### 2.1 COMMUNICATION CHARACTERISTICS ANALYSIS

Understanding the communication pattern in the parallel application is critically important in the high performance computing domain. First, the characteristics of the targeted/expected workloads are important to determine multiprocessor system architecture. Second, system communication software needs to be optimized for both the system architecture and the application workload characteristics. Third, application developers need to make decisions on algorithms and data distribution models based on the system architecture and system communication software design. There is a lot of research on this topic.

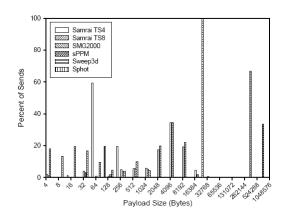

In [77], Vetter and Mueller evaluated explicit communication characteristics across a set of diverse, large-scale scientific applications, primarily from the perspective of message passing via MPI. They use the MPI profiling layer to trace applications' communication activities. That is a trace-based approach. The MPI profiling layer is capable of capturing information about

each MPI call and the actual parameters of the function call. By focusing on the MPI activity of the applications, they presented the inherent communication signatures of a diverse range of applications. They observed that a trend of novel applications parting with regimented, static communication patterns in favor of dynamically evolving patterns. Note that they traced application communication activities with MPI's profiling layer. Another interesting observation from their work is that the payload size of point-to-point MPI messages tends to be large and the payload size of collective communication tends to be small. This suggests that enabling circuit switching in multiprocessor systems can benefit a significant portion of communication—point-to-point communication.

Payload size distribution for P2P messages (64 tasks).

Payload size distribution for collective communication(64 tasks).

Figure 1. Veter's MPI Payload Size Distribution

Faraj and Yuan [27] investigated the communication characteristics of MPI implementations of the NAS parallel benchmarks [7]. They used trace-based approach too. They instrumented MPI operations by implementing MPI wrappers that allow them to monitor the MPI communication activities at runtime. Then they examined the source code and marked each

of the MPI communication routines by hand. After the execution of the program, they analyze the trace files for all the nodes off-line to obtain the dynamic measurement of all communication activities. Their work also concluded that pure dynamic communication is only a small portion of all the communication in parallel applications. Thus a compiler has the potential of effectively optimizing communication statically for parallel applications.

Ho and Lin presented a work that statically analyzes communication structures in programs written in a channel-based message passing language called communication compiling component [38].

It is also worthwhile to mention the work of Ali et al. [104]. They presented performance models for certain collective communication algorithms that exploit features of the Cell architecture.

All the works described above use traditional trace-based approaches [87-91]. Trace-based approaches are limited to profiling and trace analysis. Although these attempts revealed many valuable characteristics of the communication in parallel applications, they do not provide a systematic way to identify accurate communication patterns with respect to connections. Trace-based approaches can only provide the communication information for particular execution instances of an application on a particular platform. When multiprocessor systems scales to massive number of processors, which can be thousands or even millions processors, trace-based approaches often become impractical. The overhead of trace generation may introduce unacceptable interference to the applications' behavior. The storage capacity limits may prevent researchers from collecting enough trace data. They often have to use sample-based analysis techniques. In short, there is lack of an automated compiler-based/compiler-assisted approach to reveal the communication patterns.

As CPU design goes into the chip multi processor (CMP) era, the computation within a single multi-socket machine naturally becomes parallelized. The data movements between different CMPs, caches, and memory modules may be very different. Compiler-based approaches can be used to improve these latencies too. For example, Jin and Cho utilized a software-oriented approach to optimize CMP cache management [103]. Although CMP research is out of the scope of this dissertation, they can share the same philosophy to improve system performance as what we used for MPI parallel application run.

#### 2.2 COMPILER TECHNIQUES FOR OPTIMIZING COMMUNICATIONS

In the high performance computing domain, compiler techniques are developed to improve the execution of parallel applications, i.e. to shorten the executing time, optimize resource utilization, and reduce power consumption. We can also utilize compiler to schedule and optimize the communication activities of parallel applications if the compiler is given the knowledge of the interconnection network and is capable of identifying the application communication pattern at compile-time. This technique is called compiled communication [13, 27]. There are some interesting research efforts in this domain.

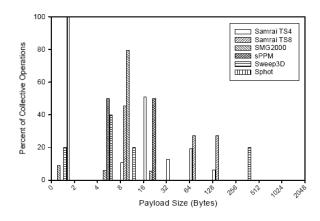

Liang et. al. presented a SUIF-based compiler and an adaptive System-On-a-Chip (aSOC) multi-core architecture [52]. Their compiler is actually an application translator that maps applications' high-level design representations to the cores on an aSOC chip. The compiler is based on SUIF infrastructure. It isolates code basic blocks from the SUIF intermediate representations. Basic blocks are the fundamental unit when they map an application to the cores. Assigning different basic blocks to different cores incurs different inter-core communication

requirements. They developed a heuristic cost-model to control the basic-block-to-core mapping. The mapping of each basic block is directed by the computation and communication heuristic. Once related basic blocks are assigned to specific cores, the inter-core communication needs are determined and communication instructions are generated and inserted by the compiler to control inter-core data transfer. Figure 2 described the architecture of Liang's system [52]. In the experiments, they mapped four high-bandwidth signal processing applications including an MPEG-2 video encoder and a Doppler radar processor to a prototype aSOC device using compiler assisted design mapping technology.

Figure 2. Liang's Adaptive System-on-a-Chip (aSOC) Architecture

Although the focus of the research of Liang et. al. is aSOC design, part of their application mapping techniques can be classified as compiled communication. But their work is in the scope of sequential program parallelization. Instead of identifying and compiling existing communication of parallel applications, they introduce inter-core communication by assigning different basic blocks of a sequential application to multiple heterogeneous resources, including cores.

Urfianto et. al. [105] presented another piece of work applying complier techniques on a Multiprocessor System-on-Chips (MPSoC) architecture. They utilized several optimizations provided by their compiler to implement efficient communication between processing elements. Their work is another example that demonstrates the feasibilities of applying compiled communication techniques on SoC architectures.

Shires et. al. [70] presented an algorithm for building a program flow graph representation of an MPI program. They augmented traditional program control flow graph with communication nodes and edges. They provided an interesting basis for important program analyses useful in software testing, debugging and code optimization. One limit of their approach is that their technique can only apply to static communication. It is possible, actually very often, that a communication occurs at run-time and has no associated communication edges. Thus it is infeasible to use their approach when the MPI program has a large number of control branches.

Cappello and Germain [13] exploited the association of compiled communication and a circuit switched interconnection network. They defined compiled communication as the technique to manage communication in parallel applications at compile-time. They investigated the feasibility of the compiled communication model and suggested using compiler to extract data references within parallel applications and translated the references to communication patterns. Their pioneer work pointed out a promising direction in interconnection network design and provided a fundamental theoretical performance analysis. But the proposed approach is targeted to data parallel programming language, which is a subset of (High Performance Fortran) HPF-like language [36, 75]. In that kind of programming languages, a communication pattern can be inferred from where the data are distributed and where the data are referenced.

Yuan [82, 85] studied compiled communication that can eliminate the run-time communications overheads of the dynamic communications by managing network resources at compile-time. A compiler, E-SUIF, is implemented to support compiled communications on optical TDM networks. In short, the techniques developed by the work analyze a program to determine its communication needs; then manage communication at compile-time with the knowledge of communication requirements and underlying network. The work targeted HPF-like programming models too. Those programs have programmer-specified explicit data alignments and distributions and no explicit communication. It is the duty of compilers to distribute the logical data set to different physical processors. Thus communication is needed to reference data stored on a remote processor.

The above two works did not target parallel programming models with explicit message passing. However, parallel applications with explicit message passing written in SPMD parallel programming models dominate today's high performance computing domain. These message-passing applications have potential to benefit from compiled communication techniques.

Karwande et. al. [44] made an attempt to apply compiled communication techniques in a prototype MPI library for Ethernet switched cluster. Basically they extends the MPI standard and uses separate routines for network control and data transmission and exposed network control routines to programmer for writing parallel programs which may benefit from compiled communication techniques. There are several limitations to the work. First, it requires the programmer, not just the compiler, to understand and manipulate network resources; and it needs run-time communication parameters to determine which implementation for a specific collective operation will be chosen at runtime. Second, the MPI system and applications may have to be modified from one cluster to another. Third, it handles collective communication only.

As we have described before, persistent communication is a significant portion of communication in parallel applications. Persistent communication can only be represented with certain unknown symbols which cannot be resolved at compile-time. This highlights the needs of performing symbolic analysis while analyzing and composing the communication pattern of an application.

Symbolic analysis is a useful technique in the parallel compiler research area. Several researches studied symbolic analysis techniques in the context of parallel compilation for High Performance Fortran (HPF)-like programs. Most of the work emphasizes the parallelization of programs with the assistance of symbolic analysis and a focus on loops and arrays. For example, Yuan et al. explored using compiled communication for HPF-like parallel applications as an alternative to dynamic network control [84].

In summary, to the best of our knowledge, there is no research that studies compiler techniques for efficient communication on circuit switching enabled multiprocessor systems for Single-Program-Multiple-Data (SPMD) programs, which is the subject of this dissertation.

#### 2.3 SIMULATIONS OF MULTIPROCESSOR SYSTEMS

Simulation is a popular approach for research in the high performance computing domain. Many parallel simulations have been developed. High performance interconnection network simulations have different characteristics than general-purpose network simulators like NS [40], Parallel/Distributed NS [32], and GTSNetS [60]. To be able to simulate thousands of nodes, decisions regarding network topologies, routing algorithms, buffering, flow control, and so on,

have to be carefully made. Many simulators for parallel systems have been developed. Petrini and Vanneschi developed a simulator SMART and used it to simulate diverse traffic patterns for studying and analyzing different network architectures [59]. Benveniste and Heidelberger designed a conservative simulator of the IBM SP2 network [9]. MINSimulate [76] focuses on multistage interconnection, limiting it to a subset of well known network topologies. 'A la carte [42] is a Los Alamos computer architecture toolkit for simulating computing architectures. It is suitable to simulate extreme-scale systems (thousands of processors) with flexible architectural configurations.

An interconnection network simulator was presented by J Miguel-Alonso et.al. for MPI traces [106]. But their work was only able to handle traces generated by the MPI profiling mechanism PMPI. It cannot take any code artifacts, such as branches, loops, function boundaries, into consideration. Also they did not provide a way to emulate computation time. These facts make it an interesting related work to this research but we cannot take any advantage from it.

To summarize, none of the currently available simulators for parallel systems meet the needs for this research. First, our target simulated parallel systems must be able to include both circuit switching and packet switching interconnection networks. Second, a run-time component is needed to explore different communication scheduling strategies. Thus we need to develop our own multiprocessor system simulator.

#### 3.0 OVERALL DESIGN OF THE COMPILATION FRAMEWORK

As described in Chapter 1.0, when parallel applications exhibit good communication locality and the locality can be effectively utilized, circuit switching has the potential of providing efficient communication. In this chapter, we present the overall design of our compilation framework to exploit the communication locality in parallel applications. First, we describe the machine model and programming model that are targeted in our framework. Then we describe the components in our compilation framework, including communication detection component, communication analysis component, communication compiling component and trace generation component. Finally, we describe the uses of our compilation framework.

#### 3.1 MACHINE AND PROGRAMMING MODEL

To be able to exploit communication locality, we need to extract the communication patterns from application programs. The method to extract communication patterns in programs depends on both the machine model and the programming model.

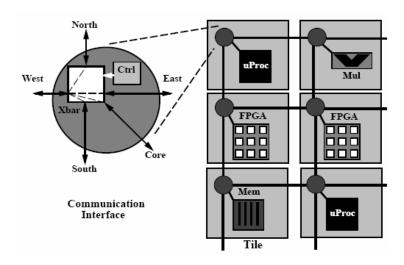

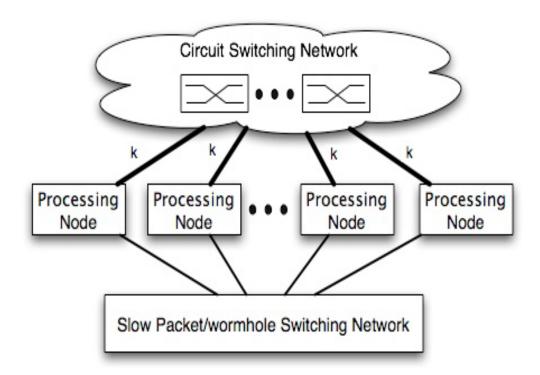

There are some requirements for multiprocessor systems to be able to effectively utilize the communication locality in parallel applications. First, the interconnection network must have the capability to preload and keep network configurations. Because of the large connection setup delay in circuit switching, it is crucial for the system to establish circuits prior to the actual communication requests. When the network cannot support all the needed circuits, dynamically setting up and tearing down circuits may lead to circuit thrashing, which establishes the same circuits many times during the execution of the application. Thus, keeping (or pinning) circuits in the network is often a better decision than dynamically setting up and tearing down circuits.

Second, we need to deploy a packet/wormhole switching network in the system in addition to the circuit switching network. The performance of this network can be significantly loosened to keep its cost low. The necessity of this network originates from the fact that there exists dynamic communication in some parallel applications. The time interval from when the needed circuits can be known to when the corresponding communication operation appears mostly is much shorter than the circuit establishment delay. For such cases, immediately delivering the message through even a slow packet/wormhole switching network may result in lower message latency than transferring the message through the circuits switching network.

Figure 3. System Model of Targeted Multiprocessor Systems

Based on these requirements, Figure 3 gives an abstract model of multiprocessor systems that are targeted in our compilation framework. The system includes two kinds of interconnection networks: a circuit switching network and a packet/wormhole switching network. The circuit switching network can support k simultaneous connections to each processing node. It also allows connection preloading and reconfiguration.

In our framework, we target Single-Program-Multiple-Data (SPMD) programs with explicit message passing. In such programs, programmers explicitly use communication primitives to perform the required communication. The communication primitives can be high level library routines, such as Message Passing Interface (MPI), or low level communication primitives such as the shared memory operations in the CRAY T3D [92] and CRAY T3E [93]. Nowadays, SPMD is the dominant parallel programming approach.

#### 3.2 COMPONENTS OF THE COMPILATION FRAMEWORK

The goal of our compilation framework is to identify communication patterns in Single-Program-Multiple-Data (SPMD) parallel applications and compile these patterns as network configuration directives. This can significantly reduce the communication overhead on circuit switching interconnection networks.

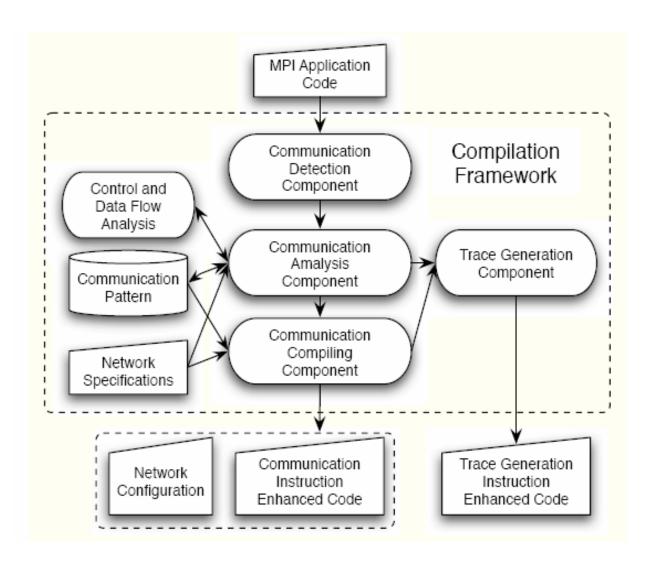

Figure 4 gives an overview of our compilation framework. Our framework includes four components: *communication detection component* to collect communication operations in the MPI parallel applications; *communication analysis component* to identify communication patterns and partition the communication phases; *communication compiling component* to insert

network configuration directives and *trace generation component* to automate trace generation for MPI applications. In the following sections, we describe these components.

Figure 4. Overview of the Compilation Framework

# 3.2.1 Communication Detection Component

The communication detection component is responsible for identifying all explicit message passing functions (i.e., the MPI functions) used in an application and the related variables and parameters used in these MPI function calls. This is the very first step for further analysis. It provides information about which constants, which variables, and what part of code are involved in communication operations. We will use the sample code shown in Figure 5 to briefly demonstrate what the communication detection component does.

```

1 call mpi_init(ierr)

2 call mpi_comm_rank(MPI_COMM_WORLD, me, ierr)

3 call mpi_comm_size(MPI_COMM_WORLD, nprocs, ierr)

4 if (me .eq. 1) then

5 call mpi_send(buf, 16, MPI_INT, 0, tag, MPI_COMM_WORLD, ierr)

6 endif

```

Figure 5. Sample MPI Code Segment Where Node 1 Sends a Message to Node 0

The communication detection component will identify that there are 4 MPI functions in the code segment, mpi\_init, mpi\_comm\_rank, mpi\_comm\_size and mpi\_send. Line 1 is the MPI function which initializes the run-time MPI context for this node. One task of the initialization works is to coordinate with other nodes and allocate an integer-type rank for this node. The rank can uniquely identify a node within an MPI application execution instance.

Line 2 dictates the rank of the node is in variable *me* and Line 3 dictates that the total number of nodes running this application is in variable *nprocs*. Line 5 dictates that there is a point-to-point communication from node *I* to node *0* and the message size is 16 integers.

# 3.2.2 Communication Analysis Component

After the MPI operations and parameter information are identified, the communication analysis component identifies and analyzes the communication patterns based on a powerful representation scheme. Current compiler techniques, such as control and data flow graph (CDFG) analysis, are capable of inferring information to analyze the communication behavior of an entire program. Besides, we need advanced compiler techniques to analyze the communication patterns. For example, we need inter-procedural constant propagation to determine if the communications are static. Many communication operations utilize array parameters. For instance MPI operation *scatter* allows one node to distribute messages to many other nodes and *alltoallv* allows many nodes to send messages to many nodes. Such MPI operations use arrays to specify what nodes are involved in the operation and the data (type and count) related to each node involved. We need array section analysis to analyze these array operations. Also, we need strong symbolic expression analysis because persistent communications include variables that can only be represented as symbolic expressions.

Communication analysis component operates as follows. First, the CDFG is constructed for each procedure and communication related information is propagated through the graphs. Then a communication graph is built for the entire application. In this whole program communication graph, any CDFG node that does not affect the communication operations will be removed. The communication pattern, whose representation is detailed in Section 4.2, is

identified from the communication graph and stored in a communication pattern repository. The communication operations of the entire application are partitioned into communication phases. By mapping the communication patterns into a sequence of phases, it is possible to create more efficient communication working sets or groups of communications that occur in relatively close proximity. The granularity of the communication phases depends on the capacities of the communication network.

# 3.2.3 Communication Compiling Component

Based on communication patterns identified by the communication analysis component and the interconnection network specification, the communication compiling component inserts network configuration instructions into the application. This is a network-dependant component.

The design of the network configuration instructions relies on the target interconnection network. For static communication patterns, the compiler generates a network configuration file that can be used by the loader and inserts respective network configuration setup instructions in the program. For persistent communication patterns, the compiler inserts symbolic network configuration instructions that aim at pre-establishing the needed connections at run-time prior to the actual communications.

For the example shown in Figure 5 (line 4-6), because communication happens between node l and node l, we can insert a network configuration directive (0, 1, 0). The first parameter specifies which circuit switching network will be used to establish the connection when there are multiple circuit switching networks. The second is the source node and the last is the destination node. Here, (0, 1, 0) means using circuit switch network l to connect node l and node l.

# 3.2.4 Trace Generation Component

Although trace study has the drawback of emulating execution based on a specific set of data and parameters, many efforts to study the communication patterns of parallel applications are based on traces. We have a trace generation component in our compilation framework to automate trace generation for MPI applications. This component is responsible for inserting trace generation instructions for MPI functions within the applications. It also includes additional instructions that detail communication-related artifacts and constructs of the source code. We use the traces to verify the analysis results obtained by the compiler. Also, the traces can be fed into parallel system simulators to investigate the effectiveness of our framework.

#### 3.3 USES OF THE COMPILATION FRAMEWORK

As previously discussed, circuit switching has the potential of providing efficient communication when the communication locality in the application can be identified and utilized. Our compilation framework can be used to identify and exploit the communication locality for parallel applications to achieve efficient communication.

Although we focus on MPI applications, our framework can be applied to other explicit message passing programming models written in SPMD style, where each processor independently executes the same program on its private data. To be able to work for other programming model, the part that needs to be changed in our framework is the detection of communication operations (i.e., instead of detecting MPI functions, our communication detection component needs to collect communication operations in other format).

The compiler techniques developed in our framework can benefit other research work in the high performance computing domain. For example, The Interconnection Cache Network (ICN)) [33, 34] statically configures its circuit switching crossbar according to the mapping from the communication graph in the parallel applications. Thus, the efficiency of obtaining the communication graph in the parallel application matters but it is beyond the scope of that work. ICN can benefit from using compiler techniques developed in our framework to obtain the communication graph in the parallel application efficiently.

We developed an experimental compiler to implement this compilation framework. The proposed components are implemented within the experimental compiler. We take advantage of Mathematica for symbolic expression manipulation. This significantly speeded up the research. This compiler is used on the benchmarks selected for this research.

Note that trace-based approach is still used by many researchers to study MPI applications. Our experimental compiler can automatically enhance MPIs programs with trace generation instructions for collecting traces of MPI operations and related code artifacts, e.g. function boundaries and branches. Thus it is a convenient tool for trace-based researches.

A multiprocessor system simulator is developed for this research. It takes execution traces and network configurations as input and generates accurate execution time information for performance study. The details will be provided at Chapter 8.2. This simulator can be used for studying MPI program and multiprocessor system.

## 4.0 COMMUNICATION PATTERN

Based on the communication locality and the compiler capability to identify the locality, we classify communication patterns into *static*, *persistent* and *dynamic*. This classification implies different possibilities to utilize the communication locality. In this Chapter, we first describe our classification. Then, we present a communication pattern representation approach to describe collective and point-to-point communications. This representation captures the property of communication patterns and allows manipulation of these patterns. Finally, we present the communications in NAS parallel benchmarks, which experimentally show that the majority of the communications are static and persistent.

## 4.1 COMMUNICATION PATTERN CLASSIFICATION

The communication within most parallel applications tends to exhibit good spatial locality and good temporal locality. The spatial locality dictates that each node often communicates only with a small number of other nodes. The temporal locality describes that the active communication set tends to be stable for certain time interval and then change to another set. Each such time interval is called a communication phase in this dissertation. Based on the temporal and spatial locality of communications and the compiler analyzability of the application code, we classify communications within a phase into three categories: *static*, *persistent* and *dynamic*. In this

context, a communication operation is specified by the source and destination of the messages exchanged. We refer to this as the topology of the communication.

**Static** - Communication is static if it can be completely determined through compile-time analysis. That is the compiler can identify both the temporal locality and the exact topology of the communication.

**Persistent** – Communication is persistent if, though the compiler cannot determine the exact topology of communication, it can determine that the topology does not change during the phase. That is, its temporal locality can be identified by the compiler, but its spatial properties remains unknown until run-time.

**Dynamic** – Communication is dynamic if it is neither static nor persistent.

Given that the communication working set of a parallel application may change during different phases of execution, an important aspect of the analysis of communication patterns is to identify and segregate different communication phases. It has been observed that a main source of communication temporal locality originates from loop structures of MPI programs. Hence, it is natural to consider a loop, which contains communications, as the basic building blocks of phases.

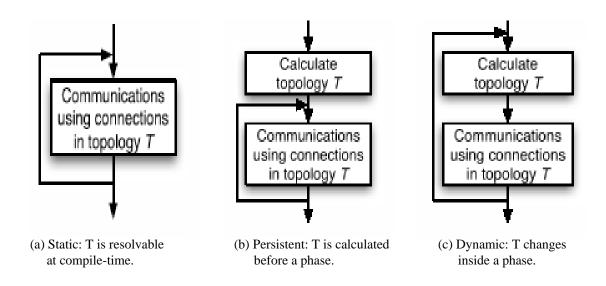

In Figure 6, we illustrate the definition of static, persistent, and dynamic communications when a phase is defined as a loop. Specifically, the communication operations are static if the topology (in terms of sources and destinations) can be completely resolved at compile-time, as in Figure 6 (a). In Figure 6 (b), the topology cannot be determined until run-time. However, once defined, the topology is repeatedly used within the loop. In this case, we call the communication

operations persistent. In Figure 6 (c), the communications are dynamic because during each iteration of the loop, the topology is re-calculated prior to use.

Figure 6. Static, Persistent and Dynamic Communications

The above classification implies different possibilities for reducing communication overhead in circuit switching networks. For example, given that the earliest opportunity for determining network configurations for a static communication operation is at compile-time, configurations can be statically inserted into the code by the compiler at the phase boundaries. For persistent communication, the topology of the communication is not known at compile-time. However, it is possible to insert at compile-time symbolic expressions specifying the topology that may be resolved at run-time. By placing these symbolic expressions at the earliest point where the expression will be resolved, the network reconfiguration may still be able to take place prior to the use within a phase.

This classification enables us to target each class with the most appropriate network technology and operating mechanism. Specifically, static and persistent communications will be compiled and dispatched to the circuit switching interconnect network. Dynamic communications will be dispatched to the packet/wormhole switching network.

## 4.2 COMMUNICATION PATTERN REPRESENTATION

Previous researches have observed that the communication operations in many applications exhibit regular patterns [38, 53, 52, 8]. Additionally, it has been shown that these regular communication patterns can often be discovered through analysis of the source code [27, 13, 18].

To solve a particular scientific problem, a parallel application is often organized in computational phases. Given that these parallel applications have computational phases, we can expect that their communication behaviors are in a similar way. For example, the communication topologies of adaptive applications evolve during their execution time. Even for parallel applications that have static communication patterns, their active communication working set may change as the phases change. The result is one or multiple communication phases. Communication phases are not identical to computational phases, but are strongly associated with them. For example, some computational phases contain no communication and thus can be ignored when identifying communication patterns. Several computational phases may yield a single communication phase. The number of phases is an artifact of the analysis used to partition the communications into phases. To be able to perform communication analysis effectively, it is

necessary to have a flexible representation that can capture the properties of communication patterns accurately.

A traditional communication representation models the rough logical topology of communication patterns, (e.g., binary tree, 2-D mesh, hypercube). These representations are too coarse and cannot describe the communication topologies accurately. Another disadvantage of prior representations is that they cannot describe temporal information. Our representation scheme is designed specifically to avoid these limitations and to effectively represent the temporal and spatial properties of communication patterns.

In the following, we describe our representation scheme, which uses a communication matrix and vector pairs to describe the communication pattern in an application. The fact that the communication pattern of an application contains phases is important and must be described while representing the pattern.

We define all the communication operations of an application as a communication pattern. There are two types of communication operations in MPI applications: collective communications and point-to-point communications. In order to represent the collective communications, we define a c-enumeration to describe the set of collective communication functions invoked in a parallel application. Note that the participating nodes of a MPI program run can forms different communication groups—called MPI communicator, which will be detailed in Section 5.5. A node can participate multiple communicators. Each node within a specific communicator has a unique integer id—called *rank*. The same node may have different ranks within different communicators. The default communicator, referred to as MPI COMM\_WORLD retains all the processors.

**Definition:** A *c-enumeration* is a list of all the collective communications that appear in a parallel application. Each collective communication is represented by a pair, the function name and optionally the corresponding MPI communicator.

For the function names, we use AA, AV, AR, and RD to represent MPI\_Alltoall, MPI\_Alltoallv, MPI\_Allreduce, and MPI\_Reduce respectively. The communicator is omitted if it is the default MPI communicator. For each related MPI communicator, the same collective MPI functions have exactly one instance in the c-enumeration. Each communication pattern retains a unique c-enumeration.

**Example 1**: CE = {AA, AR, (AR, commu<sub>1</sub>), RD} indicates that there are three different types of collective communications in the application. The first two and the last operations are performed in the default MPI communicator. The third operation, MPI\_Allreduce, is performed in a user-defined communicator  $commu_1$ . The communication detection component of the framework is responsible for building c-enumerations.

Figure 7 formally describes the grammar to represent the communication pattern with one or multiple phases for parallel programs. In rule 2,  $col_i$  represents any collective MPI function, and  $comm_i$  represents the corresponding MPI communicator. Here, we assume that m is the number of elements in c-enumeration.

```

Rule 1: communication pattern \Rightarrow c-enumeration, phases

Rule 2: c-enumeration \Rightarrow {(col<sub>0</sub>, comm<sub>0</sub>), ..., (col<sub>m-1</sub>, comm<sub>m-1</sub>)}

Rule 3: phases \Rightarrow \varepsilon | phase phases

Rule 4: phase \Rightarrow <c-vector, p-matrix> | [phases]

Rule 5: c-vector \Rightarrow \varepsilon | <w<sub>0</sub>, w<sub>1</sub>, ..., w<sub>m-1</sub>>

Rule 6: p-matrix \Rightarrow \varepsilon | <deterministic p-matrix> | <symbolic p-matrix>

```

**Figure 7.** The Grammar for Communication Pattern Representations

As described in rule 3, a communication pattern consists of a sequence of phases. A phase may also be a loop of a sequence of phases that repeat in any execution instance of an application, represented by square brackets in rule 4 of the grammar. Rule 4 also indicates that a basic communication phase is described by a *c-vector* and a *p-matrix* that represent all the collective and point-to-point communications, respectively, in that phase.

**Definition** A *c-vector* corresponds to a *c-enumeration*. Each element of the vector represents the weight of the corresponding collective communication in the *c-enumeration*.

**Definition** A *p-matrix* is a N  $\times$  N matrix that describes a set of point-to-point communications. The entry in position i, j describes the weight of communication from processor i to j. Certain weights may be unknown, which can be represented by  $\delta$ , defined next.

**Definition**  $\delta$  represents any unknown values, variable, vector, or matrix.

In the above definitions of *p-matrices* and *c-vectors* we do not enforce a specific meaning for the communication weight. Three options are described here: (1) a single bit value to indicate if there exists point-to-point communication from the source processor to the destination processor (2) the message volume or (3) message count. In the cases that the compiler cannot construct even a symbolic expression for a point-to-point communication,  $\delta$  is used in the symbolic expression for that matrix entry.

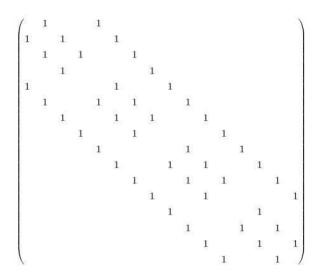

A *p-matrix* is **deterministic** if the total number of processors N is known and each entry of the *p-matrix* is a constant. A deterministic *p-matrix* is used to represent static communications. When the size N of a *p-matrix* is a symbolic constant and/or any entry can only be described by a symbolic expression instead of a constant, it is a **symbolic** *p-matrix*. A symbolic *p-matrix* can always be described by a formula list. Persistent communications can usually be described by symbolic *p-matrices*.

$$\begin{pmatrix} (rank + x) \mod N \\ rank > x : (rank - x) \mod N \end{pmatrix} \begin{pmatrix} 1 \\ 1 \\ 1 \\ 1 \end{pmatrix}$$

(a) PM\_A (b) PM\_B

**Figure 8.** A Symbolic p-matrix and Its Deterministic Instance Where x=1 and N=4

**Example 2**: As shown in Figure 8,  $PM\_A$  and  $PM\_B$  are a formula list and a deterministic p-matrix, respectively.  $PM\_A$  describes a communication pattern in which each processor rank sends to rank+x and rank-x if rank-x>0 where x is determined at run-time and N is the total number of processors. In the case x=1 and N=4, a deterministic p-matrix  $PM\_B$  is inferred from  $PM\_A$ .

Table 1. The Communication Pattern of IS

| c-enumeration | {AR, AA, AV, RD} |          |

|---------------|------------------|----------|

| Phases        | c-vector         | p-matrix |

| Phase 0       | <1,1,1,0>        | NULL     |

| Phase 1       | <1,1,1,0>        | NULL     |

| Phase 2       | <0,0,0,1>        | PM_IS    |

|               |                  |          |

**Example 3:** The communication pattern of IS (integer sorting) program from NAS parallel benchmark suite [7] is shown in Table 1 and its deterministic *p-matrix* in phase 2 is shown in Figure 9.

$$\begin{pmatrix} &1&&&&&&\\ &&1&&&&&\\ &&&1&&&&\\ &&&&1&&&\\ &&&&&1&&\\ &&&&&&1&&\\ &&&&&&&1&\\ &&&&&&&1&\\ &&&&&&&1&\\ \end{pmatrix}$$

**Figure 9.** p-matrix for IS with 8 Processors

As we already described earlier in this section, programmers can create any user-defined communicator when necessary. A node may have different rank numbers in different communicators. And each point-to-point communication function specifies the source node or destination node in terms of rank and the corresponding communicator. Two send operations to two nodes with different ranks in two different communicators may use the same connection and should be represented in the same entry of a *p-matrix*. This is possible because all user-created

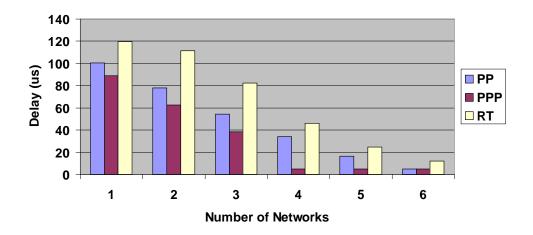

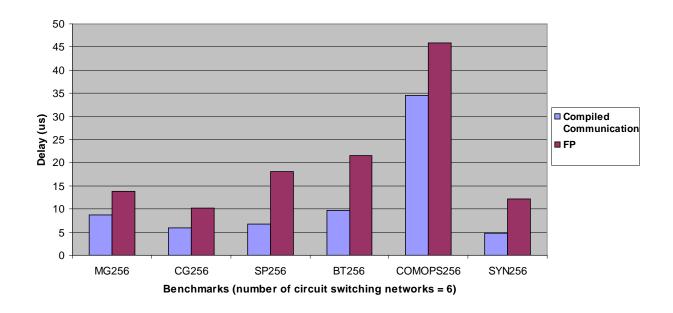

communicators are built from the default communicator with standard communicating group and communicator manipulating functions.