## TUNING AND CONTROL OF AN ON-CHIP PIEZOELECTRIC RESONATOR

by

Matthew J. Volkar

## BS Electrical Engineering, University of Pittsburgh, 2001 BS Computer Science, University of Pittsburgh, 2001

Submitted to the Graduate Faculty of

the School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

2002

#### UNIVERSITY OF PITTSBURGH

## SCHOOL OF ENGINEERING

This thesis was presented

by

Matthew J. Volkar

It was defended on

December 9, 2002

and approved by

William W. Clark, Associate Professor, Mechanical Engineering

Ronald G. Hoelzeman, Associate Professor, Electrical Engineering

Thesis Co-Advisor: James T. Cain, Professor, Electrical Engineering

Thesis Co-Advisor: Marlin H. Mickle, Nickolas A. DeCecco Professor, Electrical Engineering

## ABSTRACT

#### TUNING AND CONTROL OF AN ON-CHIP PIEZOELECTRIC RESONATOR

Matthew J. Volkar, MS

University of Pittsburgh, 2002

From clock signals for digital circuits to frequency references and voltage controlled oscillators for communication systems, oscillators are a fundamental element in many electronic circuits. With the current trend toward smaller and more tightly integrated systems, many applications would benefit greatly from the ability to integrate an oscillator onto a chip.

In this thesis, we describe the design and development of a new oscillator technology which makes use of a piezoelectric resonator for frequency control. By using a specially constructed piezoelectric structure, the proposed design exhibits several significant advantages over other currently available technologies, including the ability to be manufactured on a silicon substrate. This document presents the design of the tuning and control circuitry for such a resonator as well as experimental results with a macro-scale prototype. Details of a truly single-chip oscillator solution, including the design of on-chip capacitors, switches and an amplifier, are also presented. Tuning of the prototype resonator structure is accomplished electrically, and the design has shown frequency tuning of up to 1.5% of the nominal value with a theoretical limit of 40% given the appropriate resonator design.

#### ACKNOWLEDGEMENTS

A special thanks Dr. J.T. Cain and Dr. Marlin Mickle of the Electrical Engineering department for their support and guidance throughout this project. I would also like to thank Dr. William Clark and Muturi Muriuki of the Mechanical Engineering department for their assistance with the mechanical aspects of the design. Without the efforts of all of these people, this research would never have been possible.

Additional thanks are extended to Dr. William Clark and Dr. Ronald Hoelzeman for their efforts in serving on this committee.

This project was sponsored in part by a contract with the Pittsburgh Digital Greenhouse titled "SOC Frequency Synthesis and Control for Radio Frequency Communication: Development of Novel Hardware and Design Flow".

# **TABLE OF CONTENTS**

|     |                                 | Page |

|-----|---------------------------------|------|

| 1.0 | Introduction and Motivation     | 1    |

| 1.1 | 1 Crystal Oscillators           | 1    |

| 1.2 | 2 Non-Crystal Oscillators       | 5    |

| 2.0 | Problem Statement               |      |

| 2.1 | 1 Oscillator Requirements       |      |

| 2.2 | 2 Scope of This Thesis          |      |

| 3.0 | Background                      |      |

| 3.1 | 1 Piezoelectric Effect          |      |

| 3.2 | 2 Mechanical Resonators         | 15   |

| 3.3 | 3 Oscillator Design             | 17   |

| 4.0 | System Specifications           |      |

| 4.1 | 1 Piezoelectric Resonator       |      |

| 4.2 | 2 Tuning Network                |      |

| 4.3 | 3 Phase Shift Network           |      |

| 5.0 | System Modeling                 |      |

| 5.1 | 1 Electrical/Mechanical Analog  |      |

| 5.2 | 2 Equivalent Circuit            |      |

| 6.0 | Prototype Implementation        |      |

| 6.1 | 1 Mechanical Design             |      |

| 6.2 | 2 Equivalent Circuit Simulation |      |

| 6.3 | 3 Electrical Design             |      |

| 6.4 | 4 Experimental Results          |      |

| (   | 6.4.1 Capacitive Tuning         |      |

| (   | 6.4.2 Modal Switching           |      |

| 6.4      | .3      | Temperature Stability          | 46 |

|----------|---------|--------------------------------|----|

| 7.0 Inte | egrated | d Circuit Design               | 48 |

| 7.1      | Amp     | olifier                        | 48 |

| 7.1      | .1      | Circuit Design                 | 49 |

| 7.1      | .2      | Simulation and Layout          | 53 |

| 7.2      | Tuni    | ing Capacitors                 | 56 |

| 7.2      | .1      | Capacitor Design               | 56 |

| 7.2      | .2      | Layout and Fabrication Results | 60 |

| 7.3      | Ana     | log Switches                   | 62 |

| 7.3      | .1      | Pass Transistor Design         | 62 |

| 7.3      | .2      | Layout and Fabrication Results | 64 |

| 8.0 Su   | mmary   | v and Conclusion               | 66 |

| 8.1      | Sum     | mary of Advancements           | 66 |

| 8.2      | Adv     | antages and Applications       | 67 |

| 8.3      | Futu    | re Work                        | 67 |

| Append   | ix A    |                                | 70 |

| Append   | ix B    |                                | 72 |

| Bibliog  | raphy . |                                | 76 |

# LIST OF TABLES

# Page

| Table 1: A Comparison of Parameters for Various Oscillators         | 11 |

|---------------------------------------------------------------------|----|

| Table 2: Capacitor Values for the Electrical Equivalent Circuit     | 30 |

| Table 3: Usable Resonant Frequencies to 10kHz                       | 44 |

| Table 4: Transistor Sizes for Integrated Circuit Amplifier          | 54 |

| Table 5: Inter-Layer Capacitance Parameters for the AMI ABN Process | 57 |

| Table 6: 22.5pF Capacitor Fabrication Results.                      | 60 |

# LIST OF FIGURES

|                                                                       | Page |

|-----------------------------------------------------------------------|------|

| Figure 1.1: Methods of Cutting a Quartz Crystal                       | 2    |

| Figure 1.2: Basic Circuit for a Quartz Crystal Oscillator             | 2    |

| Figure 1.3: The Inverted Mesa Crystal Design                          | 3    |

| Figure 1.4: Typical Packaging of a Quartz Crystal                     | 5    |

| Figure 1.5: An LC Tank Circuit                                        | 6    |

| Figure 1.6: A Basic Three Stage Ring Oscillator                       | 7    |

| Figure 1.7: Current Starved Voltage Controlled Oscillator             | 8    |

| Figure 3.1: Basic Operation of the Piezoelectric Effect               | 13   |

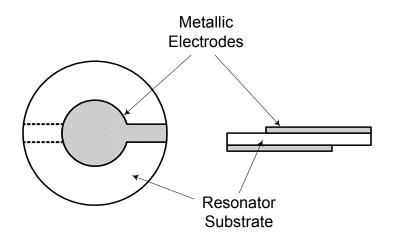

| Figure 3.2: Example Quartz Crystal Blank                              | 15   |

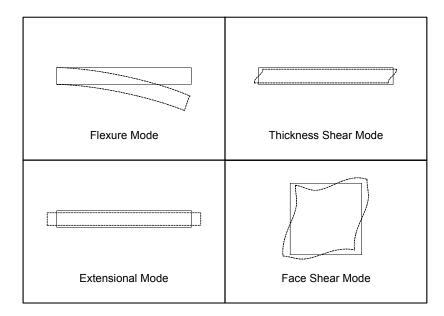

| Figure 3.3: Modes of Motion for a Mechanical Structure                | 16   |

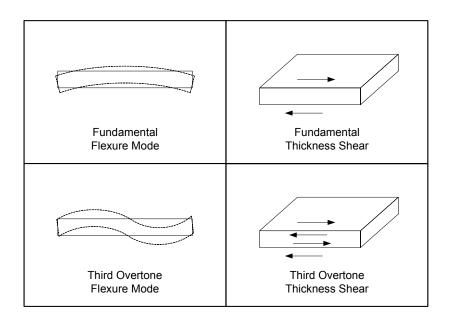

| Figure 3.4: Overtones of Some Common Modes                            | 17   |

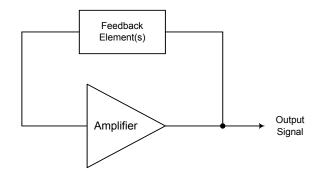

| Figure 3.5: Basic Structure of an Oscillator Circuit                  | 18   |

| Figure 3.6: Effects of Differing Loop Gain                            | 18   |

| Figure 3.7: Effects of Incorrect Loop Phase                           | 19   |

| Figure 4.1: Proposed Oscillator Basic Architecture                    | 21   |

| Figure 4.2: Possible Structures for the Piezoelectric Resonator       | 22   |

| Figure 4.3: Capacitive Shunting of the Passive Segment                | 24   |

| Figure 4.4: Simple Shunt Capacitor Configuration                      | 25   |

| Figure 5.1: Basic Mechanical Model of the Resonator                   | 27   |

| Figure 5.2: Basic Series RLC Circuit                                  | 29   |

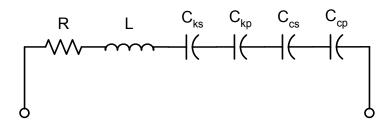

| Figure 5.3: Motional Equivalent Circuit for the Resonator             | 31   |

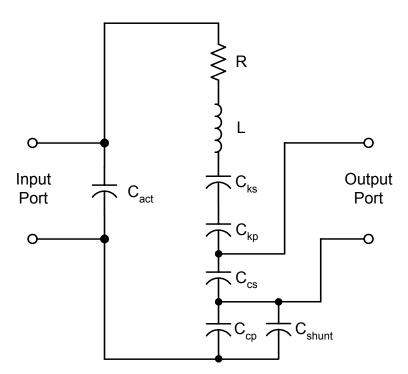

| Figure 5.4: Equivalent Circuit with Input/Output Ports and Shunt      | 32   |

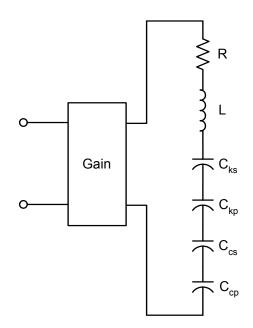

| Figure 5.5: Introduction of Gain Block to Motional Branch             | 33   |

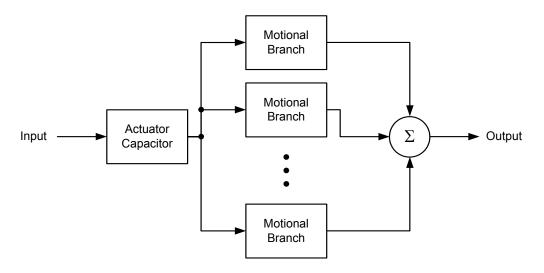

| Figure 5.6: Block Diagram Representing the Overall Equivalent Circuit | 34   |

| Figure 6.1: Basic Layout of the Cantilever Beam                                    | 36 |

|------------------------------------------------------------------------------------|----|

| Figure 6.2: Picture of the Prototype Resonator                                     | 37 |

| Figure 6.3: Frequency Response of Prototype Resonator to 10kHz                     | 38 |

| Figure 6.4: SPICE Equivalent Circuit Frequency Response                            | 39 |

| Figure 6.5: Basic Amplifier Circuit                                                | 40 |

| Figure 6.6: Variable Phase Shift Circuit                                           | 41 |

| Figure 6.7: Frequency vs. Tuning Capacitance for Third Mode                        | 43 |

| Figure 6.8: Resistance vs. Frequency for the Phase Shift Network                   | 45 |

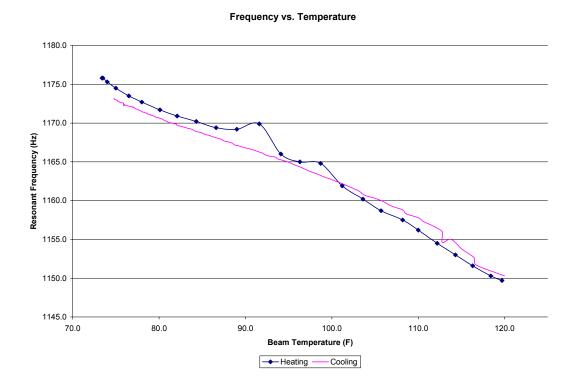

| Figure 6.9: Frequency vs. Temperature for Third Mode                               | 46 |

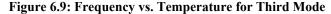

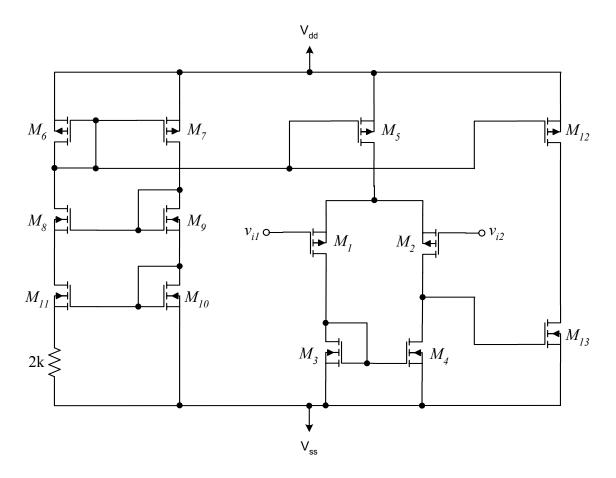

| Figure 7.1: Basic CMOS Differential Pair                                           | 49 |

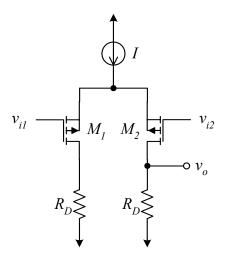

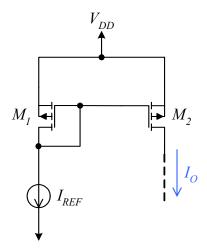

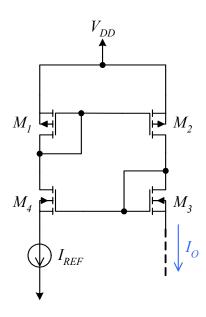

| Figure 7.2: Basic CMOS Current Mirror                                              | 50 |

| Figure 7.3: Cascode Current Mirror                                                 | 51 |

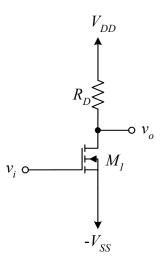

| Figure 7.4: Basic Common Source Amplifier                                          | 52 |

| Figure 7.5: Complete Two Stage Amplifier Design                                    | 53 |

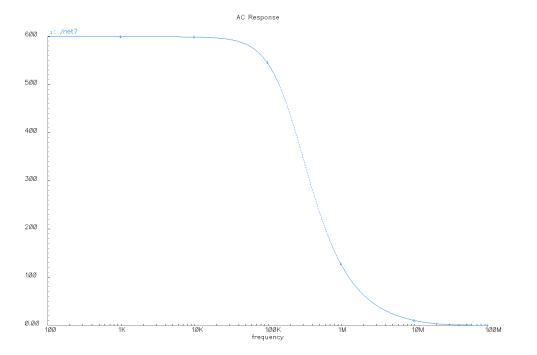

| Figure 7.6: SPICE Simulation Results for Two Stage Amplifier                       | 54 |

| Figure 7.7: Two Stage Amplifier Layout                                             | 55 |

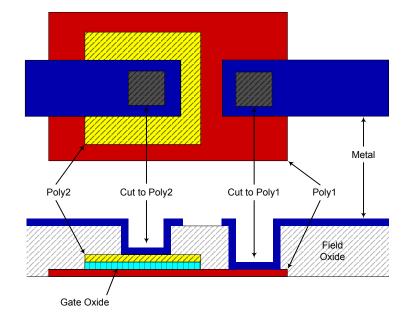

| Figure 7.8: Poly-to-Poly Capacitor Construction                                    | 56 |

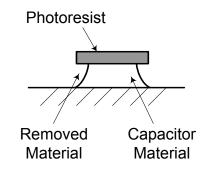

| Figure 7.9: Example of the Effect of Over-Etching                                  | 58 |

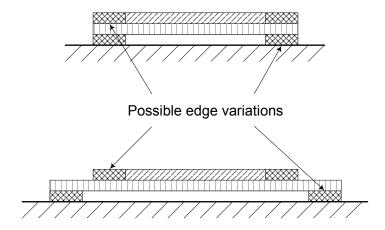

| Figure 7.10: Design Using Larger Bottom Plate to Reduce the Effect of Over-Etching | 59 |

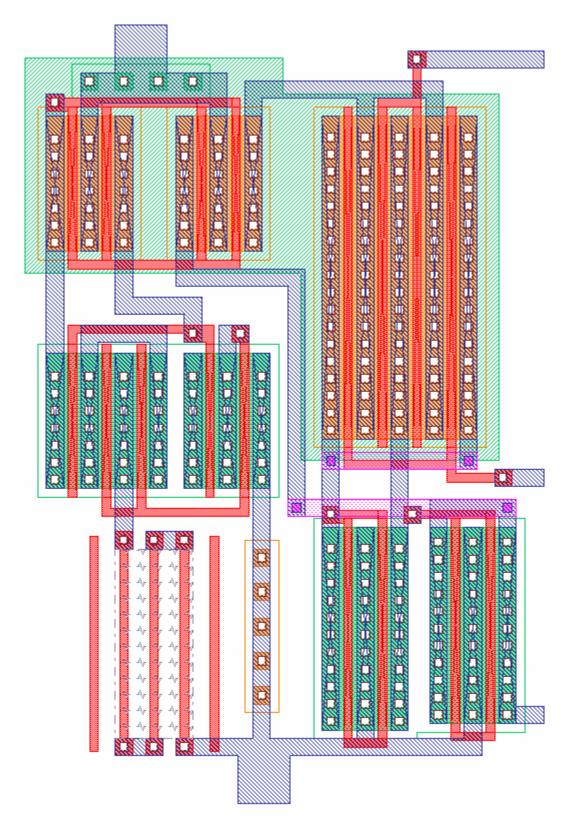

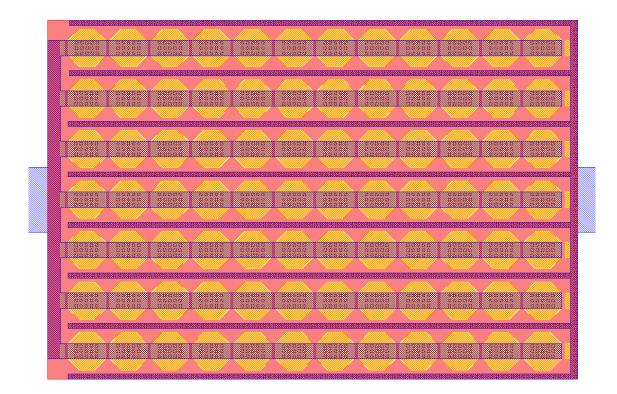

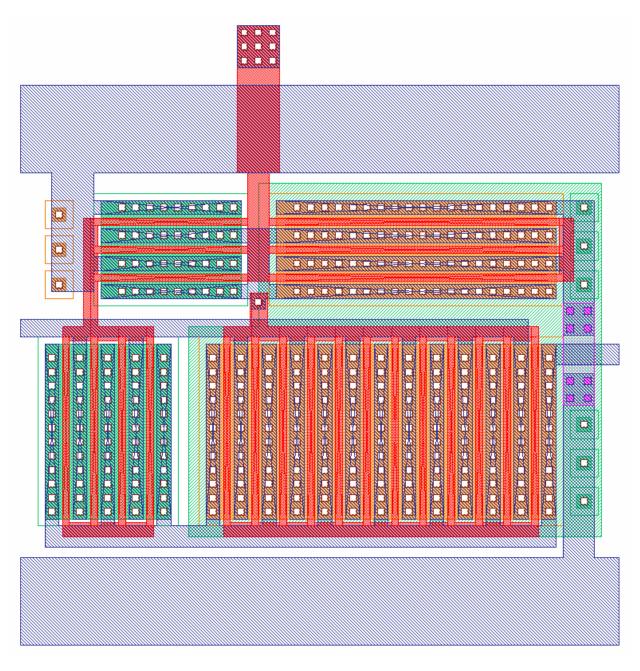

| Figure 7.11: 22.5pF Capacitor Layout using Octagons                                | 61 |

| Figure 7.12: 22.5pF Capacitor Layout using Squares                                 | 61 |

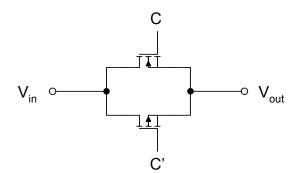

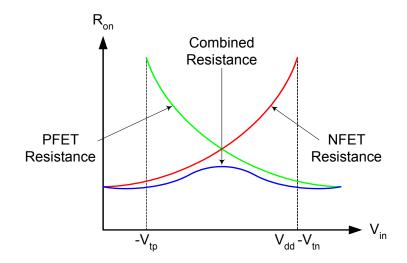

| Figure 7.13: CMOS Pass Gate                                                        | 63 |

| Figure 7.14: Resistance of PFET, NFET, and Complementary Type Switches             | 63 |

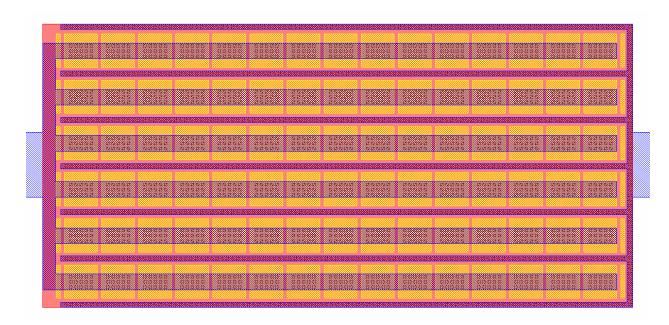

| Figure 7.15: Layout of CMOS Pass Gate with Integrated Inverter                     | 65 |

## **1.0 INTRODUCTION AND MOTIVATION**

The use of oscillators is fundamental to many areas of analog and digital circuit design. Oscillators are used to provide everything from frequency references for RF communication to clock signals for digital systems, and each type of application has a need for specific features and performance requirements. To meet these needs, oscillator designs have typically been divided into two categories: crystal controlled and non-crystal controlled. Crystal controlled oscillators make use of a crystal structure to govern the oscillation while non-crystal oscillators depend on more traditional electrical components such as inductors and capacitors or logic gates. In this thesis, we will present the design and development of a new oscillator technology that demonstrates a useful combination of the features and benefits of each of these two alternatives. The remainder of this chapter will provide additional information regarding these two oscillator types in order to provide a foundation upon which the new design will be built.

## **1.1 Crystal Oscillators**

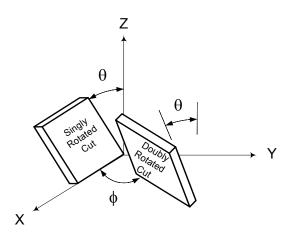

Crystal oscillators use the physical properties of a crystal structure to maintain the desired frequency of oscillation. The most common type of crystal oscillator uses a specially cut quartz crystal, and its frequency is determined by the physical dimensions and cut of the crystal. The cut of a quartz crystal refers to the angle at which it has been cut relative to the alignment of the crystal lattice. Since quartz crystals are anisotropic, meaning that their properties vary greatly with direction, this "cut" can have a large impact on the resulting oscillator characteristics such as frequency, quality factor<sup>1</sup>, and temperature stability. Many different crystal cuts have been explored for their various properties, but nearly all high stability oscillators utilize the AT and SC cuts. Both of these cuts are temperature compensated, which means that their first order temperature coefficients are zero and only higher order effects contribute to their small frequency/temperature dependence. Crystal cuts can either be singly rotated or doubly rotated as depicted in Figure 1.1. The AT cut is a singly rotated cut with an angle  $\theta$  of 35.25° with respect to the z-axis while SC-cut crystals are doubly rotated, with a  $\theta$  of 34.11° and a  $\phi$  of 21.93° [1].

<sup>&</sup>lt;sup>1</sup> Also known as Q, oscillator quality factor is defined as the nominal frequency divided by the 3dB bandwidth and is used as a measure of the frequency stability of the oscillator

Figure 1.1: Methods of Cutting a Quartz Crystal

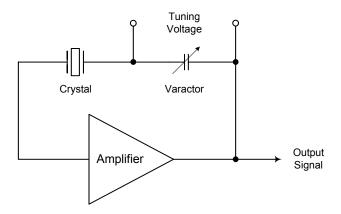

The major advantages of a crystal controlled oscillator are the extremely high quality factors that are attainable, on the order of  $10^4$ - $10^6$  [2], as well as their excellent frequency/temperature stability. Oscillators with a high Q exhibit much better frequency stability, which allows them to be used in applications that require a high precision frequency reference. The frequency/temperature stability of an oscillator defines the ability of the oscillator to maintain its frequency in the face of changes in temperature. Crystal oscillators typically exhibit very small changes in frequency due to temperature variation, and these changes can be compensated for relatively easily. The simplest method of temperature compensation is shown in Figure 1.2 where a variable reactance, typically a varactor, is placed in series with the crystal.

Figure 1.2: Basic Circuit for a Quartz Crystal Oscillator

This reactance can then be used to make small adjustments to the frequency of oscillation in response to temperature change. Other methods of temperature compensation include ovencontrolled crystal oscillators where the crystal structure is maintained at a constant temperature by placing it in an oven. By maintaining the temperature of the crystal at a specific value, any variations in frequency due to temperature change are eliminated. Because this type of design is more complicated and requires more power, it is typically only used in cases where extreme stability is required. While the two characteristics of quality factor and temperature stability are important in many applications, there are also limitations to the use of crystal oscillators that make them undesirable for other applications.

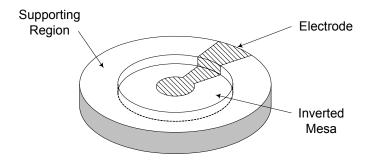

Being based on a mechanical structure, there are restrictions on the size of the crystal that can be cut without sacrificing the manageability of the resulting structure. That is, if a high frequency oscillator is desired, the size of the structure becomes so small that it can be easily broken due to the brittleness of the quartz material. To alleviate this problem, crystal manufacturers have begun using an inverted mesa design where the edges of the crystal are thicker than the center. This design is shown in Figure 1.3 and is useful because it allows the center of the blank to be manufactured much thinner while still providing the structural support

Figure 1.3: The Inverted Mesa Crystal Design

necessary for mounting the crystal. The use of this type of design increases the maximum frequency of a quartz oscillator, but this maximum is still in the range of 300MHz for fundamental mode crystals [3]. Frequencies above this limit are possible using  $3^{rd}$  or  $5^{th}$  overtone crystals, but these oscillators still exhibit many of the problems associated with

fundamental mode crystals, simply at a higher frequency. An overtone crystal is a crystal that has been manufactured so as to obtain oscillation at the odd harmonics of its fundamental frequency. So, while fundamental mode crystals reach a limit at around 300MHz, the maximum frequency of overtone crystals can reach into the gigahertz range. An additional implication of the dependence of frequency on size is that crystals are manufactured only in commonly used frequencies and, therefore, cannot be used in designs that require any arbitrary frequency. Compounding this fact is the limited tunability of a crystal oscillator, which is typically on the order of 50 parts-per-million (ppm) [4]. While this tuning range is sufficient for temperature compensation as was discussed previously, it is insufficient to make up for the lack of available crystal frequencies.

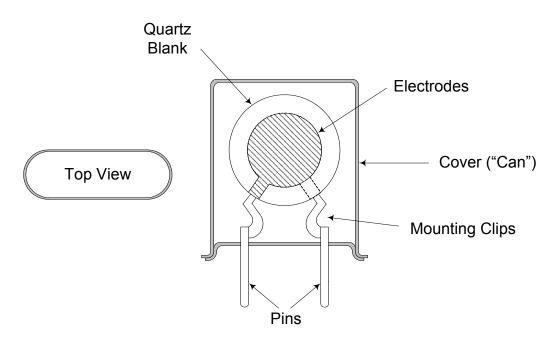

All of these considerations aside, however, the most significant drawback to the use of crystal controlled oscillators is the inability to fabricate these structures as part of an integrated circuit. The reasons for this inability are related to the manufacturing processes involved in building a quartz crystal. First, as discussed above, it is not possible to manufacture a quartz crystal that is comparable in size to that of an integrated circuit. This fact alone would prevent their integration, but even if it were possible to build such small crystals, it would be prohibitively expensive to integrate these crystals onto a chip. Because a quartz crystal must be carefully cut and sized, the crystal structure would have to be manufactured separately from the circuit and mechanically attached at a later time. This requirement of manufacturing the circuit and resonator separately and then combining them presents the biggest obstacle to constructing a single chip crystal oscillator. Due to their manufacturing characteristics, quartz crystals are typically packaged in a small metal can, as shown in Figure 1.4, and require relatively complex oscillator circuits. These circuits often involve a number of discrete components, which can result in a significant amount of space being required on a printed circuit board. Since many oscillators are used in applications where there is a severe space constraint, for example cellular telephones or handheld electronics, the ability to build the entire oscillator circuit on a single chip would be extremely beneficial. Historically, it has been this inability to manufacture fully integrated crystal oscillators that was the main driving force behind the development of alternative non-crystal oscillators.

Figure 1.4: Typical Packaging of a Quartz Crystal

## **1.2 Non-Crystal Oscillators**

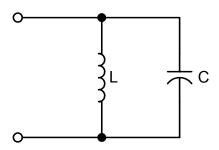

To overcome some of the limitations of crystal controlled oscillators, most importantly that of the integrability of those designs, several types of non-crystal oscillator have been developed. Some examples of this type of oscillator include LC resonant tanks, ring oscillators, and voltage controlled oscillators. An LC tank circuit, such as shown in Figure 1.5, uses the natural resonance of an inductor-capacitor pair and can thus be designed to oscillate at virtually any desired frequency. The resonant frequency of a tank circuit is given by Equation (1.1).

$$f = \frac{1}{2\pi\sqrt{LC}} \tag{1.1}$$

As can be seen from this expression, the frequency is directly dependent upon the values of the inductor and capacitor components and the tolerances of these components can then become a limitation. For example, on-chip inductors and capacitors have historically had tolerances of 20% [5], which means that it can be extremely difficult to obtain the desired frequency with any degree of accuracy using an LC tank. Assuming only a 5% variation in components, which is

Figure 1.5: An LC Tank Circuit

often considered good for inductors and capacitors, the frequency of this type of oscillator would also vary by as much as 5%. This variability in the design not only means that the frequency will be off by as much as the specified amount, but that the resulting frequency will lack repeatability. For mass produced oscillators, repeatability is an important factor that can greatly impact the usability of the design. It is for this reason that LC oscillators are typically used in applications where an exact frequency is not a specific requirement. Another difficulty associated with the use of on-chip LC oscillators is the relatively large amount of area consumed by these designs. Integrated circuit designers typically try to limit the values of inductor and capacitor components used on-chip due to their large area requirement. Since the frequency of oscillation for an LC tank circuit is inversely proportional to the component values, this area limitation requires that the circuit operate at high frequencies. For this reason, typical on-chip LC oscillators operate in the gigahertz range. The quality factors of LC oscillators in this frequency range are extremely poor, however, with Q's on the order of 10 being common due to the poor quality of on-chip inductors [6]. While the use of an LC oscillator circuit eliminates some of the problems associated with crystal oscillators, their low quality factors and large area requirements, along with the difficulty in producing accurate frequencies, limit their usefulness.

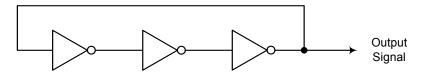

Oscillator designs that make use of digital circuits, such as ring oscillators, can avoid some of the limitations of on-chip LC oscillators by utilizing CMOS transistors in the place of inductor and capacitor components. A ring oscillator circuit, shown in Figure 1.6, can be constructed entirely of CMOS transistors and is easily manufactured on an integrated circuit. As shown in the figure, this type of circuit consists of a series connection of inverters, which results in an oscillation because of the feedback path. Without this feedback, the circuit would simply operate

Figure 1.6: A Basic Three Stage Ring Oscillator

as a standard inverter that introduces a propagation delay proportional to the number of stages. By inserting the feedback path, the circuit exhibits oscillatory behavior due to the fact that the input and output are of opposite polarity but are connected together. As we will explain later, an oscillator design must exhibit a phase shift of  $0^{\circ}$  or  $360^{\circ}$  in order to function. Since the input and the output of the ring are of opposite polarity, they could be considered  $180^{\circ}$  out of phase. An additional phase shift is introduced due to the propagation delay through the stages of the ring, and the resulting oscillation will occur at the frequency at which the total delay accounts for an additional  $180^{\circ}$  of phase shift. The expression for determining this frequency is given by Equation (1.2).

$$f = \frac{1}{2Nt_{pd}} \tag{1.2}$$

Although they are easily integrable, there are also disadvantages to the use of ring oscillator circuits. Due to the fact that a ring oscillator is fundamentally a digital circuit, the output waveform is typically a square wave, which is undesirable for many oscillator applications as it can introduce unwanted signal harmonics. Further, the frequency of oscillation is determined by the parameters N and  $t_{pd}$  which correspond to the number of stages and propagation delay of a stage respectively. This formulation imposes limits on the frequencies that are possible using ring oscillator designs. For example, if the design uses minimum size inverters (which have the largest delay), increasing the number of stages is the only available method of slowing the oscillator. For this reason, low frequency oscillators are typically not feasible using a ring oscillator circuit due to the large number of stages and subsequent die area that would be required. Illustrating the relatively large number of stages that would be required, a ring oscillator circuit using 31 minimum size stages operates at a frequency of roughly 40MHz in the AMI ABN 1.5µm process [7]. The frequency of this same circuit would be significantly higher in today's advanced deep sub-micron fabrication technologies due to their significantly lower

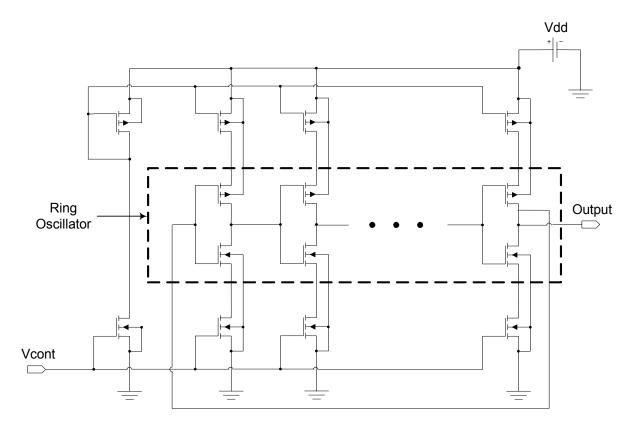

propagation delays. In order to increase the frequency of a ring oscillator, we can reduce the number of stages to the minimum of three, but to further increase this frequency we must resort to lowering the propagation delay of each stage. This can be accomplished by increasing the sizes of the transistors used in the inverters but again increases the die area consumed by the design. Furthermore, there is a physical limit to the speed at which an inverter can switch, which will limit the maximum frequency possible in a given fabrication technology. Similar to crystal controlled oscillators, which have a very small tuning range, ring oscillator circuits are typically completely non-tunable, except in the case of specially designed voltage controlled configurations. By using what is known as a current starved ring oscillator, as shown in Figure 1.7, we can vary the oscillation frequency by varying a control voltage. In the design shown, lowering the control voltage limits the current available to the inverters in the ring and therefore increases their propagation delays. This increase in propagation delay results in a decrease in the

Figure 1.7: Current Starved Voltage Controlled Oscillator

frequency of oscillation for the circuit. These voltage controlled oscillators (VCOs) typically exhibit poor frequency stability, however, and are only used where their wide frequency range is required. As was the case with LC oscillators, we again see that these alternative types of circuits improve on some of the deficiencies of crystal designs, but do not offer a compelling alternative to those circuits.

#### 2.0 PROBLEM STATEMENT

Given the limits of existing oscillator technology, it is desirable to develop a new type of oscillator that does not exhibit the same limitations. The most significant problem associated with current technology is the inability to construct precise, high quality oscillators as part of an integrated circuit. Today's high precision oscillator designs, such as quartz oscillators, cannot be built on-chip, while those that can be easily integrated exhibit relatively poor performance or other significant limitations. In this thesis, a new method of on-chip frequency synthesis is proposed that makes use of a micro-scale piezoelectric resonator. Using this resonator, we design and test an oscillator that exhibits good performance as well as the scalability required to make it a viable on-chip solution.

## 2.1 Oscillator Requirements

In order for an on-chip piezoelectric oscillator to become a practical alternative to the more traditional techniques, several issues must be considered. These factors include the possible frequency range, the size and complexity of the control circuit, the performance of the oscillator, and the ability to easily and inexpensively manufacture these devices. The requirements of the oscillator proposed in this thesis bridge the gap between those of the alternatives available in typical crystal and non-crystal designs. It is our intention to design, fabricate, and test a new oscillator technology that will exhibit many of the advantages of a crystal controlled oscillator while providing features not typically found in either of the two alternatives. Of considerable importance to this design is the ability to scale the resonator structure, along with necessary tuning and control circuitry, such that it can be constructed on a single integrated circuit. Since the most significant drawback to the use of standard crystal controlled oscillators is the inability to fabricate them on an integrated circuit, this scalability is one of the most important features of our proposed design. As was discussed briefly in Section 1.1, it is not strictly a size limitation that prevents crystals from being utilized on-chip. The ability to manufacture these devices as an integrated part of the design is also lacking. For this reason, it is not only necessary for the new design to be scalable, but it also must be easily constructed on-chip using CMOS compatible processing techniques.

Other features to be incorporated into the proposed design are the ability to switch and tune the frequency of operation dynamically using an electrical input. While the ability to build an oscillator of any arbitrary frequency, as is possible with an LC tank, is desirable, it is often not feasible when using a mechanical resonator. In the case of our oscillator design, the alternative is a single mechanical resonator that can operate at multiple frequencies and/or be tuned throughout a significant range. The increased tuning range of this design, along with its ability to switch nominal frequencies, makes its use possible in applications that do not typically utilize a crystal oscillator. A further concern of this new design is the frequency/temperature stability. As mentioned earlier, specific cuts of quartz, such as AT and SC, exhibit a very small frequency/temperature dependence that makes them ideal for many applications. In order to be competitive with these types of oscillators, the new design must exhibit good temperature stability or the ability to easily compensate for temperature changes. In the new design, temperature compensation can be implemented by making use of the large tuning range of the new oscillator. Table 1 summarizes some of the parameters of crystal and non-crystal oscillators as well as that of the design presented in this thesis. It is important to note that the parameters

|            | Crystal                  | LC                    | Ring                   | Prototype                | Theoretical              |

|------------|--------------------------|-----------------------|------------------------|--------------------------|--------------------------|

| Frequency  | $10^3 - 10^8 \text{ Hz}$ | $10^8$ - $10^{10}$ Hz | $10^{6}$ - $10^{8}$ Hz | $10^2 - 10^4 \text{ Hz}$ | $10^3 - 10^8 \text{ Hz}$ |

| Q          | $10^3 - 10^6$            | <20                   | N/A                    | >100                     | $10^2 - 10^5$            |

| Tunability | <50ppm                   | Varies                | None                   | ~1.5%                    | 40%                      |

| Size (mm)  | 8x8x2.5                  | On-chip               | On-chip                | 16x57x0.3                | On-chip                  |

Table 1: A Comparison of Parameters for Various Oscillators

presented in this table are typical values and that those of the proposed design are included for both the prototype, which will be discussed later, as well as the theoretical performance limits of the design.

## 2.2 Scope of This Thesis

The focus of this thesis is the tuning, control, and electrical modeling of a piezoelectric resonator. Issues related to the mechanical properties of the resonator will be discussed only in cases where they directly influence the electrical control of the system or help to further illustrate the design of the oscillator. Modeling of the structure itself will be approached from the perspective of electrical/mechanical analogies with the end result being an equivalent circuit model that will be used in simulating the oscillator design. Design of the remainder of the oscillator circuit will be discussed in terms of off-the-shelf components, which are used in the prototype design, but will also include a description of the steps involved in integrating the design onto a chip. This description will highlight the design and implementation of a single integrated circuit that contains the tuning and control electronics necessary for the oscillator design. A demonstration of the abilities of this new design will be shown via electrical simulation as well as experimentally through the results of testing on a macro-scale prototype. A summary and conclusion will include a discussion of some of the applications for such an oscillator design as well as areas of future consideration.

#### **3.0 BACKGROUND**

In order to more fully understand the design presented in this thesis, it is necessary to have a fundamental understanding of several basic concepts that are important to oscillator design. The two most important concepts, which will be relied upon heavily in the remainder of this thesis, are the piezoelectric effect and the concept of mechanical resonance. Without either of these two properties, the design and construction of the proposed oscillator would be impossible. The remainder of this chapter will be devoted to a detailed discussion of these two concepts as well as the fundamentals of basic oscillator design.

## 3.1 Piezoelectric Effect

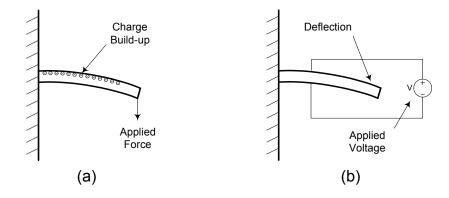

The piezoelectric effect describes the interaction between mechanical stress and electrical charge that occurs in certain materials. In these materials, a mechanical stress on the material generates an electrical charge in proportion to the magnitude of the stress. Conversely, an electric charge placed on the material will induce a mechanical stress. The piezoelectric effect, in both of its forms, is illustrated in Figure 3.1. In Figure 3.1(a), an applied stress in the form of a deflection has created an electrical charge on the surface of the material. The opposite effect is shown in Figure 3.1(b) where an applied voltage has caused a deflection in the material. Piezoelectric materials were first discovered in 1880 by Jacques and Pierre Curie who observed that, when a weight was placed on a quartz crystal, charges appeared on the crystal surface [4].

Figure 3.1: Basic Operation of the Piezoelectric Effect

This interaction between electrical and mechanical forces is known as electromechanical coupling and the value which relates charge and stress is known as the coupling factor. The coupling factor is a measure of the ability of a piezoelectric material to convert energy from its mechanical to electrical form and vice versa. A higher coupling factor implies that the material is more efficient in this energy conversion process, that is, that a given stress will generate more electrical charge. This electromechanical coupling is an extremely important part of the proposed oscillator design, where it provides both the interface between the electrical circuit and the mechanical structure, as well as the ability to tune the resonant frequency of the structure.

Since its discovery, the piezoelectric effect and materials which exhibit it have become widely used in many areas, including various types of electromechanical transducers such as pressure and flow sensors. More familiar applications of the piezoelectric effect include "click" lighters and common quartz wristwatches. In a so-called click lighter, pressing the ignition button places pressure on a piezoelectric material which, due to the piezoelectric effect, creates an electric charge. This charge is used to create a small spark that then ignites the lighter's fuel. The advantages of using a piezoelectric material in this application are the elimination of moving parts such as a flint sparker or expendable resources such as a battery. Under normal operation, the piezoelectric material will not wear out or need to be replaced or recharged as would alternative options. In a quartz wristwatch, a crystal controlled oscillator circuit, as was discussed above, is used as the frequency reference for the timekeeping function. In this case, the relatively good accuracy and temperature stability of the quartz design is ideal for the application, which does not require extreme precision. This application is probably the most common, yet little known, application of the piezoelectric effect. In each of these examples, the electromechanical coupling is used to provide a function that would not be available without the piezoelectric material. In the wristwatch oscillator, the electromechanical coupling provided by the quartz crystal is used to interact with an electrical control circuit. By converting the mechanical motion of the crystal into electrical energy, the resonance of the quartz crystal can be used to govern the frequency of oscillation of the circuit. This use of a mechanical structure in an oscillator circuit is discussed further in the following section.

## **3.2 Mechanical Resonators**

Many oscillator designs, including the familiar quartz crystal oscillator discussed above, make use of a resonant mechanical structure. The basis for these designs is the fact that any given mechanical structure will demonstrate natural resonant frequencies that depend on the size, shape, and material properties of the structure. Through careful design of the structure, we can cause it to have a natural resonance at a specific frequency. Mechanical resonators can then be used in conjunction with, or in the place of, electrical components in an oscillator circuit. This is done by utilizing the electromechanical coupling of a piezoelectric material, such as a quartz crystal, to convert mechanical energy into electrical energy. The piezoelectric material can then be used as part of the structure or, in the case of most quartz oscillator designs, as the structure itself. The most common quartz crystal oscillators are mechanical resonators made of a single disc shaped piece of quartz crystal like that shown in Figure 3.2. This crystal structure is manufactured to a specific diameter and thickness based on the desired frequency, and designs of

Figure 3.2: Example Quartz Crystal Blank

this type have been demonstrated operating at frequencies into the gigahertz range [4]. In this design, an alternating voltage applied to the electrodes causes the quartz disc to deform an amount that is determined by the natural response of the crystal structure. This deformation is maximum at the resonant frequency and ideally falls off quickly at frequencies above and below

resonance. Quartz crystals have a high quality factor which means that the range of frequencies for which the magnitude of this motion is high is limited to a very narrow band. It is this property of quartz crystals that makes them ideal for use in oscillator applications.

Since every mechanical structure can exhibit multiple types of motion (e.g. bending, twisting, stretching), each structure will also have multiple resonant frequencies. These different types of motion are referred to as modes, with some of the more common modes being illustrated in Figure 3.3. As a result of the effects of structure size and shape on these different modes of oscillation, each mode shown in the figure will oscillate at a different frequency. This allows the designer the freedom to specify the frequency of operation for an oscillator design by choosing

Figure 3.3: Modes of Motion for a Mechanical Structure

the oscillation mode that will be used. Typical high frequency quartz oscillator designs make use of thickness shear mode, while lower frequency designs, such as those in wristwatches, use flexure mode [4]. Adding further flexibility to the design is the fact that each mode also exhibits overtones, which can be used to produce oscillators at higher frequencies than are possible using the fundamental mode. A mechanical overtone is similar to a harmonic in an electrical signal, except that the frequencies of mechanical overtones are not necessarily integer multiples of the fundamental. Examples of mechanical overtones for two common modes of oscillation are shown in Figure 3.4. Further discussion of these mechanical overtones will be presented in Chapter 4.0 where their use in the proposed design will be discussed.

Figure 3.4: Overtones of Some Common Modes

#### **3.3 Oscillator Design**

At the most basic level, an oscillator is simply an amplifier with a frequency dependent feedback network, which is used to control the frequency of oscillation. The block diagram for this basic configuration is shown in Figure 3.5. Expanding upon this simple description, two important conditions must be met in order for oscillation to occur within the circuit. First, the gain/loss through the combined amplifier and feedback loop must be greater than unity in order for the system to be self sustaining. If this condition is exactly met (i.e. gain equal to 1), the oscillator will reach a steady state oscillation. If this condition is not met, the response of the system will vary depending on whether the gain is greater or less than one. In the case of a gain less than one, the magnitude of the oscillation will decay toward zero and the oscillator will not

Figure 3.5: Basic Structure of an Oscillator Circuit

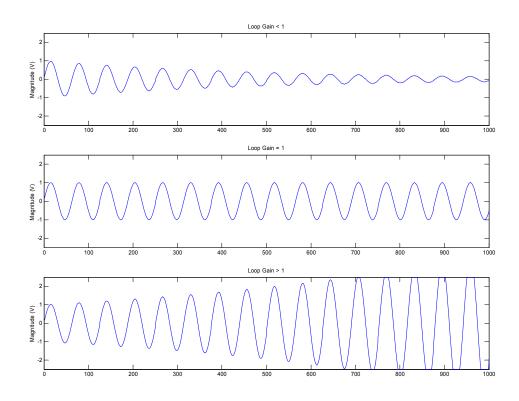

function. If the gain is greater than required, the magnitude of oscillation will increase until reaching the saturation voltage of the amplifier. The oscillation for each of these three conditions is shown in Figure 3.6. The first plot shows a loop gain less than one, the second a loop gain of exactly one, and the third a gain greater than one. Note that the signal begins to clip at the maximum amplifier voltage ( $\pm$  2.5V) for a gain greater than one.

Figure 3.6: Effects of Differing Loop Gain

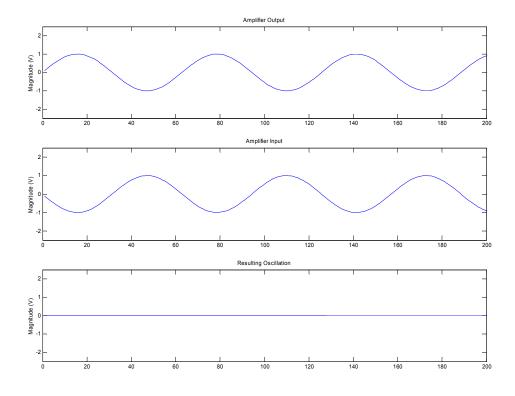

The second condition that must be met in an oscillator design involves the phase shift around the amplifier/feedback loop, which must be equal to  $0^{\circ}$  or  $360^{\circ}$ . This condition is important so that the energy fed back into the system adds to the total response. For example, if the loop phase was  $180^{\circ}$ , the energy that is fed back from the output to the input would interfere destructively therefore eliminating the oscillation. This effect is demonstrated in Figure 3.7. In this figure, the first plot represents the output signal from the amplifier while the second

Figure 3.7: Effects of Incorrect Loop Phase

represents the input signal. Note the phase difference of 180° between these two signals. In the figure, the third plot shows how these two signals would combine in the oscillator. Since the loop phase is not equal to 0°, the two signals interfere with each other thus preventing oscillation from occurring within the circuit. Henceforward the two conditions discussed above will be referred to as the amplitude and phase conditions, respectively.

While both crystal and non-crystal oscillators can be thought of as using the same basic structure, these two types differ in the method of providing feedback. In the case of a noncrystal oscillator the natural resonance of an inductor-capacitor pair, also known as an LC tank, is often used as the feedback element. Using this configuration, the LC tank governs the amplitude condition by attenuating those signals that are far from the natural resonant frequency of the inductor-capacitor pair. The LC tank circuit also introduces a phase shift of 90° at its resonant frequency, which must be compensated for in the circuit design. Ring oscillator circuits, on the other hand, control the frequency of oscillation by governing the phase condition. As was discussed earlier, this type of circuit oscillates at the frequency at which the total propagation delay through the ring is equal to half of the period of oscillation. This essentially adds a 180° phase shift that is then compensated for by the 180° introduced by the inverting nature of the circuit. These two shifts add to satisfy the phase condition of the oscillator. In a crystal controlled oscillator, the amplitude condition is governed by the crystal, which takes the place of the tank circuit in an LC oscillator. In this type of oscillator, it is the mechanical properties of the crystal which are used to attenuate signals occurring at frequencies other than the resonant frequency of the structure. As was the case in an LC oscillator, the crystal structure also introduces a 90° phase shift that must be accounted for in the oscillator circuit. We will use a similar property of our piezoelectric resonator to introduce the ability to dynamically switch the frequency of operation.

#### 4.0 SYSTEM SPECIFICATIONS

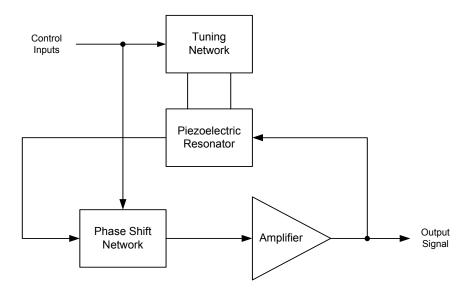

With a basic understanding of the principles of piezoelectricity, mechanical resonators, and oscillator design in hand, we can now develop the specifications of our new oscillator. These specifications will illustrate the details of the design as well as outline the functionality and performance of the resulting oscillator circuit. The fundamental architecture for this new design is illustrated in Figure 4.1. As discussed above, the most basic oscillator architecture consists of an amplifier with a feedback network. In order to meet the design requirements, the new

Figure 4.1: Proposed Oscillator Basic Architecture

oscillator maintains these portions, but it also expands upon this basic architecture to provide additional functionality. As can be seen in the above figure, there are two additional components in this new oscillator design: a phase shift network and a tuning network. It is these networks, in conjunction with the piezoelectric resonator, which provide this design with the additional features beyond those of a standard crystal controlled oscillator. This chapter will describe in greater detail the function of each of these components and the features that they enable. Further details regarding the implementation of this new architecture will be discussed in Chapter 6.0 where the prototype design is presented.

## 4.1 Piezoelectric Resonator

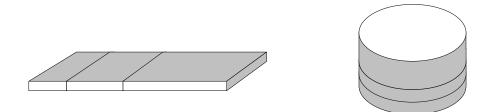

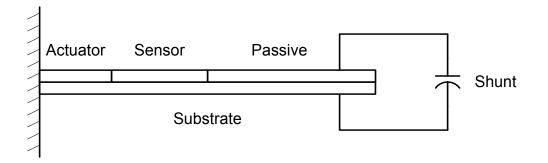

The main component of the feedback network for our new oscillator design is the piezoelectric resonator. This structure is designed to have a mechanical resonance at a specific frequency and consists of a multi-segment piezoelectric structure that is bonded to an elastic substrate. There are a several possible designs for this structure that will satisfy the requirements and the specific design chosen is not of particular importance to the techniques presented in this thesis. The design techniques used for the remainder of the tuning and control circuitry will remain the same regardless of the structure chosen, as long as this structure meets the specifications presented in this section. Two possible structure designs are shown in Figure 4.2, those of a cantilever beam and a stacked cylinder. Further, it is possible to design different size

Figure 4.2: Possible Structures for the Piezoelectric Resonator

structures which will exhibit similar properties and can thus be utilized in this oscillator design. While the overall goal of this research is to design and implement a single chip piezoelectric oscillator, a multi-step approach to the issue of structure size has been taken. The prototype structure, presented in Chapter 6.0, is the first step and will be followed by at least one intermediate size structure before realizing the goal of an on-chip solution. The scaling of the design to an on-chip structure is possible due to the properties of the materials being used. Unlike a quartz oscillator, which must be specially cut from a single quartz crystal in order to have piezoelectric properties, the materials used for this structure can be deposited on a substrate in the desired shape and the piezoelectric properties can then be introduced.

The important specification for this structure is that it contains three independent piezoelectric portions that have been designed with specific functions in mind. In contrast to a

standard quartz crystal, which is a two terminal device, the structure used for this oscillator is of a unique design with four terminals. The added terminals are necessary to interface to the additional portions of piezoelectric material, which provide the flexibility of the new design. The first piezoelectric element is used to drive the structure and will be connected to the output of the amplifier. This element converts the electrical energy from the amplifier into mechanical energy, which is stored in the motion of the structure. A second element is used to provide feedback for the system and converts the motion of the beam back into an electrical signal, which can be processed by the amplifier. The final element is not directly utilized by the amplifier circuit, but instead provides the tuning ability for the design. This tuning function will be discussed in more detail in the next section. These three piezoelectric elements will henceforward be known as the actuator, sensor, and passive portions of the structure.

When power is applied to the oscillator control circuit, electrical noise in the amplifier circuitry is sent into the actuator which induces small oscillations of the structure. Oscillations of a frequency other than the resonant frequency are significantly damped and, therefore, filtered out by the mechanical response of the structure. These small oscillations then produce an electrical signal in the sensor piezoelectric element that is fed back into the amplifier circuit. This electrical signal, which has now been amplified, is applied back to the actuator electrode which, in turn, increases the amplitude of oscillation. If the amplitude and phase conditions of the oscillator have been properly met, the system will begin to oscillate at one of the resonant frequencies of the structure. Using only the actuator and sensor portions in this manner, we would have an oscillator design very similar to that of a typical quartz oscillator. It is the addition of the passive portion of the structure, which is used to provide an interface to the frequency tuning network, that makes this design unique. The details of this interaction between the passive piezoelectric element and the tuning network are presented in the following section.

#### 4.2 **Tuning Network**

The tuning network, which interfaces with the passive piezoelectric element, makes it possible to tune the resonant frequency of the structure. This tuning is achieved by modifying the electromechanical coupling of the passive portion of the piezoelectric material. It has been found that by modifying the electrical circuit connected to a piezoelectric structure, the structure's mechanical properties can be modified [8]. In the case of our tuning network, this

modification is accomplished by capacitive shunting of the piezoelectric material. Figure 4.3 shows an example of how this might be implemented using a simple cantilever beam and a capacitor placed in parallel with the passive piezoelectric element. The mechanical oscillation of

Figure 4.3: Capacitive Shunting of the Passive Segment

a piezoelectric material would normally cause a build-up of electrical charge on the electrodes of the material, but by shorting these two electrodes, this charge is dissipated and the piezoelectric effect is eliminated. Eliminating the piezoelectric effect for the material has the effect of removing the electromechanical coupling, which affects the mechanical properties of the material. This causes a change in the equivalent stiffness of the structure and varies its resonant frequency. In addition to simply shorting the material, we can actively change its properties by using a capacitive shunt as shown in the above figure. When a capacitor is placed across the piezoelectric material, the electromechanical coupling is reduced because the charge generated by the motion is shared between the capacitance of the piezoelectric element and that of the shunt capacitor. By shunting in this manner, the resonant frequency is shifted to some point between that of the open and short-circuit cases.

While the prototype system exhibits a much smaller range, this type of resonator can be constructed such that the frequency change between open and short circuit is theoretically up to 40% of the open circuit frequency. There are many factors that affect this maximum range, including the size of the passive portion and its location on the structure. A structure with a larger passive portion, or with a passive portion located such that its stiffness contribution is a dominant factor in determining the resonant frequency, will exhibit a larger difference between

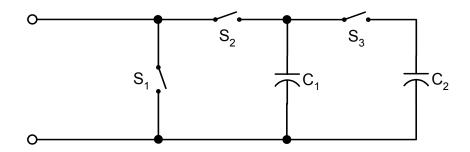

the open and short circuit frequencies. Since the relationship between shunt capacitance and frequency is non-linear, a small change in capacitance has a large effect on the frequency near the open circuit frequency, but has a much smaller effect near short circuit. To allow frequency adjustments with the desired resolution, a network of shunt capacitors is connected in parallel using electrically controllable switches. By closing a specific subset of these switches, we are creating an electrically variable capacitor, which is then used as the shunt capacitance. For example, the simple configuration of two switched capacitors as shown in Figure 4.4 can provide a total of four distinct frequencies, those of open and short circuit and two intermediate values.

Figure 4.4: Simple Shunt Capacitor Configuration

By leaving all switches open, the circuit operates at the open circuit frequency, while closing switch  $S_1$  will cause the circuit to operate at the short circuit frequency. Alternately, by closing only switch  $S_2$  we can cause the circuit to operate at a third frequency somewhere between open and short circuit and determined by the value of capacitor  $C_1$ . If we close both switches  $S_2$  and  $S_3$ , we get the fourth and final frequency which is determined by the parallel combination of capacitors  $C_1$  and  $C_2$ ,  $C_1+C_2$ . By increasing the number of capacitors and the complexity of their interconnection, we can produce an oscillator that is tunable to any accuracy required, limited only by the number of capacitors that can be feasibly integrated. Capacitors fabricated in a CMOS process, discussed in Section 6.4, are limited in size due to the die area consumed, which grows linearly with capacitor size.

## 4.3 Phase Shift Network

Recalling that one of the necessary conditions for an oscillator is the phase condition (i.e. loop phase equal to  $0^{\circ}$  or  $360^{\circ}$ ), the phase shift network of this oscillator design is intended to meet this requirement. At the most basic level, the phase shift network is used to provide the phase shift required to satisfy the phase condition at the resonant frequency of the structure. For example, if the structure exhibits a resonant frequency of 10kHz with a phase shift of  $90^{\circ}$ , the phase shift network would need to provide a shift of  $270^{\circ}$  or  $-90^{\circ}$  at that frequency in order to satisfy the phase condition. The phase shift network can be implemented in a variety of ways using passive components such as resistors and capacitors or using active circuits such as integrators and differentiators. Additionally, the amplifier itself can be used to provide phase shift by operating in the inverting configuration, which introduces a  $180^{\circ}$  shift. In the above manner, it can be relatively simple to sustain oscillation by introducing the phase required to satisfy the phase condition, however, by allowing the phase shift network to be variable, we introduce additional possibilities.

Recalling that a mechanical structure exhibits multiple resonant frequencies due to the various modes of motion, we can use the variable phase shift network to force the piezoelectric structure to oscillate in a specific mode. This network then makes it possible to quickly change the nominal frequency of oscillation for the system by changing the phase that is introduced and, therefore, the mode of oscillation. For example, consider a mechanical resonator that exhibits resonant frequencies of 5kHz and 15kHz and which introduces a phase shift of 90° at each frequency. By using a phase shift network that is frequency dependent, we can introduce a -90° shift at 5kHz, which will satisfy the phase condition and cause the oscillator to operate at that frequency. If we then modify the network to introduce a -90° shift at 15kHz instead, the system will begin to oscillate at the new frequency. Now, considering that any mechanical structure exhibits multiple resonances, we can use this phase shift network to produce a single oscillator design that can operate at multiple possible frequencies as required for this design.

#### 5.0 SYSTEM MODELING

In order to perform electrical simulations of this new oscillator design using SPICE<sup>2</sup>, it is necessary to have accurate electrical models of the components involved. While most components, such as the amplifier, tuning capacitors and phase shift network, are easily characterized, we must develop an equivalent circuit model for the piezoelectric resonator. This process involves examining the electrical/mechanical analogs for the system to determine the topology of the circuit and then extracting the equivalent circuit parameters. The steps used in developing this electrical model for our piezoelectric resonator are presented in this chapter.

## 5.1 Electrical/Mechanical Analog

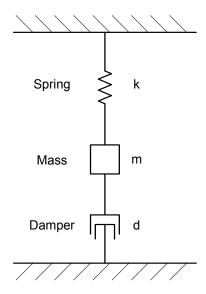

In modeling the piezoelectric resonator, it is important to remember that it is a mechanical structure that is forced to oscillate at a specific set of frequencies and can be modeled mechanically as a simple vibrating structure. The basic model for a vibrating mechanical structure is that of the mass, spring and damper shown in Figure 5.1. For this model, there are

Figure 5.1: Basic Mechanical Model of the Resonator

<sup>&</sup>lt;sup>2</sup> SPICE, or Simulation Program with Integrated Circuit Emphasis, is a general purpose circuit simulation program originally developed by the University of California at Berkeley

three fundamental parameters that determine the overall response: the mass of the system (m), the stiffness of the spring (k), and the damping of the damper  $(d)^3$ . Writing the equation of motion for this system we obtain Equation (5.1).

$$m\frac{d^2x}{dt^2} = F(t) - d\frac{dx}{dt} - kx(t)$$

(5.1)

Assuming that we do not apply any external forces to the system, the F(t) term goes to zero, and the system oscillates at its natural resonant frequency as governed by Equation (5.2).

$$\omega = 2\pi f = \sqrt{\frac{k}{m}} \tag{5.2}$$

With no external forces applied to the system, the magnitude of oscillation will decay toward zero at a rate proportional to the damping coefficient, d. If we now assume that the structure is made of a piezoelectric material, the expression of Equation (5.1) must be modified. The presence of the piezoelectric effect introduces the conversion of mechanical energy into electrical, and it is proportional to the displacement of the system. The new force introduced into the system due to this effect is given by Equation (5.3), where *C* is the physical capacitance of the piezoelectric material and  $\theta$  is its electromechanical coupling factor.

$$F(t) = \frac{\theta^2}{C} x(t) \tag{5.3}$$

Introducing this new term into the original equation of motion and setting the applied force equal to zero, we get an overall equation of motion that is given in Equation (5.4).

$$m\frac{d^{2}x}{dt^{2}} + d\frac{dx}{dt} + (k + \frac{\theta^{2}}{C})x(t) = 0$$

(5.4)

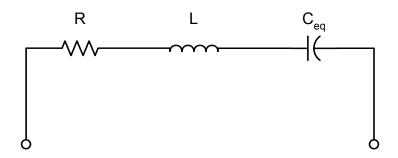

By examining this expression, we can see that it is a standard second order differential equation. From a basic understanding of circuit analysis, we recognize that this equation is of the same general form as that of the series RLC electrical circuit shown in Figure 5.2. Using Kirchoff's

<sup>&</sup>lt;sup>3</sup> The symbol typically used for damping is c, but to avoid confusion with capacitance C, we use d instead

Figure 5.2: Basic Series RLC Circuit

voltage law around the loop gives the differential equation shown in Equation (5.5).

$$L\frac{d^{2}q}{dt^{2}} + R\frac{dq}{dt} + \frac{1}{C_{eq}}q(t) = 0$$

(5.5)

By making an analog between charge and displacement, we can perform a mechanical to electrical conversion and thus develop an equivalent electrical circuit for our resonant mechanical structure.

While the above expressions are sufficient to develop an electrical model for a simple mechanical structure, the structure used in this oscillator design is more complicated. There are two important differences between our structure and that described above. First, our structure uses a piezoelectric layer bonded to an elastic substrate, which implies that there are two stiffness terms in the differential equation (or two springs in the mass/spring/damper model). Further, the piezoelectric layer is divided into three portions: actuator, sensor and passive, which requires that there be three coupling forces in the equation as well. However, due to the relatively small size of the actuator piezoelectric and its placement on the first prototype, we can neglect its electromechanically coupled contribution to the overall stiffness. Introducing these additional terms leaves us with the expression given in Equation (5.6) as the coefficient of the x(t) term.

$$k_{steel} + k_{piezo} + \frac{\theta_{sens}^2}{C_{sens}} + \frac{\theta_{pass}^2}{C_{pass}}$$

(5.6)

Recognizing the relationships between the coefficients of the mechanical and electrical differential equations discussed above, we can write three expressions relating the mechanical and electrical parameters. In our basic electrical circuit, which was shown in Figure 5.2, the three

electrical parameters are inductance (L), resistance (R) and capacitance (C). From a comparison of the coefficients of the mechanical and electrical equations, we develop the relationships given in Equations (5.7) through (5.9).

$$L = m \tag{5.7}$$

$$R = d \tag{5.8}$$

$$\frac{1}{C} = k_{steel} + k_{piezo} + \frac{\theta_{sens}^2}{C_{sens}} + \frac{\theta_{pass}^2}{C_{pass}}$$

(5.9)

We can break the capacitor value down further by noting that the equivalent capacitance of a series connection of capacitors is of the form shown in Equation (5.10).

$$\frac{1}{C_{eq}} = \frac{1}{C_1} + \frac{1}{C_2} + \dots + \frac{1}{C_n}$$

(5.10)

It follows that the expression of Equation (5.9) can be interpreted electrically as a series connection of four capacitors having the values given in Table 2. Having developed the relationships between the mechanical and electrical parameters, the following section will discuss the remainder of the electrical equivalent circuit.

Table 2: Capacitor Values for the Electrical Equivalent Circuit

| Name            | Description                                   | Value                        |

|-----------------|-----------------------------------------------|------------------------------|

| C <sub>ks</sub> | Stiffness contribution of the steel substrate | 1/k <sub>steel</sub>         |

| C <sub>kp</sub> | Stiffness contribution of the piezoelectric   | 1/k <sub>piezo</sub>         |

| C <sub>cs</sub> | Electromechanical coupling of the sensor      | $C_{sens}/\theta_{sens}^2$   |

| C <sub>cp</sub> | Electromechanical coupling of the passive     | $C_{pass}/{\theta_{pass}}^2$ |

# 5.2 Equivalent Circuit

Based on the discussion of the mechanical properties of the system presented in the previous section, the equivalent electrical circuit shown in Figure 5.3 has been developed. This circuit is

Figure 5.3: Motional Equivalent Circuit for the Resonator

not a completely accurate electrical representation of the structure, however, as it models only the mechanical behavior of the structure, not the electrical behavior. Furthermore, this circuit is only a single port model and it does not include the effects of the shunt capacitance. To correctly model the electrical behavior of the system, the equivalent circuit must also include the capacitance of the actuator electrode. This capacitance arises from the fact that the actuator piezoelectric element acts as a capacitor in the electrical circuit. In order to model this effect in our circuit, we simply add the actuator capacitance in parallel with the above RLC circuit. Since the output of the amplifier is connected to the actuator electrode, this capacitor also then serves as the input port of the equivalent circuit model. To determine the location of the output port, we recall that the input to the amplifier circuit is connected to the sensor electrode and, therefore, we take our output to be the voltage across this capacitance. Finally, to model the effects of tuning the structure, we place the shunt capacitor in parallel with the passive capacitance. The shunt is placed in this location because, as was discussed in the previous section, the shunting of the passive piezoelectric element varies its equivalent stiffness. The modified equivalent circuit model showing the input and output ports and the shunt capacitance is shown in Figure 5.4. This circuit now contains all of the necessary components to accurately model the frequency response of our resonator structure, but it falls short in two important aspects. First, this model represents only a single resonant frequency, while the structure itself exhibits multiple resonances. The second issue is that the response of this circuit does not accurately model the magnitude response of the system at the resonant frequency.

Figure 5.4: Equivalent Circuit with Input/Output Ports and Shunt

To include the multiple resonances of the structure, we can introduce additional RLC branches into the circuit. Each of these branches, known as motional branches, represents a specific mode of motion and, therefore, a specific resonant frequency. To account for the differences in the way the mechanical structure behaves at each of these frequencies, the circuit parameters must now be specified for each mode. For example, the inductor value is no longer specified as the mass of the system, but as the "modal mass", which is calculated for each mode from mechanical simulations of the system. Additional motional branches can be added in parallel with the branch shown above to account for as many mechanical simulations include the first five modes of motion and, therefore, the equivalent circuit includes five motional branches. If we were to simply connect these five branches in parallel with the actuator capacitor, the result would be a circuit model that accurately models the resonant frequencies of the system, but not their relative magnitudes. The reason for this is that each mode responds differently to excitation by the actuator piezoelectric, which is a result of the size and location of the actuator on the structure. Further, the location of the sensor with respect to the actuator capacitor specified on the sensor with respect to the actuator capacitor capacitor on the structure.

motion to introduce an inversion of the signal polarity. To compensate for these two effects, we are again forced to modify our equivalent circuit.

These final modifications include the introduction of several gain elements into the circuit and a decoupling of the motional branches. Since each mode responds differently to the voltage placed upon the actuator, we can no longer simply connect the motional branches in parallel. To correctly model this, we separate the motional branches and introduce a gain element at the input of each of branch as shown in Figure 5.5. This gain element is used to model the coupling of the actuator piezoelectric to the mechanical mode represented by the given motional branch. As

Figure 5.5: Introduction of Gain Block to Motional Branch

stated above, each mode responds differently to excitation by the actuator and it is this element which scales the magnitude of this response. A second element, which can have a gain of +/-1, is placed at the output of each motional branch to model the inversion of the signal for some modes. With the inclusion of this last element, we have an accurate model for the motion of the system. To model multiple modes, these motional branches are connected such that they receive their input from the actuator capacitor and their outputs are summed to make up the output

Figure 5.6: Block Diagram Representing the Overall Equivalent Circuit

signal. This configuration is shown in the block diagram in Figure 5.6. By constructing the equivalent circuit as presented in this section, we have a two port model which accurately represents each of the necessary aspects of the design. Results of the use of this model with the parameters of the prototype structure will be presented in Chapter 6.0.

## 6.0 PROTOTYPE IMPLEMENTATION

To demonstrate the basic operation of this new oscillator design, a prototype structure and corresponding oscillator circuit were designed and constructed. As stated earlier, a multi-step approach to the problem of constructing an on-chip oscillator has been taken. The prototype presented in this chapter represents the first step of this approach. The goal of this first prototype is simply to demonstrate the operation of the oscillator design including the frequency tuning and switching abilities. A second prototype structure of considerably smaller size is currently in development and will begin to demonstrate the scalability of the design. A final step will be to construct the resonator on-chip, along with the necessary oscillator electronics, and to demonstrate the operation of this single chip oscillator design. The mechanical design and construction of the first prototype resonator, as well as the frequency response data from this design are presented in the first part of this chapter. Also included are results of SPICE simulations using the equivalent circuit model developed in the previous chapter. The remainder of the chapter will provide details of the electrical circuit used to control and tune the prototype and will conclude with the results of these efforts.

#### 6.1 Mechanical Design

In general, the mechanical resonator used for this design could be of any one of various different shapes or sizes as was discussed earlier. For the prototype design, a simple cantilever beam structure, which operates in flexure mode, was used. This particular structure was chosen for several reasons. The most important of these is its ease of manufacture at both the macro-scale, used for the prototype, and the micro-scale, which will be used in continuing this research. There are, however, disadvantages to this type of structure that impose limits on the performance of the oscillator. The two most significant disadvantages are that the quality factor of the piezoelectric material is poor for the flexure mode and that the frequencies for this mode are low compared to those of other modes. The piezoelectric material used in this design is Lead Zirconate Titanate which is more popularly known as PZT. This material was chosen due to its widespread availability and use in many sensor and actuator applications. Furthermore, PZT exhibits a relatively high electromechanical coupling, which allows us to demonstrate a larger tuning range than would be possible with other materials. The chosen design uses a cantilever

structure where a layer of PZT is bonded to an elastic substrate. This substrate, which is stainless steel in the prototype, is necessary because of the brittleness of the piezoelectric material. By bonding the piezoelectric to the steel, not only is the structure strengthened, but the steel layer increases the quality factor of the resonator. Ideally, the resonator would be constructed entirely of stainless steel, or some other high Q material, with only enough piezoelectric material as is required to excite and tune the structure.

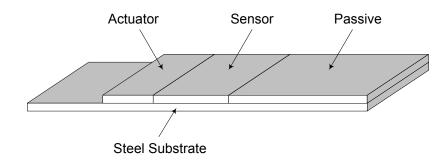

In order to provide the required sensor, actuator, and passive portions, the piezoelectric layer is partitioned into three pieces by the creation of three separate electrodes. The basic structure of the beam and the layout of these three portions are shown in Figure 6.1. This

Figure 6.1: Basic Layout of the Cantilever Beam

structure is manufactured using several simple steps. The first step in the process is to cut the substrate materials (i.e. the PZT and stainless steel) to the appropriate size. The two layers are then bonded together and allowed to cure in a clamping mechanism. The next step involves creating the three separate electrodes required on the PZT material. This is accomplished by masking the three portions and etching away the electrode material. The final step involves making connections to each of the electrodes, which is accomplished by bonding a fine wire to the electrodes using conductive epoxy. The prototype structure measures 57mm long, by 16mm wide and 0.3mm thick. The actuator, sensor and passive piezoelectric portions are 10mm, 16mm and 28mm long respectively. Using this design, a tuning range of approximately 1% was expected from the resonator. Larger tuning ranges are possible, but for the first prototype, a

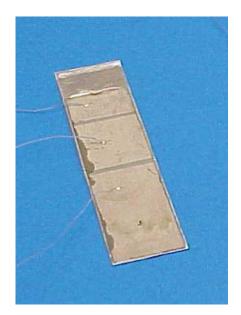

Figure 6.2: Picture of the Prototype Resonator

range of 1% was deemed sufficient to demonstrate the desired effects. For example, if we consider the frequency hopping scheme used for IEEE 802.11, the frequency range required is of approximately the same magnitude. 802.11b, which operates in the ISM band and offers up to 11Mb/s of data transfer, uses 80 communication frequencies with separations of 1MHz. Considering the base frequency of 2.4Ghz, this translates into an overall frequency range of roughly 3.3%. Comparing this result with our expected tuning range of 1%, we see that it is not unreasonable to expect to implement such a frequency hopping scheme using a single oscillator.

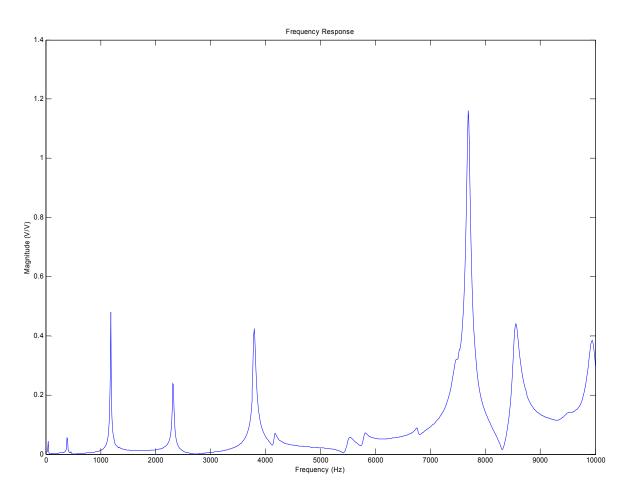

Figure 6.2 shows a picture of the completed beam structure. When operating in flexure mode, this beam exhibits a fundamental frequency of ~42Hz with multiple modes/overtones at higher frequencies. The frequency response of this structure from 0-10kHz is shown in Figure 6.3. Note the multiple resonant frequencies that are shown throughout even this small range. Using this frequency response data, simulations were performed with the equivalent circuit model discussed above to determine the validity of the model. The results of this simulation are presented in the following section.

Figure 6.3: Frequency Response of Prototype Resonator to 10kHz

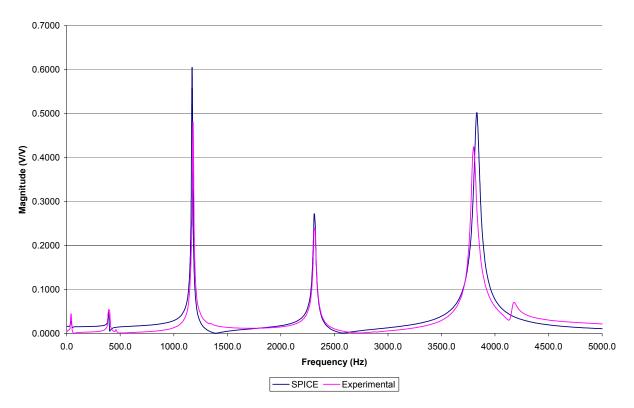

# 6.2 Equivalent Circuit Simulation

Using the electrical equivalent circuit developed in Section 5.2 and mechanical parameters developed from the mechanical design and simulation, a SPICE frequency sweep was performed to determine the accuracy of the model. The contents of the input file for this simulation are shown in Appendix A. The results of this simulation are shown in Figure 6.4 overlaying the experimental frequency response data. As can be seen from the figure, the results of this simulation very closely match those of the experimental data. Note that the mechanical modeling of the structure included only the first five modes of motion and so the equivalent

#### **Magnitude Response**

Figure 6.4: SPICE Equivalent Circuit Frequency Response

circuit only models the first five resonances. With the results of this simulation in agreement with the experimental frequency response data, the circuit that will make up the remainder of the oscillator design was developed. The development of this circuit is presented in the remainder of this chapter along with the relevant experimental results.

# 6.3 Electrical Design

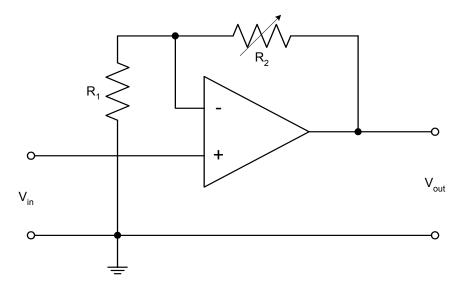

As was discussed previously, the basic electrical circuit required for tuning and control of the mechanical resonator includes an amplifier, phase shift network and tuning capacitors. Due to the size of the prototype structure, it was not necessary to integrate these components onto a single chip and the design could be implemented using off-the-shelf components. The relatively low frequency of oscillation allowed for the use of a standard 741 operational amplifier as the basic amplifier component. The basic gain circuit, which is a simple non-inverting

configuration, is shown in Figure 6.5. The gain of this circuit is adjustable due to the use of potentiometer  $R_2$  and is given in Equation (6.1).

$$A_{\nu} = 1 + \frac{R_2}{R_1} \tag{6.1}$$

Using a 100k $\Omega$  potentiometer for R<sub>2</sub> and a 2.2k $\Omega$  resistor for R<sub>1</sub>, the circuit provides a gain in the range of 1-45V/V. This adjustable gain circuit allows the design to be adjusted so that it can satisfy the amplitude condition of the oscillator at the various resonant frequencies.

Figure 6.5: Basic Amplifier Circuit

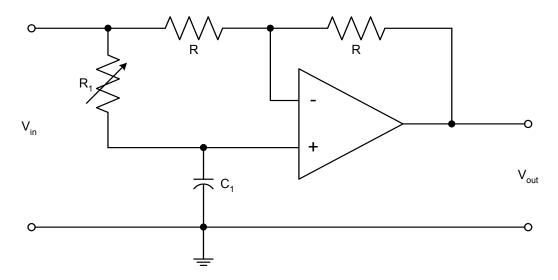

During prototype testing it was also desirable to have an adjustable phase shift network in order to demonstrate the ability to select the mechanical mode of oscillation. This phase shift network is implemented as an all-pass filter, which can be adjusted to produce a variable phase shift by changing the value of a resistor. The circuit used for this portion of the design is illustrated in Figure 6.6. By using a potentiometer in the place of resistor  $R_1$ , it is possible to vary the phase shift introduced at a specific frequency between 0° and 180°. The phase shift,  $\phi$ ,

Figure 6.6: Variable Phase Shift Circuit

introduced by this circuit is dependent on  $R_1$ ,  $C_1$  and the frequency of interest,  $\omega$ , and is given by Equation (6.2).

$$\phi = \tan^{-1} \left( \frac{\frac{2\omega}{R_1 C_1}}{\omega^2 - \left(\frac{1}{R_1 C_1}\right)^2} \right)$$

(6.2)

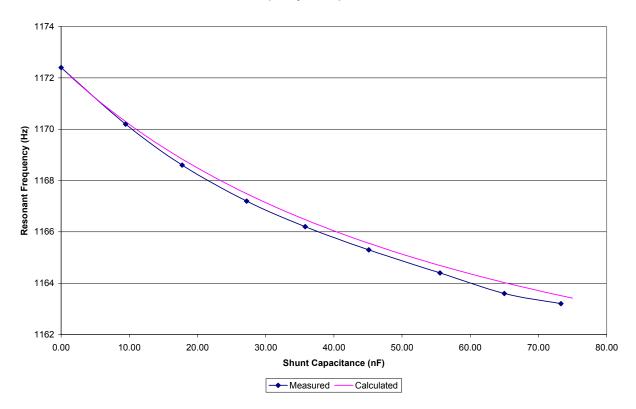

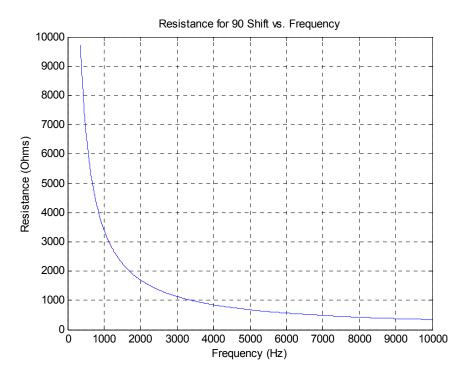

Rather than using potentiometer  $R_1$  to adjust the phase shift between 0° and 180°, it is instead used to adjust the frequency at which the circuit provides a 90° phase shift. Recalling that, at each of the resonant points, the piezoelectric structure introduces a +/-90° phase shift, this allows the phase shift circuit to compensate for this shift at the various resonant frequencies. In order to simplify this process, the capacitor value  $C_1$  is chosen such that a 5k $\Omega$  potentiometer can be used to adjust the frequency of this 90° shift throughout the range of interest. For the prototype design, the frequencies under consideration are between 1kHz and 10kHz and the resulting capacitor value is 47nF. The final portion of the prototype design is that of the tuning network. As discussed in Section 4.2, the tuning network is simply an interconnection of capacitors which allows for a variable shunt capacitance to be placed across the piezoelectric structure. For testing purposes, a selection of different capacitors, whose values ranged from 1-47pF, was used to demonstrate the tuning ability of the design.

# 6.4 Experimental Results