# **Exploring the Surface Interactions of Graphene for Applications in Dual-Sided Field Effect Transistors**

## by

## Jorge Torres Quiñones

B.S. Engineering Physics, University of Pittsburgh, 2014

M.S. Electrical Engineering, University of Pittsburgh, 2017

Submitted to the Graduate Faculty of the

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

### UNIVERSITY OF PITTSBURGH

### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

## Jorge Torres Quiñones

It was defended on

June 4, 2024

and approved by

Zhi-Hong Mao, PhD, Professor, Department of Electrical and Computer Engineering

Susheng Tan, PhD, Associate Professor, Department of Electrical and Computer Engineering

Feng Xiong, PhD, Associate Professor, Department of Electrical and Computer Engineering

Mostafa Bedewy, PhD, Associate Professor, Department of Mechanical Engineering and

Materials Science

Dissertation Director: Minhee Yun, PhD, Associate Professor, Department of Electrical and Computer Engineering

Copyright © by Jorge Torres Quiñones

2024

# **Exploring the Surface Interactions of Graphene for Applications in Dual-Sided Field Effect Transistors**

Jorge Torres Quiñones, PhD University of Pittsburgh, 2024

Graphene is a two-dimensional (2D) material with superior electrical properties that make it attractive for electronic applications. These applications often desire higher transistor densities, leading to the formulation of a dual-sided wafer. Its large surface area to volume ratio renders it extremely susceptible to surface effects, necessitating increased understanding to develop higher quality devices. Large-scale incorporation of graphene requires a growth and transfer process that can affect its properties. It is essential to understand how graphene may be transferred cleanly for improved reliability and CMOS compatibility. Additionally, strong adhesion is desired to withstand the stresses a device can undergo during fabrication and operation. How graphene's electrical conduction is modulated by different substrates is crucial to improving the design and reliability of graphene-based devices. Recent advances in graphene transfer and how these improvements can be incorporated will be discussed. Easy to implement solutions include ammonium persulfate etching of copper foil, heated acetic acid, and lower molecular weight PMMA. The adhesion energy of graphene to SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, gold, and platinum substrates was investigated using the intercalation of nanoparticles method. A key aspect of the adhesion energy was how polarizable the interface material was, with increasing polarization bringing larger adhesion energies. Gold was found to have the largest adhesion energy at 7687.10 mJ m<sup>-2</sup>. Interfacial effects on the electrical conduction of single layer graphene (SLG) and multilayer graphene (MLG) were investigated by determining the temperature coefficient of resistance (TCR). The strongest effect without surface modifications was for SLG on Si<sub>3</sub>N<sub>4</sub>, where the sheet resistance changed 0.393%/K. The modifications strongly affected graphene's properties and offered avenues for improvement, showing a 0.456% change for SLG on SiO<sub>2</sub>. The results of these

experiments were used to develop a dual-sided graphene field effect transistor (GFET). GFETs were developed on both sides of the wafer, with electron and hole mobilities measured up to 1259 and 512 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The fabrication of these transistors allows for new device architectures to create compact and versatile devices. The devices are CMOS compatible and can offer higher transistor densities than previously possible.

# **Table of Contents**

| Prefacexiv                                                                        |

|-----------------------------------------------------------------------------------|

| 1.0 Introduction 1                                                                |

| 2.0 Graphene Transfer Implementations 6                                           |

| 2.1 Wet Transfer Methods                                                          |

| 2.2 Dry Transfer Methods                                                          |

| 2.3 Other Transfer Methods30                                                      |

| 2.4 Recommendations                                                               |

| 3.0 Graphene Adhesion to Silicon and Metal Substrates                             |

| 3.1 Experimental Methods41                                                        |

| 3.2 Results and Discussion                                                        |

| 4.0 External Modulation of Graphene TCR via Substrate Choice and NP Deposition 52 |

| 4.1 Experimental Methods54                                                        |

| 4.2 Results and Discussion                                                        |

| 5.0 Dual-Sided Wafer of Graphene Field Effect Transistors                         |

| 5.1 Experimental Methods82                                                        |

| 5.2 Results and Discussion                                                        |

| 6.0 Future Work                                                                   |

| 7.0 Conclusion                                                                    |

| Bibliography                                                                      |

# **List of Tables**

| Table 1. Recent wet transfer method materials 12                                                                        |

|-------------------------------------------------------------------------------------------------------------------------|

| Table 2. Dry transfer method papers with a brief description                                                            |

| Table 3. A succinct description of other transfer methods                                                               |

| Table 4. Graphene adhesion energy for recorded substrates                                                               |

| Table 5. SLG without nanoparticles on glass data using Linear fit slope, 310 K value, and $\%$                          |

| change of data shown in Figure 10 58                                                                                    |

| Table 6. SLG with nanoparticles on glass data using Linear fit slope, 310 K value, and $\%$                             |

| change of data shown in Figure 1160                                                                                     |

| Table 7. SLG without nanoparticles on $SiO_2$ data using Linear fit slope, 310 K value, and $\%$                        |

| change of data shown in Figure 12 [59]62                                                                                |

| Table 8. SLG with nanoparticles on SiO <sub>2</sub> data using Linear fit slope, 310 K value, and %                     |

| change of data shown in Figure 1364                                                                                     |

| Table 9. SLG without nanoparticles on Si <sub>3</sub> N <sub>4</sub> data using Linear fit slope, 310 K value, and $\%$ |

| change of data shown in Figure 1466                                                                                     |

| Table 10. SLG with nanoparticles on Si <sub>3</sub> N <sub>4</sub> data using Linear fit slope, 310 K value, and %      |

| change of data shown in Figure 15 68                                                                                    |

| Table 11. MLG with and without nanoparticles on glass data using Linear fit slope, 300 K                                |

| value, and % change of data shown in Figure 1670                                                                        |

| Table 12. MLG with and without nanoparticles on SiO <sub>2</sub> data using Linear fit slope, 300 K                     |

| value, and % change of data shown in Figure 1771                                                                        |

| Table 13. MLG with and without nanoparticles on Si <sub>3</sub> N <sub>4</sub> data using Linear fit slope, 300 | K  |

|-----------------------------------------------------------------------------------------------------------------|----|

| value, and % change of data shown in Figure 18                                                                  | 72 |

# **List of Figures**

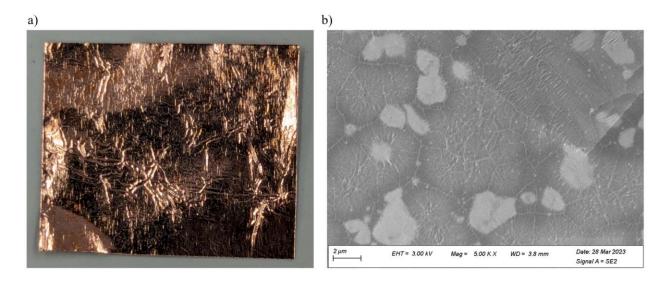

| Figure 1. a) Optical image of graphene grown on copper foil; b) SEM image of graphene               |

|-----------------------------------------------------------------------------------------------------|

| grown on copper foil7                                                                               |

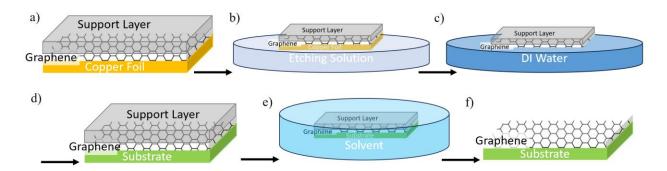

| Figure 2. a) Support layer is applied to as grown graphene; b) the combination is lowered           |

| into an etching solution to remove the copper foil; c) the remaining support layer and              |

| graphene is cleaned via DI water baths; d) the target substrate is used to scoop up the             |

| graphene/support layer; e) the support layer is removed by immersion in solution; f)                |

| the graphene on substrate is dried and ready for further processing12                               |

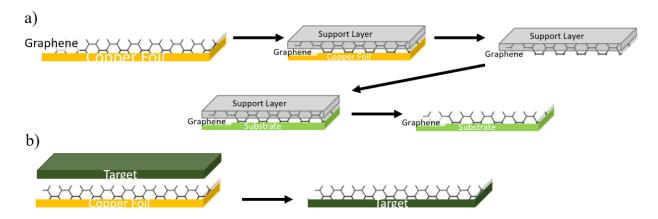

| Figure 3. a) indirect dry transfer process; b) direct dry transfer process                          |

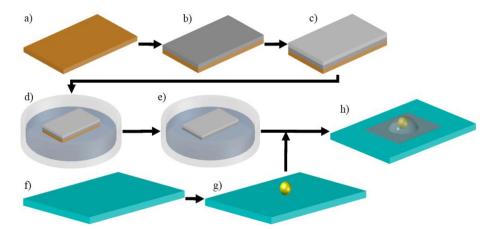

| Figure 4. The sample creation process. a) Copper foil is cleaned and annealed. b) Graphene          |

| is grown on the Cu foil using a CVD method. c) PMMA is spun on top of the grown                     |

| graphene and the backside of the Cu foil is cleaned of any excess graphene growth. d)               |

| The Cu/graphene/PMMA is put into an etchant bath, Cu side down. e) The Cu is                        |

| etched away and the remaining graphene/PMMA hybrid is cleaned in DI water baths.                    |

| f) A substrate is chosen to deposit nanoparticles onto. g) Gold nanoparticles are                   |

| deposited onto the substrate. h) Graphene is transferred onto the prepared substrate,               |

| sandwiching the nanoparticle between the substrate and graphene, resulting in a                     |

| blister [59]                                                                                        |

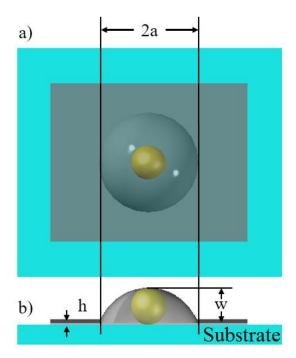

| Figure 5. The visualization of the parameters in Eq. $(3)$ . h is the thickness of the 2D material, |

| a is the radius of the blister, w is the height of the blister. a) top view, b) cross sectional     |

| view [59]                                                                                           |

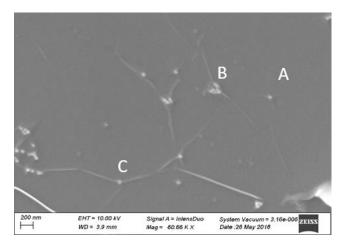

| Figure 6. Graphene on Si <sub>3</sub> N <sub>4</sub> with Au nanoparticles SEM image with working distance |

|------------------------------------------------------------------------------------------------------------|

| 3.9mm and magnification 60.66kx. The electron beam voltage was 10kV. A regular                             |

| blister with a single nanoparticle is shown at position A. A complex blister with many                     |

| nanoparticles is shown at position B. A single nanoparticle blister with a wrinkle in                      |

| the graphene layer is shown in position C [59]47                                                           |

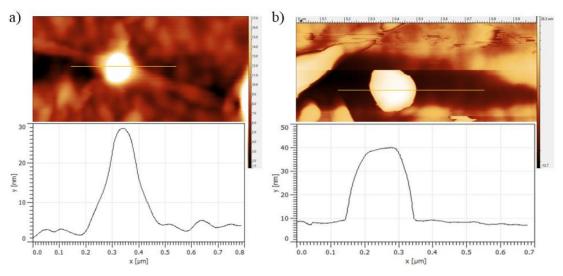

| Figure 7. Representative AFM images of graphene covering an Au nanoparticle with a) a                      |

| SiO <sub>2</sub> substrate, b) a Pt substrate. Taller structures are represented by lighter regions.       |

| The line profiles of each blister are also shown. The line profiles have an x-direction                    |

| unit of um, and a y-direction unit of nm [59]48                                                            |

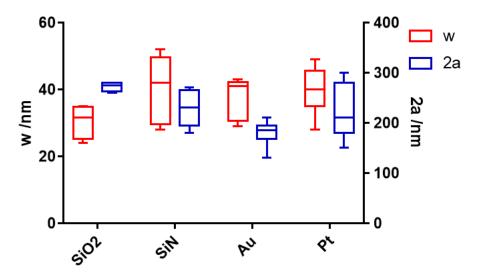

| Figure 8. Range of blister data for graphene on various substrates. The red data on the left               |

| for each substrate is the blister height, w, while the blue data on the right is the blister               |

| diameter, "2a" [59]49                                                                                      |

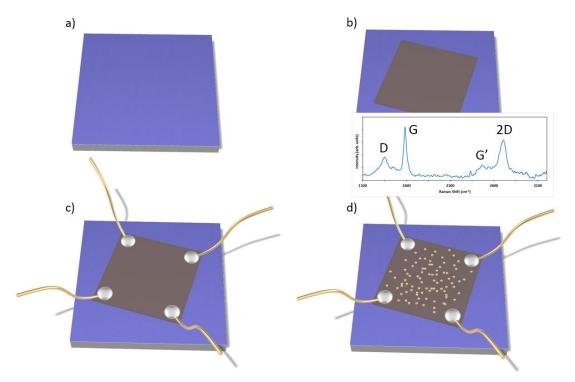

| Figure 9. Representation of the sample preparation process. (a) The substrate is cleaned                   |

| before graphene transfer; (b) a wet transfer process applies graphene to the                               |

| substrate; (c) soldering/wire-bonding is used to bond contacts to graphene; (d)                            |

| nanoparticles are drop cast on top of graphene. Reprinted with permission from                             |

| [113]. Copyright [2020] American Chemical Society 55                                                       |

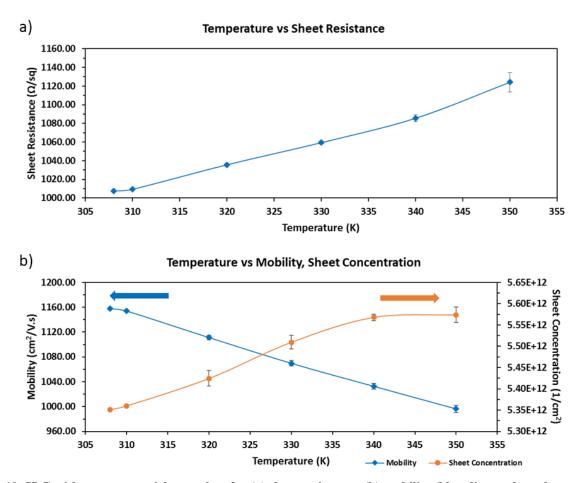

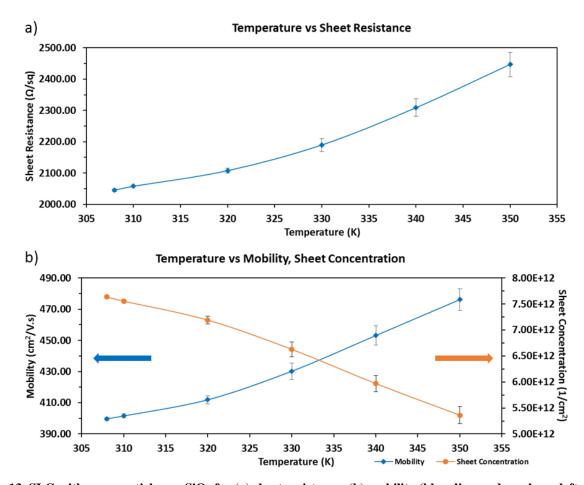

| Figure 10. SLG without nanoparticles on glass for (a) sheet resistance, (b) mobility (blue                 |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                         |

| axis) over the temperature range 300-350K Reprinted with permission from [113].                            |

| Copyright [2020] American Chemical Society58                                                               |

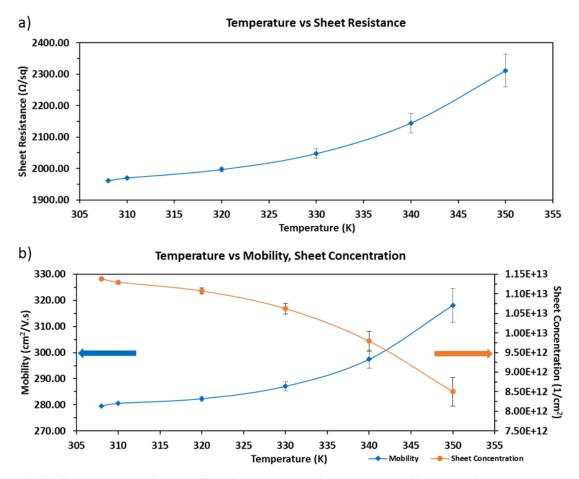

| Figure 11. SLG with nanoparticles on glass for (a) sheet resistance, (b) mobility (blue                    |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                         |

| axis) over the temperature range 300-350K. Reprinted with permission from [113].                                    |

|---------------------------------------------------------------------------------------------------------------------|

| Copyright [2020] American Chemical Society60                                                                        |

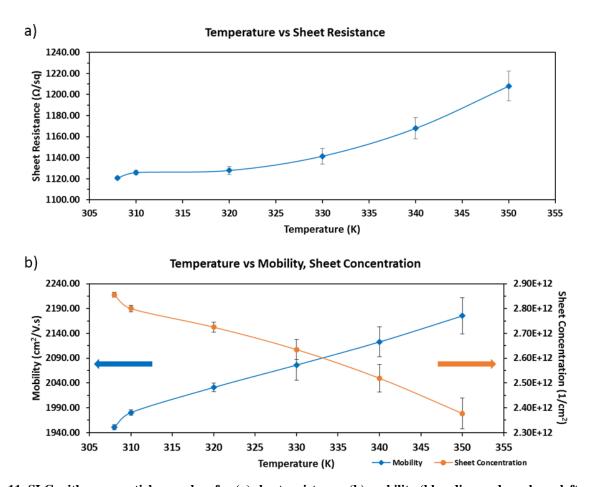

| Figure 12. SLG without nanoparticles on SiO <sub>2</sub> for (a) sheet resistance, (b) mobility (blue               |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                                  |

| axis) over the temperature range 300-350K. Reprinted with permission from [113].                                    |

| Copyright [2020] American Chemical Society62                                                                        |

| Figure 13. SLG with nanoparticles on SiO <sub>2</sub> for (a) sheet resistance, (b) mobility (blue                  |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                                  |

| axis) over the temperature range 300-350K. Reprinted with permission from [113].                                    |

| Copyright [2020] American Chemical Society64                                                                        |

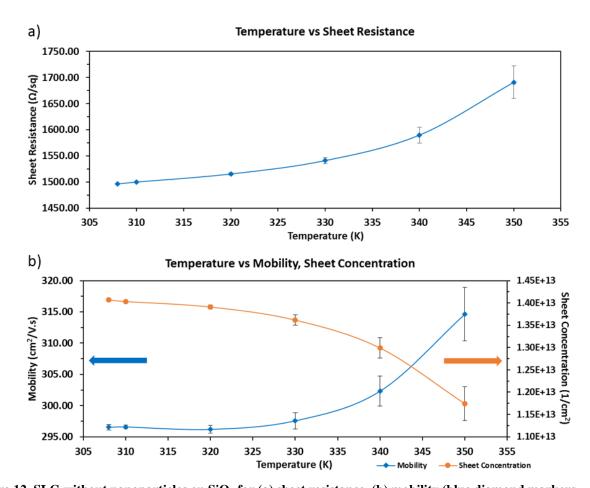

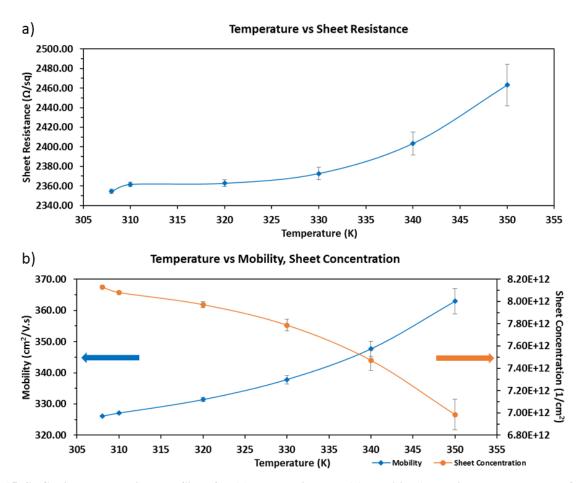

| Figure 14. SLG without nanoparticles on Si <sub>3</sub> N <sub>4</sub> for (a) sheet resistance, (b) mobility (blue |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                                  |

| axis) over the temperature range 300-350K. Reprinted with permission from [113].                                    |

| Copyright [2020] American Chemical Society66                                                                        |

| Figure 15. SLG with nanoparticles on Si <sub>3</sub> N <sub>4</sub> for (a) sheet resistance, (b) mobility (blue    |

| diamond markers, left axis), and sheet concentration (orange circle markers, right                                  |

| axis) over the temperature range 300-350K. Reprinted with permission from [113].                                    |

| Copyright [2020] American Chemical Society68                                                                        |

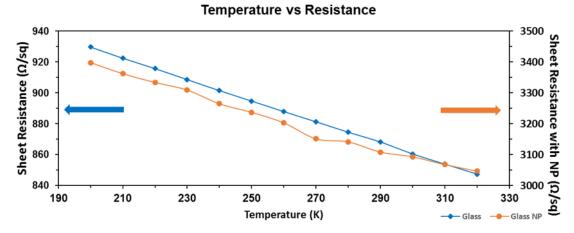

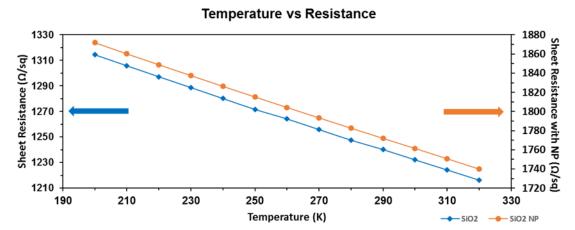

| Figure 16. MLG without nanoparticles (blue diamond) and with nanoparticles (orange                                  |

| circle) on glass over the temperature range 200-320K. Reprinted with permission                                     |

| from [113]. Copyright [2020] American Chemical Society70                                                            |

| Figure 17. MLG without nanoparticles (blue diamond) and with nanoparticles (orange                       |

|----------------------------------------------------------------------------------------------------------|

| circle) on SiO <sub>2</sub> over the temperature range 200-320K. Reprinted with permission               |

| from [113]. Copyright [2020] American Chemical Society71                                                 |

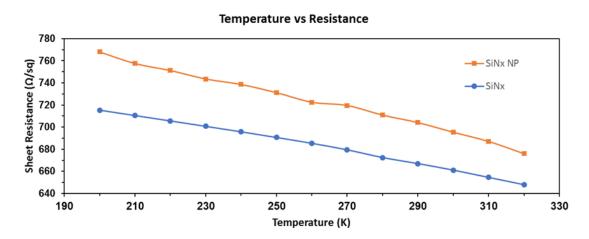

| Figure 18. MLG without nanoparticles (blue circle) and with nanoparticles (orange square)                |

| on Si <sub>3</sub> N <sub>4</sub> over the temperature range 200-320K. Reprinted with permission from    |

| [113]. Copyright [2020] American Chemical Society                                                        |

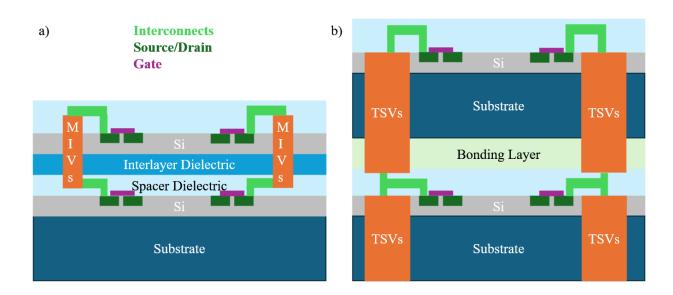

| Figure 19. Different 3D IC fabrication methods. a) Monolithic Method; b) Wafer Bonding                   |

| Method                                                                                                   |

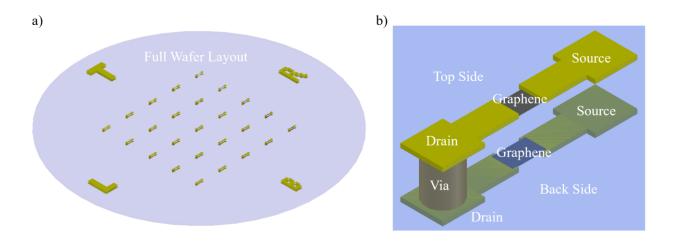

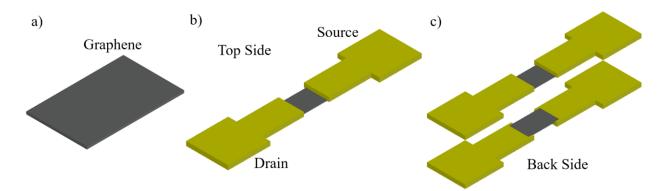

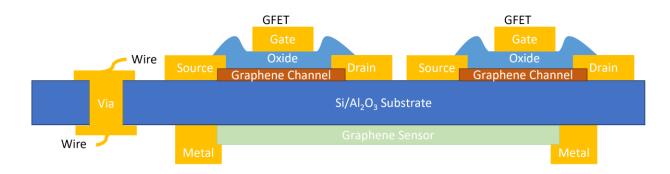

| Figure 20. 3D Model of a dual-sided graphene FET. a) Whole wafer; b) Close-up of a single                |

| device structured as an inverter80                                                                       |

| Figure 21. Fabrication process overview. a) Graphene transfer and etching; b) Source and                 |

| drain contact deposition; c) repeat steps a and b on the backside82                                      |

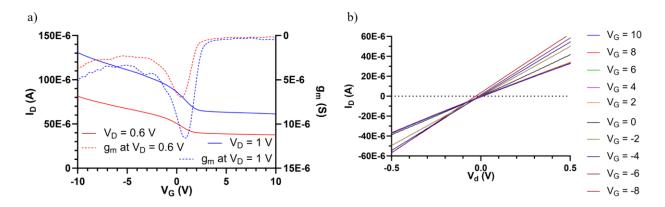

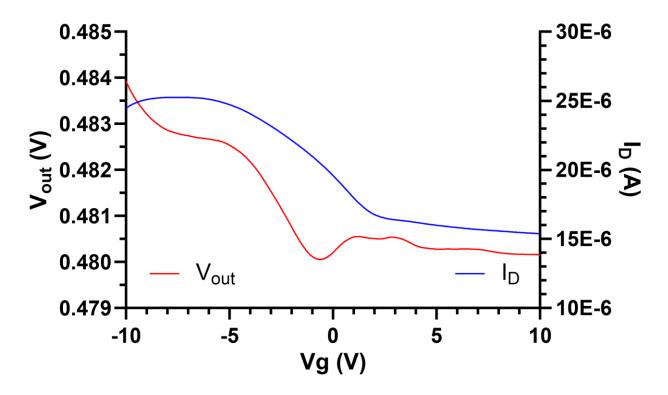

| Figure 22. Electrical characterization result of a device on the front side of the wafer. a) $V_{\rm G}$ |

| vs $I_D$ , $g_m$ graph at different $V_D$ values. The red lines correspond to $V_D$ = 0.6 V, while       |

| the blue lines correspond to $V_D=1\ V.$ The straight lines are $I_D$ curves with Y values               |

| on the left axis, while the dashed lines are $g_m$ and have Y values on the right axis; b)               |

| $V_D$ vs $I_D$ graph at different $V_G$ values86                                                         |

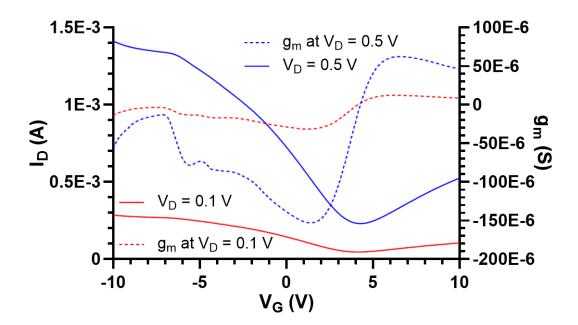

| Figure 23. Electrical characterization result of a device on the back side of the wafer. $V_{\rm G}$ vs  |

| $I_D$ and $g_m$ graph at different $V_D$ values. The red lines correspond to $V_D$ = 0.1 V, while        |

| the blue lines correspond to $V_D = 0.5 \; V$ . The straight lines are $I_D$ curves with Y values        |

| on the left axis, while the dashed lines are $g_m$ and have Y values on the right axis 88                |

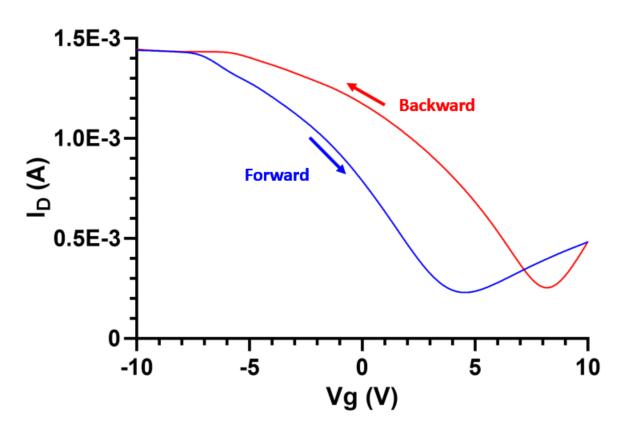

| Figure 24. Hysteresis of Back Side Device                                                                |

| Figure 25 Two GFETs Connected in Inverter Configuration 92                                               |

| Figure 26. A conceptual example of a dual-sided graphene-based | device 97 |

|----------------------------------------------------------------|-----------|

|----------------------------------------------------------------|-----------|

#### **Preface**

First and foremost, to my family. My mom, my dad, my brother, all of whom have provided me with unconditional support and love. Though we are separated by physical distance, know that you are forever close to my heart and that I love you all very much. Your constant belief in me, and continued support and understanding have been great sources of strength for me. Thank you for pushing me and sticking with me throughout this journey. I look forward to continuing to share our lives together.

To my girlfriend, Sierra. Thank you for being with me, for sharing my hopes and dreams, for pushing me when I am feeling down, and being a wonderful girlfriend. I hope to continue experiencing the world with you, both in far off places and in the deepest parts of our minds. To share in life is truly sacred, and I am happy to share it with you.

I would like to extend my gratitude to the many friends I have made along my path, from the ones I haven't heard from in a while, and to the ones who stay in touch, thank you. I have enjoyed my time playing games and sports, conversing about any and every topic, dancing the night away, and other activities with each and every one of you. Thank you for making my life richer and fuller with your presence and for being wonderful human beings.

Thank you, Professor Minhee Yun, for your invaluable guidance, support, and encouragement throughout my PhD journey. Your insightful feedback and dedication to my academic and professional growth have been instrumental in the successful completion of my dissertation. Thank you for continuing to believe in me and for your mentorship. I would also like to express my thanks to the committee for their agreement to support me in this endeavor. Their faith in me has not gone unnoticed and is much appreciated.

I would like to extend my gratitude for the financial support provided by NSF, AGEP, Sungkyunkwan University, and the University of Pittsburgh. Their contributions have enabled me to focus on my research and achieve significant milestones. This journey would not have been possible without their assistance.

#### 1.0 Introduction

Graphene, a two-dimensional (2D) carbon-based material with a hexagonal lattice configuration, was a groundbreaking discovery in 2004. The pioneering work of Novoselov et al., who first transferred few layer graphene by repeated peeling of graphite, marked the beginning of a new era in materials science and nanotechnology [1]. Since then, graphene has been extensively studied, with a focus on its growth and transfer processes, and the unique properties and applications that emerge from its 2D confinement. Despite the exploration of other 2D materials, graphene remains a major research area due to its versatile properties.

Graphene has a unique sp3 bond structure that gives rise to its many properties. It has a measured in-plane thermal conductivity of up to 5600 Wm<sup>-1</sup>K<sup>-1</sup> and has a high Seebeck coefficient that enables its use for thermally derived power [2, 3]. It has one of the highest mobilities known, reaching over 2E5 cm<sup>2</sup>/Vs at room temperature, allowing it to be highly conductive [4]. Graphene has a theoretical conductivity as high as 1E5 S/m [5]. While its absolute optical absorption of ~2% is relatively low, it is astounding that such a thin material can absorb so much light. Additionally, graphene has a Young's modulus of 1TPa, making it about 200 times stronger than steel and several times harder than diamond [6]. As for its chemical properties, it possesses antibacterial properties and can be used as a chemical sieve to allow the passage of some compounds while blocking others [7]. These miraculous properties have given rise to numerous applications.

The exceptional properties of graphene have led to its application in diverse fields such as medicine, chemistry, and electronics, showcasing its potential for transformative impact. In medicine, graphene has been utilized to detect various viruses and bacteria, demonstrating its potential in disease diagnosis [8]. Similarly, graphene has been employed as a gas sensor and a

catalytic support in the chemical field, highlighting its role in environmental monitoring and chemical reactions [9, 10]. In electronics, graphene's high-frequency transistors, memory devices, and improved battery technology can revolutionize the industry [11-13]. The broad spectrum of applications underscores the unique value of graphene.

Despite graphene's numerous excellent properties and practical applications, its full potential is yet to be realized. The road to unlocking this potential has its challenges. The heavy influence of graphene's growth and transfer processes and its surface interactions pose significant hurdles. The processes required to transfer graphene onto various surfaces need to be optimized for the best performance in any given application. Graphene's ultrahigh surface area to volume ratio underscores the importance of external interfacing in determining material behavior and device performance. The adhesion properties of graphene change substantially based on the choice of substrate. Any surface modifications performed can significantly alter graphene's critical electrical properties. Therefore, a better understanding of the substrate's influence on graphene is crucial to maximize the performance of graphene-based devices. This optimization can lead to better integration with existing complementary metal oxide semiconductor (CMOS) technology, but it's a complex task that requires careful consideration and research.

The processes needed to use graphene differ slightly from those of CMOS technology. Conventional CMOS technology involves thin film grown directly on the substrate via chemical vapor deposition (CVD) or electron-beam (e-beam) evaporation processes, which can then be subsequently patterned. One example is CVD-grown polysilicon, which yields a uniform thin film that helps enable CMOS-based devices [14]. Metal contacts are typically fabricated using e-beam evaporation due to the process control available and resulting uniform thin films. However, graphene is difficult to grow or deposit directly on a desired substrate, especially with non-metallic

substrates [15]. Thus, graphene must be grown on a different substrate, followed by the transfer of graphene from the growth substrate to the target substrate. Device performance can be detrimentally affected by these growth and transfer processes. While several methods have been discovered to grow graphene, the most prominent is the CVD growth of graphene on a transition metal substrate. This growth process can be tuned to provide high-quality graphene, though the choice of growth substrate thus requires a transfer process to allow for integration into CMOS devices. The transfer is typically done using a wet process, in which a polymer covers the graphene. The polymer/graphene/metal material is then set in a chemical bath to etch away the metal, and the resulting polymer/graphene material can be transferred onto the target substrate after cleaning. After transfer, the polymer can then be removed via solvent. This transfer process is essential to providing graphene-based devices, though the process often leaves residues and cause mechanical deformations that negatively affect the performance of the transferred graphene. Consequently, careful consideration must be made to the growth and transfer processes to obtain the best graphene performance possible.

Following the successful transfer of graphene to the desired substrate, studies are needed to determine the usability of graphene for various applications. Due to graphene's 2D nature, it is highly affected by the interactions between itself and the material it contacts. These external interfaces can drastically alter graphene's performance characteristics, thus necessitating an understanding of how such interfaces may affect the operation of a graphene device. Adhesion studies will help show the reliability of graphene-based devices, with solid results improving the contact uniformity of graphene. Additionally, such interfaces affect the electrical conduction of graphene, providing the need for information on how one can alleviate any ill effects or use the effects to an advantage. The study of how graphene resistivity responds to temperature increases

as a result of different surface interactions can elucidate the electrical response of graphene to different interfaces. The results of these experiments can inform future design and fabrications processes as to which materials may work best with graphene, diminishing any harmful effects while maximizing any beneficial effects. This will enable the design and fabrication of graphene field effect transistor (GFET) on both sides of a wafer's surface, which we term dual-sided GFETs (DSGFET).

The ability to successfully fabricate DSGFETs will require understanding of transfer processes and the surface interactions of graphene. Thus, it is necessary to set objectives for this work to provide a foundation for success. The current state of transfer technology should be explored to inform best practices in creating ultraflat, ultraclean graphene. While the best graphene transfer requires appropriate growth processes, graphene growth quality is high enough that transfer improvements can provide more significant results. The adhesion energy of graphene will be explored to different substrates, though it will be necessary to limit the number of materials tested. Thus, only commonly used substrates will be tested. The thermal and electrical response of GFETs are important to consider as well, and how graphene's response changes due to surface interactions. This can be investigated by the exploration of the change in graphene's resistivity as a result of temperature changes across different substrates. As before, the number of materials tested will need to be limited. Additionally, we will not be considering other thermoelectric properties of graphene, such as thermal conductivity. The information gathered from these investigations will then be used to inform the design and fabrication of DSGFETs. This process serves as a proof of concept and will not integrate extensive circuit designs or large-scale techniques.

These objectives will provide the contributions necessary to advance graphene device applications. The refinement of graphene transfer techniques offers increased quality of graphene, which includes less defects and undoped graphene. This creates more reliable GFETs with better performance. The study of adhesion factors can improve device reliability and reduce delamination of graphene during processing. The study of the graphene's resistivity response to temperature and surface interactions can elucidate how the choice of substrate material is important in determining GFET performance. The successful completion of a dual-sided graphene device will open up new possibilities in device architecture, potentially leading to new compact and versatile devices. These devices can offer improved integration with CMOS technology and higher transistor densities than previously possible.

This work will demonstrate investigations into graphene electronics, beginning with a discussion on the state of graphene transfer technology in Chapter 2.0. Adhesion studies of graphene on different substrates will follow in Chapter 3.0. The adhesion interactions between graphene and various gate dielectrics and metal electrodes are investigated using the intercalation of nanoparticles method. Chapter 4.0 evaluates the effects of the substrate and other surface modifications on both single-layer graphene (SLG) and multilayer graphene (MLG) temperature coefficient of resistance (TCR) to advance the understanding of how external influences affect the electrical and thermal properties of graphene, which leads to the final part of this research. The final research avenue displayed in Chapter 5.0 was the development of dual-sided graphene Field Effect Transistors (GFETs). The dual sided GFET is a new platform for advanced applications, allowing for more compact and powerful devices to be made. We show a working prototype and explore how improvements can be made. Future work is then discussed in Chapter 6.0, followed by the Conclusion in Chapter 7.0.

## 2.0 Graphene Transfer Implementations

The work presented in this chapter was published in [16]. Reused in part with permission.

The graphene transfer process is crucial in determining the quality of resulting devices. Graphene has been used in many applications due to its excellent properties. These graphene-based devices have shown an exciting potential to transform many industries. Despite these possibilities, graphene has not consistently yielded devices with the full characteristics of pristine graphene. As a 2D material, graphene is easily changed by the processes used to fabricate devices. For graphene to provide its most significant benefits, high-quality, ultraclean preparation processes must be created. Depositing or growing graphene on desirable substrates is challenging, thus necessitating a transfer method. The growth method used may affect the quality of later transfer processes. Three of the most common methods to grow graphene are 1) SiC-based growth, 2) highly ordered pyrolytic graphite (HOPG), and 3) transition metal CVD-based growth. Each growth method can be followed by diverse transfer methods. Here, they are divided into wet transfer, dry transfer, and other methods. These processes will be discussed in detail later.

The synthesis of graphene usually takes one of three primary methods: 1) SiC-based growth [17, 18]; 2) highly ordered pyrolytic graphite (HOPG) delamination [19, 20]; and 3) transition metal CVD-based growth [21, 22]. Graphene growth on SiC is typically costly, allowing only limited use cases. Graphene created via HOPG tends to provide graphene with remarkable quality, with limited defects and nearly nonexistent doping due to the ability to use solvent-free processes. However, HOPG is similarly costly and has a low yield. With a low cost and a high scaling capability, CVD graphene is a facile method widely used and can provide high-quality samples.

With a CVD growth process, single-layer or multilayer graphene can be produced. One drawback of this method is that growing graphene directly on the desired substrates is onerous, requiring thin transition metal foils. Since copper has low carbon solubility, it is often chosen as the growth substrate. The low solubility allows for a self-limiting process that can provide repeatable, high-quality, and layer-controlled growth [23]. Figure 1 exhibits different examples of the process and the associated outcome. Copper foil that has already gone through the growth process is shown in Figure 1a, while Figure 1b shows the growth of graphene as viewed with SEM. Typical CVD processes include an annealing and polishing that increases the grain size of the copper, thereby increasing the grain size of the graphene grown on top. The defect sites on the copper surface can be controlled, providing further avenues for increased control. These characteristics have enabled CVD growth to become the primary method of growing graphene. However, using transition metal foils is challenging for the semiconductor industry as conductive metals are unsuitable substrates for most applications. The lack of suitable growth substrates has led to the development and advancement of techniques that can transfer as-grown graphene to the desired substrate.

Figure 1. a) Optical image of graphene grown on copper foil; b) SEM image of graphene grown on copper foil

Transfer methods have been developed by the necessity of growing graphene on undesirable substrates and then placing it onto suitable substrates. Graphene transfer from the undesirable growth substrate must fulfill at least two conditions: 1) an intact and complete separation of graphene from the growth material and 2) subsequent intact placement of graphene onto the desired substrate. Many methods have been investigated that fulfill these conditions, with a typical condition being the successful application and removal of an intermediate supporting layer. While previous reviews have detailed many advances, graphene transfer is a subject of intense research, with many new advances being brought to the fore. The pace of experimentation requires a continual update to the state of the art. This chapter focuses on three distinct groups: wet transfer, dry transfer, and other transfer. Wet transfer seeks to use liquid etchants and solvents to separate graphene from its growth material before application onto the target substrate in a liquid environment. Dry transfer removes graphene from the growth material through multiple methods, though the target substrate will receive graphene in an environment without any liquid. Any intermediate supporting layer is typically removed via solvent upon successful lamination. Other methods may use parts of these processes but do not neatly fall into either category. Of the three methods, all are viable paths to a successful transfer. However, due to graphene's high specific surface area, the environment notably affects the resulting properties [24, 25]. If not adequately accounted for, the transfer process may suffer various ill effects. These effects must be considered in any transfer process to deliver ultrahigh-quality graphene.

Transfer processes for graphene can suffer from various issues. These issues can include wrinkles, cracks, and contamination. Wrinkles occur when the graphene sheet overlaps or bunches like a poorly flattened rug. Wrinkles may occur due to differences in topology between the growth

substrate and the target substrate [26], or because the environment causes gaps between graphene and the substrate [27]. The wrinkles cause a deleterious effect on the electrical properties of graphene by creating potential barriers and additional scattering centers [28]. The slender thickness of graphene makes it vulnerable to physical damage and is known as cracking [29]. These physical deformations will also cause undesirable decreases in conduction and poor thermal transfer. Finally, contamination can be caused by the inadequate separation of the growth material or the intermediate support layer [4, 30]. Additional sources of contamination come from the environment, which can cause unwanted doping. Graphene quality and performance are degraded because of these issues, which affect subsequent device performance. Each method achieves different results in its handling of these issues. The etchants and solvents incorporated into the wet transfer process can reduce the level of contamination but may introduce other defects [31]. Dry transfer steps can cause physical damage, and some intermediate support layers can also leave contamination when removed [32, 33]. Various characterization methods have been used to appraise the resulting material properties and defects.

The determination of the quality of graphene may be accomplished through various techniques. SEM imaging, Raman spectroscopy, AFM, and graphene FETs are some accepted instruments used for characterization. SEM imaging may differentiate between single and multilayer graphene samples and determine whether the grain size is monocrystalline or polycrystalline. It can also spot cracks and wrinkles in the graphene structure and potential contaminants [34, 35]. Raman spectroscopy is another method that can determine the number of layers and is also capable of sensing mechanical deformations, strain, and doping [36, 37]. A typical Raman spectrum of graphene will include two peaks, the G peak at ~1580 cm<sup>-1</sup> and the 2D peak at ~2690cm<sup>-1</sup>. The ratio of I<sub>2D</sub>/I<sub>G</sub> indicates single layer graphene (SLG) or multilayer

graphene (MLG). A third peak that may show in spectrographic results is the D peak at ~1350cm<sup>-1</sup>. This peak indicates the existence of mechanical defects in the graphene layer. Note that the position of the D and 2D peaks cited here assume a laser excitation wavelength of 532 nm [38]. AFM can also determine the layers of graphene and spot cracks and wrinkles thanks to its subnanometer resolution. The acquisition of the graphene's surface roughness, uniformity, and morphology can determine additional details of its surface quality. More specialized modes of AFM can allow for the gathering of localized material properties, allowing for in-depth analysis of the factors that can influence graphene properties [39, 40]. The creation of GFETs allows for probes into the structure of graphene. The location of the smallest current value for a given drain voltage as a gate voltage is swept is known as the Dirac point. The location of the Dirac point relative to 0 V indicates the doping level present. Additional characteristics, such as mobility and carrier concentration, can be found through this method as well.

The rest of this chapter will focus on graphene transfer and the many methods offered. The wet transfer method is considered in 2.1, the dry transfer method in 2.2, and other transfer methods in 2.3. The overall approach to each method will be discussed, along with benefits, limitations, and possible issues. Section 2.4 will discuss potential avenues of success that may improve graphene transfer quality.

## 2.1 Wet Transfer Methods

Here, wet transfer is defined as any method in which graphene lies on top of a liquid before being adhered to the target substrate and then dried. Further, only supported transfer processes will be considered here, where a supporting polymer is added to mechanically stabilize the transferred graphene. As one might expect, the transfer environment is dominated by liquid. Despite graphene's impressive mechanical strength, its thin structure causes it to be a fragile material [41]. The forces involved in a liquid environment can thus damage graphene, requiring a support layer. The removal of graphene from its growth substrate is typically accomplished via an etchant. Figure 2 shows a synopsis of the process. A support layer is deposited after the growth process is complete, as seen in Figure 2a. As stated, the lack of thickness causes graphene to often break without this addition. One common supporting material is PMMA, which can be spin-coated onto the as-grown graphene. As mentioned, this metal is typically copper because of its low carbon solubility and relatively low cost [42]. The combination is then lowered into a suitable etching solution, as Figure 2b shows. Once the metal is etched, the graphene/polymer layer is left floating on top, the graphene side down. The graphene/polymer can then be lifted by another material for additional cleaning, normally by flotation in DI water, as in Figure 2c. After the additional cleaning, the graphene is scooped up by the desired substrate and dehydrated, as in Figure 2d. After drying, the removal of the supporting polymer follows, as in Figure 2e, and another drying round leads us to the finished product in Figure 2f. While this method is simple, each step can cause unwanted contamination and deformation if process control is not maintained. This section will cover further specifics of the wet transfer method and recently introduced technological advancements, as listed in Table 1.

Figure 2. a) Support layer is applied to as grown graphene; b) the combination is lowered into an etching solution to remove the copper foil; c) the remaining support layer and graphene is cleaned via DI water baths; d) the target substrate is used to scoop up the graphene/support layer; e) the support layer is removed by immersion in solution; f) the graphene on substrate is dried and ready for further processing

Table 1. Recent wet transfer method materials

| Support Layer        | Growth Removal          | Support Removal                           | Ref  |

|----------------------|-------------------------|-------------------------------------------|------|

| PMMA                 | FeCl <sub>3</sub> + HCl | Acetone                                   | [43] |

| PMMA (different MWs) | $FeCl_3 + HCl$          | Acetone/IPA                               | [44] |

| PMMA                 | FeCl <sub>3</sub>       | No removal of PMMA                        | [45] |

| PMMA                 | APS                     | Acetone                                   | [46] |

| PMMA                 | APS                     | 2 <sup>nd</sup> PMMA layer + acetic acid, | [47] |

|                      |                         | chloroform, or hot acetone                |      |

| Rosin                | FeCl <sub>3</sub>       | Acetone/Banana Oil                        | [48] |

| Anthracene           | APS                     | Sublimation                               | [49] |

| Camphor              | APS                     | Sublimation                               | [50] |

| Naphthalene          | $H_2O_2 + HCl$          | Sublimation + optional ethanol            | [51] |

| TFB/PMMA             | Electrochemical         | Acetone                                   | [52] |

|                      | Bubbling                |                                           |      |

Deformation and contamination problems may occur during the wet transfer process. The problems occur due to the use of liquid etchants and PMMA as its preferred support layer. The etching process may not result in complete removal of the growth substrate, and its particulates are still in solution and may attach themselves to the graphene/polymer stack (Figure 2b and c). The transfer process may also cause the liquid to be stuck between the substrate and graphene, causing the formation of wrinkles as the graphene dries (Figure 2d) [53, 54]. Meanwhile, PMMA-based support layers can bind tightly to graphene thanks to PMMA's functional groups. The strong bonds make PMMA challenging to remove and are a source of p-type doping (Figure 2e and f) [55, 56]. It is not typically practical to remove the support layer, causing the exploration of other materials to be used as a support layer.

Another method attempted is the exploration of different etchants, which may decrease the contamination of metal particles on graphene. These etchants aim to create water-soluble salts that may be eliminated via subsequent DI water-cleaning steps. Initial studies utilized iron chloride (FeCl<sub>3</sub>) as an etchant. This process left substantial metallic contamination upon completion [47]. A way to improve this situation was to introduce a weak HCl solution, which lowered the remaining metal contaminates [57]. The addition of HCl by Liao et al. was met with success. The added process step removed the excess iron contamination caused by etching copper with FeCl<sub>3</sub> [44]. This addition increased the process steps required, which increases the processing time required and may result in mechanical damage. This concern has been removed by other etchants that provide equal or superior results.

Ammonium persulfate (APS) is another etchant that has been examined. This method is used throughout this dissertation due to the inability of FeCl3 to remove metallic contamination

adequately [58, 59]. Other studies have shown that APS is a superior etchant to FeCl3, with much reduced metallic contamination [30]. A comparison of the processes in Ref [43] and Ref [46] shows that the APS process has fewer and smaller residues despite similar cleaning steps. While APS can reduce metallic contamination to an insignificant level, some studies demonstrated that APS may cause increased crosslinking in PMMA polymers, making PMMA more problematic to remove [49]. Additionally, the concentration of APS may cause graphene to crack upon being transferred. The unwanted cracking can be prevented through a lower concentration of APS. The tradeoff comes as a longer etch time [47]. While polymeric residues will occur regardless of etchant, etchants have a role to play in the removal of polymer support layers and thus may necessarily require investigation.

A major problem with wet transfer techniques is polymer residue. Despite its impressive strength-to-size ratio, graphene is easily damaged during the transfer. Thus, the exploration for better support processes has been ongoing for a long time. Improvements to the cleaning process is one method advanced for the reduction of polymer residue. An improved cleaning process can be observed by incorporating the support layer as part of the device and using the properties of the support layer to modulate certain aspects of graphene. Keeping the support layer removes the issue of polymer residue, as the polymer is now a device component. Depending on the application, this may be a preferred method. The polymer may increase the ability to sense certain compounds while restricting the ability to sense others. For example, it is possible to use PMMA to boost the detection and specificity of volatile organic compounds (VOCs) of graphene-based gas sensors. Rattanabut et al. recorded the detection of VOCs using graphene/PMMA and graphene layers [45]. The difference in sensing mechanisms between a PMMA/graphene sensor and a pure graphene sensor enabled different sensitivities and results. The PMMA layer being left on the graphene thus

increased the utility of the graphene sensor. Though PMMA was helpful in this instance, further research is required to determine if support layers can be developed for other applications. The research is required because PMMA is not a universally helpful material. Regardless, this method may be a valuable approach to device fabrication [45]. This approach is unlikely to be universal due to the excellence provided by pristine graphene. However, this approach is suitable for use in various applications and avoids contamination.

Since a change in the support layers cannot meet the needs of all applications, better cleaning solutions are still needed. Many approaches have been attempted, such as annealing in various environments [60, 61], using ion beam treatments [62, 63], plasma treatments [64, 65], or laser exposure [66, 67]. These avenues have the unfortunate drawback of making total removal harder or damaging the transferred graphene [44]. Practical alternatives to these methods are chemical solvents. These chemical solvents can safeguard the mechanical stability of graphene, and thus, this review will explore the different solvents that have been reported and their effectiveness. Park et al. [47] studied the ability of acetone, chloroform, and acetic acid to remove PMMA. Chloroform and acetic acid were used at 25 °C, while acetone was heated to 80 °C. Each chemical performed differently as contrasted to usual acetone-based techniques. AFM images showed that acetic acid resulted in the lowest average surface roughness, achieving a 0.76 nm value. This value was close to the initially recorded value for the substrate before the transfer. In addition, the Dirac voltage of the fabricated GFET moved toward 0V, indicating that the graphene was much cleaner than before. It was accompanied by a gain in electron and hole mobilities. An attempt at annealing was also made, with a 300 °C process showing improvements while a 500 °C process showed detrimental effects. A further benefit of the annealing process was the flattening of graphene on the target substrate. Though higher temperatures work better, the degradation of graphene at higher temperatures causes a tradeoff between flatness and device performance [47]. This study showed a well-constructed, clean, and flat transfer setup, though enhancements can still be introduced to a thorough transfer process.

Another path toward improved transfer is to investigate how the transfer polymer is manufactured and used. An examination of how the molecular weight (MW) of PMMA affects the remaining residue was conducted by Liao et al. [44]. A simple acetone bath was used to determine how easily the various commercial forms of PMMA could be removed. Lower MW PMMA was found to leave less residue. However, when PMMA of too low a MW was used, it amplified the potential for physical damage due to the diminished mechanical stability of the PMMA. With this data, an improved solution of PMMA was developed that had a low MW and adequate mechanical strength. The solution was made through the mixture of PMMA-15 k and PMMA-550 k in anisole at a 2:1 ratio at 3 wt%. The resulting Raman studies showed a redshift, indicating a reduction of PMMA residues. Low surface roughness and a drop in the quantity of residual particles were recorded with AFM. Specifically, the count of 2.5 um or larger particles in a 650 x 500 um<sup>2</sup> area showed a reduction to <10 particles from a value of ~190 when high MW PMMA was used. The reduction in residue supports the idea that care in the support layer material choice can result in reduced residues [44]. An appropriate chemical solvent and a low MW PMMA support layer can provide ultraclean transfer, though it remains to be seen if such combinations suffice. More improvements can be made, though more thorough cleaning processes may increase the complexity of the wet transfer process. While the additional complexity may achieve the desired ultraclean transfer, simpler processes may achieve such results using a different support layer.

A change in the support layer material provides another approach to reducing residues.

PMMA is a strong candidate for transfer due to its low viscosity, high solubility in various organic

solvents, and its nontoxic nature. However, it firmly adheres to graphene and thus necessitates a more involved cleaning approach [47, 48]. Therefore, one method for reducing residues is to find different materials that can serve a similar purpose but are easy to remove. An investigation has been conducted into rosin, camphor, naphthalene, and anthracene [48-51]. The materials listed each provide clean and facile transfer while being simple to remove. Rosin is removed via solvent, while camphor, naphthalene, and anthracene can sublimate at comparatively mild temperatures.

Rosin is a support layer chosen by Zhang et al. [48] for its high solubility in organic solvents, weak adhesion to graphene, and sufficient mechanical strength. Rosin with a MW of 302 was dissolved in ethyl lactate before spin-coating onto a metallic substrate with grown graphene. The metallic substrate was etched with FeCl<sub>3</sub>. The removal of rosin was achieved using acetone and banana oil. Banana oil was used to ensure the removal of rosin components that were not readily removed via acetone. A surface roughness of 0.66 nm after rosin-based transfer was achieved. Further optical and High-Resolution Transmission Electron Microscopy (HRTEM) images showed remarkably clean graphene surfaces. HRTEM images did show infrequent minute residues, though such results were vastly exceeded the standard PMMA process. The cleanliness was further proved with X-ray photoelectron spectroscopy (XPS), Raman, and GFET studies [48]. The rosin process was used to create organic light-emitting diodes (OLEDs) on a flexible substrate and showed better results than a comparable PMMA or Indium Tin Oxide (ITO) process. Further improvements to the rosin-based transfer process may be possible by using different MW rosin, chemical solvents, or further annealing.

Research into the use of camphor as a support layer was conducted by Wang et al. [50]. The deposition of camphor was done by heating the powder form at 160 °C. The heated camphor was vaporized at this temperature and allowed to deposit on graphene-oxide until it achieved a

thickness of 500 um. The underlying copper growth substrate was removed via APS. After the graphene oxide was transferred, the camphor could be easily removed via sublimation at 60 °C for 24 hours. The sublimation could proceed at room temperature if left for 48 hours. While an etching process was still required to remove the copper layer, the graphene oxide was subjected to reduced stress compared to solvent-based methods. Raman studies performed before and after the removal of camphor indicated complete success, with AFM imaging unable to find traces of camphor residue and providing confirmation. The camphor-based process was replicated for graphene grown on copper. This camphor-based process achieved transfer onto an ultrathin (~100 nm) layer of polycarbonate (PC). The transfer onto an ultrathin layer is a substantial improvement in comparison to the transfer onto 1 um PC thickness that can be achieved without using camphor. Of particular interest is the failure to transfer graphene onto SiO2. However, camphor can be removed effectively, as shown [50]. Materials that can sublimate after transfer are thus still materials worthy of consideration for ultraclean transfer processes.

Another material under consideration is naphthalene. It can also sublimate and was chosen due to the lack of charge transfer to graphene and its low MW. Chen et al. melted naphthalene crystals at 100 °C and drop-cast the solution onto as-grown graphene [51]. A glass slide covered with Kapton tape was then used to press and spread the solution. The glass slide method was favored over spin coating as it did not require a solvent. The growth substrate was removed, and the graphene/Naphthalene combination was transferred. The cleaning process used a vacuum oven at 60 °C for 1 hour, though the process may proceed in air. An optional ethanol step can also reduce or eliminate any remaining residues. Images taken via AFM and SEM displayed minor residues; subsequent Raman spectroscopy corroborated the observations. The fabricated GFET displayed a mobility of 700 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and little to no doping effect. The satisfactory mobility shows that

naphthalene is a clean process with few drawbacks. As with other materials that can be sublimated, naphthalene can function for transfer onto a flexible substrate. No solvent is required, and it has sufficient mechanical strength to endure the etching and transfer process [51]. This process provides an additional example supporting the use of polymers that can be sublimated for use in the graphene transfer process.

The last material to be discussed is anthracene, which can also be sublimated with elevated process requirements compared to naphthalene and camphor. A study by Yulaev et al. [49] used thermal evaporation in a vacuum oven at -20 °C to deposit the polymer. The copper substrate was removed via APS, and the anthracene was removed by heating it at 120 °C for 40 minutes. SEM and Raman spectroscopy studies confirmed a clean transfer compared to standard PMMA processes. The study determined that an extra process using activated carbon was necessary for ultraclean graphene surfaces. The activated carbon process mandated a Pt thin film deposition onto the target substrate to provide a catalytic effect [49]. The proposed process is effective, though it requires utilization of dedicated equipment. In addition, the practical application of activated carbon may be limited.

The appeal of alternative polymer materials for facile and ultraclean transfer is high. However, these processes could be better investigated and utilized. Each method provides a simple preparation and more straightforward removal, except for anthracene, which requires a low-temperature vacuum oven. A comparison of the SEM images taken for each material will all show remarkably clean substrates. While a direct comparison is unavailable, all studies confirmed little to no left-over contaminants compared to PMMA.

The use of intermediate layers is another avenue for reduced contamination. The intermediate layer can be used to reduce the adhesion of graphene to the support structure, enabling

a cleaner removal process. A conductive polymer known as TFB (poly(9,9-di-n-octylfluorene-alt-(1,4-phenylene-(4-secbutylphenyl)imino)-1,4-phenylene), which doped with was tetrafluorotetracyano-quinodimethane, was shown to adhere to graphene in a work by Liu et al. [52]. This intermediate layer of TFB allowed for a near total removal of PMMA via acetone and was not removed itself. The process culminated in high-quality OLED devices. The researchers showed proof of cleanliness via Raman spectroscopy [52]. Though success was achieved in this instance, further exploration is required to determine if intermediate layers can be used in other applications. One potential drawback is that shaping the material into a device configuration may require etching both the underlying graphene and the intermediate layer that persists post-cleaning. An intermediate layer that can be removed via cleaning may provide more utility. However, this may introduce unwanted complexity and other challenges that must be addressed. Regardless of these challenges, an intermediate layer may be a convenient approach to creating graphene-based devices.

This chapter has shown that the wet transfer process is well-examined, with various advances made thus far. Research continues to provide additional options with varying degrees of success. Changes in the etchants have allowed for more complete metallic substrate removal. Polymer residues have been reduced through changes in solvent, the MW of PMMA, and the use of different polymers altogether. These improvements frequently increase process complexity or time or still need to achieve optimal results. These drawbacks have led to ongoing research efforts to provide wet transfer process improvements.

### 2.2 Dry Transfer Methods

The definition of a dry transfer method used herein is any method in which the graphene is transferred in a dry environment. The transfer step to the target substrate is how the difference between the dry and wet transfer methods may be illuminated. The use of liquids in the wet transfer method, while no liquids participate in the dry transfer method. The dry transfer method allows no possibility of trapping liquid between graphene and the target substrate. Removing liquid from the process can help reduce the rate of wrinkle formation and the risk of unwanted doping [68, 69]. With this definition, liquids may prepare the target or growth substrate for any subsequent transfer process. Liquids may be used for any requisite cleaning steps. Figure 3shows two general approaches to dry transfer. An indirect approach is shown in Figure 3a. The indirect method starts similarly to a standard wet transfer process. Graphene grown on copper is coated with a support layer. The copper is removed via peeling or chemical etching. Subsequently, the graphene/support layer is laminated onto the target substrate without any liquid involved in the process. The support layer may be removed via peeling, chemical etchant, or solvent. Alternatively, as shown in Figure 3b, the graphene on copper can be directly applied to the target substrate. The copper can then be peeled or etched away. A list of recent studies that used a dry transfer method is shown in Table 2.

Figure 3. a) indirect dry transfer process; b) direct dry transfer process

Table 2. Dry transfer method papers with a brief description

| Grouping                                    | Description                                                                       | Ref  |

|---------------------------------------------|-----------------------------------------------------------------------------------|------|

| Mechanical / TRT                            | Oxidize the copper growth substrate. TRT is used to                               | [37] |

|                                             | delaminate and relaminate on a target substrate                                   |      |

| Mechanical / Al <sub>2</sub> O <sub>3</sub> | Deposit Al <sub>2</sub> O <sub>3</sub> on as-grown graphene. Oxidize copper in DI | [70] |

|                                             | water bath. Use a PVA support layer for delamination and                          |      |

|                                             | remove PVA after transfer                                                         |      |

| Mechanical / Thermal                        | Deposit ultrahigh MW PE film onto as-grown graphene.                              | [71] |

|                                             | Improve adhesion via heat and then peel copper                                    |      |

| Mechanical / Thermal                        | Spin coat PEI-GA onto the growth substrate.                                       | [72] |

|                                             | Graphene/copper lamination occurs via a rolling process.                          |      |

|                                             | Apply heat and pressure to improve adhesion. Peel copper                          |      |

|                                             | via machine                                                                       |      |

| Hot Press / R2R                             | Prepare glass or PET with APTMS+PI. Hot press or R2R                              | [73] |

|                                             | onto the target substrate from the growth substrate                               |      |

| R2R                                         | Hot roll PET/EVA film onto the growth substrate. Peel                             | [74] |

|                                             | copper via another set of rollers                                                 |      |

A recent study into the dry transfer process was done by Kim et al. [37]. The direct removal of graphene from the copper growth substrate is difficult due to its high adhesion. The high adhesion causes such attempts to be prone to damaging the graphene. One method to reduce this adhesion is to oxidize the copper surface, which makes delamination of the graphene less prone to damage. Other researchers have employed this method [75, 76]. These earlier attempts suffered from the use of polymers [75], chemical etchants [76], or limited target substrates [77]. In

addressing these drawbacks, Kim et al. explored the use thermal release tape (TRT) as the support layer. TRT was chosen because it was readily removed by the application of heat. After growing graphene on copper, the copper growth substrate was situated in a hot water bath (90-95 °C) for 5 hours. The heated water bath oxidized the copper and reduced the adhesion of graphene to its surface. The substrate was taken out of the water bath and dried after the time elapsed. Then, care was taken to laminate the TRT overtop to avoid creating air bubbles. The copper and the TRT were then delaminated, releasing the graphene from the copper surface. The graphene/TRT was then transferred directly to a target substrate. The TRT was heated at 180 °C for less than a minute, which allowed a gentle lift-off to be performed. The copper foil was lightly etched to remove the copper oxide and could then be recycled for further graphene growth and transfer [37]. While the foil cannot be infinitely reused due to the thinning of the foil after the removal of copper oxide, the ability to reuse the foil helps to lower the cost of graphene growth. This dry transfer process successfully yielded graphene that was then characterized.

The graphene transferred via TRT yields desirable characteristics upon characterization. The process significantly reduced the damage to graphene, as revealed by Raman spectroscopy. The compressive strain that usually accompanies graphene growth, which results from the thermal expansion mismatch, was eased by the formation of copper oxide. The study also determined that the adhesion from this dry transfer process was superior to a typical wet transfer process. A direct comparison could be made by fabricating a GFET device with the dry transfer method and again with a wet transfer method. The GFET created via dry transfer showed an increased symmetry in the results compared to wet transfer, showing that less residue was left on the device. Additional experiments showed this to be the case and confirmed that such a GFET device had reduced contact resistance, increased on/off ratio, and improved mobilities [37]. Thus, the dry transfer method is a

serious contender for a universal ultraclean transfer process, though additional improvements are required.

An analogous experiment was conducted by Shivayogimath et al. [70] using aluminum oxide instead of TRT. This method reduced the difficulty of depositing an atomic layer deposition (ALD) layer of alumina on transferred graphene. Graphene grown on copper was used as the substrate, with the copper foil underneath supplying increased wettability. A DI water bath at room temperature was then used to oxidize the copper/graphene/Al<sub>2</sub>O<sub>3</sub> sample. The temperature was kept low to allow time for the water to seep between the graphene and copper layers to ensure better delamination. After the copper is sufficiently oxidized, the sample is removed from water and dried. It is coated with a layer of polyvinyl alcohol (PVA). The delamination can now occur, allowing the copper foil to regenerate as described earlier. The graphene can then be transferred, and the PVA layer can be removed. This process results in a small D peak being observed in Raman spectroscopy results. The presence of the D peak shows that a small amount of damage arises during the process. Additional studies demonstrated that the graphene was lightly doped, displaying a clean transfer process. It was determined that etching methods were unsuitable for this process as they would remove the Al<sub>2</sub>O<sub>3</sub> layer. This layer would need to be of an appropriate thickness, as too thin (<10 nm) would allow it to be too easily removed, and too thick (>30 nm) would cause the Al<sub>2</sub>O<sub>3</sub> layer to crack [70]. The researchers have shown that this method makes depositing high-performance gate oxides on graphene possible. They noted that other gate oxides could also be suitable and that heating the water bath may decrease the time to transfer.

Heat is a common aspect of dry transfer processes. While previous studies have used various thermal ranges, Li et al. [71] show a process using a single temperature range to transfer graphene to a flexible substrate directly. An ultra-high MW polyethylene (PE) film was used as

the target and transfer substrate, permitting a direct dry transfer process. Ethanol was introduced to the surface of the as-grown graphene to enable the PE film to be applied. The ethanol enabled the removal of air gaps upon drying and altered the adhesion forces at play. The combination film was annealed at 125-145 °C for 10 minutes, causing the PE film to partly melt and improve contact between the PE film and graphene. Afterward, the copper film could be peeled from the PE/graphene layer. The peeling allowed for the copper layer to be reused and for the graphene to be successfully transferred to the PE substrate [71]. The PE/graphene layer could be applied to a target substrate, and the PE layer could be removed if further transfer is desired. After the transfer process, the fabricated device was characterized to ensure quality.

The characterization of the PE/graphene device showed significant benefits. A lack of wrinkles was observed in imaging, highlighting the ability of this process to transfer graphene in an ultra-flat manner. It was shown that the PE/graphene morphology followed that of the copper growth substrate. SEM images showed the presence of second-layer graphene islands. Together, they highlight the need for high-quality growth processes to make subsequent high-quality transfers worthwhile. Raman spectroscopy showed a large I2<sub>D</sub>/I<sub>G</sub> ratio and no D-band signal, indicating a high-quality transfer. The researchers attribute the high quality to the improved contact area of the PE film gained from the partial melting. The partial melting increased the conformal mapping of the corrugations present on the copper film, thus ensuring that the PE and graphene layers were tightly matched. The fabricated PE/graphene device was connected to copper electrodes to create a piezoresistive strain sensor. The resulting test showed the highest factor obtained from graphene to date, with a gauge factor of 3100 at a breaking strain of 100.6%. The result is enabled by the transfer process allowing for improved use of graphene's capabilities [71].

Thus, this method provides high-quality, clean, flat graphene on flexible substrates and allows for the reuse of copper foil.

PE film is not the only material that can be used to develop a direct transfer process onto a flexible substrate. Seo et al. [72] investigated the use of adhesive gel to increase bonding to a target substrate before peeling the copper foil from graphene. A polyethylenimine (PEI) and glutaraldehyde (GA) liquid mixture (PEI-GA) was spin-coated onto a target substrate. The asgrown graphene was then laminated onto the PEI-GA/substrate via a rolling process. A high-pressure process at 160 °C was used to improve the bonding of graphene to the PEI-GA. This process also cured the PEI-GA into its gel state. The sample was quenched by blowing N2 gas to improve performance further. The copper was delaminated by a machine process, completing the transfer and allowing for the reuse of the copper film for growth.

Characterization of the fabricated graphene device was undertaken to ensure quality. The results of Raman spectroscopy verified that the graphene was wholly detached from the copper surface. The graphene was also shown to be highly n-doped from the PEI-GA, and little to no damage was observed. Despite the doping, sheet resistance results showed a much lower resistance than a standard wet transfer process. The wrinkling of graphene was also reduced, as the average surface roughness was measured to be ~0.26 nm after transfer. This measurement is compared to the ~2.78 nm surface roughness of graphene on the copper growth substrate. It was determined through further testing that the gel's viscoelastic nature helped flatten the graphene. The proof of minor to no structural damage of graphene was obtained via a vapor test. A pristine graphene sample is impermeable to all gases except for H<sub>2</sub> [78]. A standard wet transfer process does not allow for graphene to showcase this trait due to the holes induced during the transfer process [79, 80]. The test identified an increase of 10x to a previously reported lowest value, highlighting the

defect-free nature of the transfer. This defect-free result was further proved by the graphene layer's ability to protect the underlying PEI-GA layer against solvents [72]. Presuming the n-type doping is desired or of little concern, PEI-GA is an effective polymer for dry transfer. Despite this process's high quality and ultra-flat surface, dopant-free transfer remains.

The application of heat and pressure may be performed with a hot press, as in the preceding study, or using rollers. Marchena et al. [73] performed a study that compared these two processes. They used either a glass or a polyethylene terephthalate (PET) substrate. The glass substrate was prepared with a proprietary polyimide (PI) blend, while 3-aminopropyltrimethoxysilane (APTMS) was added to the PET. The samples were dried in a 40-80 °C oven. The transfer process differed at this stage. The hot press processes were performed at 150 °C under 150-300 psi of pressure for 10 minutes. A silicone rubber sheet was used to attain a homogenous pressure distribution. The rolling process, also known as a roll-to-roll (R2R) process, was performed with heated silicon rollers at a prespecified distance. The temperature was set to 140 °C for either the glass or PET case. The distance was set to 1-2 mm for the glass substrates and 38 um-1 mm for the PET. The discrepancy in temperature between the hot press and R2R method was not a concern as these set points signified optimum operating conditions. The copper was peeled away after lamination through the hot press or R2R process. Though each process was individually optimized, the transfer results were shown to differ. The hot press process showed a diminished dependence on the morphology of the copper substrate, as the mobility was high despite the imprinting of the copper surface onto the PI film. However, the R2R method depended on surface morphology, requiring low surface roughness copper film. The R2R method additionally had heightened mechanical damage due to the associated shear and compressive forces, which could also be reduced with low surface roughness copper film [81, 82]. The PI film in this process resulted in ntype doping, overriding the effect normally present in a glass or PET substrate. The doping was due to the PI layer being the contact layer of graphene instead of glass or PET. The researchers showed that polyamic acid could create different forms of PI, allowing for a broader range of materials for this process [73]. This research reinforces the idea that the choice of graphene contact surface can strongly influence the properties of graphene. Additionally, the quality of the transferred graphene can be improved by optimizing process parameters, highlighting the need for revised processes.

Achieving large-scale graphene transfer and reusing growth substrates significantly benefit an R2R process. However, the R2R process needs to solve the issue of mechanical damage and the decreased quality that results. A study was undertaken by Hong et al. [74] o optimize the R2R process to achieve higher-quality graphene transfer. The researchers chose to optimize the peeling speed and tension. A PET and ethylene vinyl acetate (EVA) film was compressed onto the asgrown graphene with a roller at 150 °C to determine the best parameters. Results showed that low speed had a high variability in quality while high speed was less variable. Regarding the peeling tension, high tension caused increased variability due to increased mechanical damage at the grain boundaries of graphene. The two parameters also displayed a relationship, with higher speeds requiring higher tension for better results. The best results were attained at a peeling speed of 2 m/min and a peeling force of 10 N. While Hong et al. could not achieve a higher performance due to the lack of available speed, regression analysis indicated that a 1.8 m/min speed at 12 N may provide better results. Experiments on the constructed GFET showed a near-zero doping level and a low Dirac point. The researchers showed consistent results across multiple devices, displaying the ability to reproduce their efforts. In their fabrication process, gold was deposited on top of the graphene instead of underneath, which decreased the gate leakage current. A sheet resistance